# INVESTIGATIONS ON TOPOLOGY, ANALYSIS AND EXPERIMENTAL VERIFICATION OF CENTER-POINT-CLAMPED POWER LINE CONDITIONER

by

### PANKAJ KUMAR BHOWMIK

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2019

| Approved by:         |   |

|----------------------|---|

| Dr. Madhav Manjrekar |   |

| Dr. Badrul Chowdhury |   |

| Dr. Robert Cox       | _ |

| Dr. Milind Khire     | _ |

©2019 PANKAJ KUMAR BHOWMIK ALL RIGHTS RESERVED

#### **ABSTRACT**

PANKAJ KUMAR BHOWMIK. Investigations on Topology, Analysis and Experimental Verification of Center-Point-Clamped Power Line Conditioner. (Under the direction of DR. MADHAV MANJREKAR)

A new approach for power line conditioning has been presented in this dissertation. Prevalent state of the art line-conditioning devices like Static Voltage Restorer (SVR), Dynamic Voltage Restorer (DVR) and AC-AC power line conditioner offers higher bandwidth and low filter size requirement due to their high switching frequencies. However, commercial utilization of such devices is restricted by voltage blocking capability of power semiconductor switches employed in these converters. Recent literature reports a Center-Point-Clamped AC-AC Converter topology based on Neutral-Point Clamped DC-AC inverter, where the grid voltage is clamped to its midpoint to reduce the voltage stress on the bi-directional switches employed in the converter by 50%. This document introduces a Power Line Conditioner based on Center-Point-Clamped AC-AC Converter topology, where the grid voltage is clamped to its midpoint to reduce the voltage stress on the bi-directional switches employed in the converter to half the summation of grid input and load output voltage. This power line conditioner is coined as Center-Point-Clamped Power Line Conditioner (CPC PLC). A duty cycle control scheme has also been implemented for feedback control of CPC PLC. An experimental prototype has been built in the laboratory. The results verify that proposed CPC PLC offers reduced voltage stress on the bi-directional switches. It may also be that CPC PLC is capable of mitigating grid voltage sag up to 90% and grid voltage swell up to 10%, which comprise of about 74% of the grid power quality issues. Furthermore, these results verify that the designed duty-cycle based control scheme has excellent load voltage regulation under dynamic line voltage conditions.

#### **ACKNOWLEDGEMENTS**

I would like to express my gratitude towards my dad, Pradip Kumar Bhowmik, my mom, Rekha Bhowmik and my sister, Dr. Smita Bhowmik, M.D., for believing in me and making it possible for me to follow my dream of pursuing higher education. They are the ones who laid down the foundational pillars of Who I am and What I am.

I would like to thank my advisor, Dr. Madhav Manjrekar, for his guidance, mentorship and encouragement through all the trials and tribulations of the PhD degree. His words, "You are not an unskilled manual laborer. You are an engineer and a technical researcher. You need to constantly keep researching and innovating.", will always remain with me throughout my life as I embark on my professional career post PhD.

It would be my duty to extend my gratitude to the committee members Dr. Badrul Chowdhury, Dr. Robert Cox and Dr. Milind Khire for their invaluable inputs over the course of my dissertation as a part of my dissertation committee and assessing my work. Their invaluable technical inputs on my research has helped me mold a strong PhD dissertation.

I am thankful to ECE Department (Electrical and Computer Engineering) especially Stephanie LaClair Brillante who has helped me stay focused by providing invaluable guidance and support over the course of PhD. Also, I would like to thank Eddie Hill for his much-needed help and support in any technical project set-up throughout my graduate study years at UNCC. I am grateful to Dr. Yogendra Kakad, who has been and will be one of my most respected and favorite professor at UNCC, for the extremely helpful technical discussions. I would also like to thank Dr. Yawo Amengonu, for his inputs into PhD life,

being a fellow 49er. Finally, I would like to extend my gratefulness to Dr. Abasifreke Ebong, Graduate Student Coordinator for his immense support and help.

I am grateful to EPIC (Energy Production and Infrastructure Center) for its generous help and support towards my dissertation research, special thanks to Robin Moose and Lori Brown.

I am indebted to my research group for their incomparable help and support. First, I would like to extend my thanks to Dr. Ehab Shoubaki and Dr. Somasundaram Essakiappan for being a friend and mentor from time to time. I got the opportunity to work with them on several projects which helped me increase my technical acumen. Amongst my lab mates, my thanks go to Prashant Kumar Sahu and Nakul Shah for our endless coffee shop discussions. I would also like to thank Nazmus Sakib for his help and support.

Finally, I would like to thank my graduate officemate, Dr. Veysel Unsur, and all my friends at UNCC, special thanks to Dr. Mehrdad Biglarbegian, Dr. Manohar Chamana, Arnab Baruah, Roozbeh Kharandeh, Bilkis Hossain and Tumininu Lawanson.

Last but not the least, I would like to thank my Charlotte family members, Navdeep Singh Dandiwal, Kshitiz Gupta, Dr. Sukhpreet Sagoo, Ashitosh Surve and Akash Gupta for keeping me balanced on my feet financially and emotionally. They are an invaluable part of the support system which helped me navigate through life and PhD degree.

It has been a couple of years of journey towards my PhD dissertation and I would like to thank everyone who I missed in this acknowledgement and has had a positive impact on my life and PhD research.

# **Table of Contents**

| List of | List of Tables xi  List of Figures xiii  Chapter One: Introduction 1 |  |  |

|---------|----------------------------------------------------------------------|--|--|

| List of |                                                                      |  |  |

| 1. Cł   |                                                                      |  |  |

| 1.1.    | Introduction to Power Quality                                        |  |  |

| 1.2.    | Power Quality Terms                                                  |  |  |

| 1.3.    | Power Quality Definitions                                            |  |  |

| 1.4.    | Impact of Power Quality Issues                                       |  |  |

| 1.5.    | Causes of poor Power Quality9                                        |  |  |

| 1.6.    | Proposed Solution to Power Quality Issue                             |  |  |

| 2. Cł   | napter Two: Review of Power Line Conditioners (PLC)                  |  |  |

| 2.1.    | Tap-Changing Transformer                                             |  |  |

| 2.2.    | Dynamic Sag Corrector (DySC)                                         |  |  |

| 2.3.    | Dynamic Voltage Restorer (DVR)                                       |  |  |

| 2.4.    | Unified Power Quality Conditioner (UPQC)                             |  |  |

| 2.5.    | Solid State Transformer (SST)                                        |  |  |

| 2.5     | 5.1. Matrix Type AC-AC SST                                           |  |  |

| 2.5     | 5.2. Isolated Back End SST                                           |  |  |

| 2.5     | 5.3. Isolated Front End SST                                          |  |  |

| 2.4     | 5.4. Isolated Modular Multilevel Converter SST                       |  |  |

|    | 2.5  | 5.5. S     | Single Cell Approach SST                           | . 34 |

|----|------|------------|----------------------------------------------------|------|

|    | 2.6. | Thı        | ree-Phase AC Line Conditioner                      | . 35 |

| 3. | Ch   | aptei      | r Three: Principle of Center-Point-Clamping        | . 37 |

|    | 3.1. | Intı       | roduction                                          | . 37 |

|    | 3.2. | Mo         | ntivation for Center-Point-Clamped AC-AC Converter | . 37 |

|    | 3.3. | Evo        | olution of Center-Point-Clamped AC-AC Converter    | . 38 |

|    | 3.4. | Cei        | nter-Point-Clamped AC-AC Buck Converter            | . 41 |

|    | 3.4  | .1.        | Hardware Circuit Configuration                     | . 41 |

|    | 3.4  | 1.2.       | Operating Principle                                | . 42 |

|    | 3.4  | 1.3.       | Capacitor Voltage Balancing                        | . 43 |

|    | 3.4  | l.4.       | Verification Results and Discussions               | . 44 |

|    | 3.5. | Cei        | nter-Point-Clamped AC-AC 1-Ø Buck-Boost Converter  | . 50 |

|    | 3.5  | 5.1.       | Hardware Circuit Configuration                     | . 50 |

|    | 3.5  | 5.2.       | Operating Principle                                | . 51 |

|    | 3.5  | 5.3.       | Verification Results and Discussions               | . 52 |

|    | 3.6. | Cei        | nter-Point-Clamped AC-AC 3-Ø Buck-Boost Converter  | . 57 |

|    | 3.6  | 5.1.       | Circuit Configuration                              | . 57 |

|    | 3.6  | 5.2.       | Operating Principle                                | . 58 |

|    | 3.6  | 5.3.       | Verification Results and Discussions               | . 60 |

|    | 3.6  | 5 <u>4</u> | Center-Point-Clamped 3-Ø Power Line Conditioner    | 70   |

| 3.6.5. | Center-Point-Clamped 3-Ø Power Line Conditioner for 4.16kV application |

|--------|------------------------------------------------------------------------|

|        | 73                                                                     |

| 4. Cl  | hapter Four: Hardware Circuit Design of Center-Point-Clamped Power  | er Line    |

|--------|---------------------------------------------------------------------|------------|

| Condit | ioner (CPC PLC)                                                     | 78         |

| 4.1.   | Introduction                                                        | 78         |

| 4.2.   | Circuit Description                                                 | 78         |

| 4.3.   | Selection of Power Semiconductor Device                             | 80         |

| 4.4 \$ | Selection of Passive Components in converter circuit, L & C         | 81         |

| 4.     | 4.1. Steady State Circuit Analysis                                  | 82         |

| 4.     | 4.2. Selection of L and C values                                    | 89         |

| 5. Cl  | hapter Five: Dynamic Analysis and Controller Design for Center-Poir | nt-Clamped |

| Power  | Line Conditioner (CPC PLC)                                          | 93         |

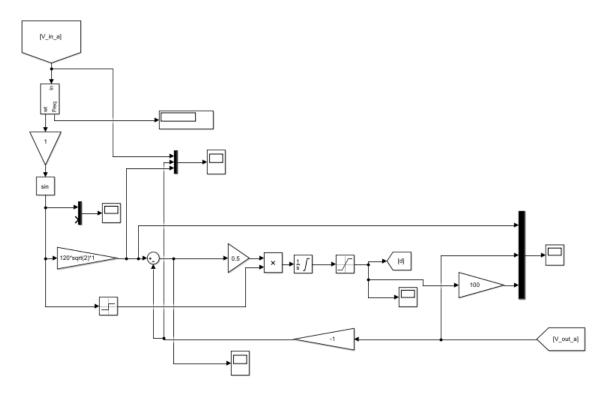

| 5.1.   | State Space Averaging                                               | 94         |

| 5.2.   | Small Signal Modelling                                              | 103        |

| 5.3.   | Open Loop Frequency Domain Plots                                    | 106        |

| 5.4.   | Controller Design                                                   | 112        |

| 5.     | 4.1 Controllability Test                                            | 112        |

| 5.     | 4.2. Controller Transfer Function                                   | 114        |

| 6. Cl  | hapter Six: Simulation Results                                      | 120        |

| 6 1 I  | Introduction                                                        | 120        |

|    | 6.2. Open  | -Loop 3-Ø CPC PLC Simulation Model                                   | 23  |

|----|------------|----------------------------------------------------------------------|-----|

|    | 6.3. Close | ed-Loop 3-Ø CPC PLC Simulation                                       | 36  |

|    | 6.3.1. L   | ine-Regulation Performance of 3-Ø CPC PLC for low input voltage 1    | 40  |

|    | 6.3.2. L   | ine-Regulation Performance of 3-Ø CPC PLC for high input voltage 1   | 54  |

|    | 6.3.3. L   | Load Regulation Performance of 3-Ø CPC PLC for low output load 1     | 68  |

|    | 6.3.4. L   | Load Regulation Performance of 3-Ø CPC PLC for high output load 1    | 82  |

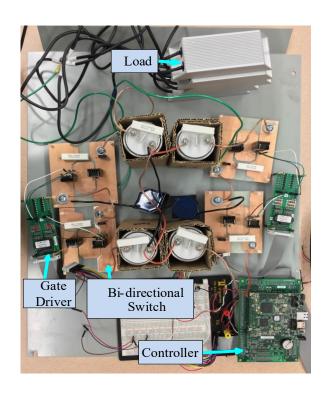

| 7. | Chapter    | r Seven: Experimental Setup 1                                        | 96  |

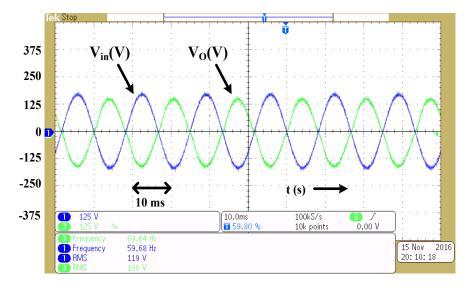

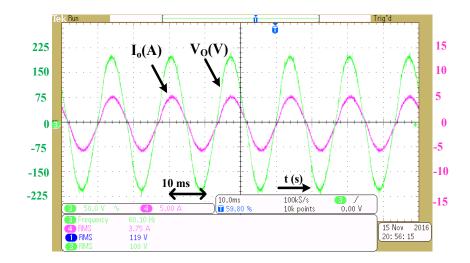

|    | 7.1. Sin   | gle-Phase Hardware Results 1                                         | 97  |

|    | 7.2. Th    | ree-phase Hardware Results2                                          | :04 |

|    | 7.2.1.     | Power Stage Hardware Design                                          | :04 |

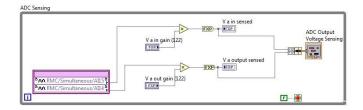

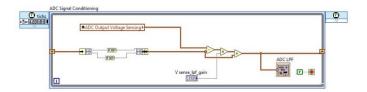

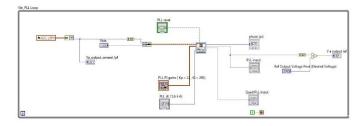

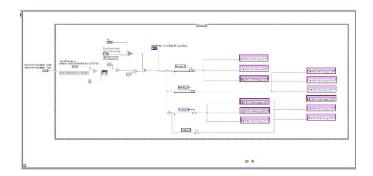

|    | 7.2.2.     | Controller Algorithm Design in LabVIEW FPGA                          | :07 |

|    | 7.2.3.     | Experimental Waveforms                                               | 211 |

| 8. | Chapter    | r Eight: Capability Verification of CPC PLC                          | 18  |

|    | 8.1. Des   | sign of Passive Components of CPC PLC for 4.16 kV application 2      | 18  |

|    | 8.2. Per   | formance of 4.16 kV Application CPC PLC model for Varying Voltage Sa | g   |

|    | 225        | 5                                                                    |     |

|    | 8.2.1.     | Grid Voltage Sag: 10 % of 4.16 kV                                    | 25  |

|    | 8.2.2.     | Grid Voltage Sag: 20% of 4.16 kV                                     | 27  |

|    | 8.3.3. 0   | Grid Voltage Sag: 50 % of 4.16 kV                                    | 29  |

|    | 8346       | Grid Voltage Sag: 80% of 4.16 kV                                     | 21  |

|      | .3.5. Grid Voltage Sag: 90% of 4.16 kV                                      | 33 |

|------|-----------------------------------------------------------------------------|----|

|      | .3.6. Grid Voltage Swell: 10% of 4.16 kV                                    | 35 |

|      | .3.7. Discussion on Performance of CPC PLC                                  | 37 |

| 9.   | Chapter Nine: Conclusions                                                   | 38 |

| 9.1  | Comparative Evaluation of CPC PLC versus related power electronic solutions | S  |

| for  | power line conditioning22                                                   | 38 |

| 9.2  | Summary                                                                     | 41 |

| 9.3  | Scope for future research                                                   | 43 |

| Refe | ences                                                                       | 44 |

## **List of Tables**

| TABLE 1-1: LIST OF CURRENT STANDARDS ON POWER QUALITY ISSUES [1]         | 1              |

|--------------------------------------------------------------------------|----------------|

| TABLE 1-2: CATEGORIZATION OF POWER QUALITY ISSUES [3], [4]               | 5              |

| TABLE 1-3: QUANTIFICATION OF POWER QUALITY ISSUES [5]                    | 6              |

| TABLE 1-4: UPTIME AND MAXIMUM DOWNTIME PER YEAR                          | 8              |

| TABLE 2-1: ANALYSIS OF POWER QUALITY ISSUES RESOLVED BY PREVALENT POWER  | -              |

| QUALITY SOLUTIONS                                                        | 14             |

| TABLE 3-1: SWITCHING PRINCIPLE OF CENTER-POINT-CLAMPED AC-AC BUCK CONVER |                |

| TABLE 3-2: SWITCHING PRINCIPLE OF CENTER-POINT-CLAMPED AC-AC BUCK-BOOST  | <del>4</del> 2 |

| CONVERTER                                                                | 51             |

| TABLE 3-3: SWITCHING PRINCIPLE OF CENTER-POINT-CLAMPED AC-AC BUCK-BOOST  |                |

| CONVERTER                                                                | 58             |

| TABLE 4-1: SWITCHING PRINCIPLE OF CPC PLC                                | 82             |

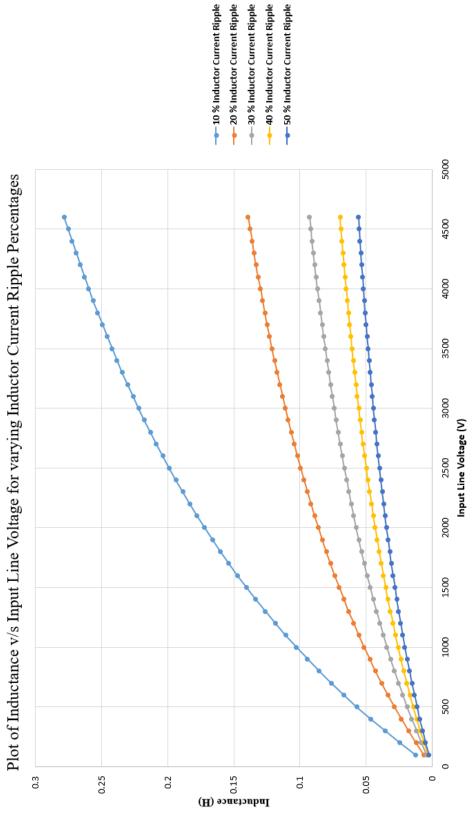

| TABLE 4-2: INDUCTANCE VALUES FOR DIFFERENT OPERATING POINTS              | 90             |

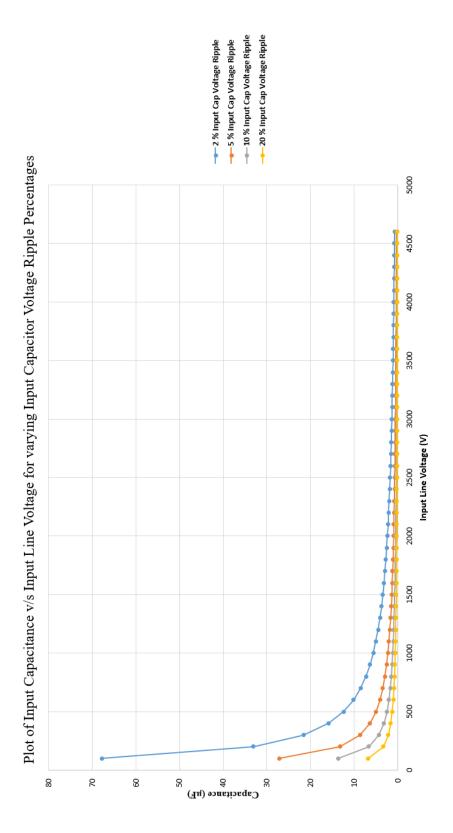

| TABLE 4-3: INPUT CAPACITANCE VALUES FOR DIFFERENT OPERATING POINTS       | 91             |

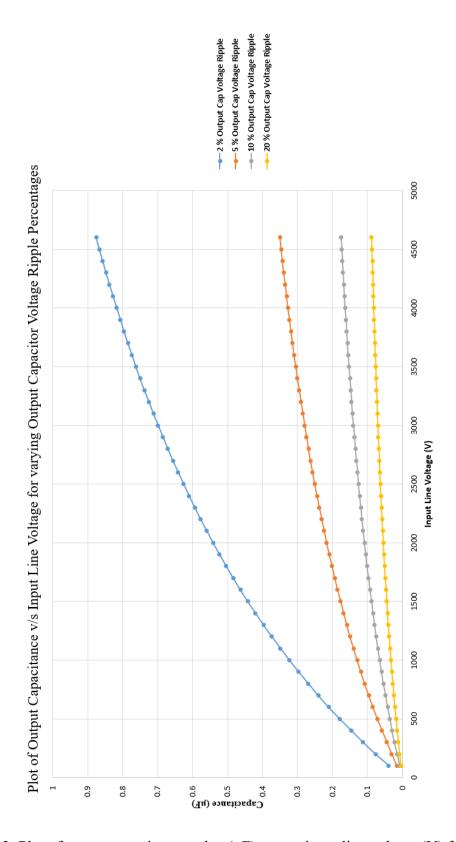

| TABLE 4-4: OUTPUT CAPACITANCE VALUES FOR DIFFERENT OPERATING POINTS      | 92             |

| TABLE 5-1: SWITCHING PRINCIPLE OF CPC PLC                                | 93             |

| TABLE 5-2: LIST OF VALUES FROM SELECTED COMPONENTS FOR STATE SPACE       |                |

| VARIABLES                                                                | 107            |

| TABLE 5-3: OPERATING CONDITION PARAMETERS                                | 108            |

| TABLE 5-4: POLES AND ZEROS OF TRANSFER FUNCTION Hcs                      | 113            |

| TABLE 6-1: LIST OF VALUES FROM SELECTED COMPONENTS FOR STATE SPACE       |                |

| VARIABLES                                                                | 120            |

| TABLE 7-1: EXPERIMENTAL PARAMETERS OF CENTER-POINT-CLAMPED POWER LINE    |                |

| CONDITIONER                                                              | 198            |

| TABLE 8-1: FIXED INDUCTOR DESIGN PARAMETERS FOR 3-Ø CPC PLC              | 219            |

| TARLE 8.2) FIXED CAPACITOR DESIGN PARAMETERS FOR 3.00 CPC PLC            | 221            |

| TABLE 9-1: COMPARISON OF CPC PLC VERSUS PREVALENT POWER QUALITY | SOLUTIONS |

|-----------------------------------------------------------------|-----------|

| BASED ON DESIGN FEATURES                                        | 238       |

| TABLE 9-2: COMPARISON OF CPC PLC VERSUS PREVALENT POWER QUALITY | SOLUTIONS |

| BASED ON POWER QUALITY ISSUE MITIGATION                         | 239       |

# **List of Figures**

| FIGURE 2-1: ANALYSIS OF POWER QUALITY EVENTS                                 | 13  |

|------------------------------------------------------------------------------|-----|

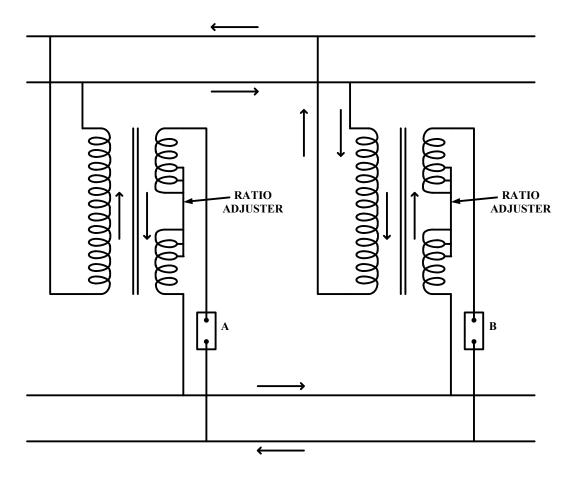

| FIGURE 2-2: SIMPLIFIED SCHEMATIC OF TWO TAP CHANGING TRANSFORMER IN A UTIL   | ITY |

| POWER LINE                                                                   | 15  |

| FIGURE 2-3: SIMPLIFIED SCHEMATIC OF MODIFIED TAP CHANGING TRANSFORMER IN A   | L   |

| UTILITY POWER LINE                                                           | 16  |

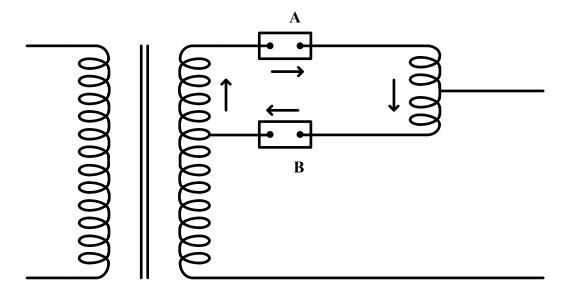

| FIGURE 2-4: CIRCUIT SCHEMATIC OF A SINGLE-PHASE DYNAMIC SAG CORRECTOR (DYS   | SC) |

| TOPOLOGY                                                                     | 18  |

| FIGURE 2-5: CIRCUIT SCHEMATIC OF A THREE-PHASE MEGA DYNAMIC SAG CORRECTOR    | R   |

| (MEGADYSC) TOPOLOGY                                                          | 19  |

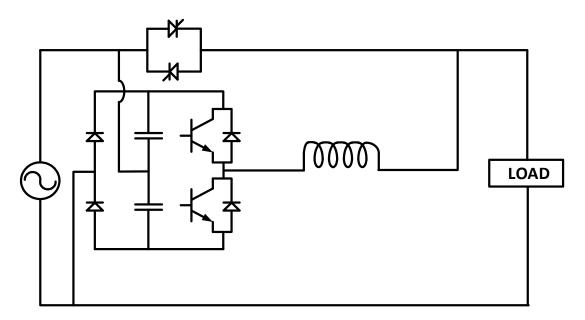

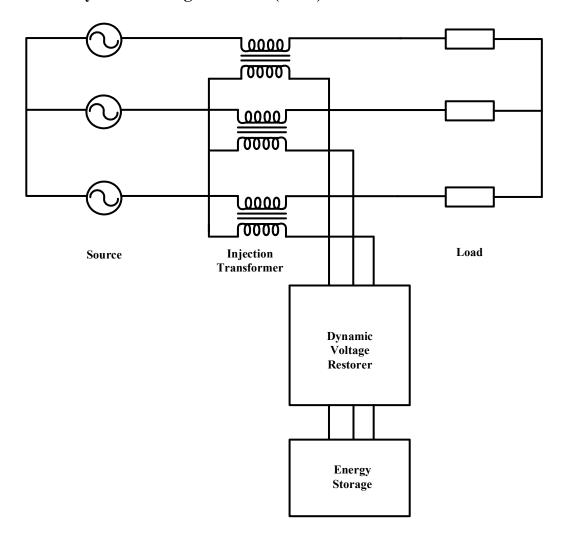

| FIGURE 2-6: CIRCUIT SCHEMATIC OF A DYNAMIC VOLTAGE RESTORER (DVR)            | 20  |

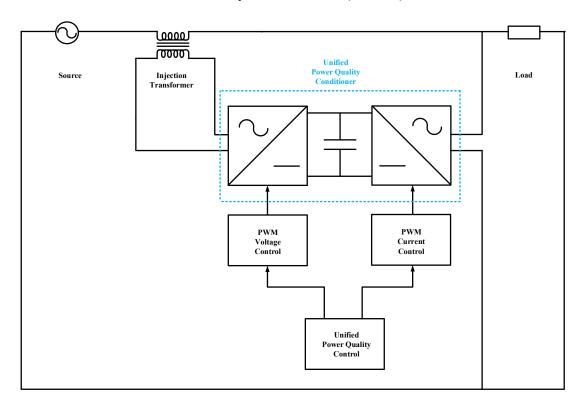

| FIGURE 2-7: CIRCUIT SCHEMATIC OF A SINGLE-PHASE UNIFIED POWER QUALITY        |     |

| CONDITIONER (UPQC)                                                           | 22  |

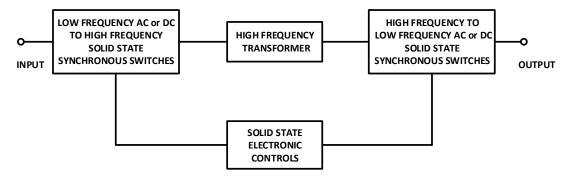

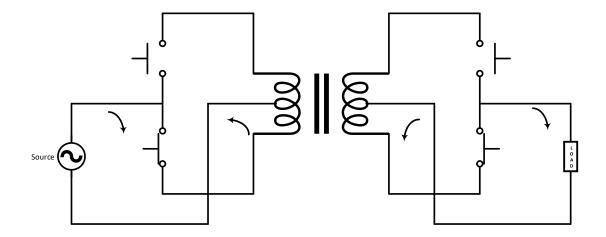

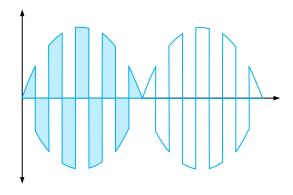

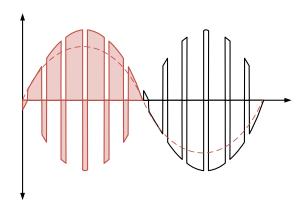

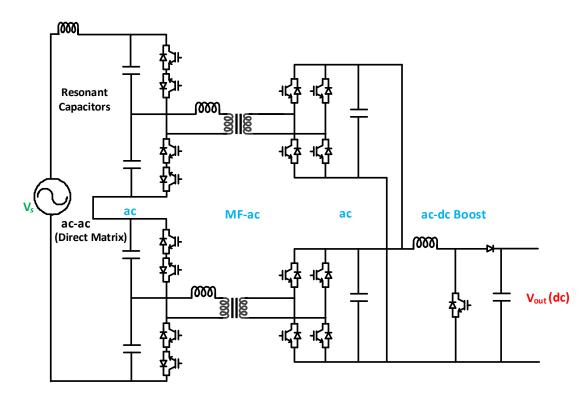

| FIGURE 2-8: POWER CONVERTER CIRCUIT HAVING A HIGH FREQUENCY LINK             | 23  |

| FIGURE 2-9: CONTROL SCHEMATIC FOR POWER CONVERTER CIRCUIT                    | 23  |

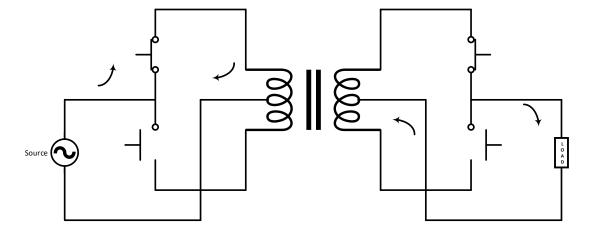

| FIGURE 2-10: POWER CONVERTER CIRCUIT DURING POSITIVE HALF CYCLE OF SINE WAY  | VE  |

|                                                                              | 25  |

| FIGURE 2-11: POWER CONVERTER CIRCUIT DURING NEGATIVE HALF CYCLE OF SINE      |     |

| WAVE                                                                         | 25  |

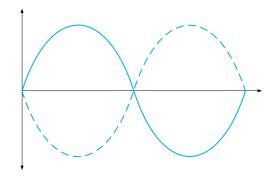

| FIGURE 2-12: INPUT SOURCE SIGNAL                                             | 26  |

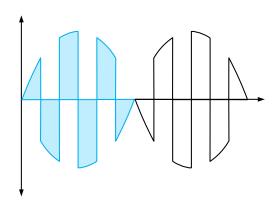

| FIGURE 2-13: INPUT SIGNAL SWITCHED AT 360HZ SWITCHING FREQUENCY              | 26  |

| FIGURE 2-14: INPUT SIGNAL SWITCHED AT 540 HZ SWITCHING FREQUENCY             | 26  |

| FIGURE 2-15: INPUT SIGNAL SWITCHED AT 720 HZ SWITCHING FREQUENCY             | 27  |

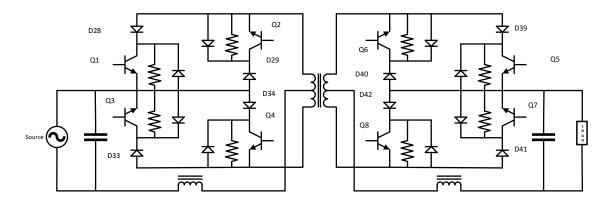

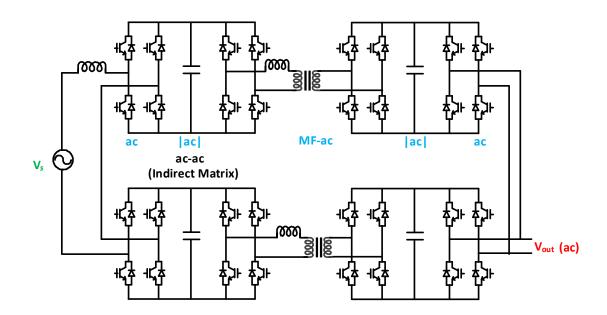

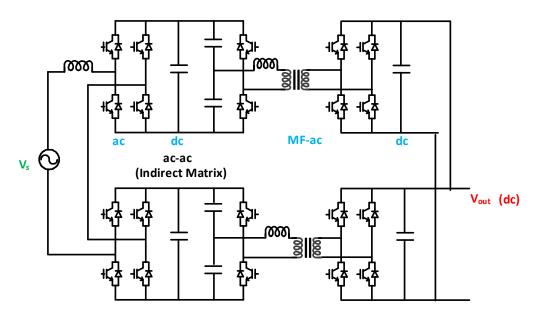

| FIGURE 2-16: SIMPLIFIED CIRCUIT SCHEMATIC OF A TYPICAL MATRIX-TYPE AC-AC SST |     |

| TOPOLOGY                                                                     | 30  |

| FIGURE 2-17: SIMPLIFIED CIRCUIT SCHEMATIC OF A TYPICAL IBE TYPE SST TOPOLOGY | 31  |

| FIGURE 2-18: SIMPLIFIED CIRCUIT SCHEMATIC OF A TYPICAL IFF TYPE SST TOPOLOGY | 32  |

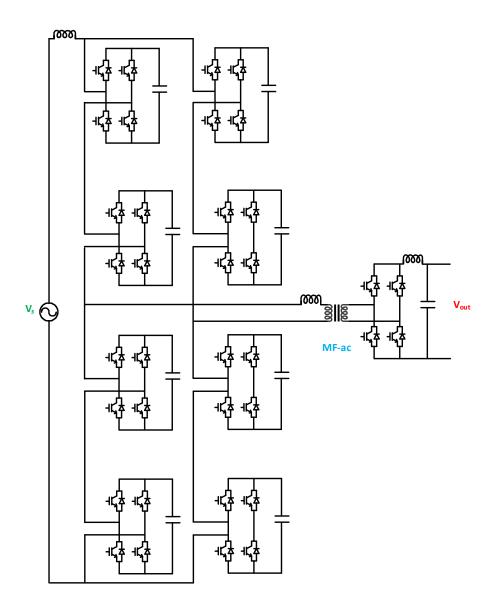

| FIGURE 2-19: SIMPLIFIED CIRCUIT SCHEMATIC OF A TYPICAL ISOLATED MODULAR                                              |                    |

|----------------------------------------------------------------------------------------------------------------------|--------------------|

| MULTILEVEL CONVERTER TYPE SST TOPOLOGY                                                                               | 33                 |

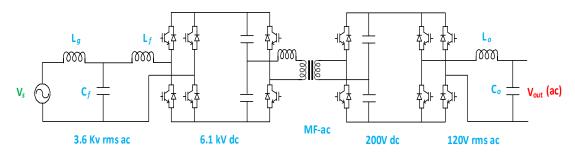

| FIGURE 2-20: SIMPLIFIED CIRCUIT SCHEMATIC OF A TYPICAL SINGLE CELL APPROACH                                          |                    |

| BASED                                                                                                                |                    |

| TOPOLOGY 34                                                                                                          |                    |

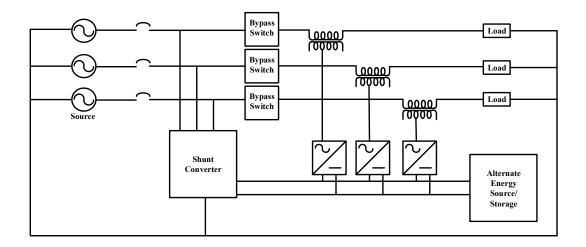

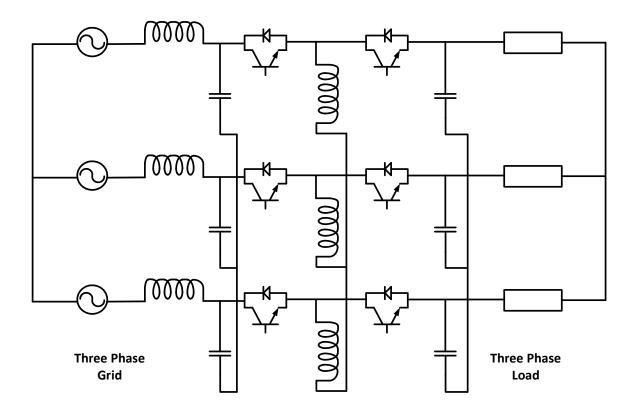

| FIGURE 2-21: CIRCUIT SCHEMATIC OF A THREE PHASE PWM AC-AC BUCK-BOOST                                                 |                    |

| CONVERTER                                                                                                            | 35                 |

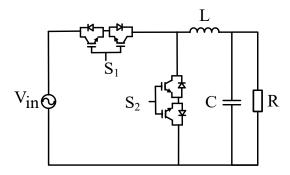

| FIGURE 3-1: SIMPLIFIED CIRCUIT SCHEMATIC OF THE AC-AC BUCK CONVERTER.                                                | 38                 |

| FIGURE 3-2: SIMPLIFIED CIRCUIT SCHEMATIC OF THE AC-AC CONVERTER WITH SERIES                                          | <b>;</b>           |

| CONNECTED IGBTS.                                                                                                     | 39                 |

| FIGURE 3-3: SIMPLIFIED CIRCUIT SCHEMATIC OF THE AC-AC CONVERTER WITH SERIES                                          | <b>\$</b>          |

| CONNECTED IGBTS IN A SYMMETRICAL CONFIGURATION.                                                                      | 40                 |

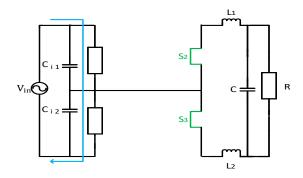

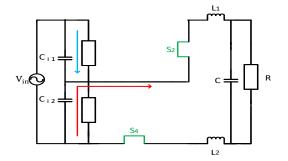

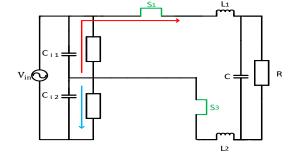

| FIGURE 3-4: SIMPLIFIED CIRCUIT SCHEMATIC OF THE CENTER-POINT-CLAMPED AC-AC                                           |                    |

| BUCK CONVERTER.                                                                                                      | 41                 |

| FIGURE 3-5: SIMPLIFIED CIRCUIT SCHEMATIC OF THE CONVERTER DURING STATES 1, 3                                         | OF                 |

| SWITCHING SEQUENCE WHEN COMMAND VOREF IS BETWEEN 0 AND VIN/2.                                                        | 43                 |

| FIGURE 3-6: SIMPLIFIED CIRCUIT SCHEMATIC OF THE CONVERTER DURING STATES 1, 3                                         | OF                 |

| SWITCHING SEQUENCE WHEN COMMAND VOREF IS BETWEEN VIN/2 AND VIN.                                                      | 43                 |

| FIGURE 3-7: SIMPLIFIED CIRCUIT SCHEMATIC OF THE CONVERTER DURING STATE 2.                                            | 43                 |

| FIGURE 3-8: SIMPLIFIED CIRCUIT SCHEMATIC OF THE CONVERTER DURING STATE 4.                                            | 43                 |

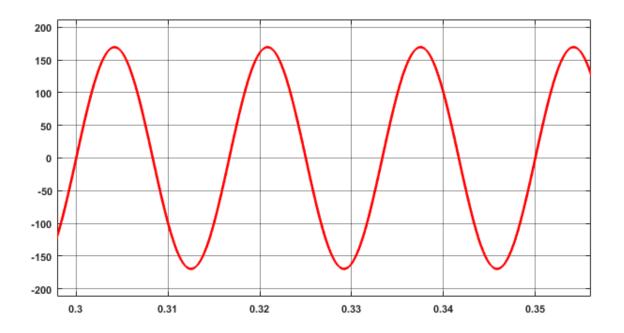

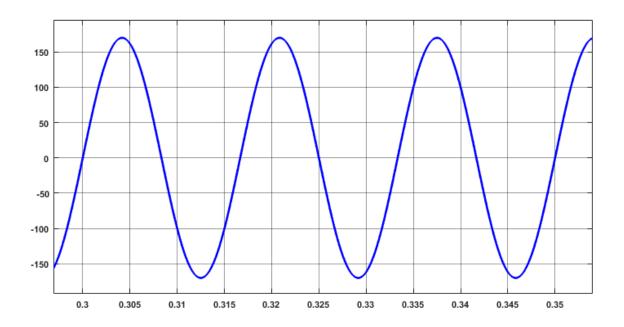

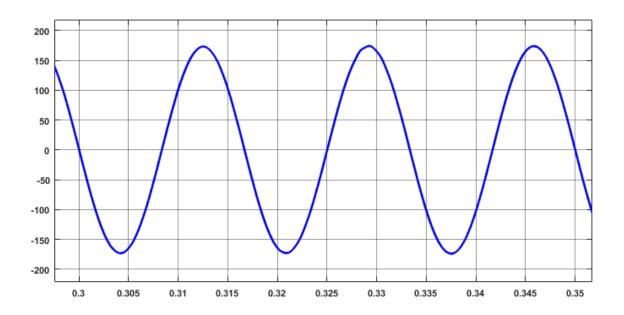

| FIGURE 3-9: INPUT SOURCE VOLTAGE APPLIED TO CPC AC-AC BUCK CONVERTER.                                                | 45                 |

| FIGURE 3-10: VOLTAGE ACROSS THE TWO INPUT CAPACITORS, $C_{11}$ AND $C_{12}$                                          | 45                 |

| FIGURE 3-11: VOLTAGE STRESS ACROSS EACH BI-DIRECTIONAL SWITCH S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> AND S | S <sub>4.</sub> 46 |

| FIGURE 3-12: OUTPUT VOLTAGE OF CPC AC-AC BUCK CONVERTER FOR DUTY RATIO OF                                            | F                  |

| 0.3.                                                                                                                 | 47                 |

| FIGURE 3-13: OUTPUT VOLTAGE OF CPC AC-AC BUCK CONVERTER FOR DUTY RATIO OF                                            | F                  |

| 0.8.                                                                                                                 | 47                 |

| FIGURE 3-14: INPUT SOURCE VOLTAGE OF CPC AC-AC BUCK CONVERTER                                                        | 48                 |

| FIGURE 3-15: VOLTAGE STRESS ACROSS EACH BI-DIRECTIONAL SWITCH, $S_1,S_2,S_3$ AND $S_4$         | ı.48       |

|------------------------------------------------------------------------------------------------|------------|

| FIGURE 3-16: OUTPUT VOLTAGE OF CPC AC-AC BUCK CONVERTER FOR DUTY RATIO OF                      |            |

| 0.3.                                                                                           | 49         |

| FIGURE 3-17: OUTPUT VOLTAGE OF CPC AC-AC BUCK CONVERTER FOR DUTY RATIO OF                      |            |

| 0.8.                                                                                           | 49         |

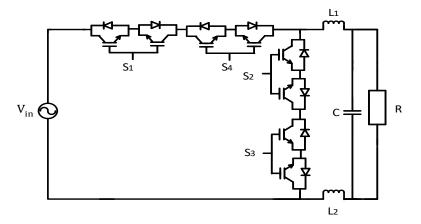

| FIGURE 3-18: SIMPLIFIED CIRCUIT SCHEMATIC OF THE CENTER-POINT-CLAMPED AC-AC                    |            |

| BUCK-BOOST CONVERTER.                                                                          | 50         |

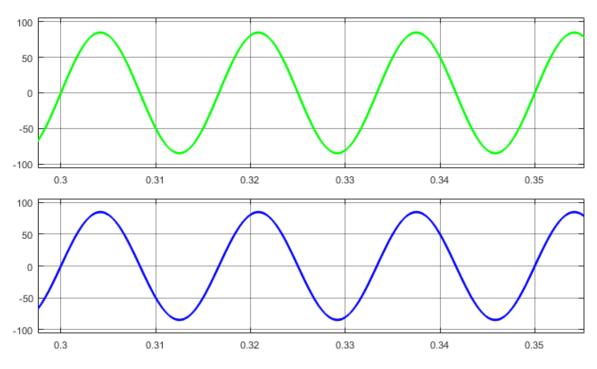

| FIGURE 3-19: INPUT SOURCE VOLTAGE OF CENTER-POINT-CLAMPED AC-AC BUCK-BOOS                      | T          |

| CONVERTER                                                                                      | 52         |

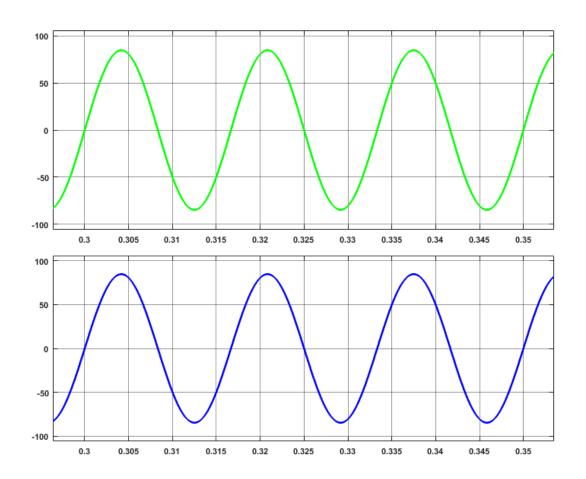

| FIGURE 3-20: VOLTAGE ACROSS THE TWO INPUT CAPACITORS, $C_{11}$ (GREEN) AND $C_{12}$ (BLU       | E).        |

|                                                                                                | 53         |

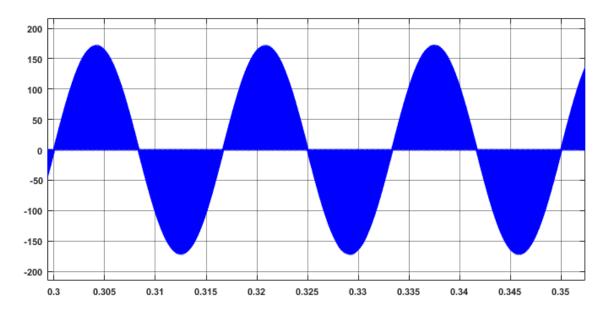

| FIGURE 3-21: VOLTAGE STRESS ACROSS EACH BI-DIRECTIONAL SWITCH $S_1,S_2,S_3$ AND $S_4$ .        | 53         |

| FIGURE 3-22: OUTPUT VOLTAGE OF CPC AC-AC BUCK CONVERTER FOR DUTY RATIO OF                      |            |

| 0.5.                                                                                           | 54         |

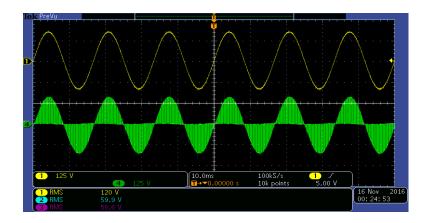

| FIGURE 3-23: INPUT VOLTAGE (YELLOW) AND VOLTAGE STRESS ON A BI-DIRECTIONAL                     |            |

| SWITCH (GREEN) OF CPC AC-AC BUCK-BOOST CONVERTER                                               | 55         |

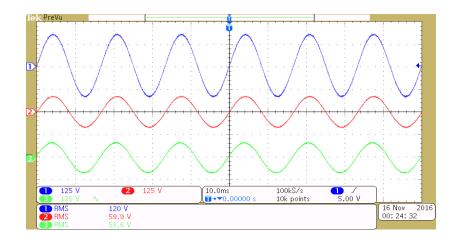

| FIGURE 3-24: INPUT VOLTAGE (BLUE), INPUT CAPACITOR 1 VOLTAGE (RED) AND INPUT                   |            |

| CAPACITOR 2 VOLTAGE (GREEN) WAVEFORMS OF CPC AC-AC BUCK-BOOST                                  |            |

| CONVERTER.                                                                                     | 55         |

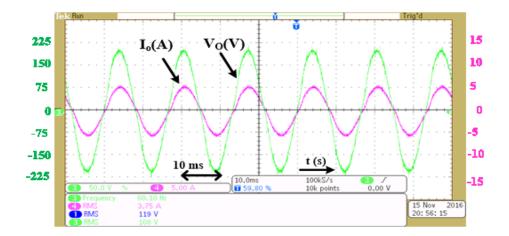

| FIGURE 3-25: OUTPUT VOLTAGE (GREEN) AND OUTPUT CURRENT (PURPLE) WAVEFORM                       |            |

| FOR A DUTY RATIO OF 0.5.                                                                       | 56         |

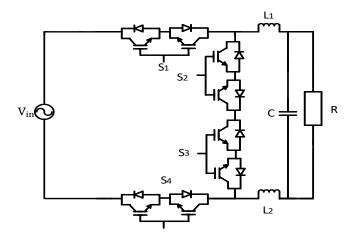

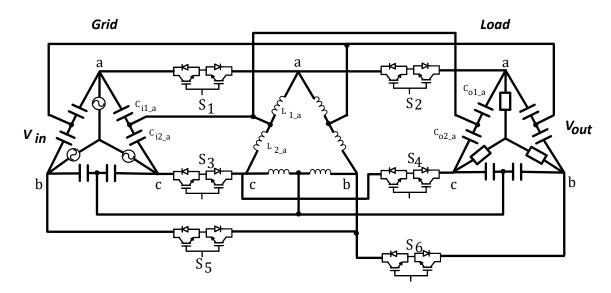

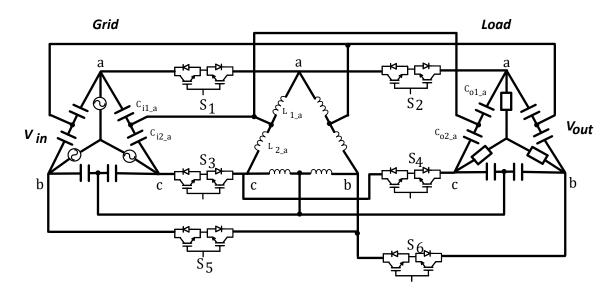

| FIGURE 3-26: SIMPLIFIED CIRCUIT SCHEMATIC OF THE FINAL TOPOLOGY OF 3-Ø CENTER                  | <b>\</b> - |

| POINT-CLAMPED AC-AC BUCK-BOOST CONVERTER.                                                      | 57         |

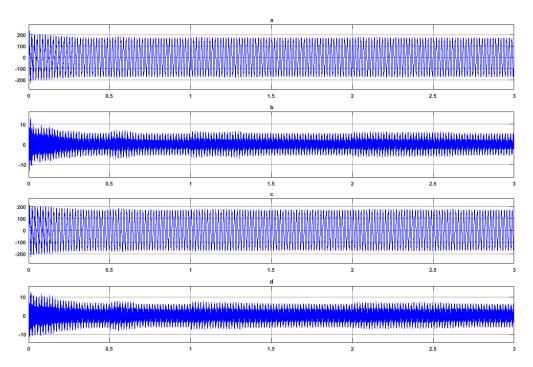

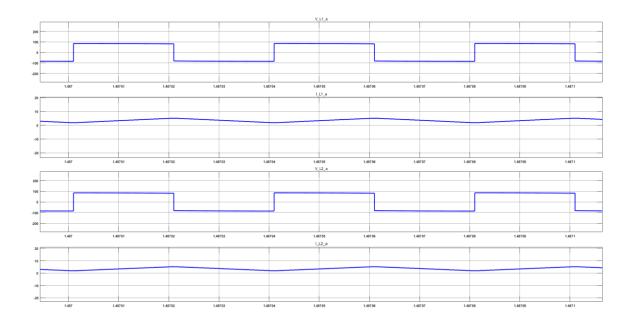

| FIGURE 3-27: (A) VOLTAGE ACROSS INPUT CAPACITOR, $C_{I1\_A}$ , (B) CURRENT THROUGH $C_{I1\_A}$ | _A,        |

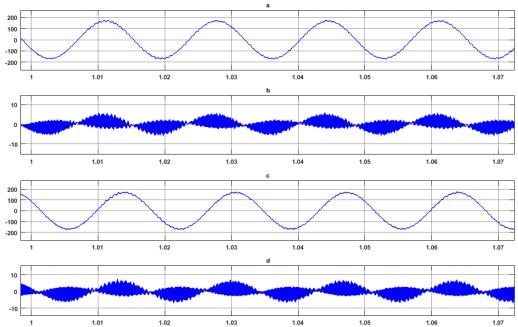

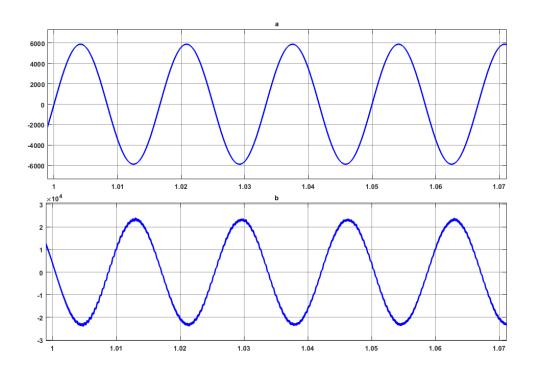

|                                                                                                | 60         |

| FIGURE 3-28: (A) VOLTAGE ACROSS INPUT CAPACITOR, $C_{II\_A}$ , (B) CURRENT THROUGH $C_{II\_B}$ | _A,        |

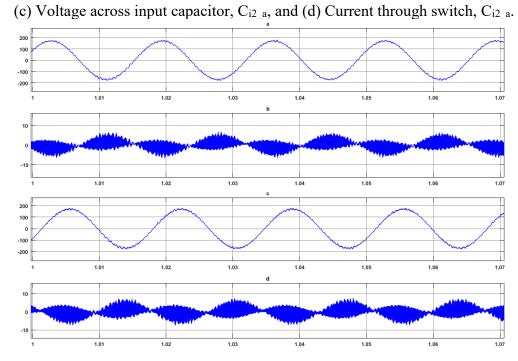

|                                                                                                | 60         |

| FIGURE 3-29: (A) VOLTAGE ACROSS SWITCH, $S_1$ , (B) CURRENT THROUGH SWITCH, $S_1$ , (C)                   |    |

|-----------------------------------------------------------------------------------------------------------|----|

| VOLTAGE ACROSS SWITCH, $S_3$ AND, (D) CURRENT THROUGH SWITCH, $S_3$                                       | 61 |

| FIGURE 3-30: (A) VOLTAGE ACROSS SWITCH, S <sub>1</sub> , (B) CURRENT THROUGH SWITCH, S <sub>1</sub> , (C) |    |

| VOLTAGE ACROSS SWITCH, $S_3$ AND, (D) CURRENT THROUGH SWITCH, $S_3$                                       | 62 |

| FIGURE 3-31: (A) CURRENT THROUGH CAPACITOR, C <sub>Il_A</sub> , (B) CURRENT THROUGH                       |    |

| CAPACITOR, $C_{12\_A}$ ,                                                                                  | 62 |

| FIGURE 3-32: (A) CURRENT THROUGH CAPACITOR, $C_{ll\_A}$ , (B) CURRENT THROUGH                             |    |

| CAPACITOR, $C_{12\_A}$ ,                                                                                  | 63 |

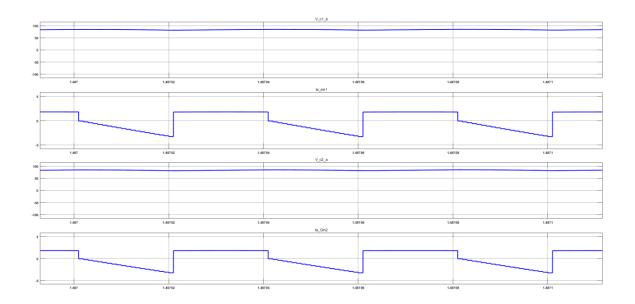

| FIGURE 3-33: (A) VOLTAGE ACROSS OUTPUT CAPACITOR, C <sub>O1_A</sub> , (B) CURRENT THROUGH                 | [  |

| $C_{01\_A}$ ,                                                                                             | 64 |

| FIGURE 3-34: (A) VOLTAGE ACROSS OUTPUT CAPACITOR, C <sub>O1_A</sub> , (B) CURRENT THROUGH                 | [  |

| $C_{O1\_A}$ , (C) VOLTAGE ACROSS OUTPUT CAPACITOR, $C_{O2\_A}$ AND (D) CURRENT THROUGH                    | ЗH |

| SWITCH, C <sub>02_A</sub>                                                                                 | 64 |

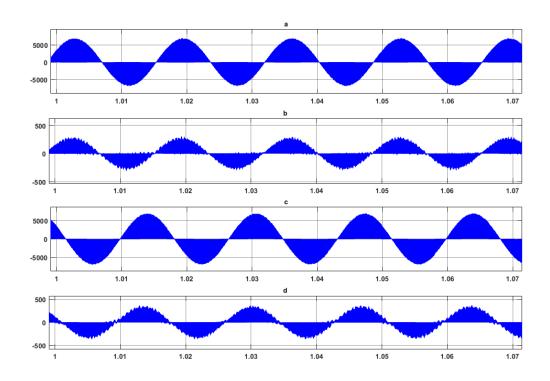

| FIGURE 3-35: (A) VOLTAGE ACROSS INDUCTOR, $L_{l\_A}$ , (B) CURRENT THROUGH $L_{l\_A}$ , (C)               |    |

| VOLTAGE ACROSS INDUCTOR, $L_{2\_A}$ AND, (D) CURRENT THROUGH $L_{2\_A}$ .                                 | 65 |

| FIGURE 3-36: (A) VOLTAGE ACROSS INDUCTOR, $L_{1\_A}$ , (B) CURRENT THROUGH $L_{1\_A}$ , (C)               |    |

| VOLTAGE ACROSS INDUCTOR, $L_{2\_A}$ AND, (D) CURRENT THROUGH $L_{2\_A}$ .                                 | 65 |

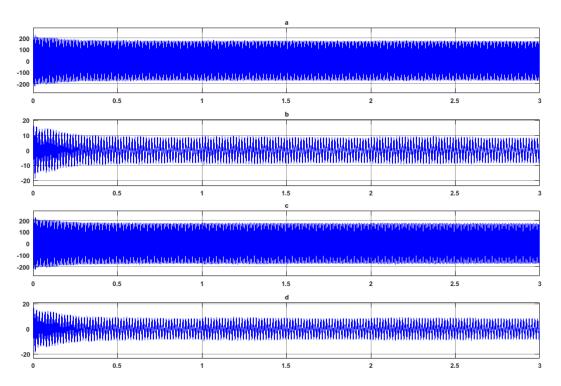

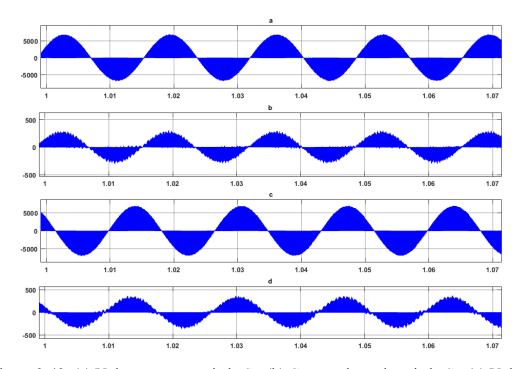

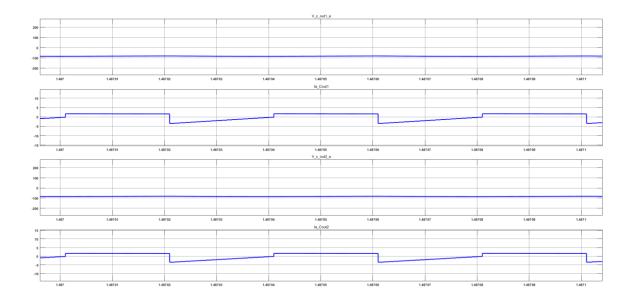

| FIGURE 3-37: (A) INPUT VOLTAGE ACROSS PHASE AB, V <sub>INAB</sub> , (B) INPUT CURRENT THROU               | GH |

| PHASE A, $I_{\text{INA}}$ , (C) INPUT VOLTAGE ACROSS PHASE BC, $V_{\text{INBC}}$ , AND (D) INPUT CURRE    | NT |

| THROUGH PHASE B, $I_{INB.}$                                                                               | 67 |

| FIGURE 3-38: (A) INPUT VOLTAGE ACROSS PHASE AB, $V_{INAB}$ , (B) INPUT CURRENT THROU                      | GH |

| PHASE A, $I_{\text{INA}}$ , (C) INPUT VOLTAGE ACROSS PHASE BC, $V_{\text{INBC}}$ , AND (D) INPUT CURRE    | NT |

| THROUGH PHASE B, $I_{INB.}$                                                                               | 67 |

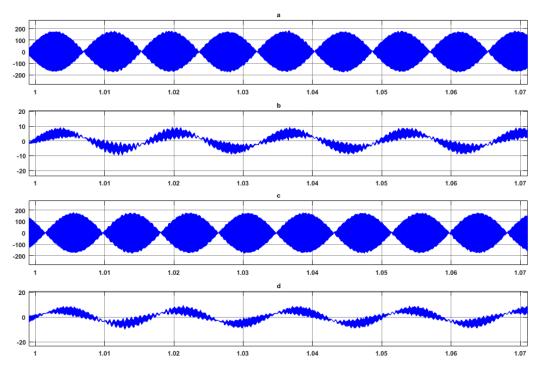

| FIGURE 3-39: (A) OUTPUT VOLTAGE ACROSS PHASE AB, V <sub>OUTAB</sub> , (B) OUTPUT CURRENT                  |    |

| THROUGH PHASE A, $I_{OUTA}$ , (C) OUTPUT VOLTAGE ACROSS PHASE BC, $V_{OUTBC}$ , AND, (                    | D) |

| OUTPUT CURRENT THROUGH PHASE B, I <sub>OUTB.</sub>                                                        | 68 |

| FIGURE 3-40: (A) OUTPUT VOLTAGE ACROSS PHASE AB, V <sub>OUTAB</sub> , (B) OUTPUT CURRENT     |     |

|----------------------------------------------------------------------------------------------|-----|

| THROUGH PHASE A, $I_{OUTA}$ , (C) OUTPUT VOLTAGE ACROSS PHASE BC, $V_{OUTBC}$ , AND, (D)     |     |

| OUTPUT CURRENT THROUGH PHASE B, I <sub>OUTB</sub>                                            | 8   |

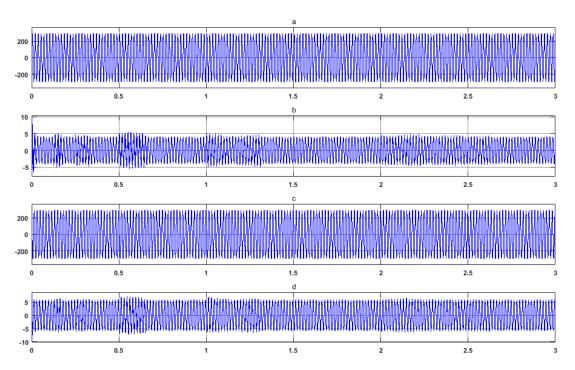

| FIGURE 3-41: (A) INPUT VOLTAGE ACROSS PHASE AB, V <sub>INAB</sub> , (B) INPUT VOLTAGE ACROSS |     |

| PHASE BC, $V_{INBC}$ , (C) INPUT VOLTAGE ACROSS PHASE CA, $V_{INCA}$ , (C) OUTPUT VOLTAGE    | 7   |

| $ACROSS\ PHASE\ AB,\ V_{OUTAB},\ (D)\ OUTPUT\ VOLTAGE\ ACROSS\ PHASE\ BC,\ V_{OUTBC},\ (E)$  |     |

| OUTPUT VOLTAGE ACROSS PHASE CA, V <sub>OUTCA</sub> .                                         | ç   |

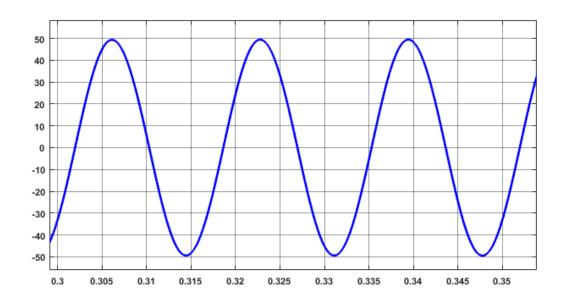

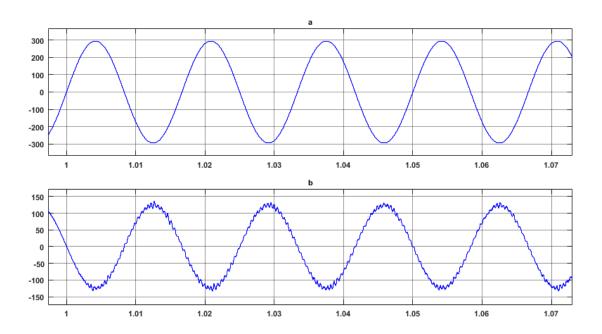

| FIGURE 3-42: (A) INPUT SOURCE VOLTAGE, AND (B) OUTPUT VOLTAGE, FOR A DUTY RATIO              | 0   |

| OF 0.3.                                                                                      | (   |

| FIGURE 3-43: (A) INPUT SOURCE VOLTAGE, AND (B) OUTPUT VOLTAGE, FOR A DUTY RATIO              | 0   |

| OF 0.5.                                                                                      | 1   |

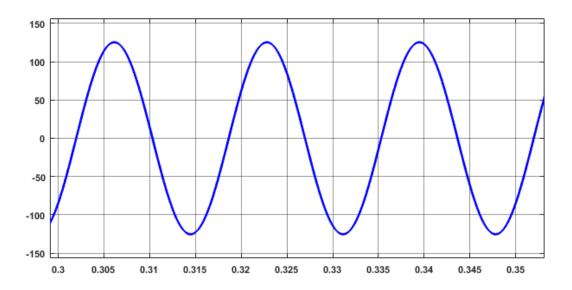

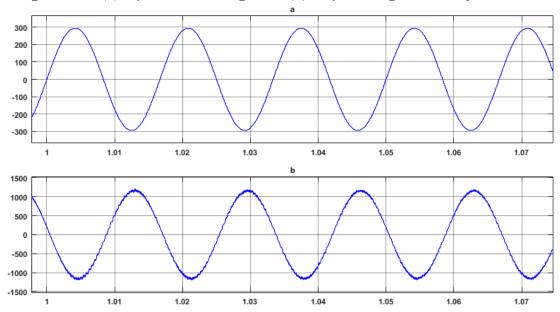

| FIGURE 3-44: (A) INPUT SOURCE VOLTAGE, AND (B) OUTPUT VOLTAGE, FOR A DUTY RATIO              | 0   |

| OF 0.8.                                                                                      | 1   |

| FIGURE 3-45: (A) INPUT SOURCE VOLTAGE, AND (B) OUTPUT VOLTAGE, FOR A DUTY RATIO              | С   |

| OF 0.3.                                                                                      | 4   |

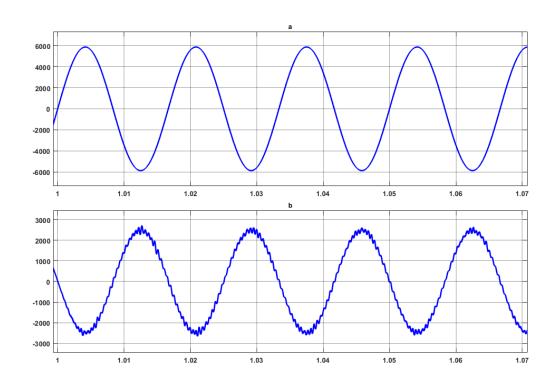

| FIGURE 3-46: (A) INPUT SOURCE VOLTAGE, AND (B) OUTPUT VOLTAGE, FOR A DUTY RATIO              | С   |

| OF 0.5.                                                                                      | 4   |

| FIGURE 3-47: (A) INPUT SOURCE VOLTAGE, AND (B) OUTPUT VOLTAGE, FOR A DUTY RATIO              | 0   |

| OF 0.8.                                                                                      | 5   |

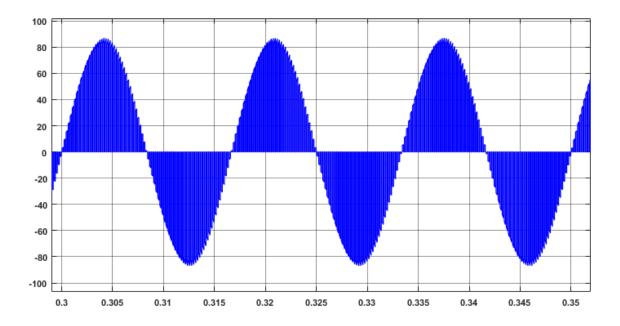

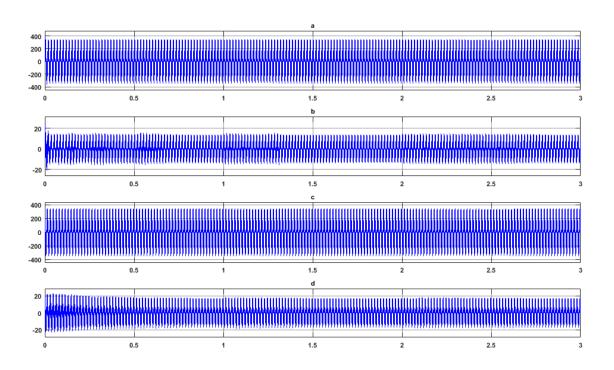

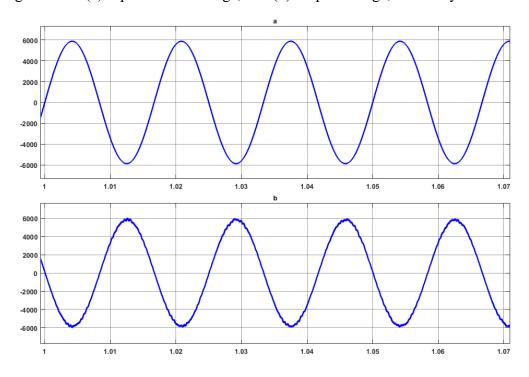

| FIGURE 3-48: (A) VOLTAGE ACROSS SWITCH, $S_1$ , (B) CURRENT THROUGH SWITCH, $S_1$ , (C)      |     |

| VOLTAGE ACROSS SWITCH, S <sub>3</sub> AND, (D) CURRENT THROUGH SWITCH, S <sub>3</sub>        | 6   |

| FIGURE 3-49: (A) VOLTAGE ACROSS SWITCH, $S_2$ , (B) CURRENT THROUGH SWITCH, $S_2$ , (C)      |     |

| VOLTAGE ACROSS SWITCH, S <sub>4</sub> AND, (D) CURRENT THROUGH SWITCH, S <sub>4</sub>        | 6   |

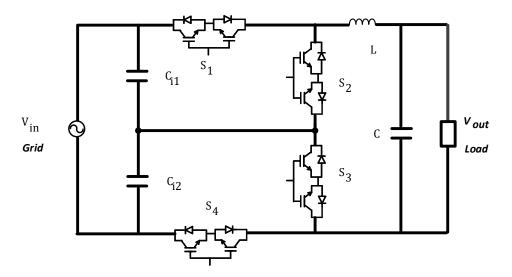

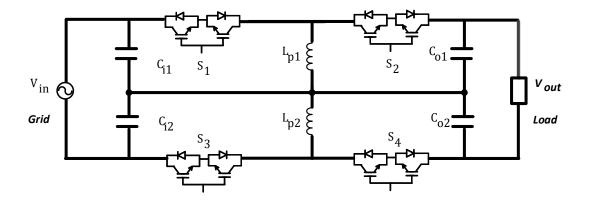

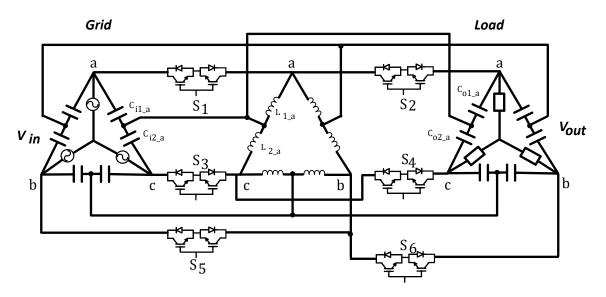

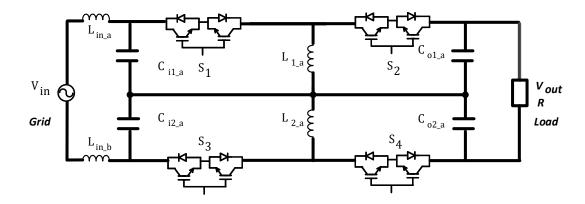

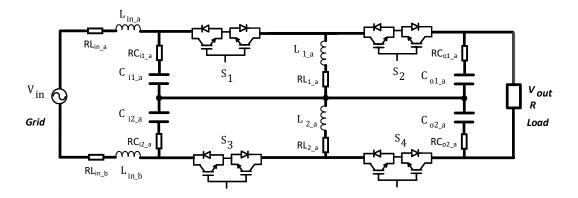

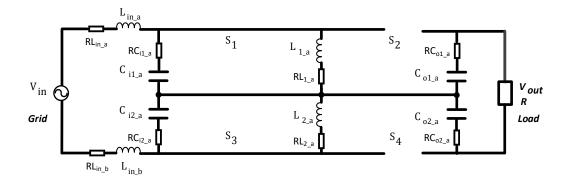

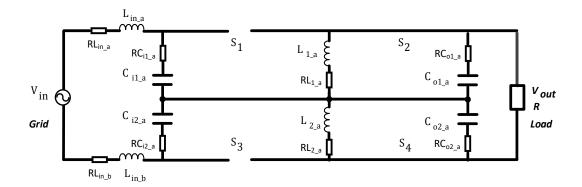

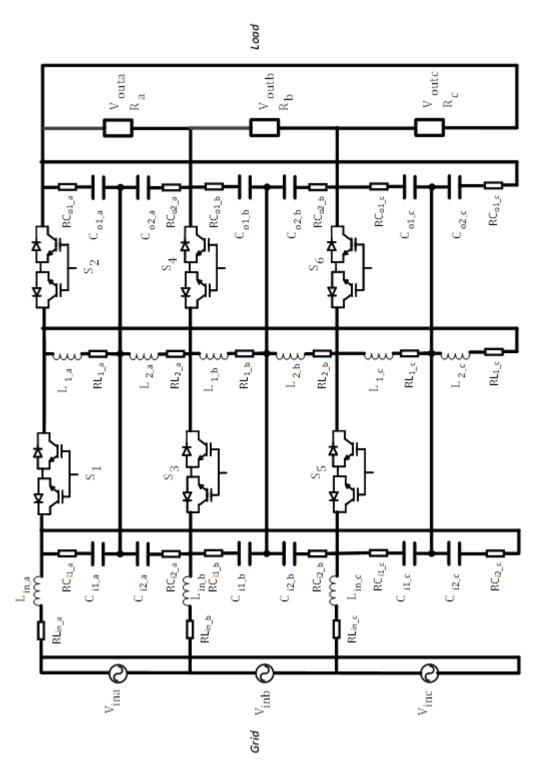

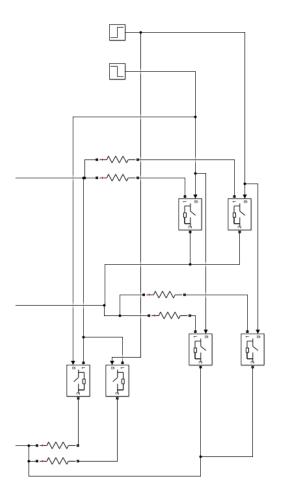

| FIGURE 4-1: SIMPLIFIED CIRCUIT SCHEMATIC OF THE 3-Ø CPC PLC.                                 | 8   |

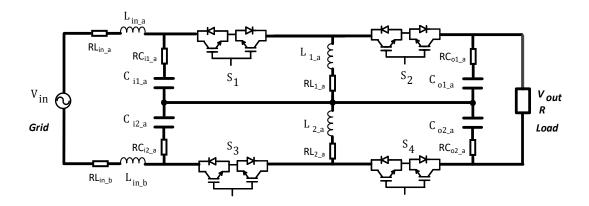

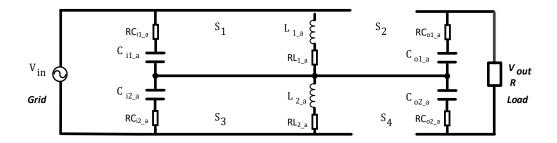

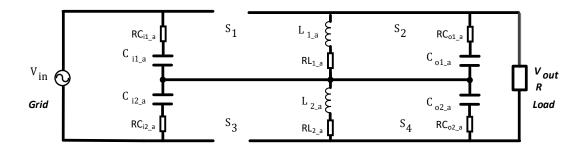

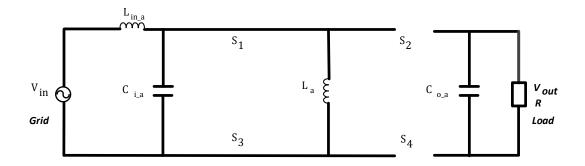

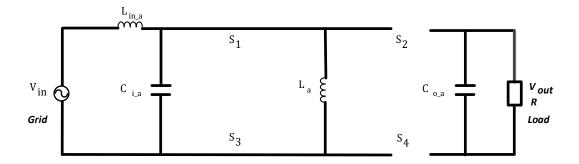

| FIGURE 4-2: SINGLE PHASE EQUIVALENT CIRCUIT SCHEMATIC OF THE CPC PLC.                        | ç   |

| FIGURE 4-3: SCREENSHOT OF SELECTED IGBT DATASHEET FROM DIGIKEY. 8                            | . 1 |

| FIGURE 4-4: DETAILED SINGLE-PHASE EQUIVALENT CIRCUIT SCHEMATIC OF THE CPC PLO                | ٦,  |

| FIGURE 4-5: DETAILED SINGLE-PHASE EQUIVALENT CIRCUIT SCHEMATIC OF THE CPC PI                             | LC                    |

|----------------------------------------------------------------------------------------------------------|-----------------------|

| DURING SWITCHING STATE 1 (S <sub>1</sub> S <sub>3</sub> CLOSED & S <sub>2</sub> S <sub>4</sub> OPEN).    | 83                    |

| FIGURE 4-6: DETAILED SINGLE-PHASE EQUIVALENT CIRCUIT SCHEMATIC OF THE CPC PI                             | ĹC                    |

| DURING SWITCHING STATE 1 (S <sub>1</sub> S <sub>3</sub> OPEN & S <sub>2</sub> S <sub>4</sub> CLOSED).    | 84                    |

| FIGURE 4-7: INDUCTOR VOLTAGE, $V_{L1\_A}$ AND $V_{L2\_A}$ AND THEIR CORRESPONDING INDUCTOR               | OR                    |

| CURRENTS, $I_{L1\_A}$ AND $I_{L2\_A}$                                                                    | 85                    |

| FIGURE 4-8: INPUT CAPACITOR VOLTAGE, $V_{\text{CII\_A}}$ AND $V_{\text{CI2\_A}}$ AND THEIR CORRESPONDING | ŕ                     |

| CAPACITOR CURRENTS, $I_{CII\_A}$ AND $I_{CI2\_A}$                                                        | 87                    |

| FIGURE 4-9: OUTPUT CAPACITOR VOLTAGE, $V_{\text{CO1\_A}}$ AND $V_{\text{CO2\_A}}$ AND THEIR              |                       |

| CORRESPONDING CAPACITOR CURRENTS, $I_{CO1\_A}$ AND $I_{CO2\_A}$                                          | 88                    |

| FIGURE 5-1: SIMPLIFIED CIRCUIT SCHEMATIC OF CPC PLC.                                                     | 93                    |

| FIGURE 5-2: DETAILED SINGLE-PHASE EQUIVALENT CIRCUIT SCHEMATIC OF THE CENTER                             | ∃R-                   |

| POINT-CLAMPED AC-AC BUCK-BOOST CONVERTER                                                                 | 94                    |

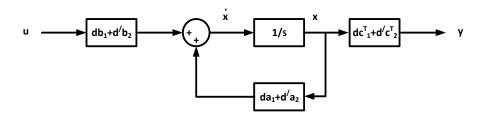

| FIGURE 5-3: SIMPLIFIED BLOCK DIAGRAM REPRESENTATION OF STATE SPACE AVERAGE                               | ΞD                    |

| CONVERTER EQUATION.                                                                                      | 96                    |

| FIGURE 5-4: DETAILED SINGLE-PHASE EQUIVALENT CIRCUIT SCHEMATIC OF THE CENTER                             | ∃R-                   |

| POINT-CLAMPED AC-AC BUCK-BOOST CONVERTER DURING SWITCHING STATE 1 (S                                     | $S_1$                 |

| S <sub>3</sub> CLOSED & S <sub>2</sub> S <sub>4</sub> OPEN).                                             | 96                    |

| FIGURE 5-5: SIMPLIFIED SINGLE-PHASE EQUIVALENT CIRCUIT SCHEMATIC OF THE                                  |                       |

| CENTER-POINT-CLAMPED AC-AC BUCK-BOOST CONVERTER DURING SWITCHING                                         |                       |

| STATE 1 (S <sub>1</sub> S <sub>3</sub> CLOSED & S <sub>2</sub> S <sub>4</sub> OPEN).                     | 97                    |

| FIGURE 5-6: DETAILED SINGLE-PHASE EQUIVALENT CIRCUIT SCHEMATIC OF THE CENTER                             | ∃R-                   |

| POINT-CLAMPED AC-AC BUCK-BOOST CONVERTER DURING SWITCHING STATE 2 (S                                     | <b>5</b> <sub>1</sub> |

| S <sub>3</sub> OPEN & S <sub>2</sub> S <sub>4</sub> CLOSED).                                             | 100                   |

| FIGURE 5-7: SIMPLIFIED SINGLE-PHASE EQUIVALENT CIRCUIT SCHEMATIC OF THE                                  |                       |

| CENTER-POINT-CLAMPED AC-AC BUCK-BOOST CONVERTER DURING SWITCHING                                         |                       |

| STATE 1 (S <sub>1</sub> S <sub>3</sub> CLOSED & S <sub>2</sub> S <sub>4</sub> OPEN).                     | 100                   |

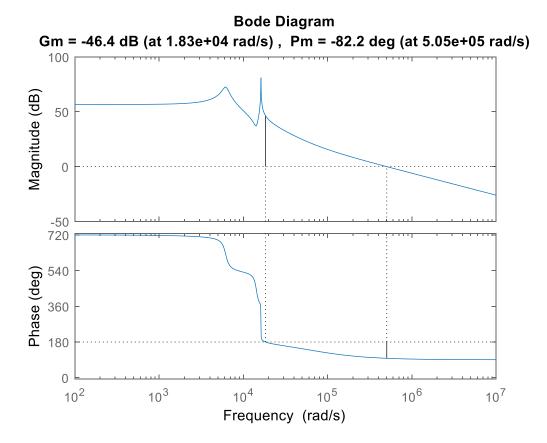

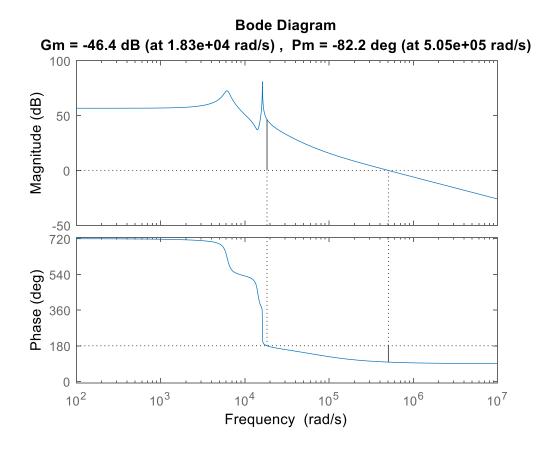

| FIGURE 5-8: BODE MAGNITUDE AND PHASE PLOT FOR OUTPUT TO DUTY RATIO TRANS                           | SFER                |

|----------------------------------------------------------------------------------------------------|---------------------|

| FUNCTION, GVOD.                                                                                    | 110                 |

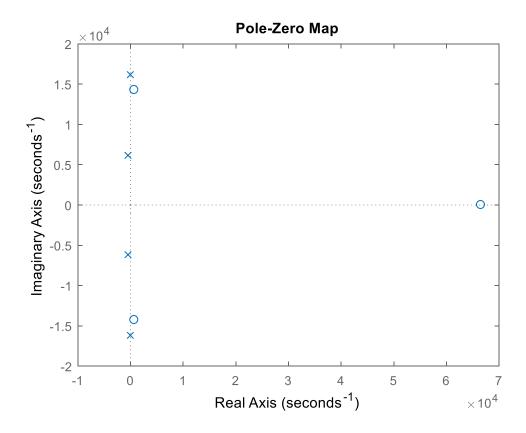

| FIGURE 5-9: POLE-ZERO MAP FOR OUTPUT TO DUTY RATIO TRANSFER FUNCTION, GVOI                         | )                   |

| (POLES ARE MARKED AS 'X' AND ZEROS ARE MARKED AS 'O').                                             | 111                 |

| FIGURE 5-10: BODE MAGNITUDE AND PHASE PLOT FOR UNCOMPENSATED OUTPUT TO                             |                     |

| DUTY RATIO TRANSFER FUNCTION, GVOD                                                                 | 114                 |

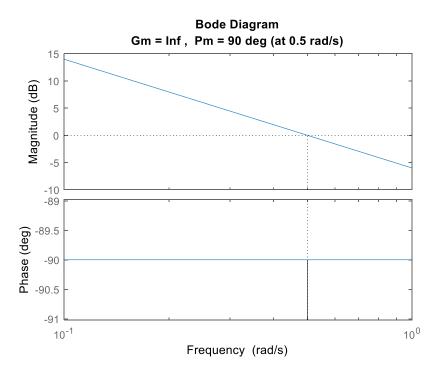

| FIGURE 5-11: BODE MAGNITUDE AND PHASE PLOTS FOR COMPENSATOR TRANSFER                               |                     |

| FUNCTION, HCOMP                                                                                    | 115                 |

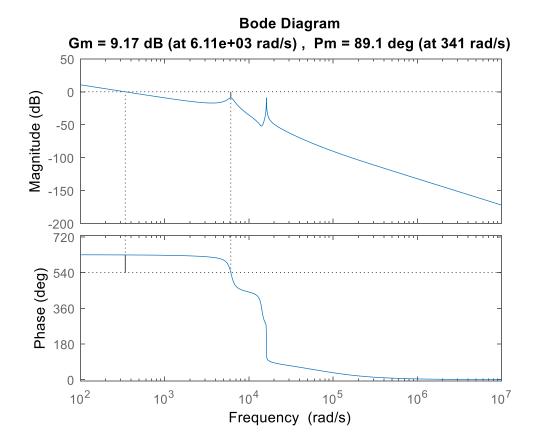

| FIGURE 5-12: BODE MAGNITUDE AND PHASE PLOTS FOR COMPENSATED TRANSFER                               |                     |

| FUNCTION, GVODOLTF*HCOMP                                                                           | 116                 |

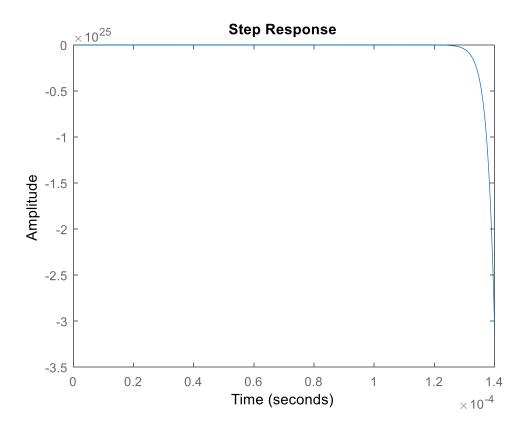

| FIGURE 5-13: STEP RESPONSE PLOT FOR UNCOMPENSATED OUTPUT TO DUTY RATIO                             |                     |

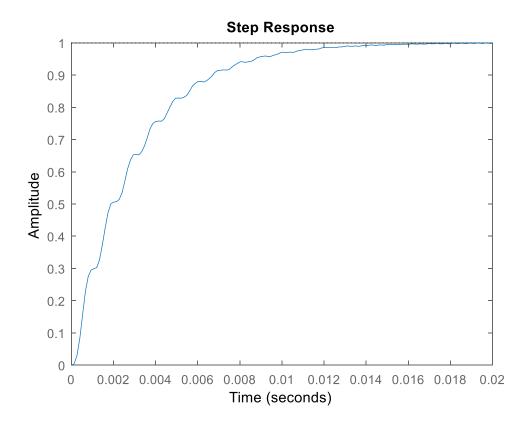

| TRANSFER FUNCTION, GVOD                                                                            | 117                 |

| FIGURE 5-14: STEP RESPONSE PLOT OF THE COMPENSATED TRANSFER FUNCTION,                              |                     |

| GVODOLTF*HCOMP                                                                                     | 118                 |

| FIGURE 6-1: DETAILED CIRCUIT SCHEMATIC OF THE 3-Ø CPC PLC.                                         | 121                 |

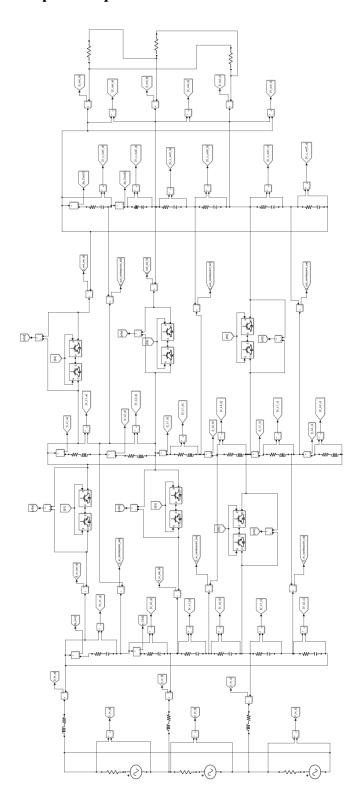

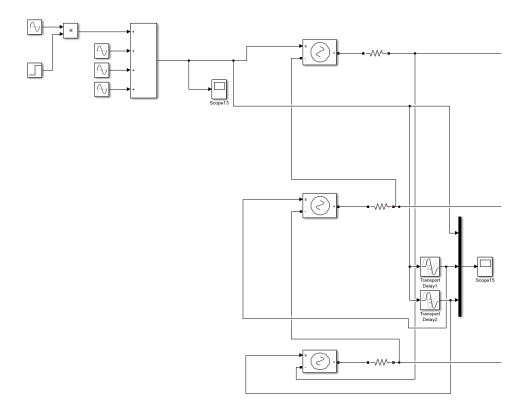

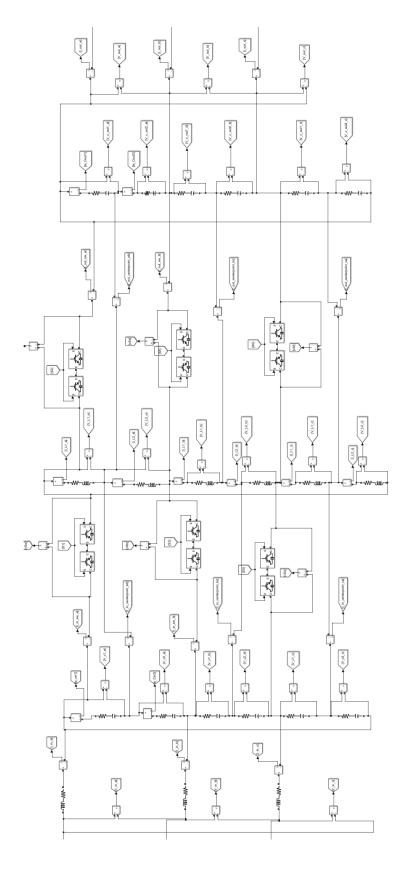

| FIGURE 6-2: SNAPSHOT OF MATLAB-SIMULINK MODEL OF 3-Ø CPC PLC                                       | 123                 |

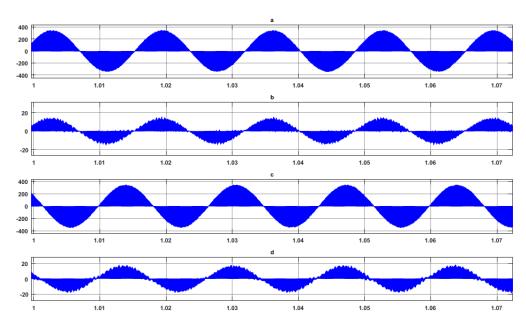

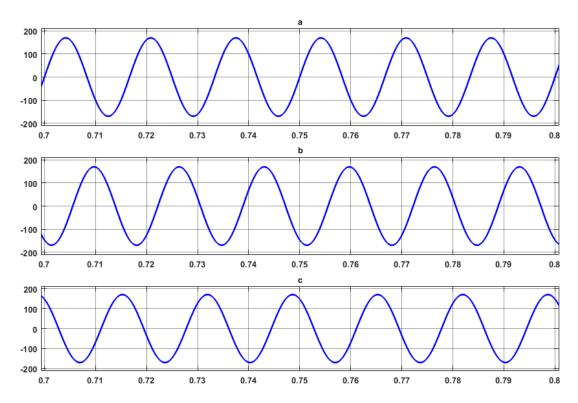

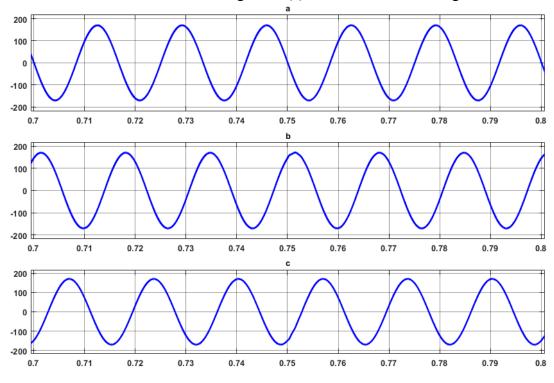

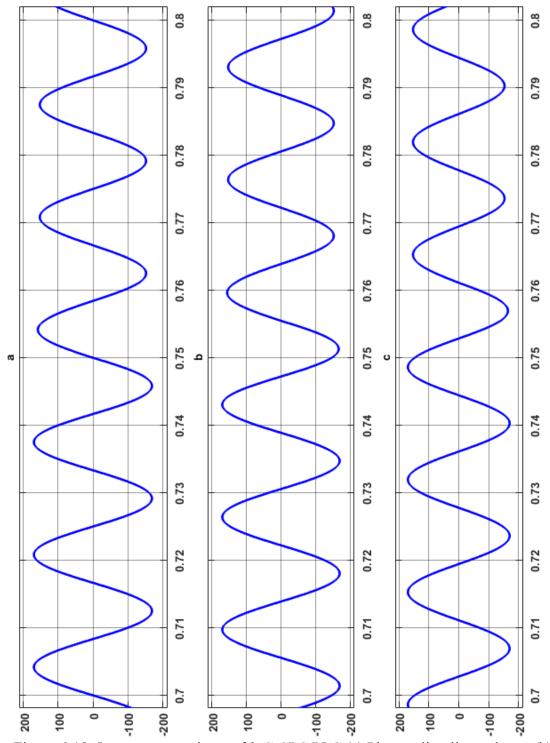

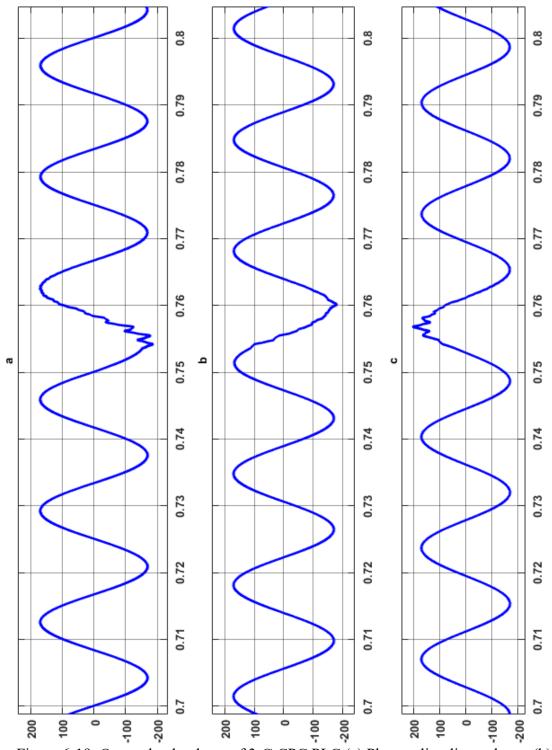

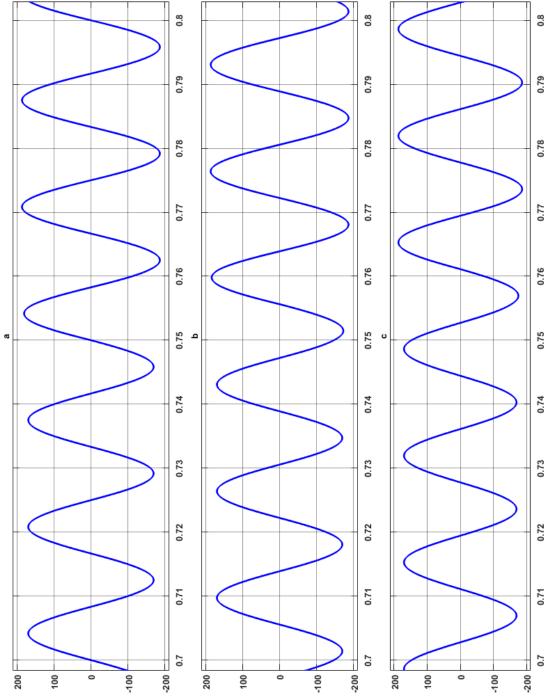

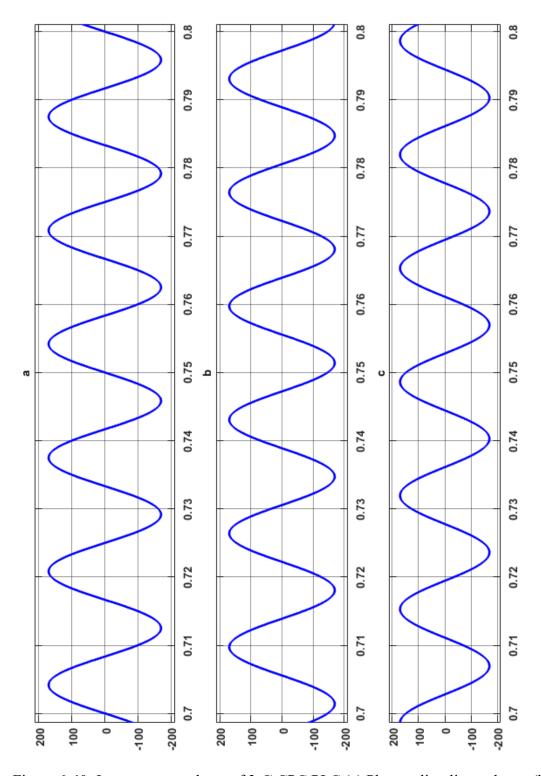

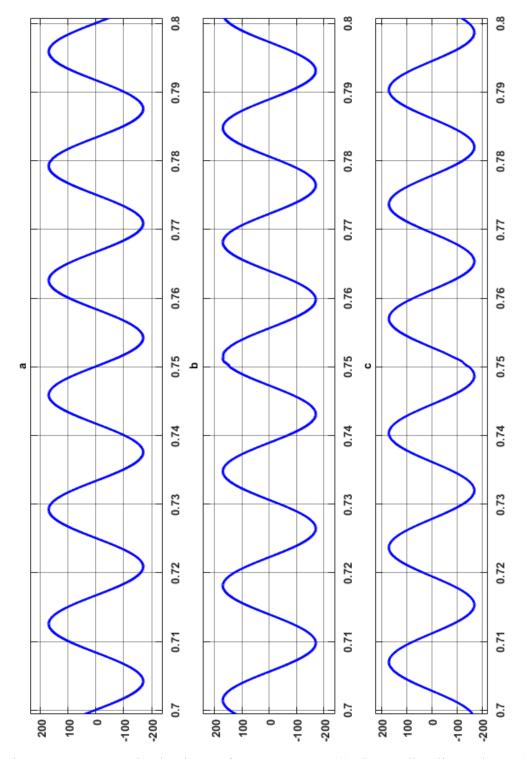

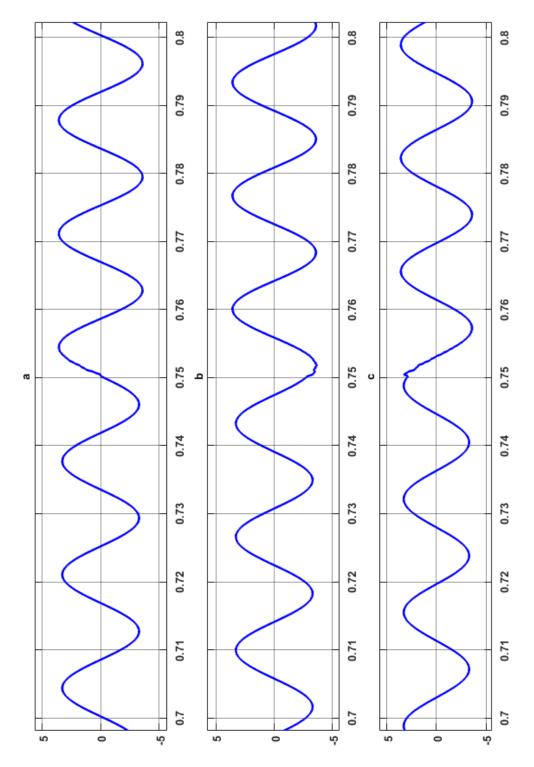

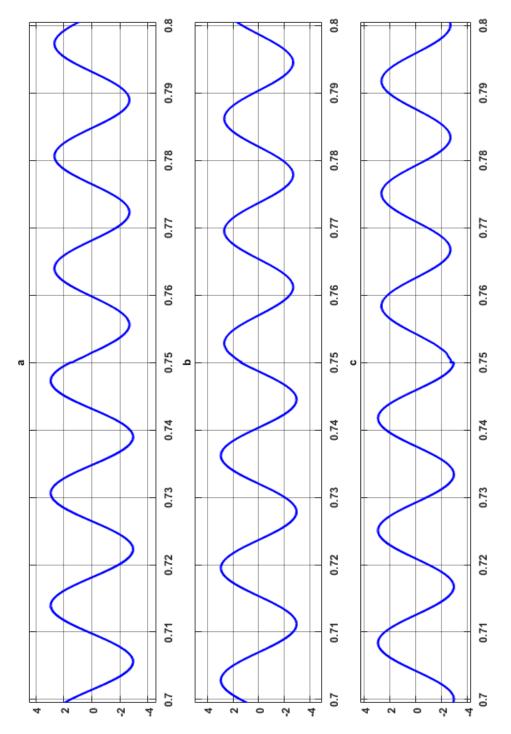

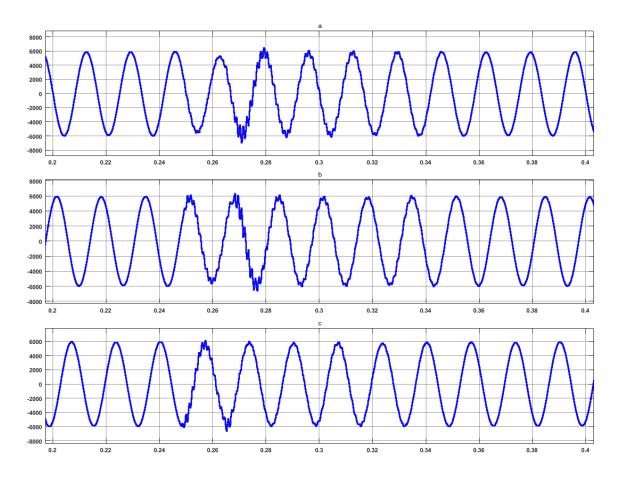

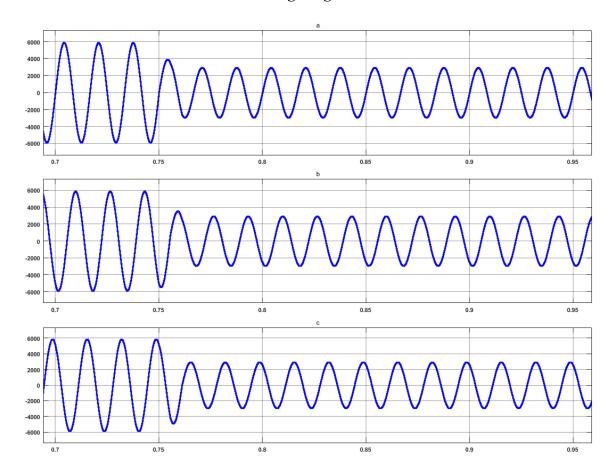

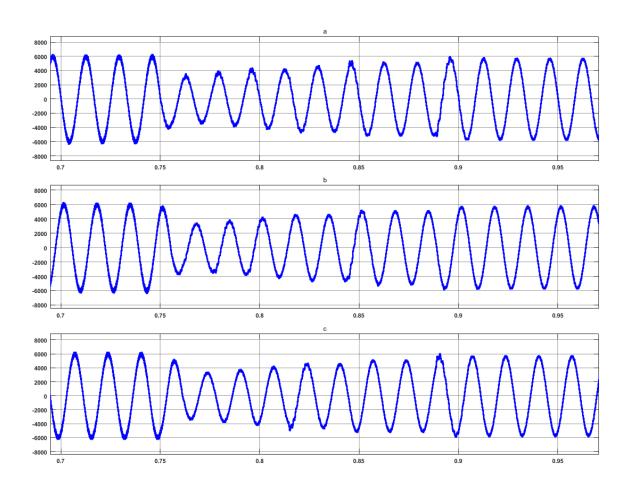

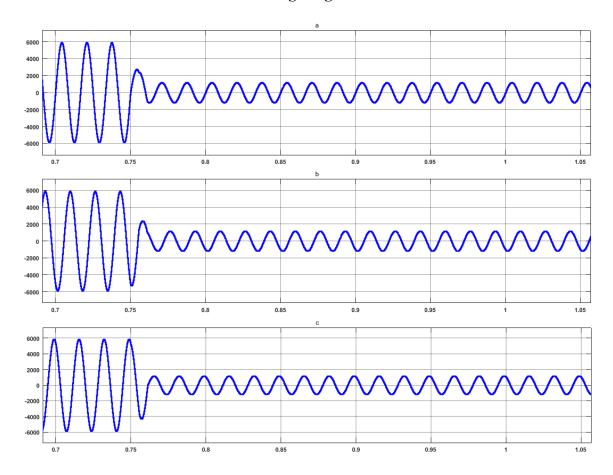

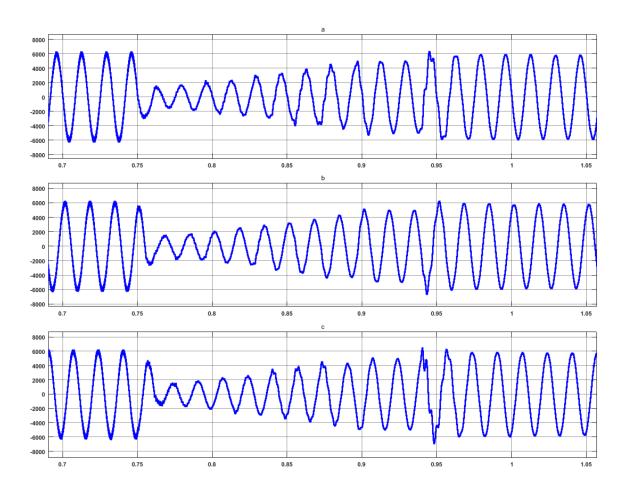

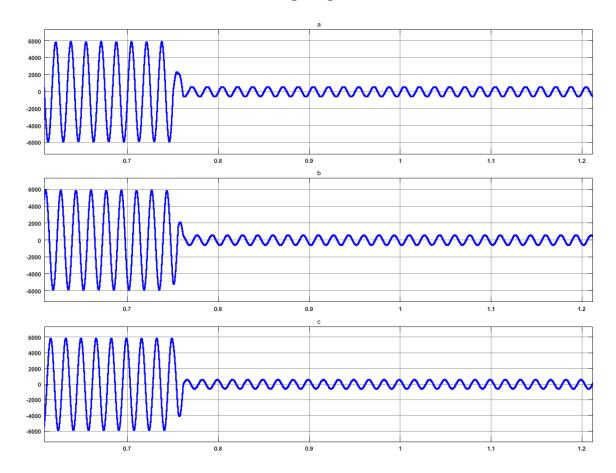

| FIGURE 6-3: INPUT SOURCE VOLTAGE OF 3-Ø CPC PLC (A) PHASE-A LINE-LINE VOLTAGE                      | E,                  |

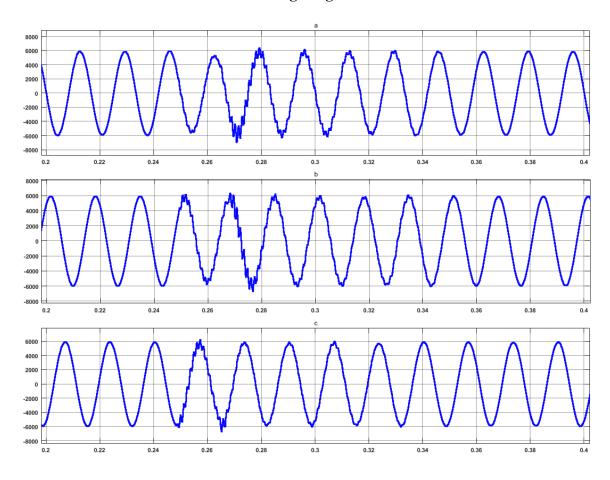

| (B) PHASE-B LINE-LINE VOLTAGE, AND (C) PHASE-C LINE-LINE VOLTAGE.                                  | 125                 |

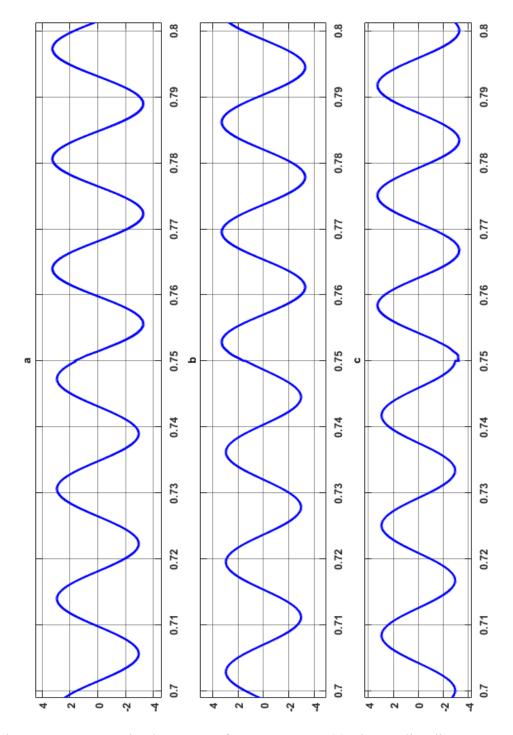

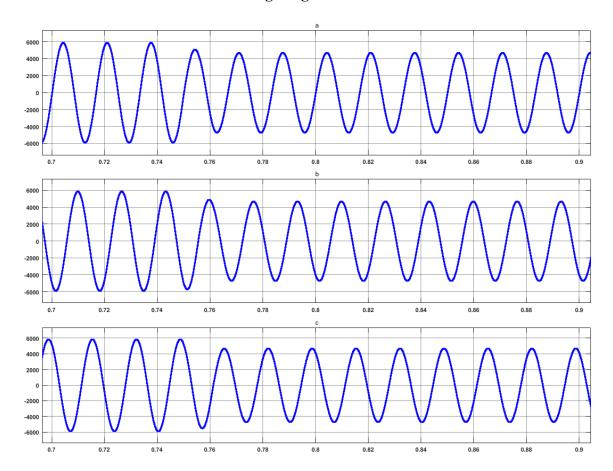

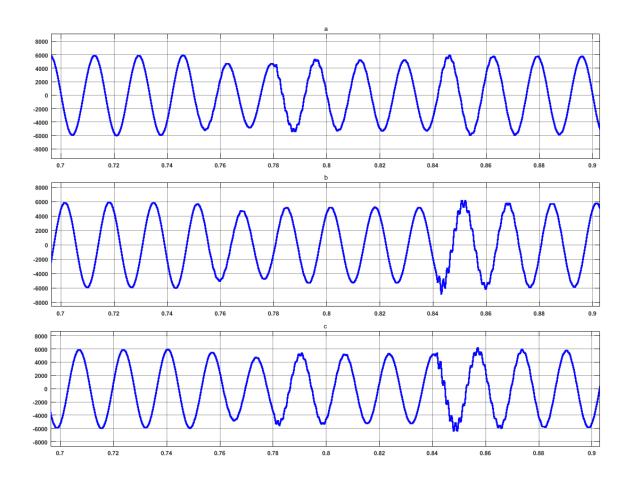

| FIGURE 6-4: OUTPUT LOAD VOLTAGE OF 3-Ø CPC PLC (A) PHASE-A LINE-LINE VOLTAGE                       | Ε,                  |

| (B) PHASE-B LINE-LINE VOLTAGE, AND (C) PHASE-C LINE-LINE VOLTAGE.                                  | 125                 |

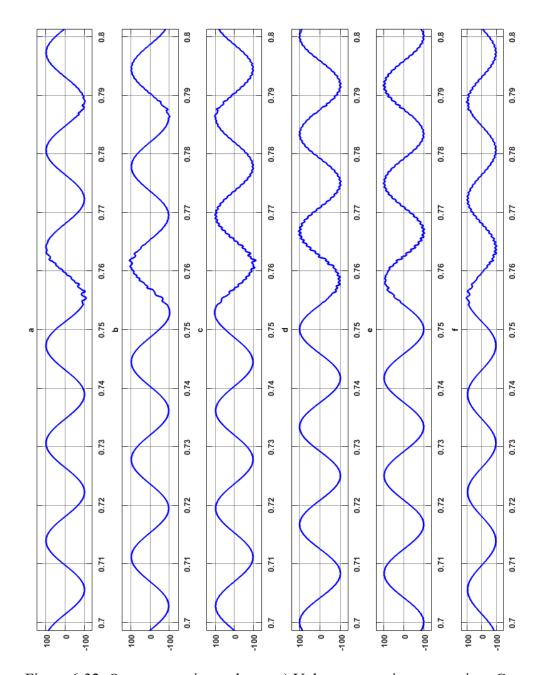

| FIGURE 6-5: INPUT CAPACITOR VOLTAGES (A) VOLTAGE ACROSS INPUT CAPACITOR, C                         | Il_A,               |

| (B) VOLTAGE ACROSS INPUT CAPACITOR, $C_{12\_A}$ , (C) VOLTAGE ACROSS INPUT                         |                     |

| CAPACITOR, $C_{I1\_B}$ , (D) VOLTAGE ACROSS INPUT CAPACITOR, $C_{I2\_B}$ , (C) VOLTAGE             |                     |

| ACROSS INPUT CAPACITOR, $C_{II\_C}$ , AND (D) VOLTAGE ACROSS INPUT CAPACITOR,                      | C <sub>12_C</sub> . |

|                                                                                                    | 126                 |

| FIGURE 6-6: OUTPUT CAPACITOR VOLTAGES A) VOLTAGE ACROSS INPUT CAPACITOR,                           |                     |

| $C_{01\_A}$ , (B) VOLTAGE ACROSS INPUT CAPACITOR, $C_{02\_A}$ , (C) VOLTAGE ACROSS INPU            | T                   |

| CAPACITOR, C <sub>01_B</sub> , (D) VOLTAGE ACROSS INPUT CAPACITOR, C <sub>02_B</sub> , (C) VOLTAGE |                     |

| ACROSS INPUT CAPACITOR, $C_{O1\_C}$ , AND (D) VOLTAGE ACROSS INPUT CAPACITOR,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| $C_{02\_C}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 127    |

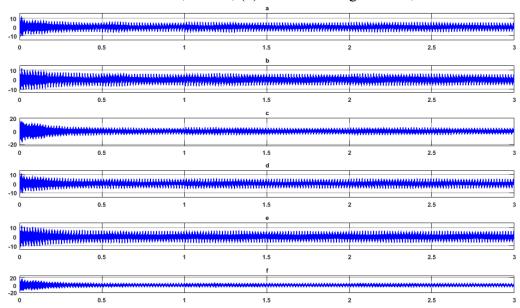

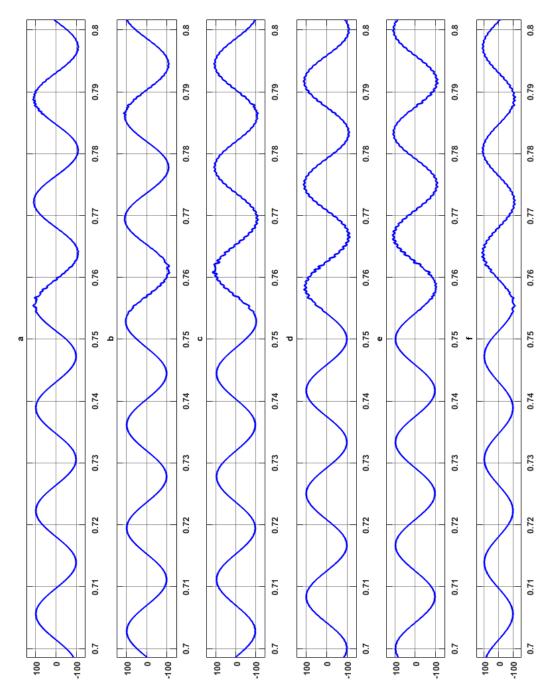

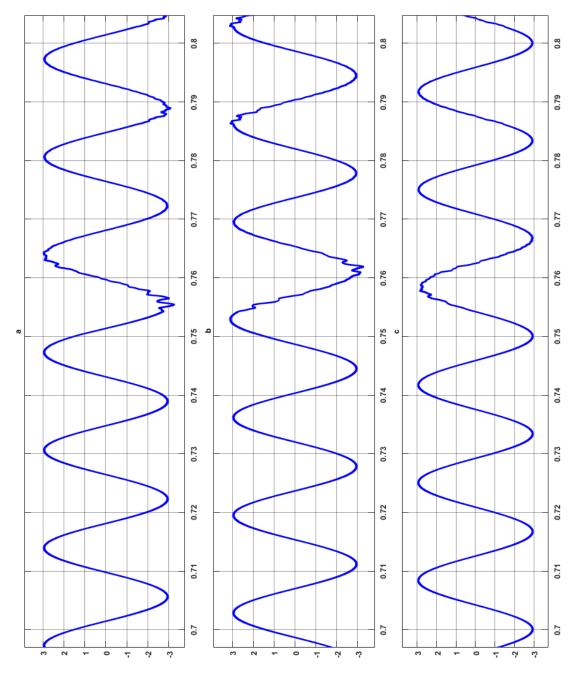

| FIGURE 6-7: BUCK-BOOST INDUCTOR VOLTAGES (A) VOLTAGE ACROSS INDUCTOR, $L_1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _A,    |

| (B) VOLTAGE ACROSS INDUCTOR, $L_{2\_A}$ , (C) VOLTAGE ACROSS INDUCTOR, $L_{1\_B}$ , (D)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| VOLTAGE ACROSS INDUCTOR, $L_{2\_B}$ , (E) VOLTAGE ACROSS INDUCTOR, $L_{1\_C}$ , AND (Fig. 1) AND (Fig. 2) AND (Fig. 3) AND (F | 7)     |

| VOLTAGE ACROSS INDUCTOR, $L_{2\_C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 128    |

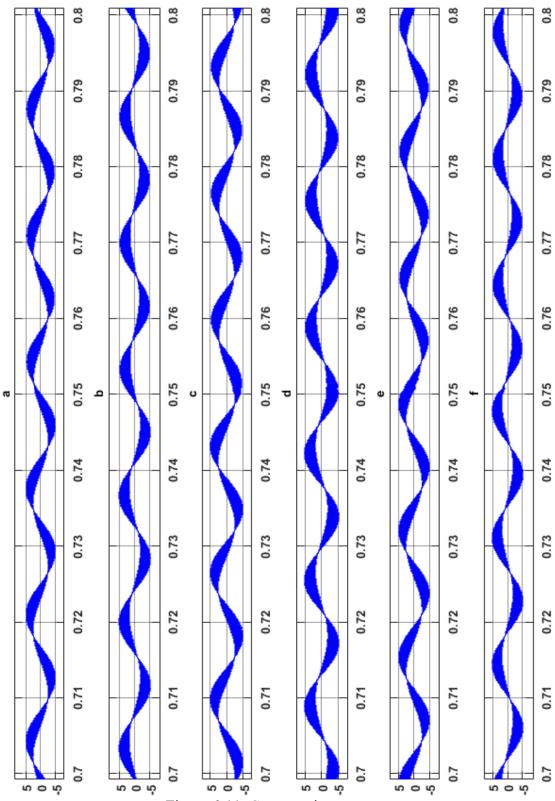

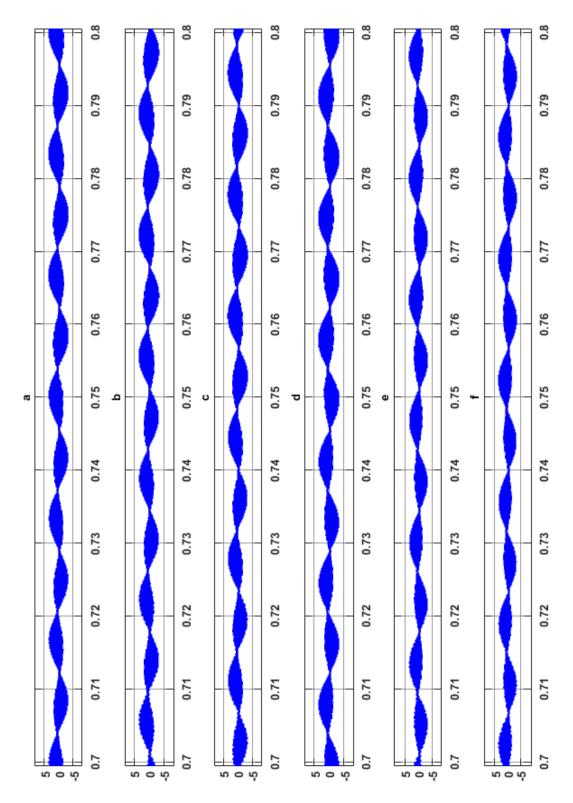

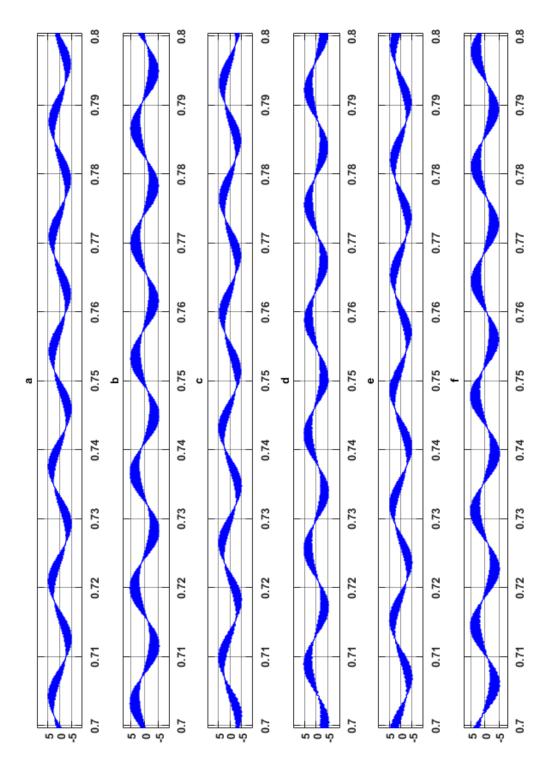

| FIGURE 6-8: BUCK-BOOST INDUCTOR CURRENTS (A) CURRENT ACROSS INDUCTOR, $\rm L_{1\_}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A, (B) |

| CURRENT ACROSS INDUCTOR, $L_{2\_A}$ , (C) CURRENT ACROSS INDUCTOR, $L_{1\_B}$ , (D)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| CURRENT ACROSS INDUCTOR, $L_{2_B}$ , (E) CURRENT ACROSS INDUCTOR, $L_{1_C}$ , AND (Fig. 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ")     |

| CURRENT ACROSS INDUCTOR, $L_{2\_C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 129    |

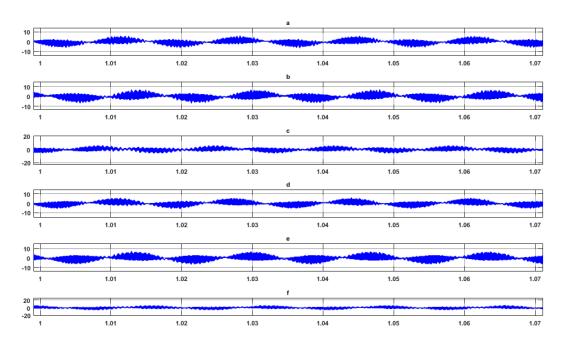

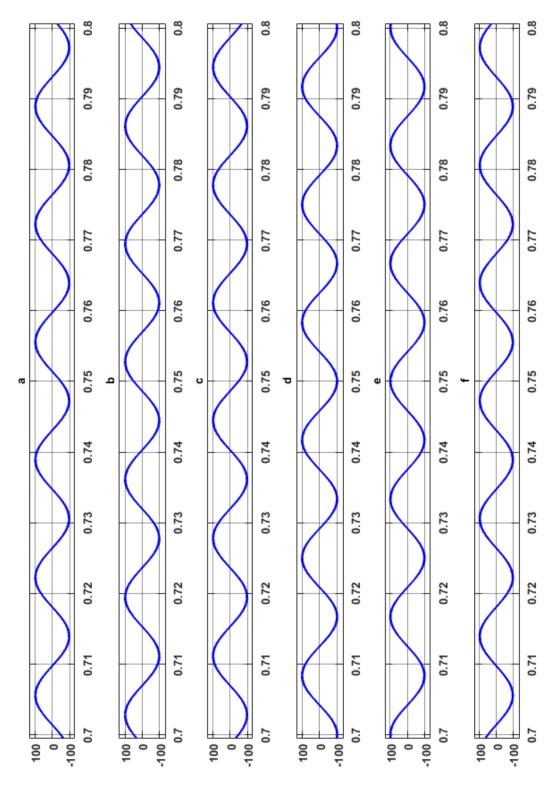

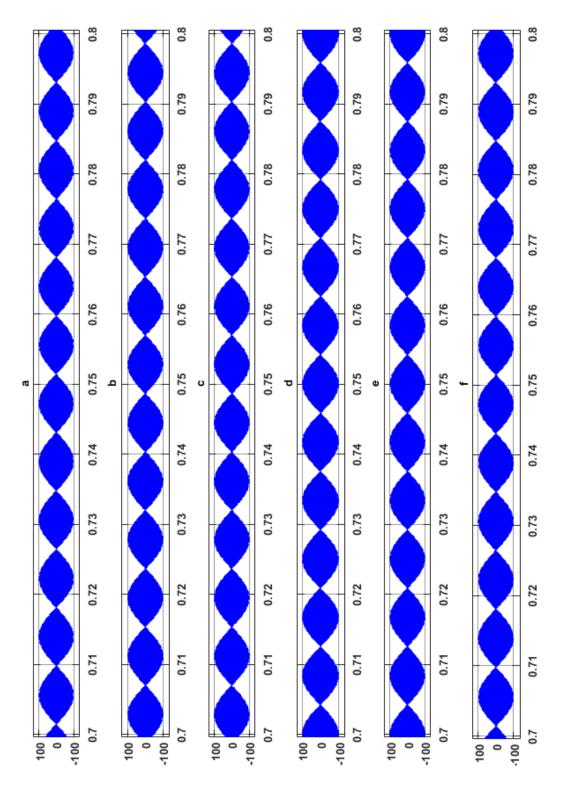

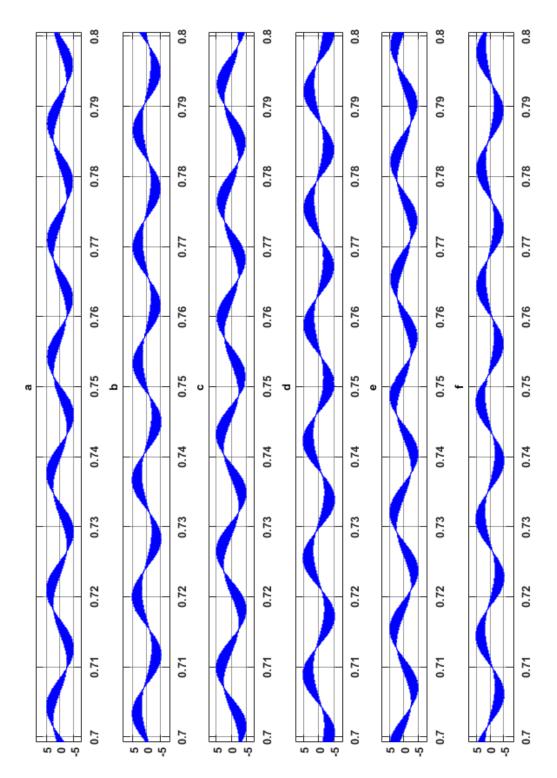

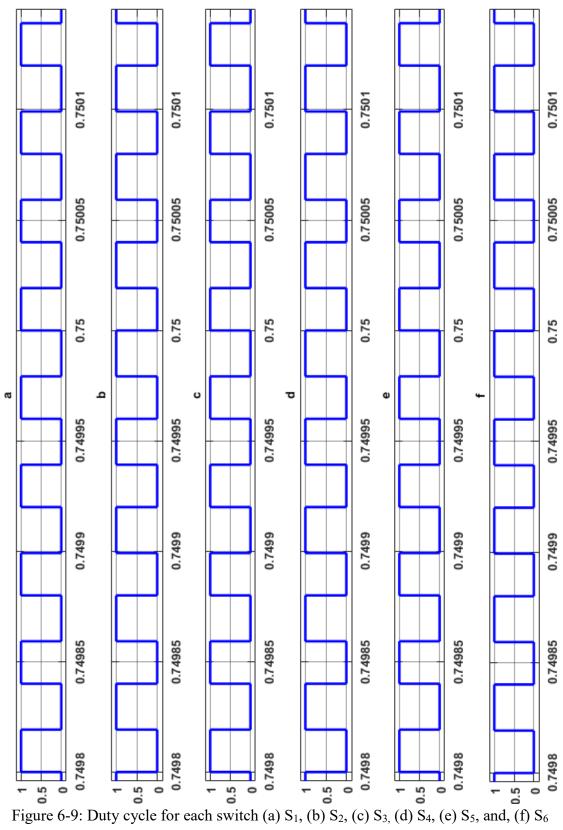

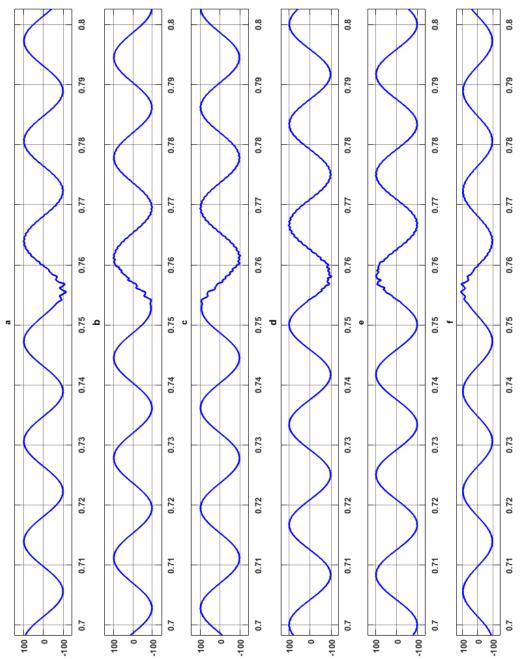

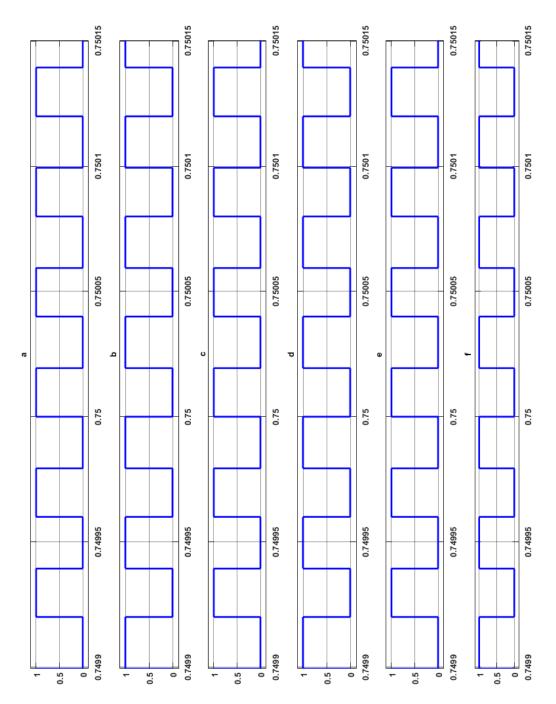

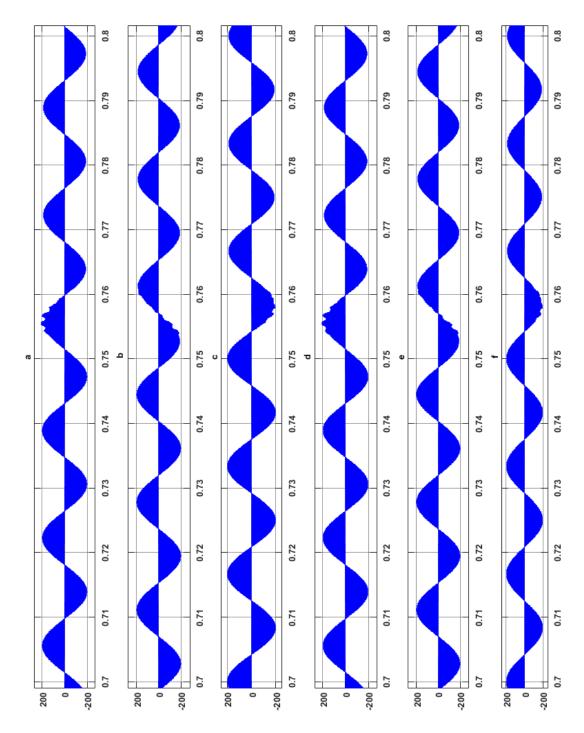

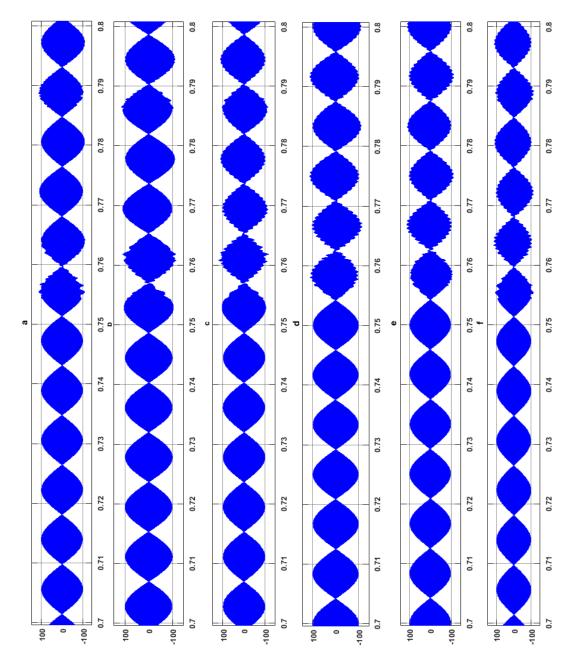

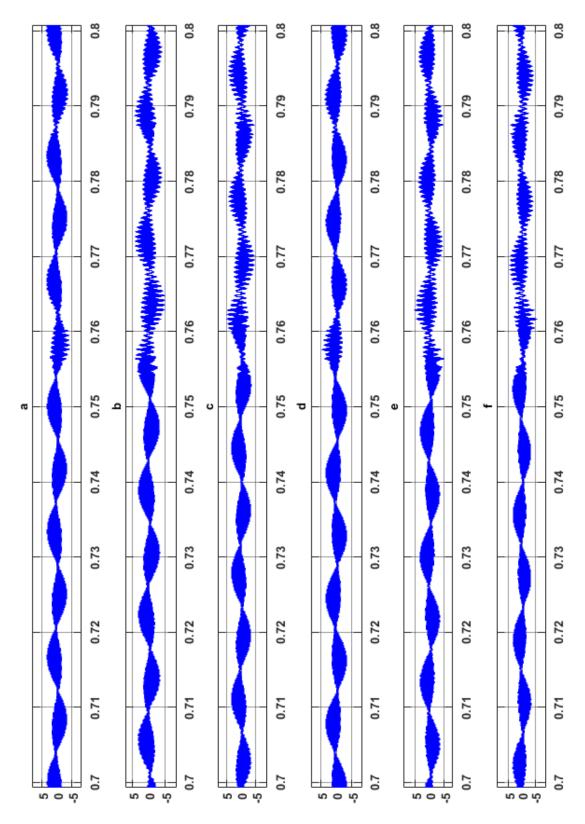

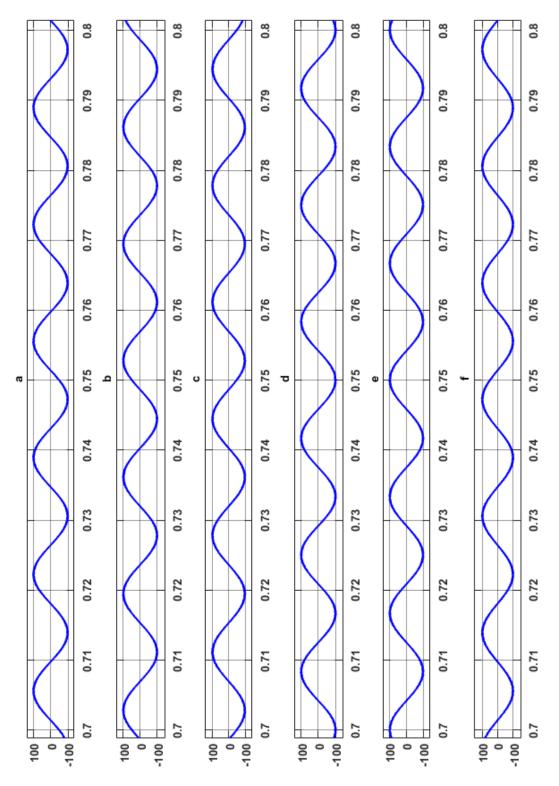

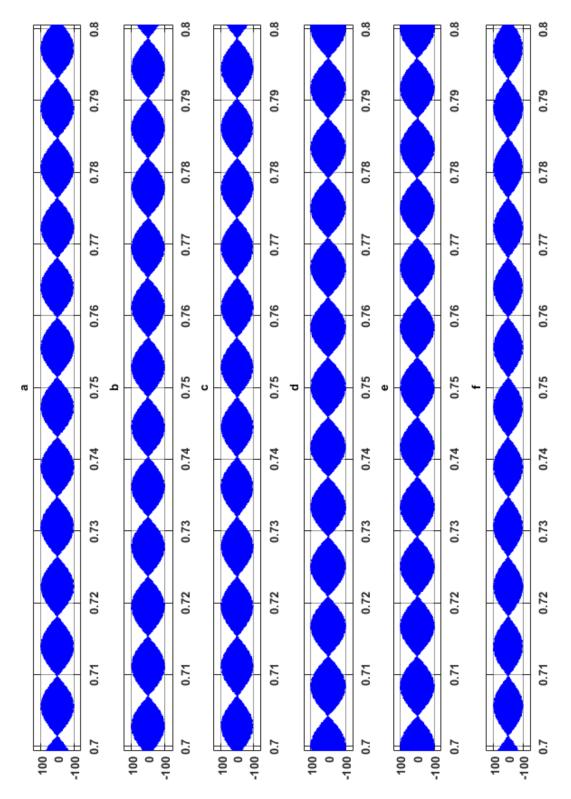

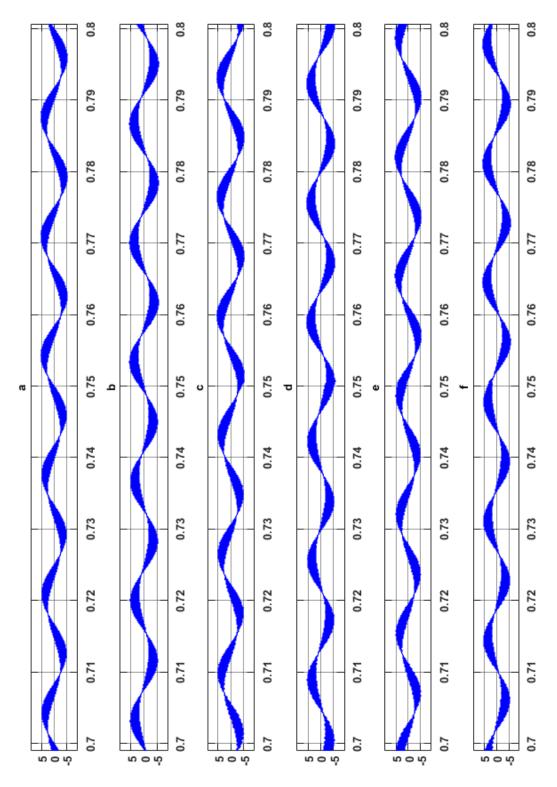

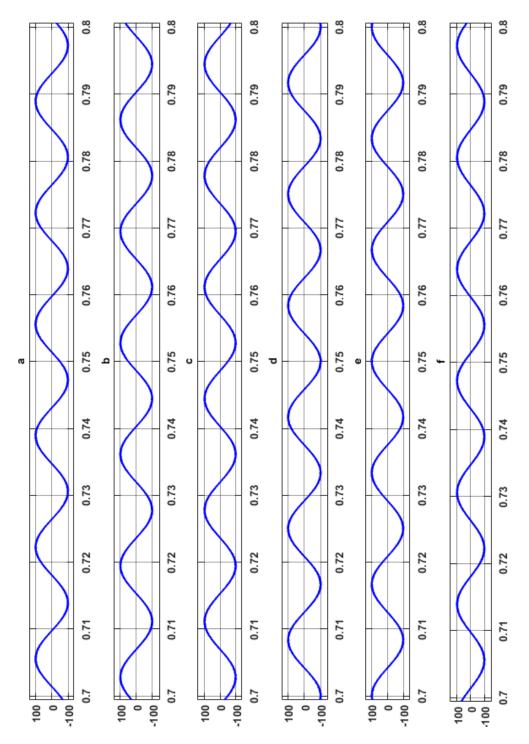

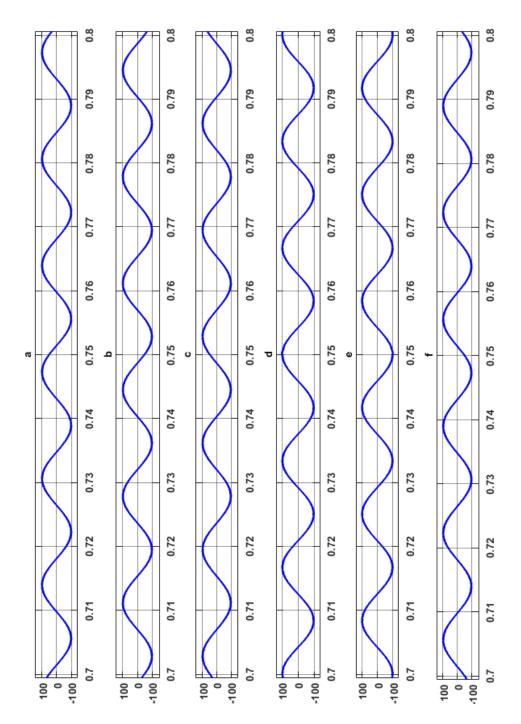

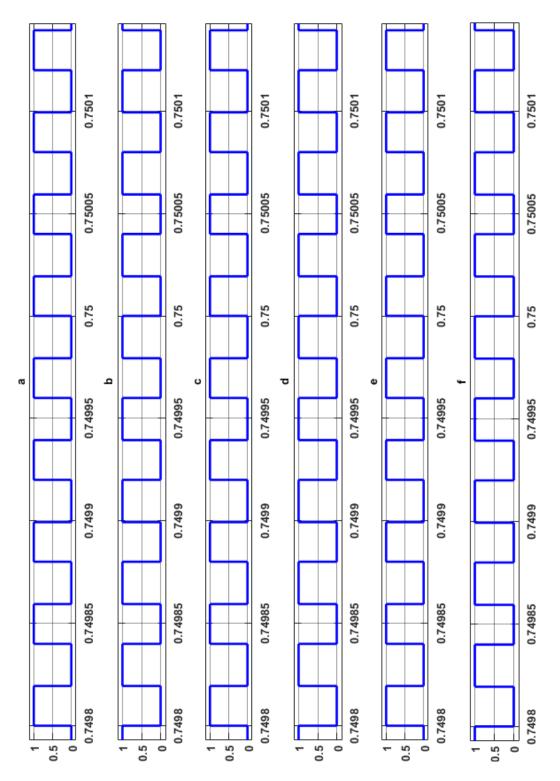

| FIGURE 6-9: DUTY CYCLE FOR EACH SWITCH (A) $S_1$ , (B) $S_2$ , (C) $S_3$ , (D) $S_4$ , (E) $S_5$ , AND, (F) $S_4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56 130 |

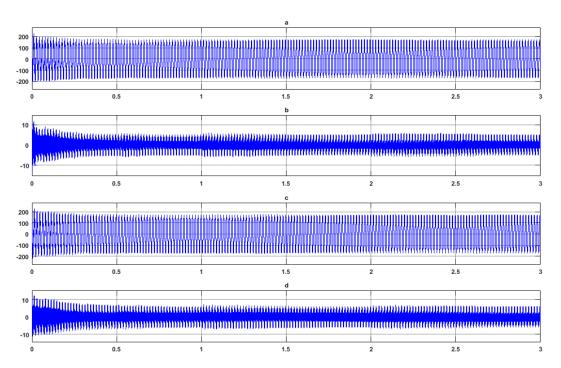

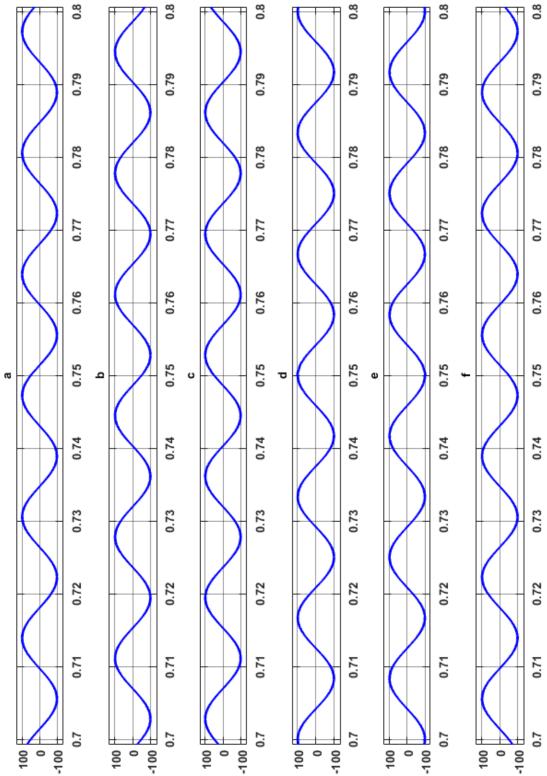

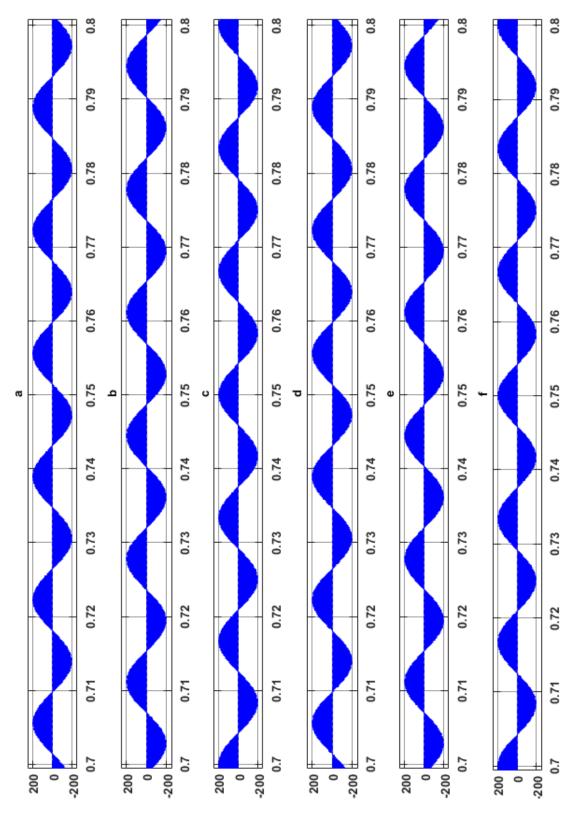

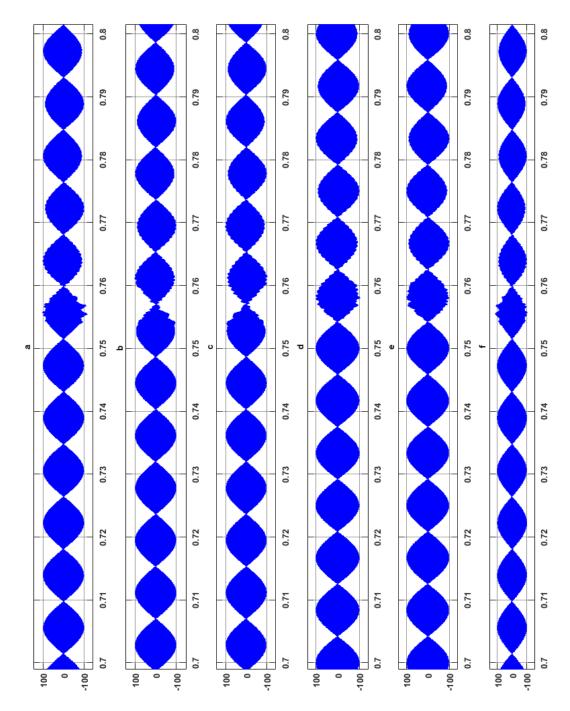

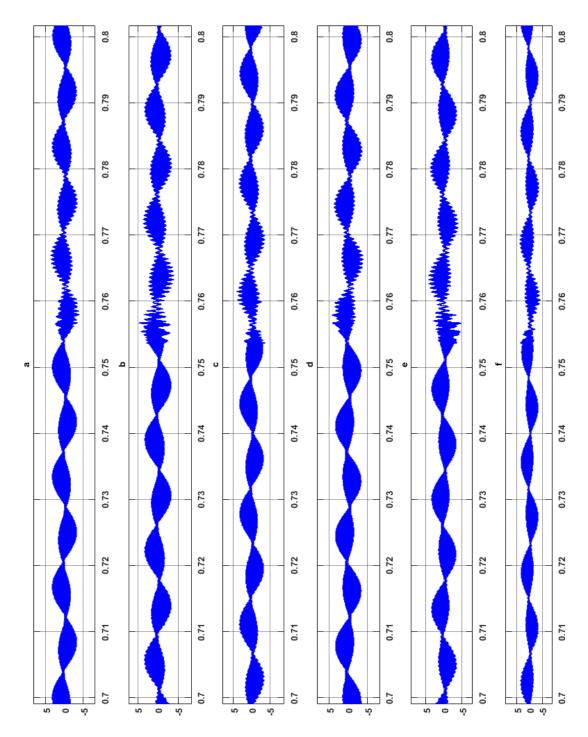

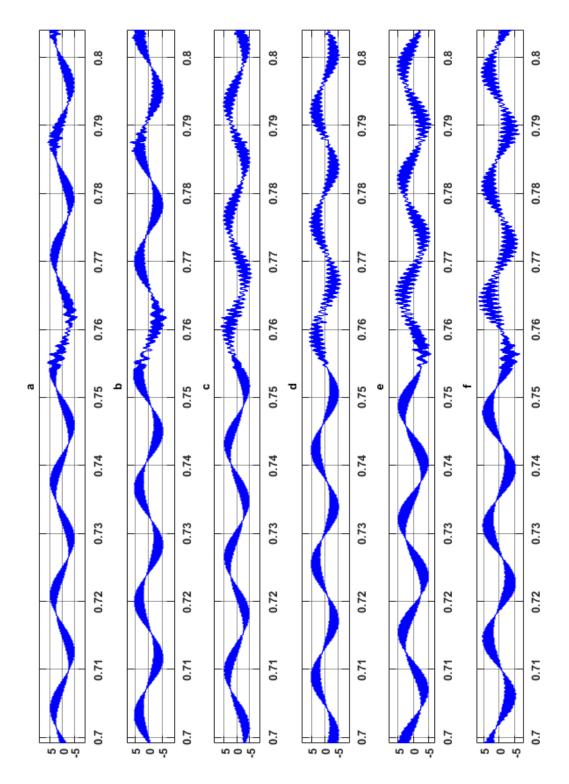

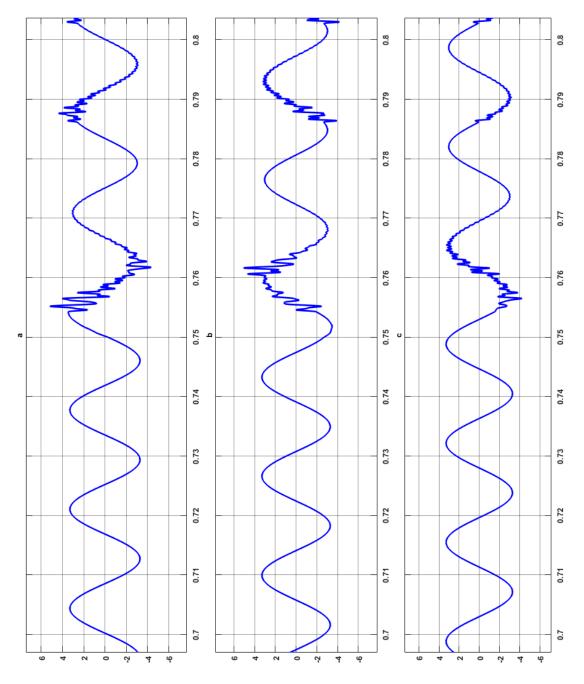

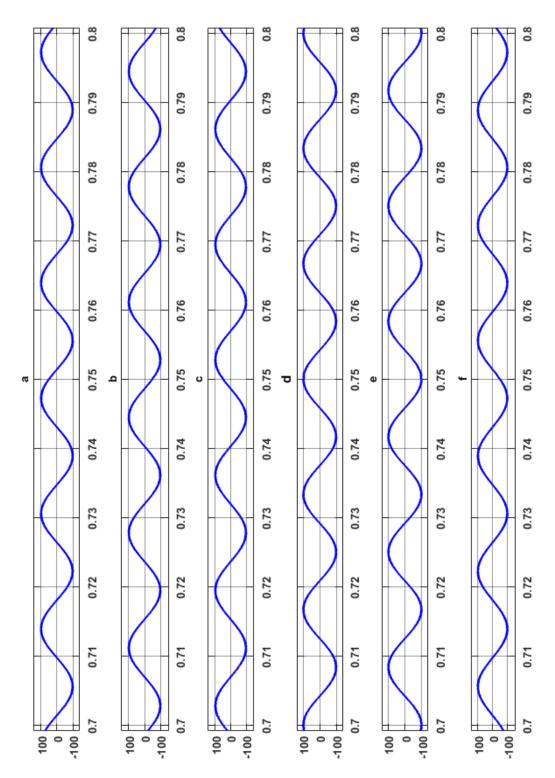

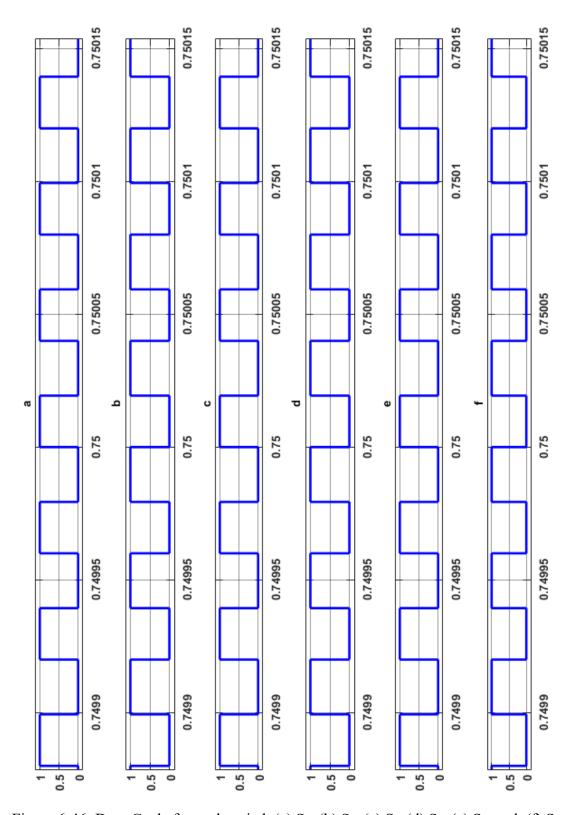

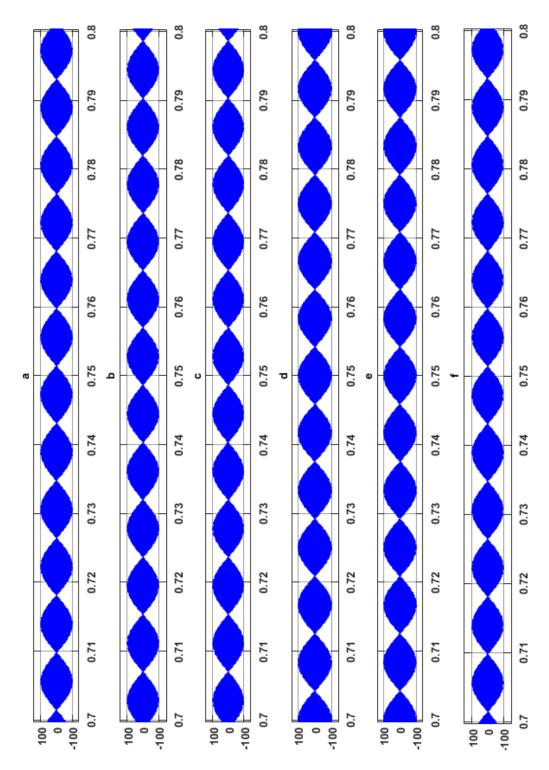

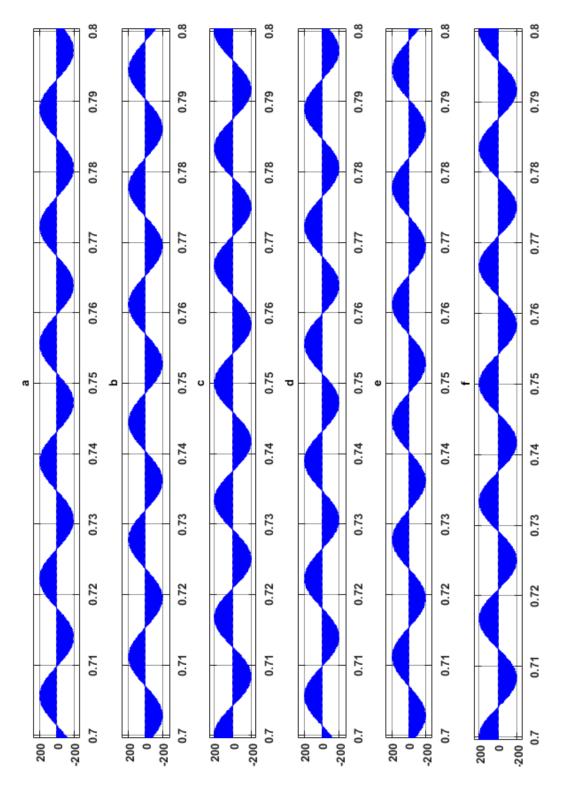

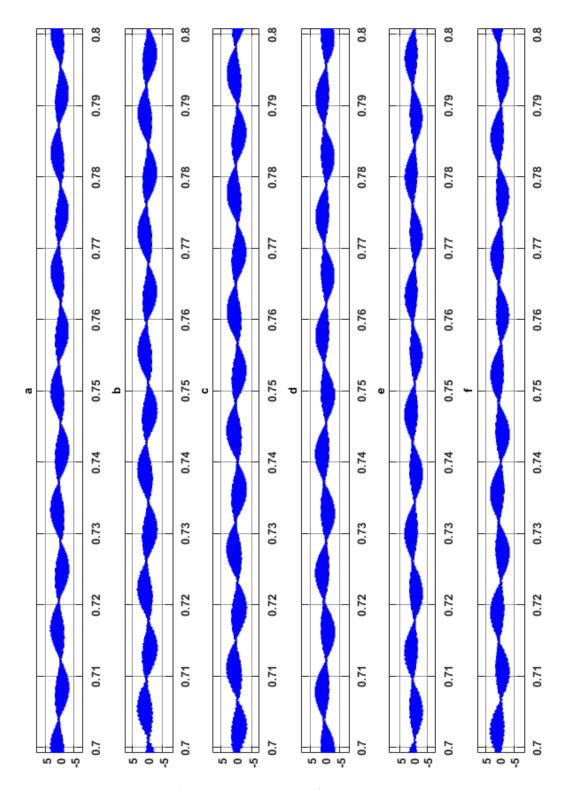

| FIGURE 6-10: VOLTAGE STRESS ACROSS EACH SWITCH (A) $S_1$ , (B) $S_2$ , (C) $S_3$ , (D) $S_4$ , (E) $S_5$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| AND,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 131    |

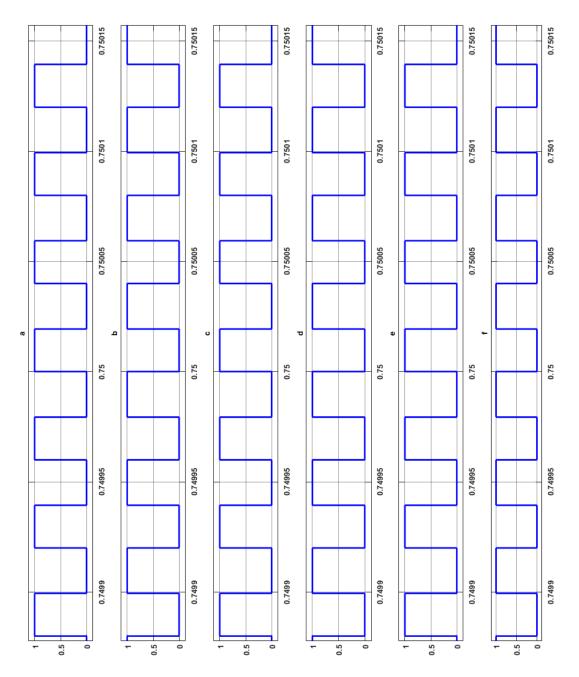

| FIGURE 6-11: CENTER-POINT CURRENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 132    |

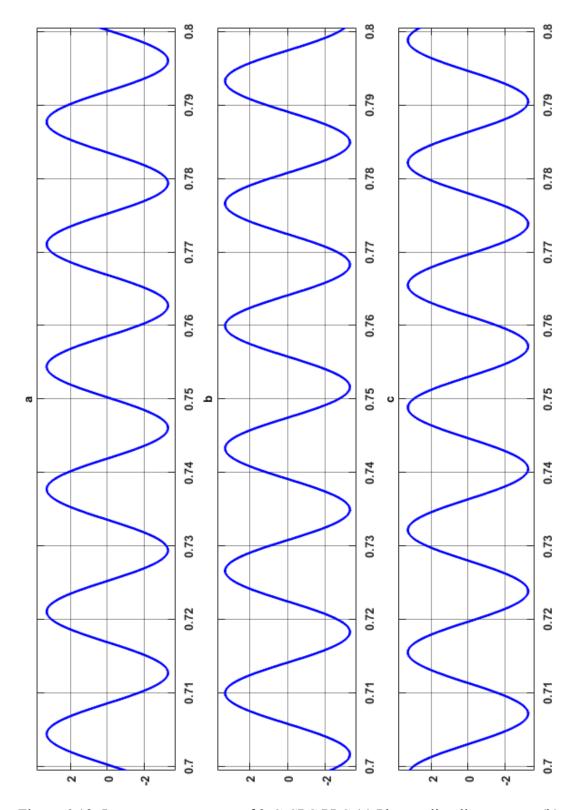

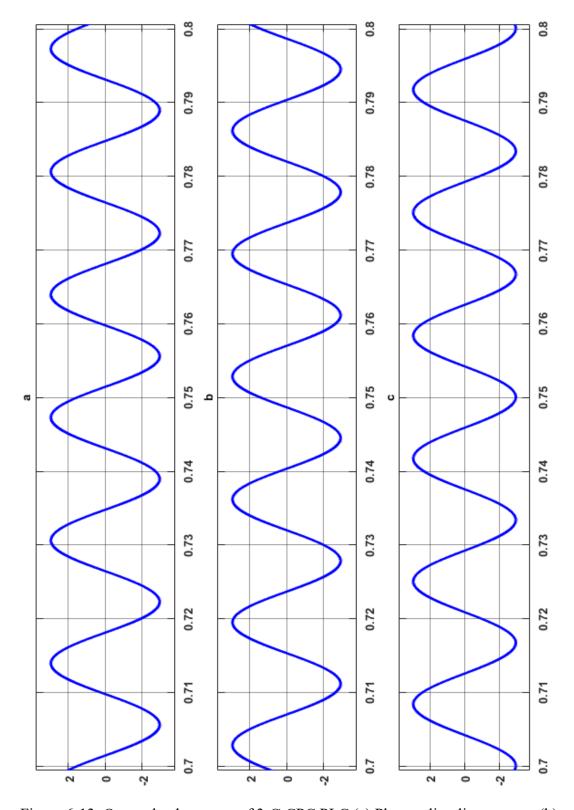

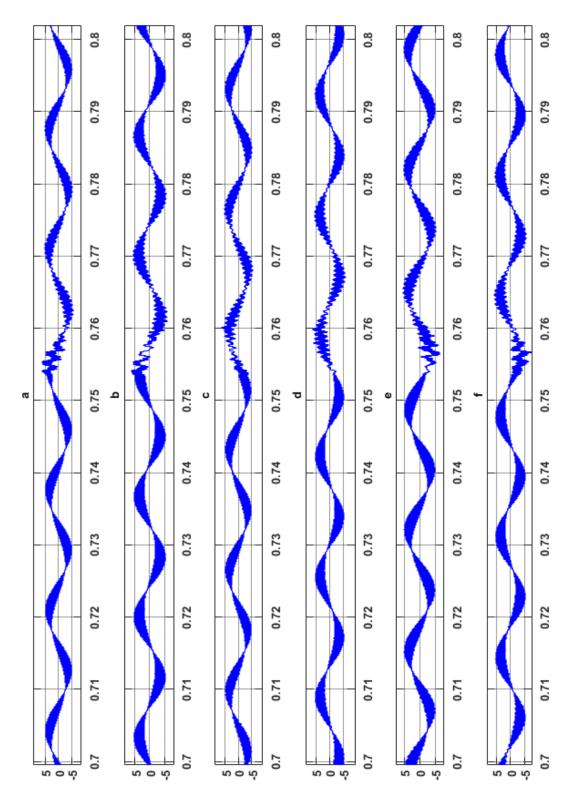

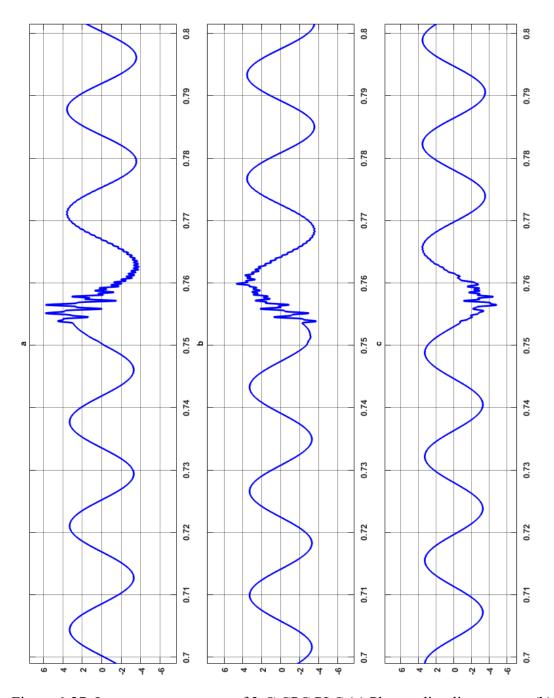

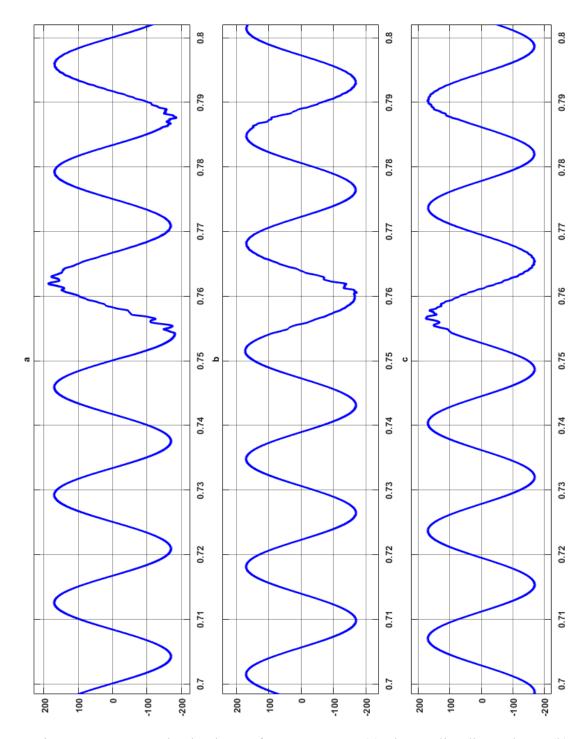

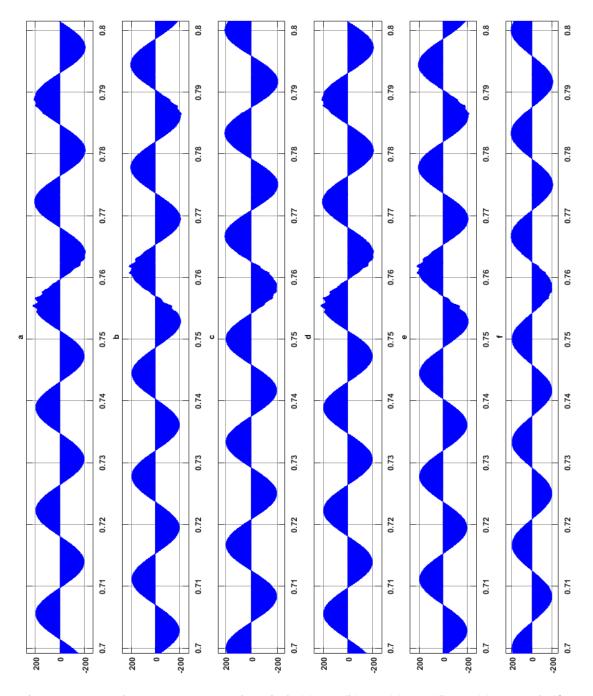

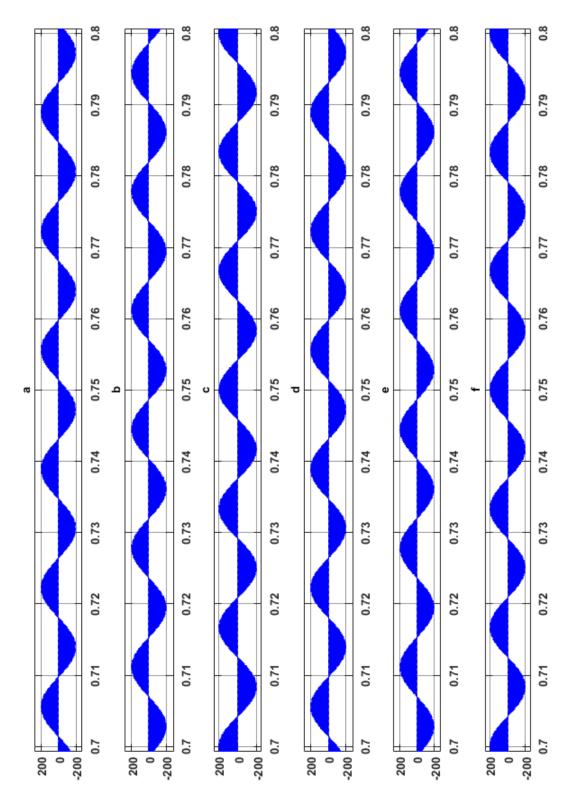

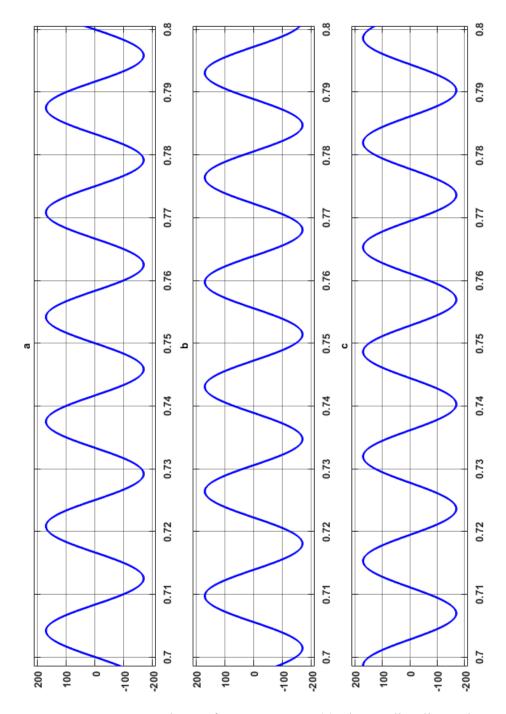

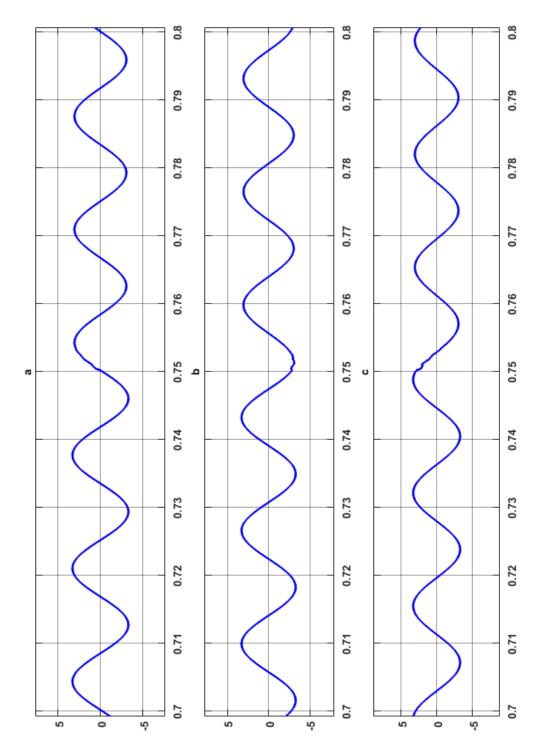

| FIGURE 6-12: INPUT SOURCE CURRENTS OF 3-Ø CPC PLC (A) PHASE-A LINE-LINE CURRI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ENT,   |

| (B) PHASE-B LINE-LINE CURRENT, AND (C) PHASE-C LINE-LINE CURRENT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 134    |

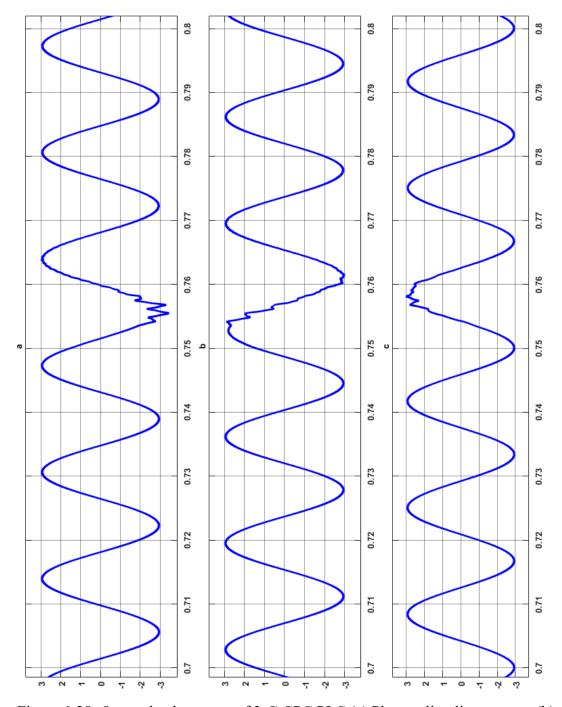

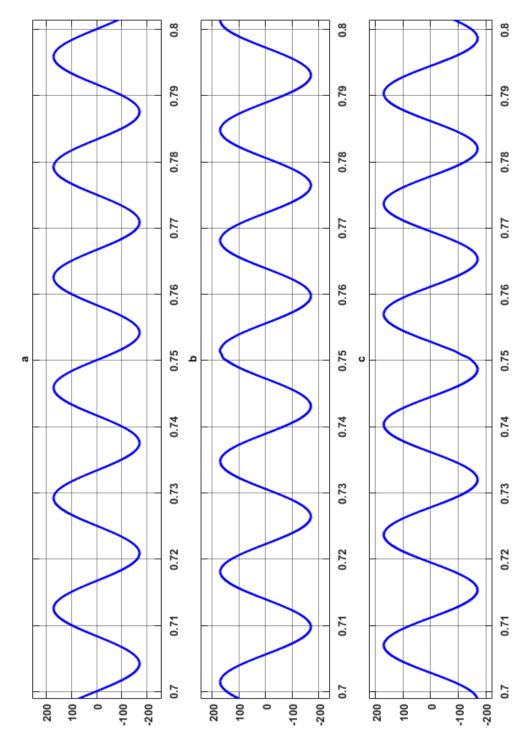

| FIGURE 6-13: OUTPUT LOAD CURRENTS OF 3-Ø CPC PLC (A) PHASE-A LINE-LINE CURRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ENT,   |

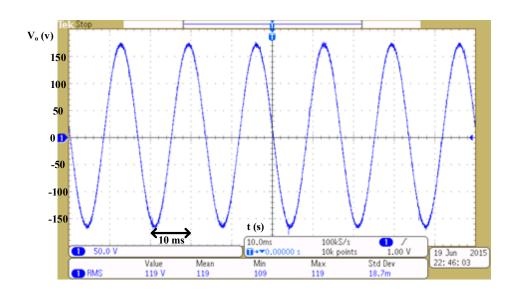

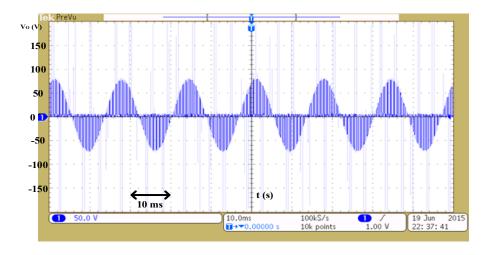

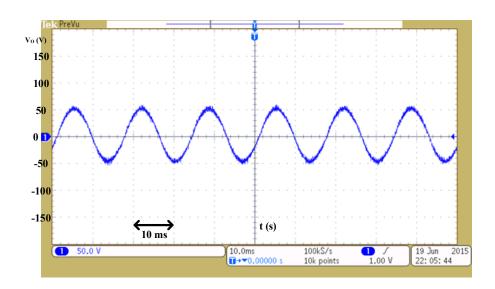

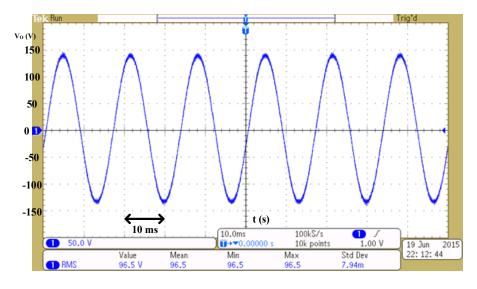

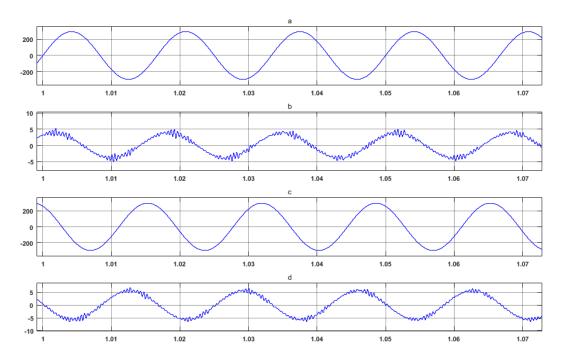

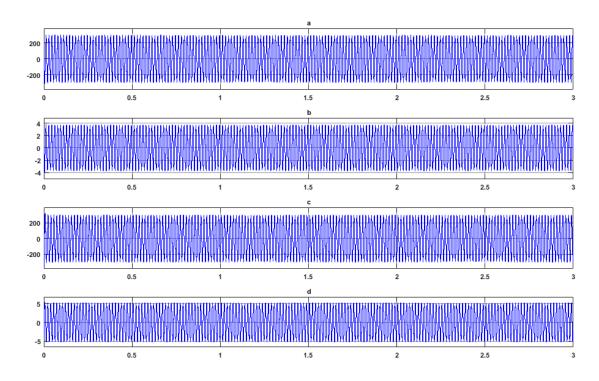

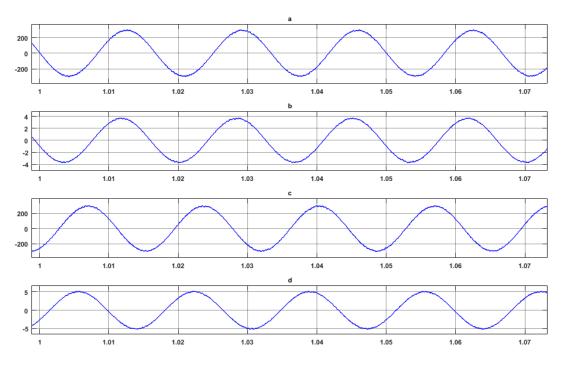

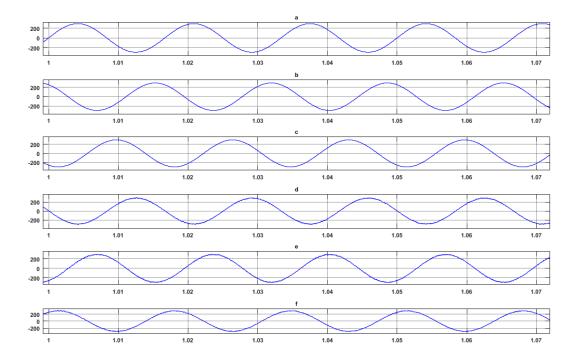

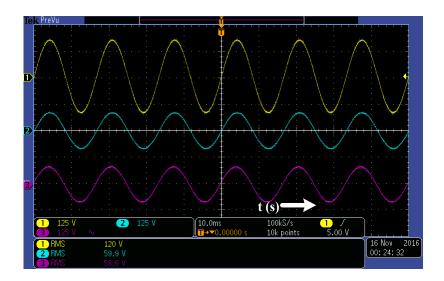

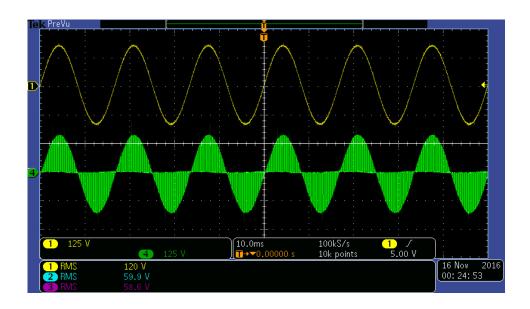

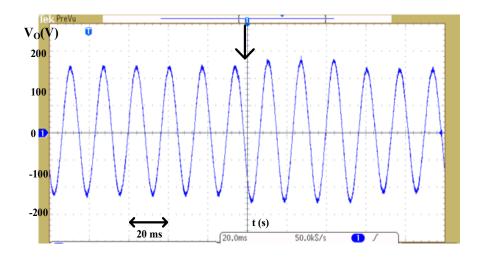

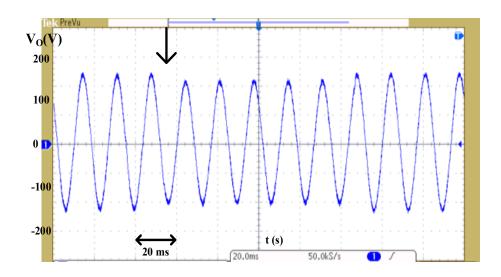

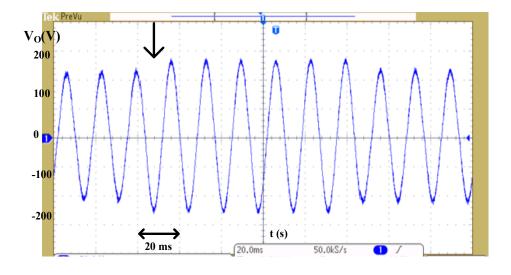

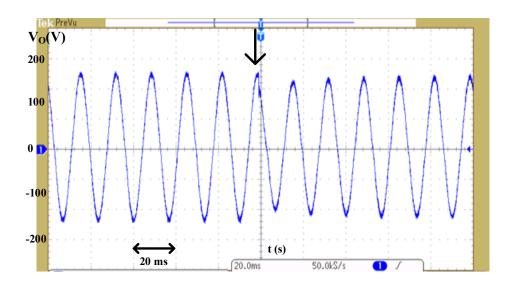

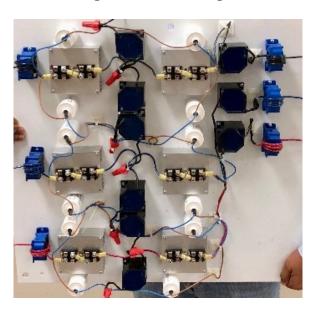

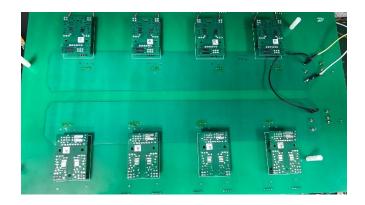

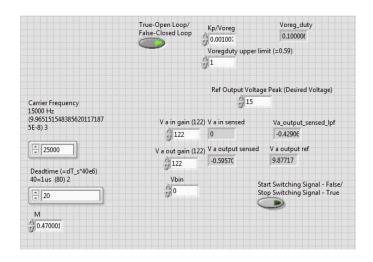

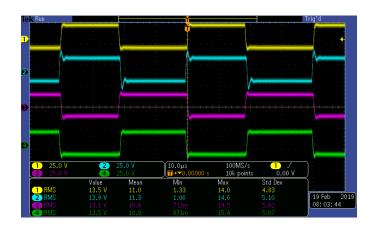

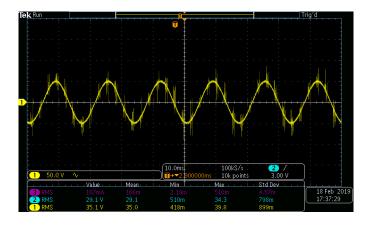

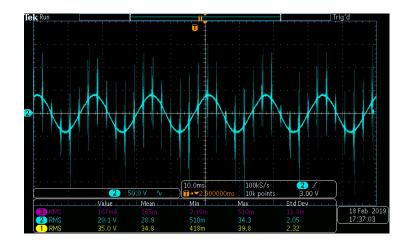

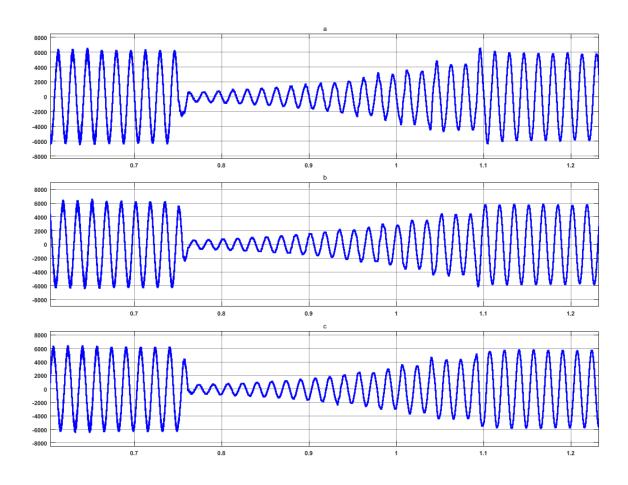

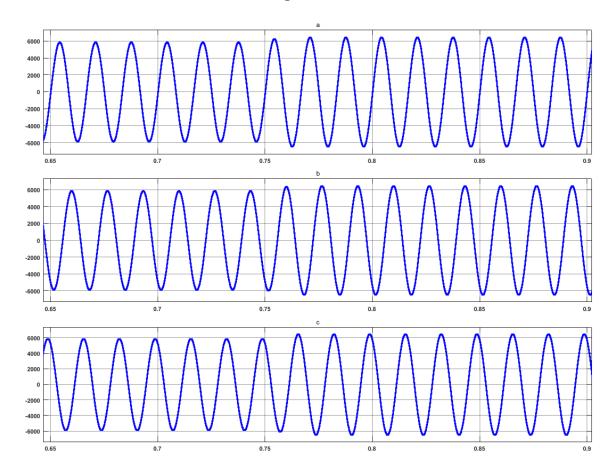

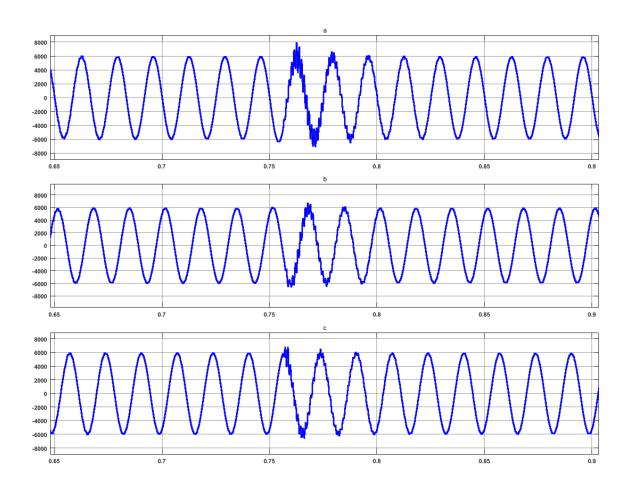

| (B) PHASE-B LINE-LINE CURRENT, AND (C) PHASE-C LINE-LINE CURRENT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 135    |