# MEMORY EFFICIENCY IMPLICATIONS ON SPARSE MATRIX OPERATIONS

by

# Shweta Jain

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2014

| App     | proved by:              |

|---------|-------------------------|

| Dr.     | Ron Sass                |

| Dr.     | James M. Conrad         |

| Dr.     | Bharat Joshi            |

| <br>Dr. | Kalpathi R. Subramanian |

© 2014 Shweta Jain ALL RIGHTS RESERVED

#### ABSTRACT

SHWETA JAIN. Memory efficiency implications on sparse matrix operations (Under the direction of DR. RON SASS)

Sparse Matrices are very large matrices with very few nonzero elements and operations on sparse matrices are central to many numerical and graph algorithms. The fundamental bottleneck in these operations is the usage of specialized storage formats which only store the NonZero (NZ) elements and the indirect memory references required to access those elements. This makes the operations very sensitive to memory latency and bandwidth. Unfortunately, microprocessor trends are not encouraging for sparse matrix operations: latency is increasing and bandwidth is becoming more scarce. This results in many important applications having very poor computation performance.

This dissertation describes a new sparse matrix format called Variable Dual Compressed Blocks (VDCB) that divides a matrix into a number of smaller, variable-sized submatrices with a bitmap to indicate the presence of NZ values. When used in conjunction with customized memory subsystem, this converts the memory reference pattern from random look-ups to a serial access pattern. To quantify how detrimental the legacy sparse matrix storage formats are, the proposed system has been implemented on an FPGA device and two common sparse matrix operations, Sparse Matrix Vector Multiplication (SMVM) and Sparse Matrix Multiplication (SMMM), were evaluated. These two operations represent a number of challenges for the memory and computation subsystems. Results demonstrate gains in bandwidth efficiency, significant impact on the performance of the SMVM and SMMM operations, and the scalability of the approach.

#### ACKNOWLEDGMENTS

A sincere thanks to several individuals who have guided me academically, professionally and personally towards the successful completion of this dissertation.

I would like to extend my thanks to my advisor Dr. Ron Sass for his patience and critical feedback. His guidance has helped me to solve difficult problems creatively and approach new research problems enthusiastically.

My parents who had firm belief in my abilities when I had none and who supported me throughout with their unconditional love and encouragement. Anita and Madhu for being my academic role models and I hope to follow their example in my professional life as well.

Ashwin you made it all possible. None of this would have ever happened without you and I will be forever grateful for your love in my life.

# TABLE OF CONTENTS

| LIST C | F TABLES                                                        | viii |

|--------|-----------------------------------------------------------------|------|

| LIST C | F FIGURES                                                       | ix   |

| LIST C | F ABBREVIATIONS                                                 | xi   |

| CHAP   | TER 1: INTRODUCTION                                             | 1    |

| 1.1    | Sparse Matrix Operations                                        | 3    |

| 1.2    | Thesis Statement                                                | 5    |

| CHAP   | TER 2: BACKGROUND                                               | 9    |

| 2.1    | Field-Programmable Gate Arrays                                  | 9    |

| 2.2    | Xilinx Integrated Software Environment                          | 11   |

| 2.3    | IEEE 754 Floating Point Format                                  | 13   |

|        | 2.3.1 IEEE 754 Floating Point Multiplication                    | 14   |

|        | 2.3.2 IEEE 754 Floating Point Addition                          | 15   |

| 2.4    | Unordered Merge                                                 | 16   |

| 2.5    | Architecture Independent REconfigurable Network                 | 17   |

| 2.6    | Sparse Matrix Vector Multiplication                             | 18   |

|        | 2.6.1 Performance Issues of Sparse Matrix Vector Multiplication | 18   |

|        | 2.6.2 Related Work for the SMVM Operation                       | 20   |

|        | 2.6.2.1 FPGA Implementations                                    | 20   |

|        | 2.6.2.2 Impact on Multi-Core Platforms                          | 21   |

|        | 2.6.2.3 Algorithmic Advances                                    | 21   |

| 2.7    | Sparse Matrix Multiplication                                    | 22   |

|        | 2.7.1 Performance Issues of SMMM Operation                      | 22   |

|        | 2.7.2 Related Work for the SMMM Operation                       | 24   |

| CHAPT  | TER 3: DESIGN                                                   | 26   |

| 3.1    | Variable Dual Compressed Blocks                                 | 27   |

|       |                                          |                                                                  | vi |  |  |  |  |

|-------|------------------------------------------|------------------------------------------------------------------|----|--|--|--|--|

|       | 3.1.1                                    | VDCB Encoder Software Design                                     | 28 |  |  |  |  |

|       | 3.1.2                                    | Definitions                                                      | 30 |  |  |  |  |

|       | 3.1.3                                    | Notations Used                                                   | 31 |  |  |  |  |

| 3.2   | Hardv                                    | ware Design for Sparse Matrix Vector Multiplication              | 32 |  |  |  |  |

|       | 3.2.1                                    | Sequential Hardware Design                                       | 32 |  |  |  |  |

|       |                                          | 3.2.1.1 Block Processing Unit                                    | 32 |  |  |  |  |

|       |                                          | 3.2.1.2 Customized Memory Interface                              | 34 |  |  |  |  |

|       |                                          | 3.2.1.3 Row Column Generator                                     | 37 |  |  |  |  |

|       | 3.2.2                                    | Performing Parallel Sparse Matrix Vector Multiplication using    |    |  |  |  |  |

|       |                                          | VDCB Format                                                      | 41 |  |  |  |  |

|       |                                          | 3.2.2.1 Parallel Hardware Design                                 | 46 |  |  |  |  |

| 3.3   | Softwa                                   | are Design for Sparse Matrix Vector Multiplication               | 48 |  |  |  |  |

| 3.4   | Perfor                                   | Performing Sparse Matrix-Matrix Multiplication using VDCB Format |    |  |  |  |  |

|       | 3.4.1 Block Selection and Multiplication |                                                                  |    |  |  |  |  |

|       | 3.4.2                                    | Count Ones Technique                                             | 57 |  |  |  |  |

| 3.5   | Hardv                                    | ware Design for the SMMM Operation                               | 58 |  |  |  |  |

|       | 3.5.1                                    | Block Selection Unit                                             | 59 |  |  |  |  |

|       | 3.5.2                                    | Block Fill Unit                                                  | 61 |  |  |  |  |

|       | 3.5.3                                    | Computation Unit                                                 | 63 |  |  |  |  |

|       | 3.5.4                                    | Parallel Hardware Design for SMMM Operation                      | 67 |  |  |  |  |

| 3.6   | Softwa                                   | are Design for Sparse Matrix-Matrix Multiplication               | 68 |  |  |  |  |

| CHAPT | ΓER 4:                                   | EVALUATION                                                       | 70 |  |  |  |  |

| 4.1   | Perfor                                   | rmance Analysis of Hardware/Software Co-Design Approach          | 71 |  |  |  |  |

|       | 4.1.1                                    | Results and Analysis for Sparse Matrix Vector Multiplication     | 71 |  |  |  |  |

|       |                                          | 4.1.1.1 Index Overhead                                           | 72 |  |  |  |  |

|       |                                          | 4.1.1.2 Sequential Hardware Design Performance Evaluation        | 75 |  |  |  |  |

|       |                                          | 4.1.1.3 Block Sizes                                              | 79 |  |  |  |  |

|              |                                                                                                                                                                                         |           |                                                      | V11 |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------------|-----|--|

|              |                                                                                                                                                                                         | 4.1.1.4   | Parallel Hardware Design Performance Evaluation      | 80  |  |

|              |                                                                                                                                                                                         | 4.1.1.5   | Resource Utilization for SMVM Operation              | 90  |  |

|              | 4.1.2                                                                                                                                                                                   | Results   | and Analysis for Sparse Matrix Matrix Multiplication | 90  |  |

|              |                                                                                                                                                                                         | 4.1.2.1   | Block Sizes                                          | 91  |  |

|              |                                                                                                                                                                                         | 4.1.2.2   | Effect of Sparsity                                   | 91  |  |

|              |                                                                                                                                                                                         | 4.1.2.3   | Bandwidth Efficiency                                 | 93  |  |

|              |                                                                                                                                                                                         | 4.1.2.4   | Scalability                                          | 95  |  |

|              |                                                                                                                                                                                         | 4.1.2.5   | Resource Utilization for SMMM Operation              | 97  |  |

| 4.2          | Perfor                                                                                                                                                                                  | mance A   | nalysis of Software Only Approach                    | 98  |  |

|              | 4.2.1                                                                                                                                                                                   | Perform   | ance Evaluation of Software Only SMVM Operation      | 98  |  |

|              |                                                                                                                                                                                         | 4.2.1.1   | Floating Point Performance                           | 99  |  |

|              | 4.2.2                                                                                                                                                                                   | Perform   | ance Evaluation of Software Only SMMM Operation      | 101 |  |

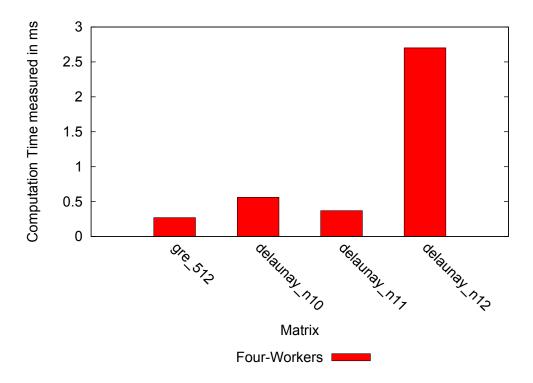

|              |                                                                                                                                                                                         | 4.2.2.1   | Computation Performance                              | 101 |  |

| 4.3          | Co-De                                                                                                                                                                                   | esign App | roach versus Software-Only Approach                  | 103 |  |

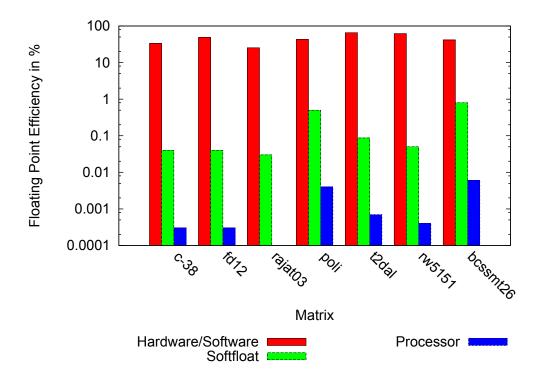

|              | 4.3.1                                                                                                                                                                                   | Floating  | Point Efficiency                                     | 104 |  |

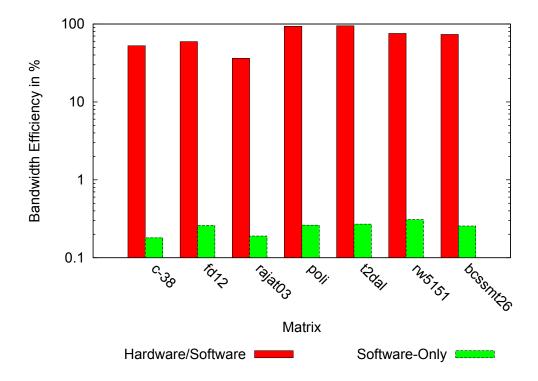

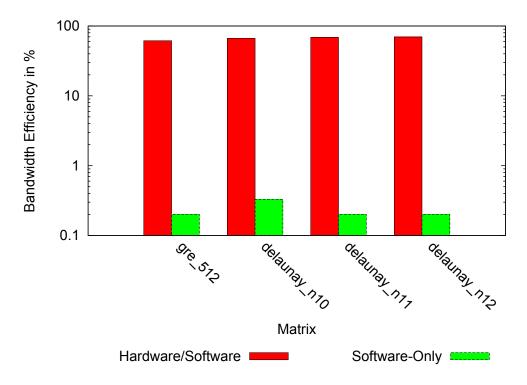

|              | <ul> <li>4.2.2 Performance Evaluation of Software Only SMMM Operation</li> <li>4.2.2.1 Computation Performance</li> <li>4.3 Co-Design Approach versus Software-Only Approach</li> </ul> |           | 106                                                  |     |  |

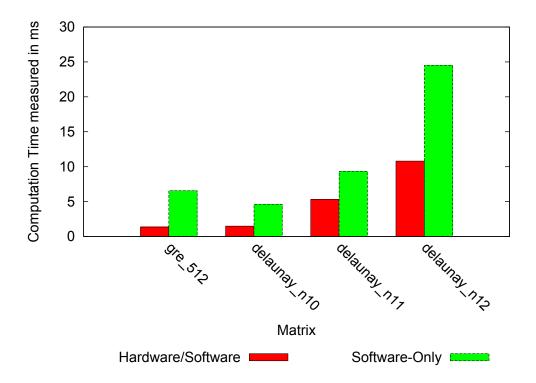

|              | 4.3.3                                                                                                                                                                                   | Comput    | ation Time                                           | 108 |  |

|              | 4.3.4                                                                                                                                                                                   | Speedup   |                                                      | 110 |  |

| CHAPT        | CHAPTER 5: CONCLUSION                                                                                                                                                                   |           |                                                      |     |  |

| REFERENCES 1 |                                                                                                                                                                                         |           |                                                      |     |  |

|              |                                                                                                                                                                                         |           |                                                      |     |  |

|            |                                                        | viii |

|------------|--------------------------------------------------------|------|

|            | LIST OF TABLES                                         |      |

|            |                                                        |      |

| TABLE 3.1: | Notations used                                         | 31   |

| TABLE 3.2: | BSU FSM action                                         | 60   |

| TABLE 4.1: | Performance metrics for evaluation                     | 71   |

| TABLE 4.2: | Test matrices characteristics                          | 72   |

| TABLE 4.3: | Sustained performance for sequential SMVM operation    | 79   |

| TABLE 4.4: | Sustained performance for parallel SMVM implementation | 89   |

| TABLE 4.5: | Hardware resource utilization for SMVM operation       | 90   |

| TABLE 4.6: | Characteristics of test matrices                       | 91   |

| TABLE 4.7: | Frequency of operation for BFU and PE                  | 91   |

| TABLE 4.8: | Hardware resource utilization for SMMM operation       | 98   |

| TABLE 4.9: | Performance metrics used for comparison                | 104  |

110

TABLE 4.10: Speedup comparison

# LIST OF FIGURES

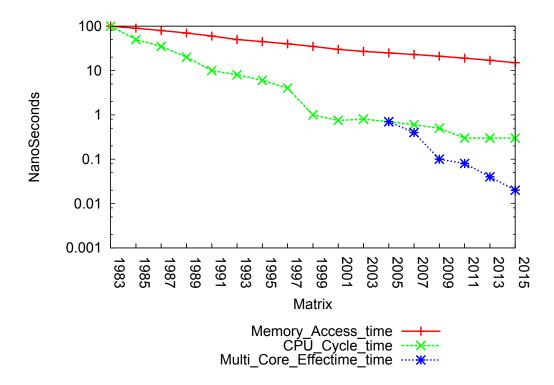

| FIGURE 1.1:  | Changes in memory access times                             | 2  |

|--------------|------------------------------------------------------------|----|

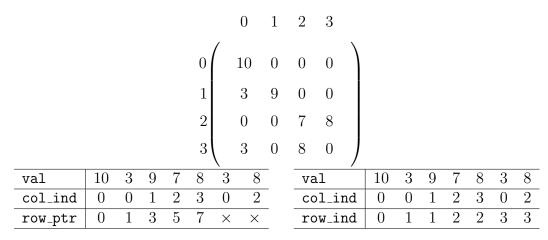

| FIGURE 1.2:  | Example of CSR and COO format                              | 3  |

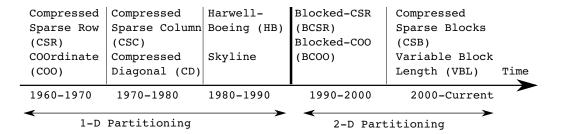

| FIGURE 1.3:  | Evolution of sparse matrix storage formats                 | 6  |

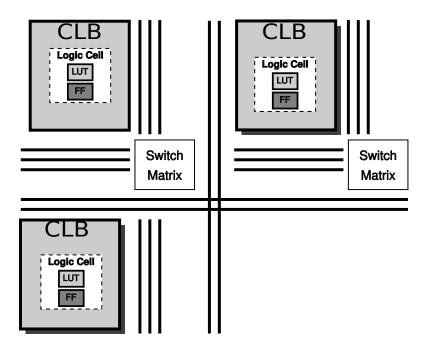

| FIGURE 2.1:  | High level view of FPGA device                             | 10 |

| FIGURE 2.2:  | Single precision floating point representation             | 14 |

| FIGURE 2.3:  | Double precision floating point representation             | 14 |

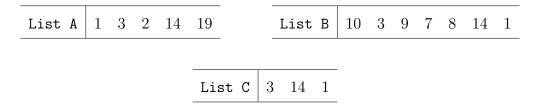

| FIGURE 2.4:  | Example of unordered merge                                 | 16 |

| FIGURE 2.5:  | Example of CSR format                                      | 18 |

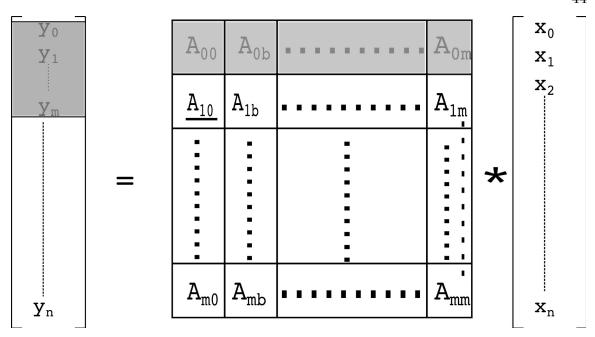

| FIGURE 2.6:  | Basic matrix multiplication                                | 23 |

| FIGURE 2.7:  | CSR Multiplication Example                                 | 23 |

| FIGURE 3.1:  | VDCB format                                                | 28 |

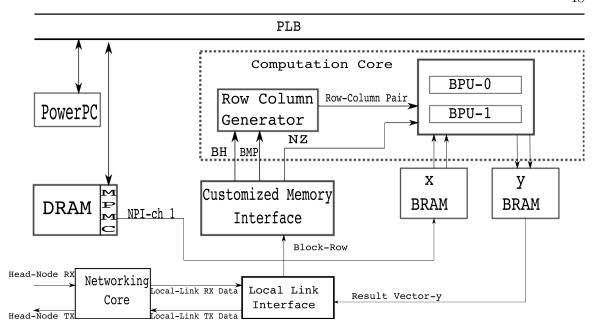

| FIGURE 3.2:  | High level architecture for SMVM operation                 | 32 |

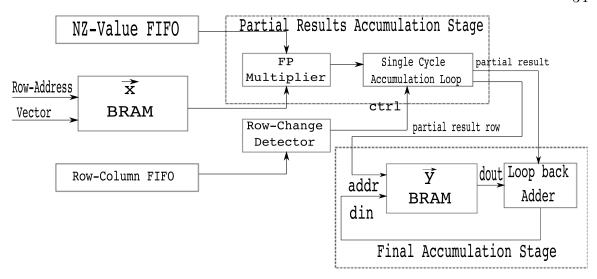

| FIGURE 3.3:  | Block processing unit                                      | 34 |

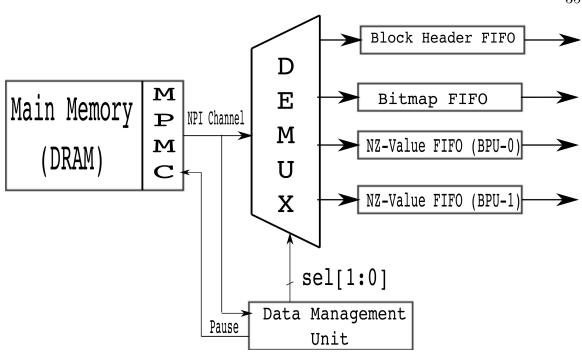

| FIGURE 3.4:  | Customized memory interface                                | 35 |

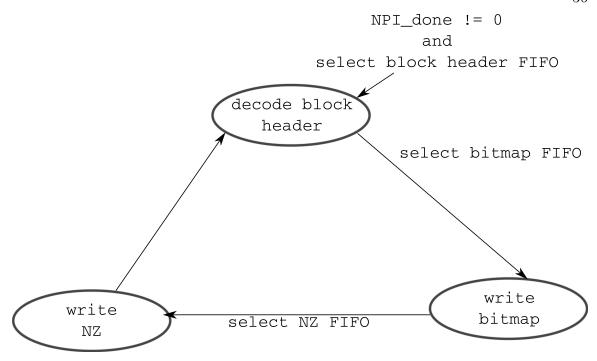

| FIGURE 3.5:  | DMU control FSM                                            | 36 |

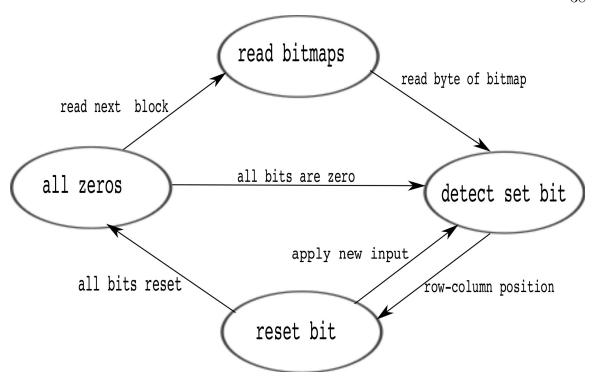

| FIGURE 3.6:  | Row-Column generator FSM                                   | 38 |

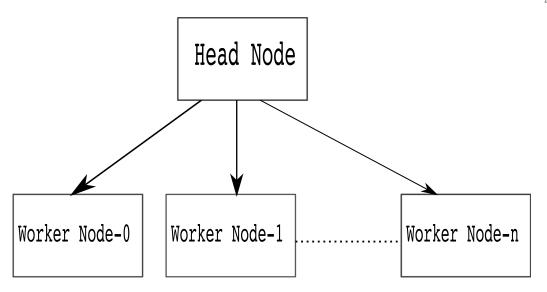

| FIGURE 3.7:  | Parallel implementation of SMVM operation using Block Rows | 44 |

| FIGURE 3.8:  | Network topology for parallel SMVM                         | 45 |

| FIGURE 3.9:  | High level architecture of worker node                     | 48 |

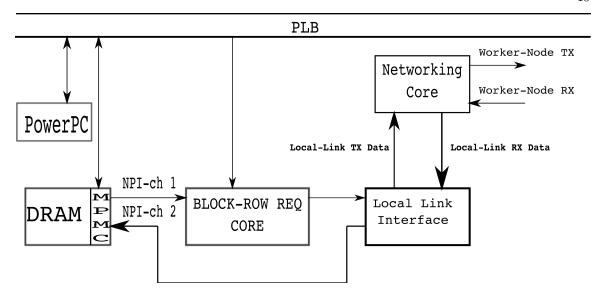

| FIGURE 3.10: | High level architecture of Head Node                       | 49 |

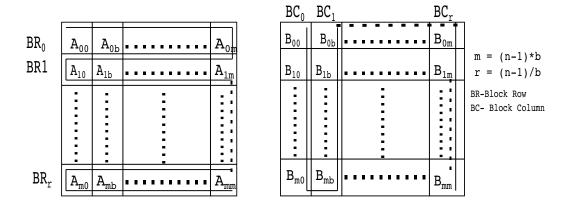

| FIGURE 3.11: | Block arrangement for the SMMM operation                   | 52 |

| FIGURE 3.12: | Dot product using bmps                                     | 56 |

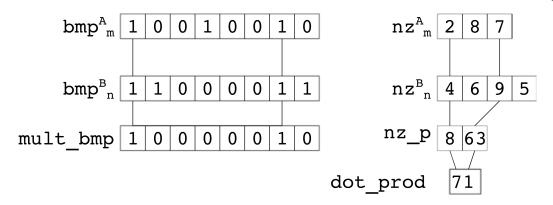

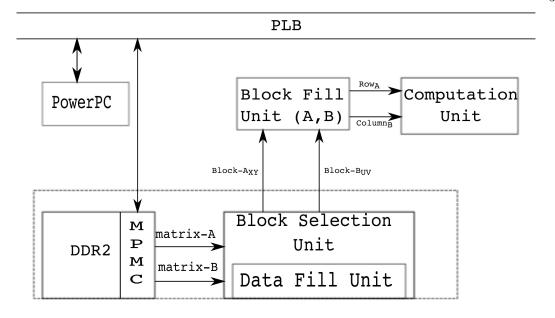

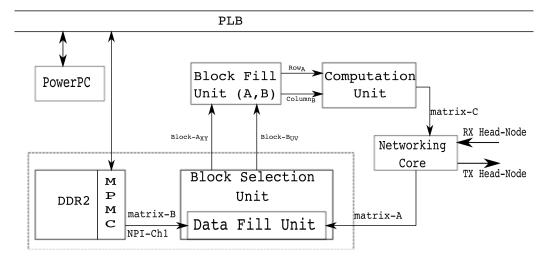

| FIGURE 3.13: | High level architecture for SMMM operation                 | 59 |

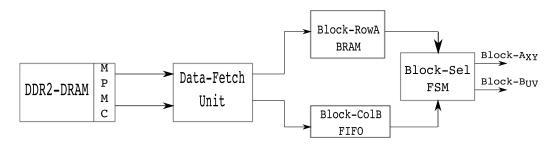

| FIGURE 3.14: | Block selection unit                                       | 61 |

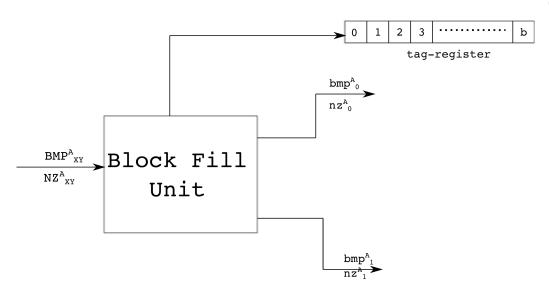

| FIGURE 3.15: | Block fill unit                                            | 62 |

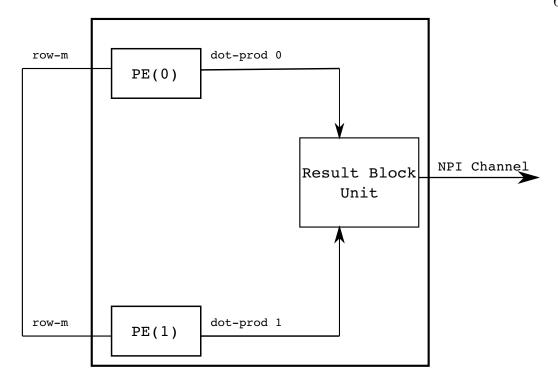

| FIGURE 3.16: | Computation unit                                          | 64  |

|--------------|-----------------------------------------------------------|-----|

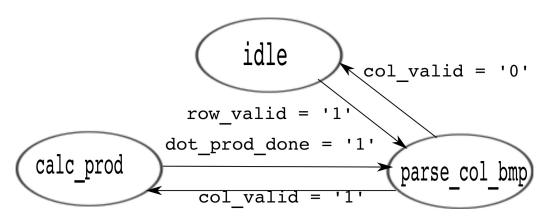

| FIGURE 3.17: | Control unit FSM                                          | 65  |

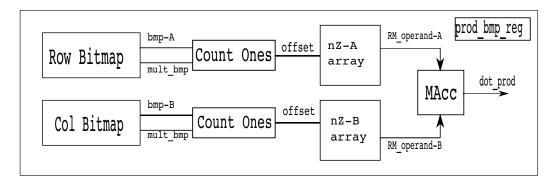

| FIGURE 3.18: | Processing element                                        | 66  |

| FIGURE 3.19: | High level architecture for parallel SMMM operation       | 68  |

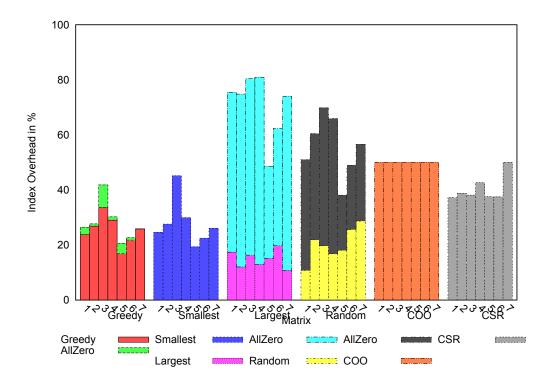

| FIGURE 4.1:  | Index Overhead                                            | 74  |

| FIGURE 4.2:  | Bandwidth efficiency for one BPU                          | 76  |

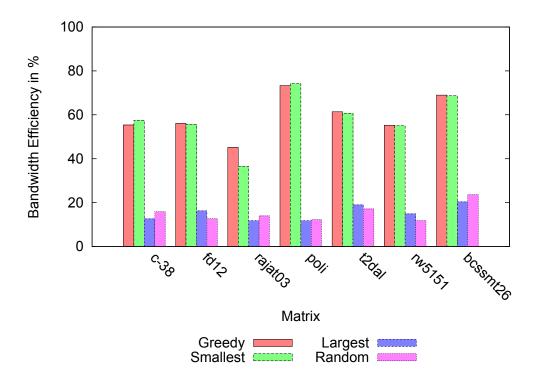

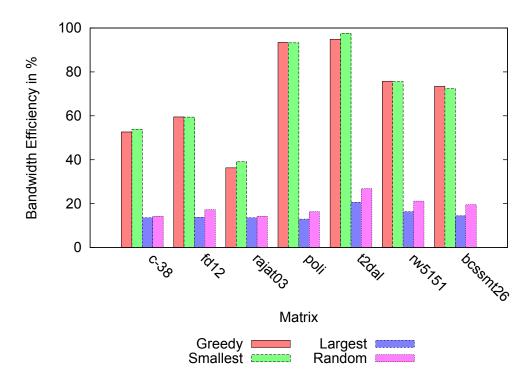

| FIGURE 4.3:  | Bandwidth efficiency for two BPUs                         | 77  |

| FIGURE 4.4:  | Floating point performance                                | 78  |

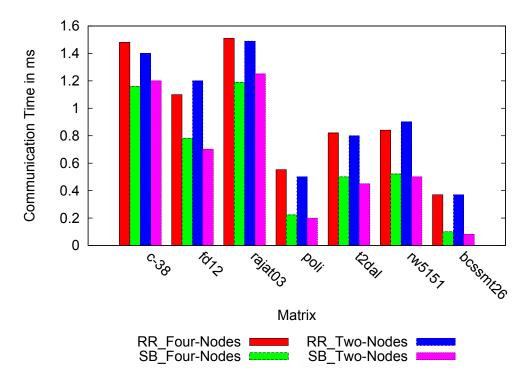

| FIGURE 4.5:  | Communication time for Block Rows                         | 81  |

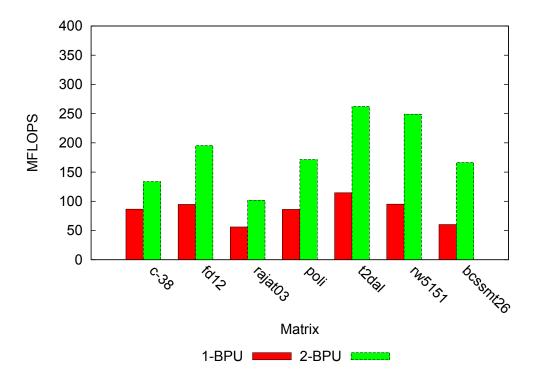

| FIGURE 4.6:  | Floating point performance                                | 84  |

| FIGURE 4.7:  | Floating point performance on increasing worker nodes     | 86  |

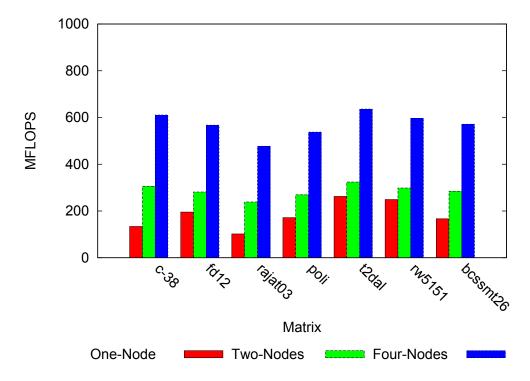

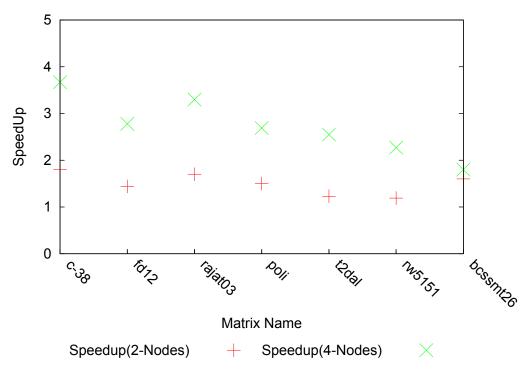

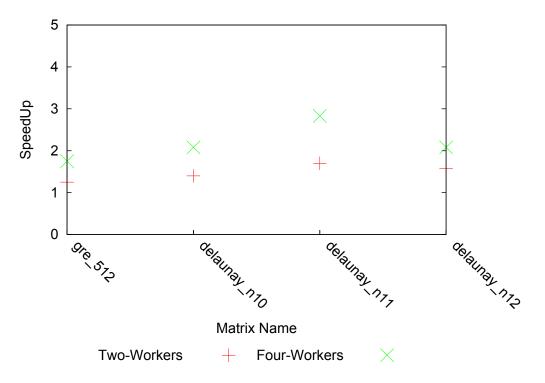

| FIGURE 4.8:  | Speedup                                                   | 88  |

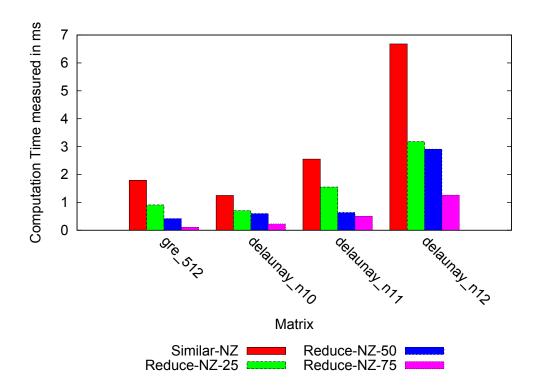

| FIGURE 4.9:  | Effect of sparsity on computation time                    | 93  |

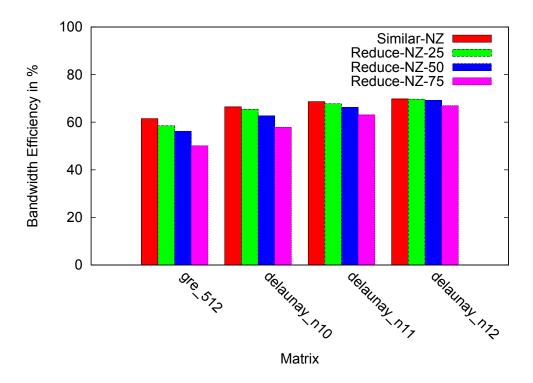

| FIGURE 4.10: | Bandwidth efficiency of matrix $B$                        | 94  |

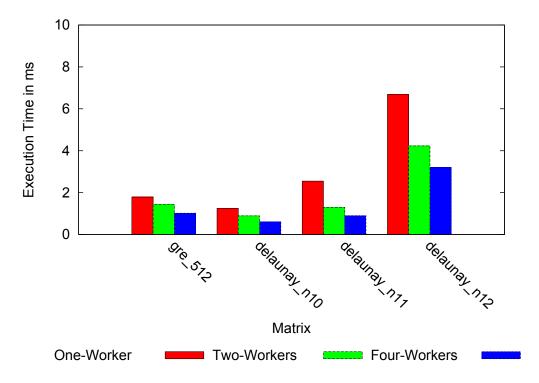

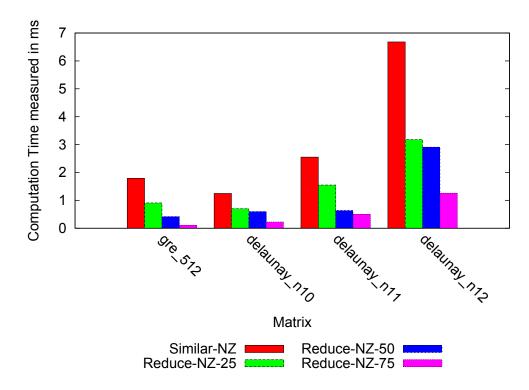

| FIGURE 4.11: | Computation time measurement for parallel hardware design | 96  |

| FIGURE 4.12: | Speedup for parallel hardware design                      | 97  |

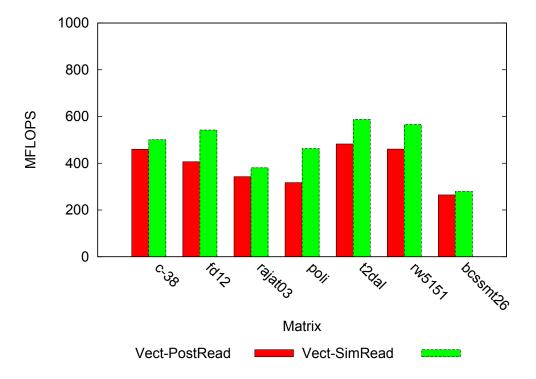

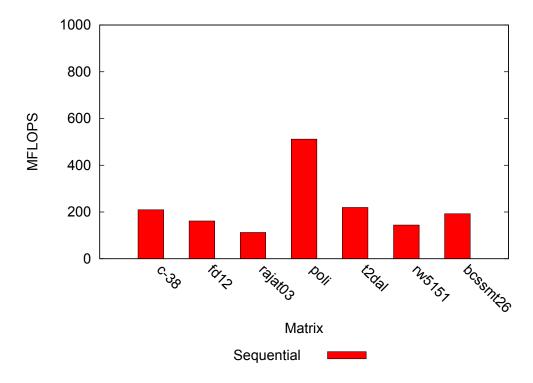

| FIGURE 4.13: | Floating point performance of sequential software design  | 100 |

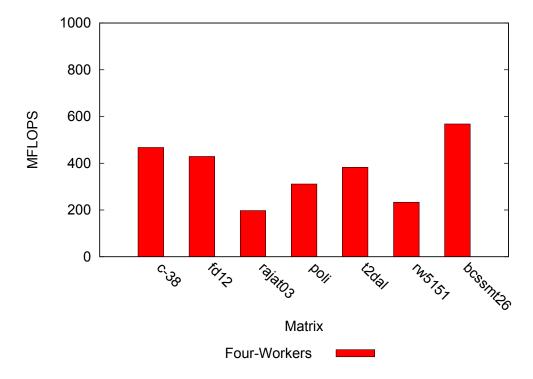

| FIGURE 4.14: | Floating point performance for parallel software Design   | 101 |

| FIGURE 4.15: | Execution time for sequential software design             | 102 |

| FIGURE 4.16: | Execution time for parallel software design               | 103 |

| FIGURE 4.17: | Floating point efficiency comparison                      | 106 |

| FIGURE 4.18: | Bandwidth efficiency comparison for SMVM operation        | 108 |

| FIGURE 4.19: | Bandwidth efficiency comparison for SMMM operation        | 109 |

| FIGURE 4.20: | Computation time comparison                               | 110 |

#### LIST OF ABBREVIATIONS

AIREN Architecture independent reconfigurable network

BCSR Block compressed sparse rows

COO Coordinate format

CSR Compressed sparse rows

DMA Direct memory access

DRAM Dynamic random access memory

EOF End of frame

FPGA Field programmable gate array

FSM Finite state machine

HPC High performance computing

IP Intellectual propoerty

MGT Multi Gigabit Transceiver

MPI Message passing interface

NPI Native port interface

SOF Start of frame

SMVM Sparse matrix vector multiplication

SMMM Sparse matrix multiplication

VDCB Variable dual compressed blocks

#### CHAPTER 1: INTRODUCTION

The sustained projection of Moore's Law has had a significant impact on processor and memory architectures. Both processor and memory systems have seen an improvement in terms of speed, but the rates have been dramatically diverging. Processors have seen an exponential growth in performance (speed and bandwidth) as a result of reduced feature size and increased number of transistors giving rise to the multi-core and many-core architectures. In case of memories the additional transistor count has provided increased capacities at a cheaper cost. But unlike the processors the increasing transistor count does not provide a significant speed improvement for the memories. In fact memory latency in terms of processor clock cycles has increased (memory cell speeds have remained constant over the past decade) as shown in Figure 1.1. In context of processor architectures where the main memory is implemented using the Dynamic Random Access Memory (DRAM) on seperate chips the dormant nature of memory speeds has resulted in a "Memory Wall". The "Memory Wall" was first identified by Wulf and Mckee in [1]. The authors predicted that the disparity between memory speeds and processor speeds will eventually result in performance degradation as the processor will be always waiting for the data from the memory.

The "Memory Wall" has seen different manifestations for uniprocessor and multiprocessor systems. In case of uniprocessor system the critical performance impediment was the memory access latency which was alleviated using caches and latency hiding techniques like hardware/software prefetching and Out-of-Order execution of instructions. But as we moved towards the multi-core and many-core architectures the increased transistor counts provided the capability of adding larger caches in order to hide the memory latency. Ideally this should have provided a performance

Figure 1.1: Changes in memory access times

improvement in the order of the increased number of cores, but this was not the case. As the number of cores and size of caches increased, the memory traffic generated also grew proportionally proving the off-chip memory bandwidth to be the performance bottleneck.

An increased bus width can be a viable option to offset the increasing demands placed on the memory bandwidth providing higher throughput for the off-chip communication in turn increasing the memory bandwidth. The I/O pins available on the processor chip can be increased to provide wider bus widths. This solution is fundamentally limited by the fact that with every processor architecture generation number of cores are going to grow proportional to the area of the chip ( $C^2$ , where C is the length of one side of the chip)whereas the number of pins are going to be proportional to the perimeter of the chip ( $4 \times C$ ). The significant difference between the rate at which the core counts and pin counts are going to improve has made memory

Figure 1.2: Example of CSR and COO format

bandwidth a critical resource on multi-core and many-core processor architectures. In this thesis we are going to investigate the *Sparse Matrix Operations* which perfectly exemplify the performance ramifications faced due to the memory bandwidth limitations.

## 1.1 Sparse Matrix Operations

The Sparse Matrices are matrices with a large number of zero elements. They arise in a number of scientific applications like Finite Element Method, Economic Modeling, Page Rank, Graph Algorithms et al. The sparse matrix due to large number of zero elements employ specialized storage formats which only store the Non Zero (NZ) elements and associated metadata to indicate the location information (row column positions) of the NZ elements.

The two most commonly used storage format for sparse matrices are Compressed Sparse Row (CSR) and COOrdinate (COO) format. An example of these formats is shown in Figures 1.2. These formats result in 1-D partitioning of sparse matrices as the matrices are partitioned either by row or columns. We also have block based storage formats like Block CSR and Block COO. The block based formats rely on 2-D partitioning as the matrix is partitioned both by rows and columns.

An important operation involving sparse matrices is the Sparse Matrix-Vector

Multiplication (SMVM). The SMVM operation perform  $y = A \times x$  where A is a sparse matrix, x and y are dense vectors. The SMVM operation is of considerable importance due to its low floating point performance (measured in MFLOPS, or million floating-point operations per second) on modern computing platforms. The poor performance of the algorithms using the SMVM operation (varies between 10% to 33% theoretical peak rate of computation [2]) can be attributed to two factors: the basic matrix-vector multiplication operation and sparse nature of the matrix. If we consider general matrix-vector multiplication, we are performing  $O(n^2)$  floating point operations on  $O(n^2)$  elements. The ratio of floating-point operations to memory transactions is O(1). With the widening gap between between processor clocks (increased computation speeds) and memory speeds this ratio of O(1) cannot hide the latency of fetching data from slow memory to the fast computational unit, making matrix-vector multiplication memory bound in nature. The SMVM performance further deteriorates due to the sparsity of matrix involved. If we consider a NZ element represented using a single precision floating point we are performing two mathematical operations (a multiply and an add) on four bytes of data, resulting in a flop:byte ratio of 0.5. Now if we consider the specialized storage format we are using for storing the NZ elements we are also going to have some associated metadata in form of indexing information (location information) with the NZ element. Assuming we need two integers (eight bytes) to indicate the row and column to which the NZ element belongs we are now generating 12 bytes of memory traffic for performing two floating point operations, thereby further driving down the flop:byte ratio. Thus we are not only having low arithmetic intensity but we also have an increased traffic on the memory subsystem due to the index information associated with each NZ element. These two factors make the SMVM problem memory bandwidth bound in nature.

It is also important to consider the issue of memory latency in case of the SMVM operation. Although not memory latency bound, the memory access latency still has

a significant impact on the SMVM operation. It has been reported by Buluç in [3] that the Intel Nehalem processor takes four clock-cycles to perform two mathematical operations and around 24 clock-cycles to fetch the 12 bytes of the data associated with the NZ operand, resulting in 20 wasted clock-cycles when processor is idle. The gap is going to increase further over the next processor generations. In order to resolve the SMVM performance issues we need a solution which is not only capable of efficient utilization of memory bandwidth but also is agnostic to the memory latency.

# 1.2 Thesis Statement

The research efforts for the sparse matrix operations have been focussed on improving data resusability for operands involved other than the sparse matrix. This is a reliable approach considering sparse matrix does not offer any temporal locality (due to the usage of sparse matrix storage format) and hence limits the data reusability. The modest performance improvements obtained using the data reusability does warrant us to look at the problem from a different performance. The researchers have been continuously modifying storage formats to be capable of extracting maximum performance from the underlying memory subsystem which is intrinsic to a processor architecture.

We investigate the problem from the point of view of storage formats and how they have evolved over the decades. If we refer to Figure 1.3 we see that for almost three decades (1960s to late 1990s) the storage formats have been exclusively based on 1-D decomposition of sparse matrices. This resulted in formats which were essentially some variation of CSR or COO format based on the NZ distribution present within the matrix. But in late 1990s we see the first block based storage format in form of Block CSR [4] almost after three decades of development of the CSR format. The sudden need of block based storage format has its roots in the widening gap between processor and memory performance. If we refer to the Figure 1.1 we see that by the late 1980s the memory access time had significantly increased when compared to processor clock-

Figure 1.3: Evolution of sparse matrix storage formats

cycles, indicating the memory access latency to be a critical performance impediment. This resulted in development of processors with on-chip caches in late 1980s and addition of more level of caches by early 1990s. As the researchers recognized the performance gains provided by caching the focus shifted towards enhancing data reusability and hiding the cache miss latency.

In case of the BCSR format the reordering of the NZ elements was used in order to provide dense blocks which improved the reusability of vectors x and y. The block based formats only needed to store the location of the block and the relative position of the NZ elements was deduced from the block location information. This reduced the memory requirement for the index information of the block based approach which resulted in reducing the number of load operations. The newer block based formats developed after BCSR, like BCOO and VBL also continued to focus on memory latency issue and provided solutions accordingly. These formats were basically developed to address the performance needs of that time. As discussed before they predominantly focused on memory access latency and improving reusability of vector x,y and looked at any improvement in memory bandwidth utilization as an ancillary benefit, although the SMVM operation is memory bandwidth bound in nature. This approach essentially created a major disconnect between the needs of today's processor architectures and the original requirements for which these storage formats were designed. All the storage formats shown in Figure 1.3 (except CSB) were designed keeping memory latency as the key performance impediment. As the paradigm shift towards multi-core/many-core architectures provided an every increasing core count the focus moved towards the memory bandwidth. The increasing complexity of the memory subsystems and aggressive memory hierarchy designs to hide memory latencies resulted in contention of aggregate memory bandwidth available to the processor, making memory bandwidth a valuable resource.

This strengthened our hypothesis that the current storage formats are not suitable for the current and future architectures and this basically motivates the central question of this thesis:

As the memory bandwidth remains limiting issue on current and future processor architectures, will the usage of legacy sparse matrix storage formats prove detrimental for sparse matrix operations?

In order to answer this question we have developed a new storage format called *Variable Dual Compressed Blocks* [5]. Based on this format we will validate our hypothesis by considering the following key questions:

focuses on memory bandwidth efficiency?

By comparing the different storage formats and their shortcomings we can assess the requirements of a storage format which will be exclusively based around memory bandwidth. If this storage format can alleviate the factors that affect the memory bandwidth negatively then we will consider it to be a successful

• Is it possible to design a new storage format for the sparse matrices which

- design. We will also evaluate if the storage format solely can provide an average memory bandwidth efficiency of at least 60% for sparse matrix operations.

- Can developing a memory hierarchy for sparse matrix operations which works

in conjunction with new storage format provide high memory bandwidth efficiency and result in performance improvement for sparse matrix operations?

If the storage format on its own cannot provide an average 60% memory bandwidth efficiency then if using a customized memory hierarchy result in an aver-

age memory bandwidth efficiency of at least 60%. If we are able to achieve the projected target using the customized memory hierarchy we will consider it to be a successful design.

- Can this storage format be extended to the Sparse Matrix-Matrix Multiplication (SMMM) Operation?

If this storage format can be extended to design a new technique for the SMMM without using unordered merge operation then we will consider it to be a successful implementation. We will further discuss this metric in detail in Chapters 2.

- Can this storage format be extended to a scalable implementation of the sparse matrix operations?

If a parallel implementation of the sparse matrix operations using the new storage format can achieve at the minimum a 2X improvement in computation time over a sequential implementation for a parallel system then we will consider it to be a successful implementation.

The rest of this thesis is organized as follows. Chapter 2 provides the background knowledge on Field Programmable Gate Arrays (FPGAs), Xilinx Tool Chain, IEEE-754 floating point format and Unordered merge. We also discuss the performance impediments faced by the sparse matrix operations due to storage formats and a survey of the current state of research for the sparse matrix operations. In Chapter 3 we will discuss in detail the VDCB format we have developed and the customized memory hierarchies for SMVM and SMMM operation. Chapter 4 presents the experimental setup and the evaluation of performance metrics to validate the efficacy of our solution. Chapter 5 concludes with a brief summary of the research.

#### CHAPTER 2: BACKGROUND

This chapter provides an overview of the background knowledge used as groundwork for this research. We discuss the Field Programmable Gate Arrays in detail in Section 2.1. The capability of designing and implementing different functionalities on the FPGA is provided by the Xilinx tool chain. A brief overview of the Xilinx tool chain is provided in Section 2.2. The IEEE 754 floating point format and the multiplication/addition operations involving the format are used extensively throughout this work. An overview of the IEEE 754 floating point format and the mathematical operations is presented in Section 2.3. The problem of unordered merge which is relevant to the Sparse Matrix-Matrix Multiply operation is presented in Section 2.4. A custom high speed network which is used to study the scalability of the design presented in the later chapters is presented in Section 2.5. We discuss the Sparse Matrix Vector Multiplication (SMVM) operation and the various performance issues and current research efforts related to the SMVM operation in Section 2.6. The Sparse Matrix-Matrix Multiplication (SMMM) operation and the related performance impediments and a brief survey of the current state of the art for the SMMM operation are presented in Section 2.7

#### 2.1 Field-Programmable Gate Arrays

In order to design a customized memory hierarchy as part of the this research, we look at Field Programmable Gate Arrays (FPGAs). A Field Programmable Gate Array (FPGA) provides an Integrated Circuit (IC) which consists of a hardware fabric which can be configured for the needed functionality after it has been manufactured. The FPGAs can be programmed using the Hardware Description Language (HDL) to describe the functionality. They consist of a large number of logical resources and

Figure 2.1: High level view of FPGA device

Block RAMs (BRAMs) to implement complex designs. A vendor specific toolchain is used to synthesize the HDL into a bitstream which can be used to configure the FPGA. The flexibility and enormous amount of computational capacity offered by an FPGA device makes it a natural fit for designing custom memory hierarchy that matches the memory access patterns of the applications for which it is used.

The FPGA consists of arrays of Configurable Logic Blocks (CLB), I/O Blocks, routing networks and special purpose blocks as shown in Figure 2.1. The CLBs are composed of LookUp Tables (LUTs) which are used as a function generator, flip-flops which are used to hold states and special purpose circuitry for interconnection. The routing network consists of switch boxes which ensures connection between the various components of a design and the I/O blocks are capable of supporting a large number of I/O standards including Low Voltage Differential Signaling (LVDC), Low Voltage CMOS (LVCMOS).

A number of special purpose design blocks are already made available by the

FPGA vendors which can be used without any modifications. These are generally known as Intellectual Properties (IPs). There are two type of IPs: Soft IP and Hard IP. The Soft IPs are implemented using the FPGA logic resources and the user needs to explicitly instantiate these IPs in the HDL design. The Hard IPs are IPs which are already implemented within the FPGA fabric They generally consist of Processor Cores, DSP blocks, High Speed transceivers, Block RAMs. A detailed description of the inner workings of an FPGA device can be found in [6].

# 2.2 Xilinx Integrated Software Environment

The Xilinx Integrated Software Environment (ISE) is the front-end GUI of the Xilinx tools which are used to program the FPGA devices with the user-defined functionality. The user describes the design in a Hardware Description Language (HDL) like VHDL or Verilog and using netlists. The *netlist* is a collocation of logic units and the intermediate connections between the units. The Xilinx tools use a set of commands to convert the HDL description of a user design and netlists into a configuration file for the FPGA. The configuration file for the FPGA is known as a *bitstream* and it is used to place the various parts of a user design into the FPGA design components. We briefly describe the various steps it takes for the Xilinx ISE to convert an HDL design into a bitstream for the FPGA device. A more detailed description of the design flow is available in [7].

# • Xilinx Synthesis Tool (XST)

The Xilinx Synthesis Tool (XST) is used to convert an HDL design into a netlist. The XST tool performs HDL code parsing for checking the syntax and reports errors if present. The XST tool is able to perform FSM extraction and macro recognition for in-built logical units like Flip-Flops, logic gates and memory. It applies low level optimizations when available for timing, area and technology. Some of the optimizations can be selected by the user and some are recognized by the tool from HDL design description.

#### • NGCBuild

The NGCBuild compiles different netlists into one common netlist in the Xilinx proprietary format of .ngc. The NGCBuild opens the design hierarchy and traverses it recursively to find the netlists associated with different IPs and also applying any user constraints specified within the User Constraint File (UCF).

## • NGDBuild

The common netlist generated in the previous step of NGCBuild is converted into a Xilinx Native Generic Database (NGD) by NGDBuild. The NGD file contains the description of the netlist in terms of Xilinx primitives of LUTs, OR AND gates, memory and Flip-Flops. The design can now be mapped to a specific Xilinx device technology.

## • Map

The Map program is used for mapping a NGD file to a specific Xilinx device. The program first performs a Design Rule Check (DRC) on the design presented within the NGD file and then maps the design to the components of the specific Xilinx device technology. The output of Map is a Native Circuit Description (NCD) file which is used for placement and routing. An initial timing information for the design is available at this point and Setup checks can be performed. The Hold checks cannot be performed till the design has been routed by the tool.

#### • Place And Route (PAR)

The PAR accepts the NCD generated as output of Map and uses it for placement on the FPGA device. During placement the physical constraints are applied to the design using the specification provided in Physical Constraints File (PCF). The placement of the various design components is followed by the routing which is used to use the interconnection network present on the FPGA device to connect the physically placed design components. The routing step is the most time consuming step of the entire design flow. The complete timing information for the design is available at this point and a final NCD file is made available.

#### • BitGen

The NCD file available after PAR is used for generating the bitstream using BitGen.

A number of tool specific optimizations for area, power, performance and timing are available at each step of the design flow to cater to specific needs of the user defined design. The details of these options can be found in [7]

# 2.3 IEEE 754 Floating Point Format

The IEEE 754 floating point format is a binary representation for floating point numbers. It is a common standard established for representing floating point numbers across various architectures and providing portability for scientific code. The format provides two forms of representation: Single Precision (32-bit) and Double Precision (64-bit). The format has three components associated with it: Sign (S), Exponent (E) and Fraction (F). In general the IEEE 754 format can be represented using the following form:

$$(-1)^S \times F \times 2^E \tag{2.1}$$

The sign value can be '0' to represent a positive floating point number or a '1' to represent the negative floating point number. The IEEE 754 format uses a concept similar to the normalized scientific binary floating point representation where no leading zeros are present. In order to use this form of representation the format relies on exponent and fraction. The exponent part of the format represents the amount of decimal point shift to the left in order to have only a leading one. The fraction part of the format represents the trailing part after the decimal point once the left

|   | SIGN | EXPONENT | FRACTION |

|---|------|----------|----------|

| - | 31   | 3023     | 220      |

Figure 2.2: Single precision floating point representation

| SIGN | EXPONENT | FRACTION |

|------|----------|----------|

| 63   | 6252     | 510      |

Figure 2.3: Double precision floating point representation

shift operation has been performed to have only a leading one. In case of the single precision representation the *exponent* part can vary from -128 to 127 for signed values and 0 to 255 for unsigned values. The *exponent* for double precision representation varies from -1024 to 1023 for signed values and 0 to 2047 for unsigned values. An example of single and double precision representation is shown in Figures 2.2 and 2.3. The format also has reserved bit patterns for representing zero, Not a Number (NaN), positive and negative infinity.

The selection between single and double precision formats is based on the requirement of the application. The double precision format can be used over single precision when a better precision is required (increased fraction bits) and the chances of underflow/overflow have to be reduced. The double precision format increase the memory requirement and can reduce the speed of operation due to higher number of bits needed for its representation.

# 2.3.1 IEEE 754 Floating Point Multiplication

The multiplication operation is heavily used in this research for the different sparse matrix operations we have performed. In this section we will discuss the floating point multiplication operation when using the IEEE 754 floating point format.

The floating point multiplication is performed by adding the exponents of the two operands and multiplying the fractions together. Before the actual operation begins a check is performed to see if any of the operands is zero. If we consider the two operands: x represented in IEEE 754 format as  $-1^{S_x} \times F_x \times 2^{E_x}$  and y represented using  $-1^{S_y} \times F_y \times 2^{E_y}$ , then the product  $z = x \times y$  is calculated using the following steps:

•

$$S_z = S_x \oplus S_y$$

$$\bullet \ E_z = E_x + E_y$$

•

$$F_z = F_x \times F_u$$

$$\bullet \ z = -1^{S_z} \times F_z \times 2^{E_z}$$

The final result is checked for overflow which can occur quite frequently in case of the multiplication due to increased bit requirement (48-bits for the fraction in case of single precision and 106-bits for the fraction in case of double precision). In case of no overflow the correct rounding scheme is applied to ensure the result is within the precision limit. In case of overflow a suitable flag is set along with the result indicating the overflow.

#### 2.3.2 IEEE 754 Floating Point Addition

The addition operation is used for the implementation of the accumulator (3.2.1.1) which is part of the hardware design implemented in this research. The addition operation is more complex than the multiplication operation due to the need of comparison operation between the exponents of two operands and aligning the fraction components accordingly.

If we consider the two operands: a represented in IEEE 754 format as  $-1^{S_a}$  ×

$F_a \times 2^{E_a}$  and b represented using  $-1^{S_b} \times F_b \times 2^{E_b}$ , then the sum c = a + b is calculated using the following steps:

- Align the fraction part of the operands based on the exponents

- If  $E_a > E_b$  perform right shift on  $F_b$  until  $F_b$  equals to  $F_b \times 2^{E_b E_a}$

- If  $E_b > E_a$  perform right shift on  $F_a$  until  $F_a$  equals to  $F_a \times 2^{E_a E_b}$

- Compute sum of the aligned fractions

$$F_c = F_a + F_b$$

- $E_c = E_a$

- $S_c = S_a$

- $c = -1^{S_c} \times F_c \times 2^{E_c}$

## 2.4 Unordered Merge

The merge operation is equivalent of an AND operation. When performing a merge operation between two lists the resultant list will consist of elements from the two list if and only if the element belongs to both the operand lists. An example of the merge operation can be seen in Figure 2.4, where  $List\ A$  and  $List\ B$  are the input lists for the merge operation and  $List\ C$  is the new resulting from the merge operation.

Figure 2.4: Example of unordered merge

It can be seen from the example presented in Figure 2.4 that performing the merge requires a search and compare between the two input lists (List A and List

B) making it a fairly expensive operation. The merge operation when used with the sparse matrix storage formats has to parse the list of columns and rows in order to perform the required sparse matrix mathematical operation. A lot of times the column indices associated with a row are not in the increasing order in which they occur within the matrix resulting in an unordered list. This makes the search and comparison operations more complex. Lets consider an example of two lists: list 1 and list 2 consisting of column indices arranged in an increasing order and used for merge operation. If list 1 provides an element A larger than element B provided by list 2, then all the elements preceding B are not used for the search operation as they are going to be smaller than the element A (due to increasing order of column indices) and this will reduce the number of elements over which a search and compare has to be performed. Thus a merge operation over an unordered list (unordered merge) becomes more expensive as every time a search operation has to be performed over all the elements of the two lists, making unordered merge an expensive operation.

#### 2.5 Architecture Independent REconfigurable Network

The Architecture Independent REconfigurable Network (AIREN) is an integrated on-chip/off-chip network that supports node-to-node communication. The AIREN interface has enabled us to implement and study the scalability of our design presented in Sections 3.2.2.1, 3.5.4. The AIREN interface consists of an AIREN Router supporting the Xilinx LocalLink Interface [8]. The router provides the ability to connect compute cores to a network including both on-chip and off-chip compute cores. The routing module present within the router is used to make the routing decisions based on the interconnection network used. The router uses the dimensional order routing for the routing decision. The router can be configured to support various network topologies. In order to support node-to-node communication AIREN interface uses the high speed transceivers present on the FPGA. The AIREN interface also uses the locallink interface to assemble the packets for the router. A packet consists

of a Start of Frame (SOF) and End of Frame (EOF) along with the payload. The locallink interface enables flow control to be incorporated for the transaction made on the AIREN network. The locallink interface uses Source ReaDY (SRDY) and Destination ReaDY (DRDY) to implement flow control. The locallink interface is a light weight protocol and incurs a very small amount of overhead. A more detailed description for AIREN can be found in [9, 10].

## 2.6 Sparse Matrix Vector Multiplication

The Sparse Matrix Vector Multiplication is used in a number of scientific and engineering problems (e.g. Finite Element Method, Conjugate Gradient, Page Rank). The operation performs  $\vec{y} = A \times \vec{x}$  where, A is a sparse matrix and  $\vec{x}$  is a dense vector.

## 2.6.1 Performance Issues of Sparse Matrix Vector Multiplication

In order to develop a Sparse Matrix Storage format which is centered around memory bandwidth we need to understand the shortcomings of the pre-existing storage formats. We use the CSR format which is the oldest and most commonly used sparse matrix storage format to highlight the performance limitations incurred by the memory subsystem when performing the SMVM operation. We look at an example presented in Algorithm 1 for performing the SMVM operation using the CSR format.

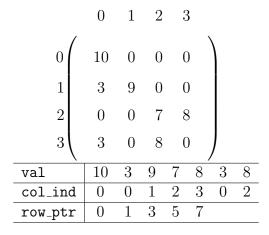

Figure 2.5: Example of CSR format

We list the memory subsystem impediments that will arise using this particular implementation (Algorithm 1) of the SMVM operation as follows:

```

\begin{array}{l} \textbf{Input: Number of rows, row\_ptr, col\_ind, val, } x \\ \textbf{Output: } y = A \times x \\ \textbf{for } i \rightarrow 0 \textbf{ to } rows \textbf{ do} \\ & | \textbf{ for } j \rightarrow row\_ptr[i] \textbf{ to } row\_ptr[i+1] - 1 \textbf{ do} \\ & | y[i] += val[j] \times x[col\_ind[j]]; \\ & \textbf{ end} \\ \end{array}

```

Algorithm 1: SMVM using CSR storage format

- Additional load operations are incurred for the index information of the NZ element in form of row\_ptr and col\_ind. These particular operations do not contribute towards the actual SMVM computation

- The indirect memory access takes place via row\_ptr for col\_ind and NZ values

- $\bullet$  Indirect and irregular memory access on x

We can see all the three performance impediments are related to the storage format and are going to affect the available memory bandwidth negatively. If we look at the first two impediments they are directly related to the storage format. The problem here is two-fold: firstly we have additional load operations in form of the indirect memory access that takes place for the row\_ptr and col\_ind. Secondly, these load operations are going to be used only for the purpose of correct indexing of val array and not for any useful computation, driving down the flop:byte ratio.

The third impediment is due to the sparsity pattern of the matrix involved and not so much related to the storage format. If we have matrix in which a large number of NZ elements are present in the same column then all of them will access the same value of x and result in improving reusability of x. This might require reordering of the NZ elements of the matrix and inclusion of zero-padding in order to improve temporal locality on x. As the performance gains using this particular approach will be highly dependent on the NZ element distribution within the matrix and up to what extent can these elements can be rearranged, we will not address this particular aspect when developing our storage format.

Based on this discussion we can summarize the two main issues that need to be addressed by a new storage format as follows:

- Can we minimize the number of additional load operations that take place for the index information of the NZ elements?

- Can we minimize or possibly eliminate the indirect memory access that are present within the storage formats?

## 2.6.2 Related Work for the SMVM Operation

There has been a significant interest in implementing the SMVM operation on an FPGA and other compute accelerators (such as IBM Cell Broadband Engine, GPGPUs, and others). Below we explain how this work fits within the context of prior efforts.

## 2.6.2.1 FPGA Implementations

The FPGAs have been actively pursued over the past decade for SMVM kernel. The main premise in a lot of these research advances have been essentially to increase the computation speed to compensate for the poor memory utilization.

The work done by Zhou et al. in [11] is one of the first research efforts on performing floating point SMVM on FPGAs. The sparse matrices used are stored in traditional CSR format and the FLOPS are improved by parallelizing the multiplication and addition of non-zero elements of a row. The paper proposes a tree-based architecture comprising of floating point adders and multipliers to achieve this. Although innovative, the splitting of rows requires padding of zeros or merging of rows together to provide the required number of operands to the multiplier nodes of tree. The zero-padding is a wasteful operation and degrades the total floating point performance by increasing the number of idle cycles and merging sub-rows from two different rows subsequently increases the complexity of the accumulation circuit.

A seminal work presented in [12] discusses the need of using off-chip memory

for storage of matrices and addresses the issue of increased latency due to off-chip memory requirements of larger matrices. The design presented, focuses on matrix reordering and providing a cache based memory structure for improving the overall performance of SMVM kernel.

## 2.6.2.2 Impact on Multi-Core Platforms

A comprehensive and detailed study on latest multi-core platforms has been performed in [13] for SMVM kernel. An exhaustive set of optimizations based on matrices and underlying architecture are used for improving performance. The results presented show *Cell Blade* (one of the platforms studied) provides a consistently high floating-point performance when compared to other state of the art architectures used. This seems contrary to popular approach for speedup, as Cell Blade has a relatively slower floating-point unit. But an essential factor on achieving speedup is the fact that Cell Blade due to its memory organization effectively utilizes the available memory bandwidth.

A number of GPU implementations of SMVM are also available. The work presented in [14] provides optimization strategies to efficiently map tasks to the GPU threads. Also, a thorough implementation of SMVM using different storage formats on a GPU is presented in [15].

#### 2.6.2.3 Algorithmic Advances

An active area in terms of algorithms regarding SMVM has been the storage format used for sparse matrices. A blocked representation of sparse matrix using CSR called BCSR format was proposed by Pinar et al. in [4]. One of the most recent developments in storage format has been Compressed Sparse Block (CSB). It has shown promising performance for multi-core platforms. The researchers involved in developing CSB have also proposed a bitmasked implementation of CSB in [3]. Although, the premise is similar to our storage format, there are some significant differences. The bitmasked implementation of CSB does not have a concept of *Block*

Header, which necessitates an offline analysis of the entire matrix to determine the number of zeros within a block and the parallelization decisions are made based on this analysis. Also, VDCB tries to represent matrix as a group of variable-sized dense blocks unlike CSB, which envisions matrix as a group of constant sized sparse blocks.

# 2.7 Sparse Matrix Matrix Multiplication

The Sparse Matrix-Matrix Multiplication (SMMM) operation is used to compute  $C = A \times B$  where both A and B are sparse matrices. The SMMM operation is used frequently in graph algorithms such as Breadth First Search, Cycle Detection, Peer-Pressure Clustering etc. A significant amount of research effort has been invested towards the Dense Matrix-Matrix Multiplication (DMMM) and has resulted in a number of cache friendly optimizations like software-prefetching, register-blocking etc. These performance optimizations have been implemented to hide memory latency and to increase the data reuse. Although applicable towards the SMMM operation to a certain extent, the performance gains using these techniques are not significant when compared to the DMMM operation.

#### 2.7.1 Performance Issues of SMMM Operation

The naïve approach for matrix-matrix multiplications uses  $O(n^3)$  operations, where  $n \times n$  is the size of matrix. To reduce the number of operations, fast matrix multiplication algorithms such as Strassen and Coppersmith-Winograd are widely used. The complexity for these algorithms varies from  $O(n^{2.78})$  to  $O(n^{2.375})$ . This indicates the number of multiplication operations are dependent on the size of the matrix and not on the Number of Non-Zero (NNZ) elements present within the matrix. This is a desirable feature in case of dense matrices where the NNZ is  $O(n^2)$ . It indicates that the NNZ elements will grow proportionally with the size of the matrix and hence having an algorithm where complexity is a function of the size of matrix  $(n \times n)$  instead of NNZ elements is more suitable. But in case of sparse matrices these algorithms provide an over-estimation of the number of multiplication operations that are actually

Figure 2.6: Basic matrix multiplication

| val     | 10 | 3 | 9 | 7 | 8 | 3 | 8 |

|---------|----|---|---|---|---|---|---|

| col_ind | 0  | 0 | 1 | 2 | 3 | 0 | 2 |

| row_ptr | 0  | 1 | 3 | 5 | 7 |   |   |

| val        | 2 | 1 | 4 |   |   |

|------------|---|---|---|---|---|

| $col\_ind$ | 1 | 0 | 2 |   |   |

| row_ptr    | 0 | 1 | 1 | 2 | 3 |

Figure 2.7: CSR Multiplication Example

needed. For sparse matrices NNZ is  $o(n^2)$  and the general trend is that as the size of matrix increases the NNZ elements reduce. If we have two sparse matrices with a and b NNZ elements respectively, then the number of multiplications operation required are around O(ab). Hence the available fast matrix multiplication algorithms do not utilize the sparse nature of matrices involved and end up performing more number of multiplication operations than are actually needed. It can be seen from Figure 2.6 that only six multiplications are needed (due to large number of zero elements) for the resultant matrix C. But if a naïve implementation is used we are still performing 64 multiplications in order to calculate the final result.

Another layer of complexity is added to this problem due to the usage of sparse matrix storage formats. In order to determine the NZ elements from the matrices which are going to multiply an unordered merge has to be performed between the indexing elements of the two matrices. If we assume both matrix A and B are represented in the CSR format then the multiplication will take place as shown in Figure 2.7.

In order to perform multiplication using the CSR format the row\_ptr of matrix B has to be decoded in order to find out the row positions of its NZ value. Then each decoded row positions have to be compared with each col\_ind of matrix A.

This process has to be repeated with every row position of matrix B. This essentially results in performing an unordered merge (Section 2.4) between rows of matrix B and columns of matrix A. Although this method provides a means of avoiding unnecessary multiplication which take place in the naïve implementation; the unordered merge that needs to be performed is a very expensive operation and results in performance deterioration.

Hence another requirement that the new storage needs to address is:

Can the new storage format perform the SMMM operation without the unordered merge and unnecessary multiplications with the zero elements?

## 2.7.2 Related Work for the SMMM Operation

The classic SMMM algorithm developed in [16] is one of the seminal works for this problem. The algorithm uses the traditional CSR format for computing the product of two sparse matrices. The MATLAB CSparse operation is based on this particular algorithm. A fast sparse matrix multiplication has been proposed by Yuster and Zwick in [17]. The proposed algorithm is not specifically used in conjunction with a format. It uses fast rectangular dense matrix multiplication for performing the multiplication for permutation matrix. The complexity of this algorithm is around  $O(m^0.7n^1.2 + n^{(2+o(1))})$  where m and n represent the number of rows and columns of the resultant matrix. The work done by Sulatycke and Ghose in [18] discusses the impact of indirect memory accesses on the performance of the SMMM operation. They also propose a loop-interchange technique for improving the performance of the SMMM operation and demonstrate a multi-threaded implementation of the proposed technique. The work done by Buluç and Gilbert in [19] discusses the scalability issues of the SMMM operation. They also use a new storage format called Doubly Compressed Sparse Columns (DCSC) which is a modification of the CSC format for the implementation of the SMMM operation.

The research efforts for SMMM operation on the FGPAs is still in nascent state.

One of the initial work on the SMMM is done by Lin et al. in [20]. The work deals with the energy efficiency of implementing the SMMM operation on FGPAs and uses the CSR format for the matrices. This work is further extended to design an analytical model for matrix-multiplication on FPGAs focusing on the SMVM and the SMMM operation are suggested in [21].

#### CHAPTER 3: DESIGN

The premise of this research is that the currently available storage formats are not memory bandwidth friendly and in turn result in performance deterioration for sparse matrix operations. In order to validate this argument we looked at the shortcomings of the currently available sparse matrix formats and develop a new storage format known as the Variable Dual Compressed Blocks (VDCB). Our work focuses not only on the development of the storage format but also on the feasibility of this format to perform the sparse matrix operations in a computationally efficient manner. We have hypothesized in Chapter 1 that the inefficient utilization of the memory bandwidth when performing sparse matrix operations is not solely due to the shortcomings of the storage formats but also the inherent processor memory hierarchy.

We evaluate our hypothesis by examining if the VDCB format independently can serve the performance deficits suffered by the sparse matrix operations or the memory hierarchy present in the processor architectures is also responsible for performance degradation. In order to examine our argument we must have a two-fold approach when developing the experimental setup. Firstly we need to use the VDCB format by itself to perform the sparse matrix operations in software. This will help in understanding if the performance shortcomings are only due to the storage format and independent of the conventional memory subsystem. Secondly we need to develop a memory hierarchy to work in conjunction with the VDCB format to perform specific sparse matrix operations. The comparison of the performance from these two approaches will help us to answer our hypothesis. We have selected two sparse matrix operations for the purpose of design development: Sparse Matrix Vector Multiplication (SMVM) and Sparse Matrix Matrix Multiplication (SMMM). Based on the

discussion above we classify the high level design into two categories:

## • Hardware/Software Co-Design Solution

In this solution a memory hierarchy is developed using the FPGAs to work in conjunction with the VDCB format to perform the SMVM and SMMM operations

# • Software Only Solution

In this solution a software code is developed to use a VDCB encoded sparse matrix to perform the SMVM and SMMM operation on a conventional processor

### 3.1 Variable Dual Compressed Blocks

Based on our discussion presented in Sections 2.6.1 and 2.7.1 we list out our expectations from an ideal storage format.

- Limits the number of indirect memory accesses

- Provides a low overhead for adding the location information of non-zero element

- Agnostic to the sparsity structure

The various formats available for sparse matrix storage differ from each other in how the index information for a NZ element is stored. The indirect memory access happening in CSR, is also present for all the currently available storage formats. An optimization proposed for reducing indirect memory access is to minimize the amount of index information needed to determine the NZ element position. This reduction in index overhead is used in block based storage formats like BCSR[4] and Compressed Sparse Blocks (CSB)[22]. Relevant information required for determining block position within a matrix is only stored for these formats. Also, blocking improves the cache reusability of the vector for SMVM[23].

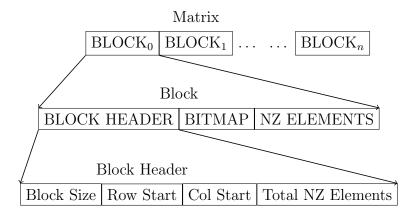

An ideal storage format should limit the number of indirect memory accesses and have a low memory overhead for adding the location information of NZ element. To

Figure 3.1: VDCB format

achieve this we have developed a storage format called Variable Dual Compressed Blocks (VDCB). The VDCB format works by dividing a matrix into a number of smaller variable sized sub-matrices. These sub-matrices are referred to as BLOCKS. Each block has three components associated with it as shown in Figure 3.1. The first component is a Block Header; it consists of all the parameters needed to define the location of a block within a matrix. The second component is a Bitmap and it is used to store relevant index (location) information of NZ elements associated with a block. The bitmap sets a one to indicate the presence of a NZ element within a block and zero otherwise. The last component of the format is the double precision NZ elements present in a block.

### 3.1.1 VDCB Encoder Software Design

The sparse matrices are only available in the commonly used storage formats like CSR and COO. This makes it essential to develop an encoding software which is able to accept a sparse matrix encoded in CSR/COO format and generate the corresponding VDCB encoded sparse matrix. We use a simple heuristic for generating the VDCB storage format from a COO encoded sparse matrix, as shown in Algorithm 2. The heuristic selects blocks based on their densities. Currently we are only using multiples of eight for block sizes and the largest block size we can support is 64x64. We have developed the search code using C++ Standard Template Library (STL).

```

Input: Number of block_rows, block_row_count

Output: Generate VDCB format for each block_row

while block\_row \neq empty do

set_vector_x = block_row_begin;

set_vector_y = block_row_end;

ldim = set_vector_y - set_vector_x + 1;

for j \rightarrow set\_vector\_x to set\_vector\_y + ldim do

Push all row, column elements of block_row in temporary block \rightarrow

temp\_block;

Push all non-zero elements of a block_row in temporary block \rightarrow

nnz\_search\_block;

end

while temp\_block \neq empty do

Determine the starting search coordinates of temp_block;

for i \rightarrow 1 to 8 do

Search blocks of sizes in multiple of 8 using starting search

coordinates;

Choose the block with highest density \rightarrow final_block;

Select larger block if multiple blocks have same density;

Remove row, col from temp_block that correspond to final_block;

Generate block header for final_block;

Generate bitmap for final_block;

Remove non-zero elements corresponding to final_block from nnz_

search_block;

end

end

end

```

Algorithm 2: Search heuristic

The STL provides a rich set of generic algorithmic solutions for search, sort and insertion that can be applied to user-defined data structures easily. We have used matrices from University of Florida Matrix Market Place[24], for testing our software and hardware design.

#### 3.1.2 Definitions

Definition 1. If the blocks or NZ elements are arranged in order of increasing rows, the storage scheme is referred as Row Major Ordering.

Definition 2. If the blocks or NZ elements are arranged in order of increasing columns, the storage scheme is referred as Column Major Ordering.

Definition 3. A Block Row is used to represent a collection of consecutive rows of a matrix when constant block sizes are used. The number of block rows for a matrix is given by equation:

$$\beta = \frac{n}{b} \tag{3.1}$$

where  $n \times n$  is the size of the matrix,  $b \times b$  is the constant block size and  $\beta$  is the total number of block rows. Similarly, a set of consecutive columns of a matrix when constant block size is used for a *Block Column*. The number of block columns of a matrix is given by Equation 3.1.

Definition 4. The collection of consecutive block rows is referred as Super Block. The number of super blocks present within a matrix is given by equation

$$S_B = \frac{\beta}{S} \tag{3.2}$$

where  $S_B$  is the number of Super Blocks present within a matrix,  $\beta$  represents the total number of block rows present within a matrix and S is the size of each Super block.

# 3.1.3 Notations Used

Table 3.1: Notations used

| Symbol         | Description                                                                   |  |  |

|----------------|-------------------------------------------------------------------------------|--|--|

| V              | Total Number of Blocks encoded in the VDCB format for matrix $A$              |  |  |

| $\gamma$       | Size of a block encoded in the VDCB format                                    |  |  |

| $A_V$          | Represents the array of all the $V$ blocks encoded in the VDCB format         |  |  |

|                | of matrix $A$                                                                 |  |  |

| $A_V[i]$       | Represents the $i^{\text{th}}$ block from array $A_V$ of matrix $A$           |  |  |

|                | when encoded in the VDCB format                                               |  |  |

| $A_V[i]_{XY}$  | Represents the block-header of $i^{\rm th}$ block                             |  |  |

|                | of matrix $A$ , where $X, Y$ are Row-Start and Col-Start fields               |  |  |

| $A_V[i]_{BMP}$ | Represents the bitmap associated with the $i^{\text{th}}$ block of matrix $A$ |  |  |

| $A_V[i]_{NZ}$  | Represents the NZ-array associated with the $i^{\rm th}$ block of matrix $A$  |  |  |

| $A_{XY}$       | Block of matrix-A encoded in the VDCB format with X,Y                         |  |  |

|                | denoting the Row-Start, Col-Start field of the block header                   |  |  |

| $B_{UV}$       | Block of matrix-B encoded in the VDCB format with U,V                         |  |  |

|                | denoting the Row-Start, Col-Start field of the block header                   |  |  |

| $BMP_{XY}$     | Row-Major bitmap of $A_{XY}$                                                  |  |  |

| $BMP_{UV}$     | Column-Major bitmap of $B_{UV}$                                               |  |  |

| $NZ_{XY}^A$    | NZ elements present in $A_{XY}$                                               |  |  |

| $NZ_{UV}^B$    | NZ elements present in $B_{UV}$                                               |  |  |

| $bmp_m^A$      | Bitmap associated with the m-th row of $A_{XY}$                               |  |  |

| $bmp_n^B$      | Bitmap associated with the n-th column of $B_{UV}$                            |  |  |

| $nz_m^A$       | NZ-element array associated with $bmp - A_m$                                  |  |  |

| $nz_n^B$       | NZ-element array associated with $bmp - B_n$                                  |  |  |

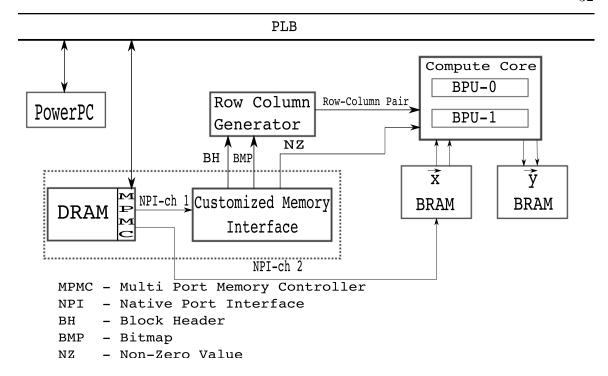

Figure 3.2: High level architecture for SMVM operation

### 3.2 Hardware Design for Sparse Matrix Vector Multiplication

In this section we will discuss the customized memory subsystem and the computation core design used to perform the SMVM operation on a matrix encoded in the VDCB format. This hardware design will provide us the evaluation platform for the SMVM operation when Hardware/Software Co-Design approach is used with the VDCB format to perform the operation.

### 3.2.1 Sequential Hardware Design

The top level sequential hardware design consists of three subsystems: Customized Memory Interface (CMI), Row Column Generator (RCG) and Block Processing Unit (BPU) as shown in Figure 3.2.

### 3.2.1.1 Block Processing Unit

When performing SMVM operation using VDCB format, matrix vector multiply operation takes place for each block. This generates a partial result vector for each block. The final resultant vector  $\vec{y}$  is a sum of all the partial results computed.

In our previous work we identified the high latency of accumulation operation to be a major performance deterrent [5]. We alleviate this problem by implementing single cycle accumulation loop floating point accumulator (based on the work presented in [25]) for the purpose of calculating partial results for each block. The single cycle accumulation loop ensures, that every time a row within a block is switched, we have to wait only for a clock-cycle before applying new sets of inputs. The BPU trigger is controlled by a Finite State Machine (FSM) which starts all the computation operations only when the  $\vec{x}$  has been read into the BRAM. The results generated by the accumulation loop need to be normalized to the standard IEEE-754 floating point format. We have modified the partial result accumulator to function as a simple loop back adder for the final stage of accumulation. In the final stage of accumulation we perform the normalization operation which is skipped in the partial result accumulation. The normalization operation takes about four clock cycles and is not implemented in the partial result accumulator, as it will be a redundant step. The blocks are interleaved in software in such a way that two consecutive blocks do not have any common rows. This avoids race conditions when the results have to be written to  $\vec{y}$ . The BPU operates at 100 MHz. The Computation Unit (CU) supports two BPUs (Figure 3.3) enabling us to perform matrix vector multiplication on two blocks in parallel. The vectors  $\vec{x}$  and  $\vec{y}$  are shared between the two BPUs. Both the vectors are stored in true dual-port Block-RAMs (BRAM) providing us the capability of issuing two read requests in parallel for  $\vec{x}$  and  $\vec{y}$ .

The inclusion of normalization step for final result accumulator provides a total latency of six clock cycles for the final stage adder. This latency might cause a data hazard if the operand from result BRAM  $(\vec{y})$  is needed before it has been written to it. This happens if partial results corresponding to the same row are applied to final stage accumulator in an interval smaller than the final stage adder latency. To avoid this we interleave the blocks in software in such a way that no two consecutive blocks