# ACCELERATED AGING AND HEALTH MONITORING OF IGBT(s) SWITCHES IN MOTOR DRIVERS

by

Paul Richard Valentine O'Connor

A thesis submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

Charlotte

2014

| Approved by:         |  |

|----------------------|--|

| Dr. Robert W. Cox    |  |

| Dr. Yogendra Kakad   |  |

| Dr. Madhav Manjrekar |  |

©2014 Paul Richard Valentine O'Connor ALL RIGHTS RESERVED

#### **ABSTRACT**

PAUL RICHARD VALENTINE O'CONNOR. Accelerated aging and health monitoring of IGBT(s) in Motor Drives. (Under the direction of DR. ROBERT W. COX)

There has been a proliferation in the use of power electronic drives in applications such as ships, aircrafts, and industrial machines. And as such, power electronic converters are playing a more crucial role in mission critical operations. Maintainability or extended operation, are often required during mission critical operations are thus becoming more valuable. The operation of these devices must be achieved with the utmost safety, reliability and repeat-ability and thus the need arises for these assets to be monitored. Diagnostic algorithms have been developed to use certain key performance indicators (KPIs) to detect incipient failures in electric machines and drives. And with new advancements in digital systems and cloud based analysis, it is becoming increasingly more likely that one can acquire the signals needed to perform incipient fault detection and offload these to computing platforms that can perform deep predictive analytics. It is with this knowledge base that this thesis proposes the development and implementation of a proof-of-concept offline incipient fault detection - OFID scheme for Insulated Gate Bipolar Transistors - IGBT(s). The thesis demonstrates a general algorithm that can be used for fault detection. The data acquisition process and the fault detection algorithm being tested on a working prototype AC drive are also presented. Considered also, is the creation of faults using accelerated aging schemes. With the OFID scheme proposed in this thesis, poof of viability of an online incipient fault detection scheme for IGBT(s) is given. And it is with this, potential benefits of lifetime extension of assets, improved controllability, safety and reductions in operating and maintenance costs can be attained.

# **DEDICATION**

I would like to dedicate this thesis to my two guiding stars my Mom Adel E. O'Connor, my Dad Paul R. V. O'Connor Sr. and the rest of my family.

#### **ACKNOWLEDGMENTS**

I would first like to thank all the members of my committee for their assistance in helping me achieve this goal. I would like to emphatically thank Dr. Robert Cox for his work as my mentor, teacher and advisor. I greatly appreciate all the hard work he has put in order to help me become a better engineer. The success of this thesis would not have been, if not for his efforts. I would like to thank Stephanie for putting up with my constant confusion about all grad. School deadlines. To all my lab mates, I would like to extend my thanks, because my success is due in part your camaraderie. The simple tasks of brain storming with me, give me advice or simply just making me get out of the lab to clear my head. These acts of kindness often times gave me the motivation to continue and for this I give my thanks. Last but definitely not least I would like to thank mom Adel O'Connor, my dad Paul O'Connor, my brothers Peter and Demisco O'Connor and my girlfriend Nachella Neal. My whole success is in no small part due to you all. Thank you for the guidance, love and support that you all, always provide. I am forever indebted.

# TABLE OF CONTENTS

| CHAPTER | 1: INTRODUCTION                                     | 1  |

|---------|-----------------------------------------------------|----|

| 1.1     | Motivation                                          | 2  |

| 1.2     | Proposed Approach                                   | 5  |

| 1.3     | Thesis Outline                                      | 6  |

| CHAPTER | 2: IGBT FAILURE MECHANISMS                          | 8  |

| 2.1     | IGBT Structure and Operation                        | 8  |

| 2.2     | Intrinsic IGBT Failure Mechanisms                   | 13 |

| 2.2.1   | Latching Failure                                    | 13 |

| 2.2.2   | Catastrophic Dielectric Breakdown                   | 13 |

| 2.2.3   | Time Dependent Dielectric Breakdown                 | 14 |

| 2.2.4   | Electron Migration                                  | 14 |

| 2.3     | Extrinsic Failure Mechanisms for IGBT               | 15 |

| 2.3.1   | Wire Bond Lifting                                   | 15 |

| 2.3.2   | Solder Die Detachment                               | 16 |

| 2.3.3   | Contact Migration                                   | 16 |

| CHAPTER | 3: METHOD FOR FAULT DETECTION AND DIAGNOSIS         | 17 |

| 3.1     | Methods for Fault Detection for IGBT in Motor Dives | 17 |

| 3.1.1   | IGBT Open Circuit Faults                            | 18 |

| 3.1.2   | IGBT Short Circuit Faults                           | 20 |

| 3.1.3   | IGBT Intermittent Gate-Misfiring Faults             | 22 |

| 3.2     | Algorithm Development                               | 23 |

| CHAPTER | 4: SWITCH CONDITION MONITORING OF IGBT(s)           | 29 |

|        |                                                                          | vii |

|--------|--------------------------------------------------------------------------|-----|

| 4.1    | System Setup Overview                                                    | 29  |

| 4.2    | Drive Architecture                                                       | 30  |

| 4.2.   | .1 50 kHz Sampling for Switch Condition Monitoring                       | 31  |

| 4.2.   | .2 100MHz Sampling for Switch Condition Monitoring                       | 37  |

| 4.3 Fe | eature Extraction                                                        | 38  |

| 4.4 IC | BT Degradation for Testing                                               | 45  |

| 4.4.   | .1 IGBT Aging due to Chronic Temperature over stress and Thermal Cycling | 47  |

| 4.4.   | .1 IGBT Aging due to Power/Thermal Cycling Setup                         | 51  |

| CHAPT  | ER 5: RESULTS                                                            | 53  |

| 5.1 La | atch up Failure due Chronic Temperature Overstress                       | 54  |

| 5.2 Ga | ate Resistance Induced Die Attach Breakdown.                             | 56  |

| CHAPT  | ER 6: SUMMARY AND FUTURE WORKS                                           | 59  |

| 6.1    | Summary                                                                  | 59  |

| 6.2    | Future Works                                                             | 59  |

| REFERI | ENCES                                                                    | 62  |

| APPENI | DIX A: MATLAB CODE                                                       | 70  |

| A.1    | Health Monitoring Algorithm Code                                         | 70  |

| A.2    | Drive KPI Extraction                                                     | 75  |

| A.3    | Data Collection Code                                                     | 82  |

#### CHAPTER 1: INTRODUCTION

The power electronics market is one of the world's most vibrant industry sectors, with some estimates projecting a compound annual growth rate of 7.74% from 2014 to 2020 [1]. This growth is often attributed to the fact that power electronics are a critical enabling technology, central to the performance of large and complex systems. Efficient and effective power conversion is essential to the adoption of renewables, the advent of electric propulsion, and the growth of "Big Data". Failures in such systems, can be catastrophic, and thus designers have developed schemes in which power converters are reconfigured once hard faults (i.e. shorts/opens) have been detected. If faults can be detected at an earlier or incipient stage, then reconfiguration can occur under conditions that allow for safer mode transitions. With new advancements in digital systems and cloud based analysis, it is becoming increasingly more likely that one can acquire the signals needed to perform incipient fault detection and offload these to computing platforms that can perform deep predictive analytics.

This thesis assumes that such trends will continue and thus proposes a fault detection (FD) system designed to exploit new digital systems to sense incipient faults in Insulated Gate Bipolar Transistors (IGBTs), which are the most common semiconductor switches in high power drives. The thesis itself reviews common IGBT failure mechanisms and demonstrates how fault indicators can be extracted using advanced systems. It also demonstrates a general algorithm that can be used for fault detection. The

data acquisition process and the FD alg. are tested on a working prototype AC drive. The creation of faults using accelerated aging schemes is also considered. The remainder of this chapter explains the motivation and, proposed approach of this thesis.

#### 1.1 Motivation

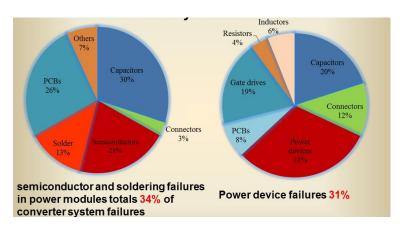

Power electronics are critical to growth in a number of sectors, including, electric propulsion, power generation, and data centers. Failures in such systems can thus have a devastating impact, but failure mechanisms are only recently being understood. Two recent studies have attempted to catalogue failures in power controllers, with both showing that power device and associated soldering failures account for roughly 1/3 of all issues (See Figure 1.1). Power and thermal cycling are the primary cause, as most converters have dynamic loads that cause thermal expansion and contraction. This phenomenon stresses internal boundaries between material layers and ultimately causes devices to wear out. As the wear out occurs, electrical and thermal characteristics change. Voltage losses and therefore power losses also increase. Thermal resistances also rise, leading to higher junction temps. Such changes can be observed, but they are only slight and thus measurements can be difficult and expensive.

Figure 1.1: Pie charts outlining the Power converter failure distribution [85] [23].

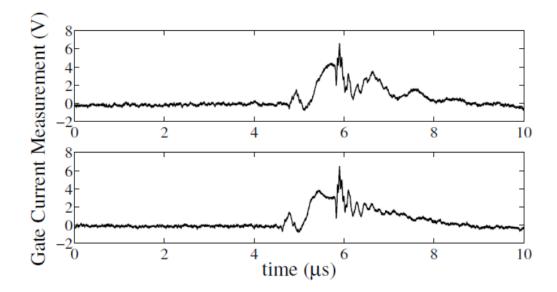

Consider gate charge, for example, which can help to identify naturally occurring gate-oxide degradation [12], [13]. Figure 1.2 shows the noise corrupting the gate-current measurements in a 208V motor drive. Clearly, switching noise makes it difficult to consistently extract the injected gate charge. Another issue apparent in Fig. 1.2 is that the signals of interest change rapidly and thus must be sampled at very high rates and/or carefully conditioned using well-designed analog circuits. Given the noise issues, such sampling and conditioning must be performed near the switch. [2]

Figure 1.2: Output of a differential amplifier in a prototype drive measuring the voltage across a 10 gate resistor during two different turn-on instances. Note that the gate current has a slightly different shape during the two instances as a result of switching noise. [2]

To deal with the possibility of switching failures, big efforts have been put into fault tolerant drive systems. The two guiding principles are hard fault detection and active reconfiguration. In most such drives, faulty switching components are detected, and the appropriate switches are then isolated and disconnected. See Refs. [18] [19]. Reconfiguration thus happens only after hard faults such as open or short circuits have occurred. Although such approaches are desirable, they can still cause problems.

Consider, for instance, an IGBT that slowly wears over its lifetime because of thermal cycling. Ultimately, such a device will short circuit, which is desirable in a drive with N + 1 component. Eventually, however, the bond wires burn away, leading to an indeterminate failure state that may cause an arc flash and subsequent collateral damage to the rest of the circuit or to nearby humans [3].

Recent advancements in the use of digital signal processors (DSPs) and field-programmable gate arrays (FPGAs) close to the power semiconductor [14]-[17] provide the opportunity to overcome the aforementioned issues to perform early stage fault detection in real time. Intelligent FPGA-based controllers close to the switches have been used to measure switch terminal variables at very high speeds [16][17]. These measurements can be used to extract useful health-related features, including threshold voltage, gate charge, and on-state voltage and resistance [2].

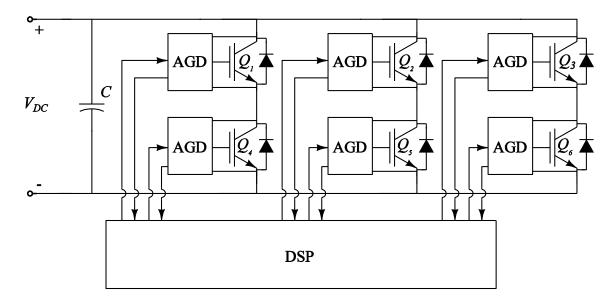

Figure 1.3 shows a 3- $\emptyset$ , full bridge converter with the ability to sample all of the necessary terminal variables (i.e.  $V_{GE}$ ,  $V_{CE}$ ,  $I_C$ , and  $I_G$ ). The key feature is the advanced gate-drive concept that has now been described in several works [14]-[17]. FPGA-based gate drives have been used to acquire switch terminal variables at rates as high as 100MHz. with emphasis on their use in optimizing turn-on and turn-off performance [16][17]. The signals measured by such devices can also be used to extract meaningful health-related features, such as on-state voltage and resistance. Feature extraction can be performed locally at the gate-drive unit, and features can be transmitted back to a central controller over fiber-optic cables at a much lower data rate [2].

Fig. 1.3: A potential smart drive architecture including FPGA-based gate drives such as those discussed in [14]-[17]. These devices are labeled here as advanced gate drivers (AGDs). The AGDs provide the controller with appropriate measurements. These connections would be fiber optic [2].

Work in the area of advanced gate drives (see Refs [9]-[11]) continues to be focused heavily on real-time thermal modeling (see Refs [4]-[8]) and control of switching (i.e. dv/dt and di/dt). Although in their early stages, digital approaches can provide optimization between switching losses, reverse recovery current, and overvoltage at turn-off by carefully controlling gate current. Cost is a concern with such advanced devices, but their ability to act as a platform for diagnostics could potentially add to their value.

# 1.2 Proposed Approach

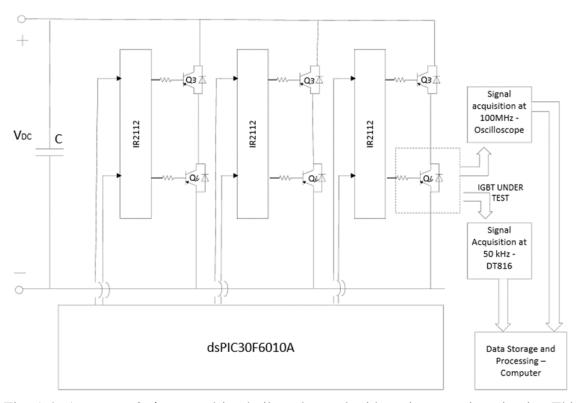

This thesis assumes that interest in advanced gate drives will only continue to grow, and that these devices should be exploited or early—stage fault detection. The focus is placed on an off-line proof-of-concept using the system shown in Figure 1.4. A custom 3-Ø motor drive was built and tested, and various sensing circuits were also constructed to focus on demonstrating the concept rather than engineering design, these measurement systems were not optimized for real time implementation, although other authors have

demonstrated the ability to monitor the necessary quantities in real-time systems. The focus here is placed on demonstrating the ability to detect faults using an algorithm adopted form the field of facial recognition. The necessary hardware and software are discussed in the later chapters of this thesis.

To demonstrate the proposed fault detection scheme, two specific early-stage faults are considered, namely latch-up and gate dielectric breakdown. Methods for inducing or simulating such failures were developed and used in chapter 5.

Fig. 1.4: A custom 3-Ø motor drive built and tested with various sensing circuits. This device was constructed to focus on demonstrating the off-line proof-of-concept.

#### 1.3 Thesis Outline

The following chapters of this thesis describe the background methodologies and works pertaining to those ideas previously stated. Chapter 2 describes failure mechanisms affecting IGBT(s), chapter 3 describes the method for fault detection and diagnosis.

Chapter 4 discusses the system designed for testing, chapter 5 presents experiment results and chapter 6 includes conclusions.

#### CHAPTER 2: IGBT FAILURE MECHANISMS

This chapter describes various failure mechanisms associated with the IGBT, several of which are targets of the proposed health-monitoring algorithm. Since failures are directly related to the physical structure of the device, Section 2.1 first presents a brief description of the device's structure and operation. Section 2.2 then details intrinsic failure mechanisms that occur within the device itself, and Section 2.3 describes extrinsic faults associated with packaging and placement.

# 2.1 IGBT Structure and Operation

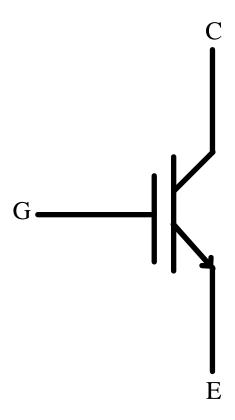

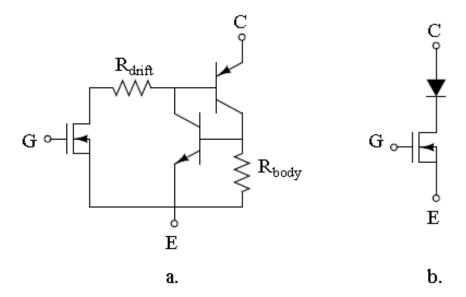

The Insulated Gate Bipolar Transistor (IGBT) is a three terminal power semiconductor device commonly used in high power switch-mode amplifiers and drives. Figure 2.1 shows its circuit symbol and indicates the names of each of its three terminals. The IGBT combines the characteristics of both the Bipolar Junction Transistor (BJT) and the Power Metal-Oxide-Semiconductor Field Effect Transistor (Power MOSFET). Specifically, the IGBT has input characteristics like a power MOSFET (i.e. high gate impedance), and output characteristics like the BJT. The IGBT thus acts like a voltage-controlled bipolar device. It was designed specifically for power switching applications, with the goal of being simple to drive (like a MOSFET) with a wide safe operating area (SOA) (like a BJT). Although far more information about IGBTs can be found in the literatures [21][24], it is essential for the purposes of this thesis to review the basic device structure and its principles of operation.

Figure 2.1: IGBT Circuit Symbol. Terminal connections are as follows, G - Gate, C - collector and E-Emitter.

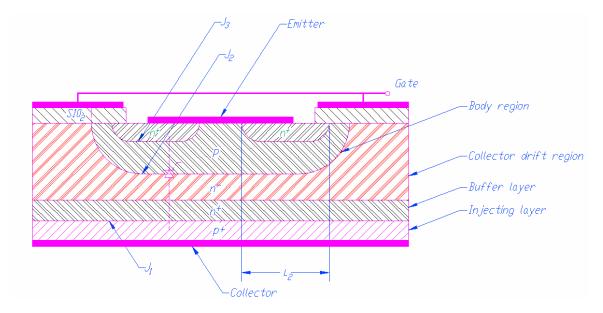

The most common IGBTs are n-channel devices built using a Double Diffused Metal-Oxide-Semiconductor (DMOS) process. Figure 2.2 shows one of several common structures. The silicon cross-section is similar to that of a vertical power MOSFET, with a Metal-Oxide-Semiconductor (MOS) gate structure and N+ source regions embedded in P wells at the emitter. The P+ layer at the bottom is the drain or collector. The doping profile in each layer can be reversed to form a p-channel device, but these are far less commonly found in practice [21].

Figure 2.2: Cross section of a generic N-Channel IGBT. Each layer that is discussed in this chapter is labeled [24]. (From [21]).

The cross-section in Fig. 2.2 can be used to understand the operation of the device. When a positive voltage is applied between the collector and emitter terminals with the emitter and gate both connected to ground, the device enters the forward blocking mode. Although denoted as a forward operating region, no current is conducted between the collector and emitter terminals. As the gate voltage is increased above the emitter voltage, the p-type silicon below the gate (known as the base region) becomes inverted. A conduction channel forms, connecting the  $n^+$  emitter to the n-type drift region. Electrons thus begin to flow into the drift region. This flow of electrons lowers the potential of the drift region, and the pn junction between the drift region the  $p^+$  collector becomes forward-biased. Under this condition, a high density of minority carrier holes is injected into the drift region from the  $p^+$  collector. Once the injected carrier concentration is much larger than the background concentration, a condition defined as a plasma of holes builds up in the  $n^-$  drift region. This plasma of holes attracts electrons from the emitter contact to maintain local charge neutrality. As a result, the

concentrations of excess holes and electrons gathered in the drift region are approximately equal. These excess concentrations drastically enhance the conductivity of drift region, phenomenon known as conductivity modulation [3]. More information about the forward blocking and conduction modes can be found in [21][24] [25][26].

When a negative voltage is applied across the collector-emitter terminals, the junction between the  $n^-$  buffer and P+ collector becomes reverse-biased and its depletion layer extends into the  $n^-$  drift region. The resulting breakdown voltage is determined by the open-base BJT formed by the  $p^+$ collector, N- drift, and p-type base regions. The device is prone to punch-through if the N--drift region is very lightly doped. The desired reverse voltage capability can be obtained by optimizing the resistivity and thickness of the N- drift region [21].

The device described above is known as a punch-through (PT) IGBT. Devices without the  $n^+$  buffer layer shown in Fig. 2.2 are known as Non-Punch Through (NPT) IGBTs. With a properly selected doping level and thickness, this buffer layer can improve device performance. Thought the IGBT's structure more closely resembles that of a power MOSFET, the conductivity modulation caused by the minority carrier injection means that its operation is more like that of a power BJT. Far more details about these phenomena can be found in various references [21]-[27].

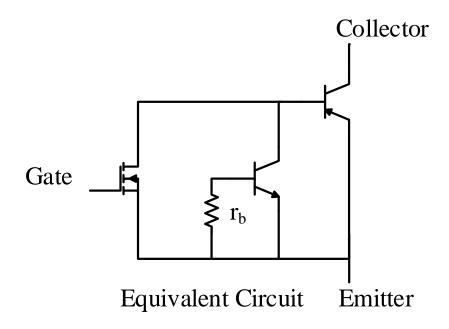

Figure 2.3: Equivalent circuit model for an IGBT.

A careful consideration of device operation yields the equivalent circuit model shown in Fig. 2.3. This circuit combines a shorting resistor rb, a MOSFET, and PNP and NPN transistors. The terminal called collector is actually the collector of a PNP transistor. The MOSFET drives the base of the PNP and determines the turn-on speed of the IGBT and its voltage drop The base of the PNP device is directly connected to the collector of the NPN transistor, and the base of the NPN device is connected to the resistor rb [84]. The NPN and PNP transistors form a parasitic thyristor. Recall that such devices have a regenerative feedback loop in which increasing device current only causes greater device current to flow, a phenomenon known as latch-up. The resistor rb represents the shorting of the base-emitter junction of the NPN transistor, which helps to prevent latch up. Turn-on of this thyristor can occur, and the result can be a device failure. More details about this model can be found in [21].

#### 2.2 Intrinsic IGBT Failure Mechanisms

An intrinsic failure mechanism is one that results directly from an alteration of the semiconductor. Several important examples are covered in this section, namely latching, dielectric breakdown, time dependent breakdown, and electron migration.

#### 2.2.1 Latching Failure

It was previously noted that the layering of the IGBT resembles that of a thyristor. This thyristor is parasitic and is normally prevented from turning on by limiting the current gain of the two transistors and reducing the value of the parasitic resistance  $R_B$ . During conditions when the collector current is particularly high (i.e. when the load is demanding excess current), problems can occur as the device is turning off. During this time, the MOSFET channel is reducing and thus higher than normal current flows through  $R_B$ . The excess voltage drop across this resistance increases the collector current in the NPN transistor, and more current is thus drawn from the base of the PNP device. The resulting positive feedback loop can drive the IGBT into a latch condition during which the device cannot be controlled from its gate. The collector current at which latch-up occurs is called the latching current. The magnitude of this value reduces with increasing device temperature. Hence, the IGBT is more susceptible to latch-up as temperature increases [27][29].

# 2.2.2 Catastrophic Dielectric Breakdown

Dielectric breakdown occurs when a strong electric field creates a current channel in an insulating medium. During conduction, breakdown can occur between the gate and collector terminals or between the gate and emitter terminals. Catastrophic breakdown of the gate oxide typically results from severe thermal or electrical over-stress (i.e.

electrostatic discharge, junction over-voltage, etc.) [30][2]. Key indicators of the breakdown are a lowering of the IGBT's thermal resistance and a corresponding rise in the junction temperature beyond safe operating values. Note that breakdown can also occur between the collector and the emitter when the device is in a blocking state.

#### 2.2.3 Time Dependent Dielectric Breakdown

This a failure caused by chronic defect accumulation in the  $SiO_2$  insulator during standard operation [13]. Such defects naturally result from a combination of at least three different mechanisms. These include impact ionization, hot carrier injection, and so-called trap creation attributed to the redistribution of hydrogen within the device. Before causing a complete failure, these naturally-occurring phenomena affect various device parameters. For instance, they can change the gate leakage current, a phenomena considered later in this thesis. Similarly, any charges that become trapped in the gate oxide affect the threshold voltage VT and the transconductance gm [13]. The deterioration of the silicon dioxide insulator also changes various device capacitances and thus changes device turn-on times [2].

#### 2.2.4 Electron Migration

Electron migration is the transport of mass from metals when stressed at high current densities. This phenomenon occurs as the result of two different forces. The first is the electric field force, and the second is a force exerted on the metal ions in the direction of electron flow. This latter force is caused by the momentum exchanged as electrons collide into the activated metal ions [31]. Under such conditions, voids can form in the metal and the result is an increase in resistance or a complete open-circuit. This type of failure mechanism is dependent upon the occurrence of high collector

currents in the IGBT [2]. Key parameters be affected by such deterioration are the device resistance and on-state voltage.

#### 2.3 Extrinsic Failure Mechanisms for IGBT

An extrinsic failure mechanism is one related to device packaging or placement. Some of the key failures explored here include wire bond lifting, solder-die detachment, and contact migration. Such failures are important to consider because dynamic thermal conditions are common in power-handling circuits. Such conditions cause solder and metal connections to be alternately expanded and contracted and thus weaken.

### 2.3.1 Wire Bond Lifting

Bonding wires are subjected to tensile stress as a result of power cycling [33]. As such cycling occurs, the junction temperature swings. Because the different materials within the device have different Coefficients of Thermal Expansion (CTEs), the adjacent materials expand and contract at different rates. Over time, the uneven rates of expansion and contraction can ultimately cause the bond wires to lift from the die and the die-attach layers to deteriorate. Held et al. concluded that power cycling is directly related to junction temperature and found that the number of cycles to failure can be characterized by the empirical relationship

$$N_f \propto \left(\Delta T_J\right)^{\alpha} e^{\frac{K_T}{T_J}}$$

2.1

where alpha and kt are real-valued constants,  $T_J$  is the actual junction temperature, and  $\Delta T_J$  is the change in junction temperature [34].

Bond-wire lift eventually leads to higher junction temperatures  $(T_J)$ , and therefore it affects parameters such as on-state resistance and on-state  $V_{CE}$ . Because increases in these parameters cause greater internal losses, they only act to further increase the

junction temperature. The result is a positive feedback loop that eventually leads to complete device failure [2].

#### 2.3.2 Solder Die Detachment

Solder attaching the silicon die to the package heat sink can develop cracks and voids due to dissimilar thermal expansion in the two materials [36]. The junction-to-case thermal impedance thus rises, which causes a higher junction temperature. A positive feedback mechanism is thus created once again. As in the case of bond-wire failures, this mechanism affects parameters such as the on-state resistance and on-state  $V_{CE}$  [35][2].

#### 2.3.3 Contact Migration

Contact Migration is related to electro-migration, which occurs when voids between external metal contacts and silicon cause metal to diffuse into the semiconductor. Ultimately, this diffused metal can short-circuit internal p-n junctions. Before causing a complete failure, this mechanism impacts parameters such as on-state resistance and on-state  $V_{CE}$  [35][2].

#### CHAPTER 3: METHOD FOR FAULT DETECTION AND DIAGNOSIS

This chapter briefly details the current state-of the art with respect to hard faults detection in IGBT drives, and then describes the proposed approach for detecting the early stage indicators that would prevent such faults occurring. Section 3.1 describes approaches for detecting the three most common hard switch faults, namely opens, shorts, and gate failures. Section 3.2 then focuses on the details of the proposed incipient fault detection scheme. Ideally, such a scheme would become the first line of defense for fault detection, and approaches such as the ones indicated in Section 3.1 would become a last resort.

#### 3.1 Methods for Fault Detection for IGBT in Motor Dives

Voltage-source inverters (VSIs) are commonly used in motor drive and utility applications. It is estimated that about 38% of the faults in variable-speed ac drives, in industry are due to failures of power devices [40]. Even though drives can use a multitude of semiconductor switching devices, IGBTs are mostly used due their capability for high voltage and current ratings and their capacity to withstand short-circuit currents for periods exceeding 10 µs [41]. Though IGTB(s) are known for their sturdiness, they are not immune to failure. These failures are often due to excess electrical and thermal stress which arises in various applications. IGBT failures can be broadly categorized as open-circuit faults, short-circuit faults, and intermittent gate misfiring faults. And for these categorizations there have been, the development of various protection methods. The rest

of this section will then proceed to define each fault's category and catalog the protection diagnostic/detection methods used for them.

## 3.1.1 IGBT Open Circuit Faults

A gate-drive open-circuit fault may happen due to lifting of bonding wires caused by thermic cycling. It may be caused by a driver fault or a short-circuit-fault-induced IGBT rupture. Open-circuit faults lead to dc current offset in both the faulty and healthy phase. The interaction between the dc component and the field generates a pulsating torque at the stator current frequency, which may substantially reduce the maximum average torque available to the drive [42]. Unequal stress is also generated in the upper and lower transistors due to the dc currents. These effects may cause secondary faults in the inverter, motor or load. The voltages and currents carry the fault signatures and hence can be analyzed to detect and locate the fault. Open circuit faults generally do not cause system shutdown, but degrade its performance [41]. Listed in Table 3.1 are the diagnostic methods that can be used for open fault detection as well as the literature in which can more details can be found. Also listed are particulars about effectiveness, resistivity, detection time, implementation time, detection parameter and threshold dependence on detection variable with respect to each other.

Table 3.1: Open circuit fault detection methods from [41].

| Methods                                        | Effectiveness                     | Resistivity                               | Detectio<br>n Time | Implementatio<br>n Time | Timing<br>Effort | Detection<br>Parameter | Threshold<br>Dependence<br>on Detection<br>Variable |

|------------------------------------------------|-----------------------------------|-------------------------------------------|--------------------|-------------------------|------------------|------------------------|-----------------------------------------------------|

| Park's<br>Vector<br>Method [43]                | Ambiguous<br>at small<br>circuits | Poor at small currents                    | >20 ms             | Medium                  | High             | 3-phase currents       | High                                                |

| Normalized<br>DC Current<br>Method<br>[44][45] | Poor at small currents            | Poor as<br>multiple<br>condition<br>s may | 18.4 ms            | Low                     | Low              | 3-phase<br>currents    | Independent                                         |

|                                                             |                                                         | antiafy                     | <u> </u>          |                                                               |            | 1                                                         |             |

|-------------------------------------------------------------|---------------------------------------------------------|-----------------------------|-------------------|---------------------------------------------------------------|------------|-----------------------------------------------------------|-------------|

|                                                             |                                                         | satisfy                     |                   |                                                               |            |                                                           |             |

| Modified<br>Normalized<br>DC Current<br>Method [45]         | Good                                                    | Good                        | 18.4 ms           | Low                                                           | Low        | 3-phase currents                                          | Independent |

| Slope<br>Method [46]                                        | Poor at small currents                                  | Poor                        | 38.3 ms           | Low                                                           | High       | 3-phase currents                                          | High        |

| Simple DC<br>Method<br>[44][45]                             | Poor at small currents                                  | Medium                      | Load<br>dependent | Low                                                           | Mediu<br>m | 3-phase currents                                          | High        |

| AC<br>Instantaneou<br>s Frequency<br>Method [46]            | Cannot locate<br>faulty<br>transistor                   | Medium                      | 20 ms             | Low                                                           | Low        | 3-phase currents                                          | Low         |

| Comparison of Actual and Reference Quantity Method [40][47] | Needs, 2-4<br>sensors for<br>effective<br>detection     | Good                        | 5 ms              | High                                                          | Mediu<br>m | Inverter pole voltage, phase voltages and neutral voltage | Independent |

| Sensing Voltage across the lower Switch [48]                | Good                                                    | Good                        | 2.7 ms            | Medium                                                        | -          |                                                           | Low         |

| Centroid<br>Based Fault<br>Detection<br>[49]                | Good                                                    | Good                        | -                 | Medium                                                        | -          | 3-phase currents                                          | N/A         |

| Current Pattern Recognition Method [50]                     | Many<br>parameters to<br>consider                       | Medium                      | 10 ms             | High                                                          | Mediu<br>m | 3-phase currents                                          | High        |

| Converter<br>Behavior<br>Rules [51]                         | Not yet proven online                                   | Good                        | -                 | High                                                          | None       |                                                           | Independent |

| Spectrum<br>Analysis<br>Method [52]                         | -                                                       | -                           | -                 | Medium                                                        | High       | 3-phase currents                                          | High        |

| Current<br>Deviation<br>Method [53]                         | Good                                                    | Medium                      | 2 cycles          | High (Requires<br>change in<br>inverter control<br>algorithm) | Low        | Normalize<br>d 2-phase<br>currents                        | Independent |

| Wavelet –<br>Fuzzy<br>Method [54]                           | Good if the<br>fuzzy rules<br>are carefully<br>designed | Good                        | 5 cycles          | High                                                          | Mediu<br>m | 3-phase currents                                          | Low         |

| Wavelet-<br>Neural<br>Network                               | Diagnosis<br>error < 5%                                 | Good if<br>NN is<br>trained | -                 | High due to<br>NN training                                    | Low        | 3-phase currents                                          | N/A         |

| Method [55]                                                                 |                                     | thoroughl<br>y                                                 |         |                            |     |                                                |      |

|-----------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------|---------|----------------------------|-----|------------------------------------------------|------|

| Wavelet-<br>ANFI<br>Method [56]                                             | -                                   | Good as<br>the NN is<br>trained<br>for noisy<br>condition<br>s | -       | High due to<br>NN training | Low | DC link<br>current                             | N/A  |

| Clustering-<br>ANFI<br>System [57]                                          | Worst- error<br><2.26%              | -                                                              | -       | High                       | Low | 3-phase<br>currents                            | N/A  |

| Subtractive<br>Clustering<br>Based Mean<br>Current<br>Vector<br>Method [58] | Good                                | -                                                              | ⅓ cycle | Medium                     | Low | 3-phase<br>currents                            | N/A  |

| Model Based<br>ANN<br>Method [59]                                           | Prediction<br>rate of around<br>75% | -                                                              | -       | High                       | -   | 3-phase<br>voltages,<br>currents<br>and torque | N/A  |

| Rules Based<br>Expert<br>Systems<br>[20][21]                                | Offline<br>diagnosis tool           | -                                                              | -       | High                       | -   | User Input                                     | N/A  |

| Bond Graph<br>Method [22]                                                   | -                                   | -                                                              | -       | High                       | -   | Switch<br>voltages                             | High |

#### 3.1.2 IGBT Short Circuit Faults

A transistor short circuit in the motor drive system causes a nonzero dc component current flow in the stator winding and the machine experiences dynamic braking with other base drives disabled. In many short-circuit failure conditions; the time between the fault initiation and the device failure is very short. The IGBTs can withstand abnormal currents up to around 10 µs. Therefore, detection and protection should happen dynamically with the changing conditions. Detection methods based on mathematical transformations can detect the damaged device, but they are not fast enough to cause any protective action. Other methods that are based on voltage level change are fast but need too many measurements for fault localization [63][41]. Detection methods that have been

used for detection of short circuit faults are listed in Table 3.2. For a more expansive look in to each method the literature review for each is provided in the first column beside the identified method

Table 3.2: Short circuit fault detection methods from [41].

| Methods                                                               | Parameters<br>Requirements | Turn-off | Dynamic | Implementation<br>Effort | Reliability | Comments                                            |

|-----------------------------------------------------------------------|----------------------------|----------|---------|--------------------------|-------------|-----------------------------------------------------|

| De-saturation<br>detection Method<br>[64]                             | Collector<br>voltage       | Abrupt   | No      | Low                      | Medium      | Device turn-<br>off not assured                     |

| Current Mirror<br>Method [64]                                         | Device<br>current          | Abrupt   | No      | Low                      | Medium      | Very expensive                                      |

| Gate Voltage<br>Sensing Method<br>[63]                                | Gate voltage               | Abrupt   | No      | Low                      | Low         | Requires<br>complicated<br>protection<br>circuitry  |

| Di/dt Feedback<br>Control Method<br>[64]                              | Device<br>voltage          | Soft     | Yes     | High                     | Medium      | Stray<br>inductance<br>hard to control              |

| Protection by<br>Gate Voltage<br>Limiting [65]                        | Gate voltage               | Soft     | Yes     | Medium                   | Low         | Interferes with normal operation                    |

| Protection by<br>Snubbers and<br>Clamp Circuits<br>[66]               | Device<br>voltage          | N/A      | Yes     | High                     | Low         | Very expensive for fault protection                 |

| Protection by<br>Slow Turn-off<br>Using Additional<br>Parameters [66] | Gate voltage               | Soft     | Yes     | High                     | Low         | Require<br>complex<br>circuitry                     |

| Protection by<br>Two-Step Gate<br>Pulse [67]                          | Gate voltage               | Soft     | No      | High                     | High        | Reliable<br>shutdown of<br>the device,<br>di/dt     |

| Average Current<br>Park's Method<br>[43]                              | Phase currents             | N/A      | N/A     | Medium                   | High        | Reliable<br>detection but<br>offer no<br>protection |

| Vector<br>Composition of<br>the Inverter<br>Output Voltage<br>[68]    | Inverter output voltage    | N/A      | N/A     | Medium                   | Low         | Slow response<br>as it uses<br>filters              |

#### 3.1.3 IGBT Intermittent Gate-Misfiring Faults

A catastrophic breakdown of the device can be caused by IGBT gate-misfiring faults, if the faults remain undetected. It may be a result of driver open circuit, control circuit element deterioration, degraded electromagnetic compatibility, etc. Inverters can operate for a considerable period of time even with sustained gate misfiring. However, this is accompanied by degraded output voltage and overstress on other switching devices and dc bus capacitors. Gate misfiring may also lead to a short-circuit fault of a device. This may happen when the device fails to turnoff causing shoot-through. In most cases, gate misfiring is intermittent in nature. Online monitoring is important in safety-critical applications. Detection methods in frequency domain are not suitable for intermittent faults, since the steady-state measurements do not contain information about the fault after the system has recovered. Therefore, time-domain techniques are desirable. Intermittent gate-misfiring fault has not been extensively studied in the previous literature [41].

Two approaches that are used to detect this type of fault are Detection by Output Current Trajectory and Pattern Recognition Approach. The methodology behind Current Trajectory approach is as follows. When a gate-misfiring fault occurs in one of the inverter switching devices, the voltage disturbance will cause an increment to the stator current space vector. The incremental current happens toward a unique direction that is determined distinctively by the failed device. An incremental system model is used to provide compensation to the measured current response, so that the modified incremental current signal will decay in the opposite direction to the initial offset caused by the

voltage disturbance. The trajectory of the current response can be used to detect the fault and locate the defect switch [69] from [41].

The Pattern Recognition Approach is a fuzzy logic based technique and that inverter output current to detect the intermittent loss of firing pulses. A fuzzy fault detection and diagnosis block compares the stator Concordia current vector with that in the rule base. By this process, the method can detect a fault, locate the faulty device and can also find the fault severity. The method is discussed more in [70] and [71] from [40].

## 3.2 Algorithm Development

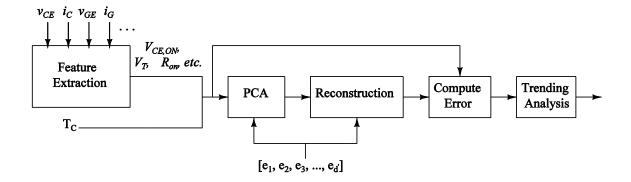

Although the algorithm described previously are desirable for enabling drives to operate in emergency situations, it is desirable to detect the underlying root causes much earlier so that performance degradation or potential root catastrophic danger could be avoided. This Section describes our solution to this problem, and it is based heavily on the failure modes and effects work done by several other researchers [[16]-[20]]. Figure 3.1 shows the proposed health-monitoring scheme. Inputs include various raw sensor signals or terminal variables. The inputs are the current ( $I_C$ ), the voltages ( $V_{CE}$   $V_{CE,ON}$   $V_{GE}$ ), the ambient temperature ( $I_A$ ), and the case temperature of the IGBT ( $I_C$ ). The first step is to extract relevant key-performance indicators (KPIs) or features. Examples include the root mean squared (RMS) value collector current ( $I_C$ ), the threshold voltage VT (gate voltage at which the IGBT turns on and collector current begins to flow),  $V_{GE,ON}$  and other features which with are competed by the various manipulations of the terminal signals.

Figure 3.1: Generalized condition-monitoring algorithm for an operational IGBT based on principal-components analysis (PCA). The  $e_i$  are based on healthy conditions. New input signals and parameters can be added as needed. A similar implementation would be used for a MOSFET form [72].

This extraction is done in the feature extraction block which contains the raw signal manipulations needed in order to output the KPI(s). The process of each feature's extraction is detailed in section 4.3. It is to be noted that the terminal signals must be sampled at a high rate due to the fact that the extracted features are processed at a much slower rate. This is mostly due to the fact that multiple data samples are usually required for processing. For this experimentation the terminal signals are sampled at both 100 MHz and 50 KHz but are processed at much lower rate.

The crux of the fault-detection algorithm is the principal-component analysis (PCA) block. PCA casts high-dimensional data onto a lower dimensional space, which implements a transformation that best represents the information in the overall data set. In other terms, PCA aggregates a set of KPIs and provides information about the germane trends without having to develop a set of rules a priori. Experience has shown that that PCA leads to a robust detection mechanism [72]. The PCA block then relays information about relevant trends within the monitored data to the reconstruction block.

In order to provide such information, the features measured at each time step  $t_k$  are first grouped into a column vector  $x_k$ . The length of this vector is equivalent to the number of features; for generality, we say it has length d. The basic approach of the principal component- based algorithm is to compare each measurement  $x_k$  to an expectation. This expected vector is computed by projecting  $x_k$  onto a vector space created using "healthy" features. The healthy values are learned during a training phase in which the motor is assumed to be fault-free. During training, the healthy vectors are decomposed into a small set of characteristic vectors that best describe the distribution of the healthy parameters. During operation, each measured vector is projected onto this space. In the language of information theory, we are extracting the relevant information from the feature vector, encoding it efficiently, and then comparing the encoded result to a database of healthy features encoded in a similar manner. Any differences indicate that a fault may be developing. This approach is partially patterned after the facial-recognition scheme presented in [72].

The training space includes feature vectors recorded under normal operating conditions. In all, there are M such feature vectors and they are denoted as  $\Gamma$  1,  $\Gamma$  2,  $\Gamma$ 3, ...,  $\Gamma$  M. These training vectors are subject to a principal-component analysis in which one seeks a set of orthogonal vectors  $e_i$  that best describe the distribution of the data. The j-th training vector can thus be expressed as

$$\Gamma_i = m + \sum_{i=1}^{d'} a_{i,i} \boldsymbol{e}_i \qquad 3.1$$

where m is the sample mean, i.e.

$$\boldsymbol{m} = \frac{1}{M} \sum_{j=1}^{M} \boldsymbol{\Gamma}_{j} \qquad 3.2$$

Note that the distribution of the data is best described using  $d' \le d$  orthonormal vectors [[74], [75]]. During the training phase, one calculates these vectors by minimizing the squared-error criterion function

$$J = \sum_{j=1}^{M} ||(m + \sum_{i=1}^{d'} a_{j,i} \boldsymbol{e}_i) - \Gamma_j||^2 \quad 3.3$$

[75] and [74] show that the  $e_i$  correspond to the eigenvectors of the sample covariance matrix which is

$$S = \sum_{j=1}^{M} (\Gamma_j - m) (\Gamma_j - m)^T \quad 3.4$$

The actual  $e_i$  are the eigenvectors corresponding to the d' largest eigenvalues of S [[74], [75]]. Ultimately, this process yields a compact basis that efficiently encodes the relevant features of a healthy motor during normal operating conditions. Further details on the PCA algorithm are included in various references, including [74] and [75].

When the motor is operational and the algorithm is applied to monitor its health, the first step is to project the features measured at time  $t_k$  onto the space spanned by the  $e_i$ . This projection is performed by the block labeled PCA, which computes the coefficients

$$a_{k,i} = \boldsymbol{e}_i^T (\boldsymbol{x}_k - m)$$

3.5

The next block uses these coefficients to reconstruct an approximation of  $x_k$ . The resulting estimate is thus denoted as

$$\widehat{\boldsymbol{x}}_k = \boldsymbol{m} + \sum_{i=1}^{d'} a_{k,i} \boldsymbol{e}_i \quad 3.6$$

Following reconstruction, the algorithm calculates the two-norm of the residual vector  $\mathbf{r} = \hat{x}_k - x_k$ . This quantity, which we term the health indicator (HI), is computed at each time tk. HI is thus

$$HI_k = \mathbf{r}^T \mathbf{r} = (\widehat{\mathbf{x}}_k - \mathbf{x}_k)^T (\widehat{\mathbf{x}}_k - \mathbf{x}_k) \quad 3.7$$

This quantity represents the error between the measured features  $x_k$  and their expected value for a healthy motor. In a very basic sense if the error is small, the motor is operating under normal conditions; if the error grows, a problem may be developing. The final block, labeled "Trending Analysis," monitors for such variations [72].

On its face, this mathematical derivation of the principal components seems unintuitive. Thus it would be best if a step back was taken in order to frame the PCA in terms of the problems at hand. Consider each vector  $\mathbf{x}_k$  as a set of 8 KPIs recorded at intervals of 3 seconds. In general, its unknown if the machine has a fault, and therefore what is indicated by  $\mathbf{x}_k$  is unknown. One could develop a set of rules that would monitor each of these 8 values. But in a rules-based context it would mostly likely be assumed that as long as each feature is individually important as a sort of fault indicator, it would be more prudent to simultaneously monitor all 8 KPIs. While it may seem natural to think that each feature possesses independence, this is not usually the case and as such classification accuracy does not improve with the monitoring of additional features. There can be a point diminishing returns due to the fact that the more features are added the more convoluted the information being acquired becomes and as such the more difficult it becomes to make meaningful sense in terms of creating a set of rules that can envelop all possible trends in the data.

The health monitoring algorithm combines the features/KPIs in such a manner that it compresses the size of the feature set and presents the trends that best highlights the difference in the features. This is demonstrated in chapter 4. It should be noted that the there is an effect on the Health Indicator due to loading conditions of the motor. As the load on the motor changes, there is an effect on other quantities such as The IGBTs collector current. This point will also be explored in chapter 5.

#### CHAPTER 4: SWITCH CONDITION MONITORING OF IGBT(s)

This chapter focuses on the experimental setup developed to test the algorithm discussed previously. Section 4.1 provides an overview of the complete experimental system. Section 4.2 describes the drive architecture and sensing circuits for raw signal extractions. Section 4.3 details the process used in software to extract the features needed by the algorithm. Section 4.4 describes the methods used to degrade several IGBT(s). These degraded IGBT(s) were placed in the drive during the testing described in Chapter 5.

## 4.1 System Setup Overview

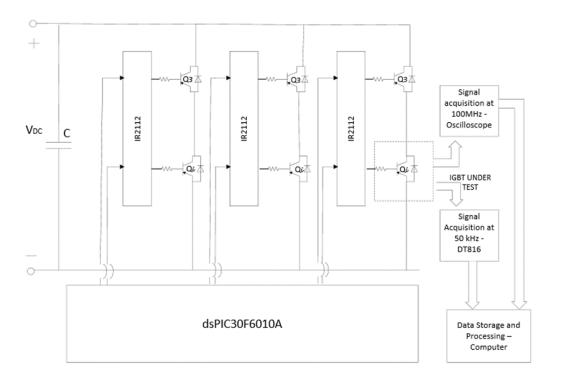

As previously stated in the Section 1.2, this thesis aims to produce an offline IGBT incipient fault detection scheme based on PCA which can then be upgraded to an online method. The ultimate goal is to create an electronic motor drive using an advanced FPGA based controller (see Figure 1.3) with the diagnostic ability to sample key parametrics of the IGBT. In order to implement the proof of concept, for the offline incipient fault detection in IGBT switches in motor drives. A system comprised of the combination of custom designed hardware setup and custom software was developed. Figure 4.1 illustrates a high level block diagram of the systems structure. The system in its entirety is made up of custom built motor drive architecture with both sensing circuits and an oscilloscope for data measurements. The data measured by the sensing circuits are

sampled by the data acquisition device the DT9816. The sampling of data by both the DT9816 and the oscilloscope are controlled via coding developed in MATLAB software. The data is then passed to the computer with the MATLAB which then handles the data collection and processing by means of PCA in the MATLAB environment.

## 4.2 Drive Architecture

Figure 4.1 shows a three-phase full-bridge motor drive that has been constructed in a way that makes it is possible to sample all of the required terminal variables. The key feature is the advanced gate drive concept from [14]. The raw signals that are measured are as follows; the phase current  $(I_C)$ , the collector-to-emitter voltage  $(V_{CE})$ , the collector-to-emitter on-state voltage  $(V_{CE,ON})$ , the gate-to-emitter voltage  $(V_{GE})$ , case temperature  $(T_C)$ , and ambient temperature  $(T_A)$ .

Figure 4.1: Schematic of custom-built IGBT based motor drive used for driving a 0.5hp induction motor. The control signals are supplied using a dsPIC30F6010A.

From a health monitoring point of view, it is paramount to sample raw signals such as  $V_{CE,ON}$ ), and  $I_C$  fast enough to be able to extract features such as VJ and  $R_{ON}$ . Sampling rate is one issue that must be addressed regardless of the actual circuit architecture. Practically speaking when sampling, the sample rate must be sufficiently above the switching frequency. This in turn may pose a limitation in real world applications dealing with lower powered drives with switching frequencies at 10 kHz or higher. This would have to be overcome by using powerful microcontrollers or Field Programmable Gate Array - FPGA boards with a sampling speed in excess of 100 MHz with at least 8 bit resolution. In high power, medium voltage (MV) drives, which are more likely to require condition monitoring and power-dissipation limits, tend to cap switching frequencies at values on the order of 1 kHz [72] [75].

Given that the focus of this thesis is on demonstrating the algorithm, there were not sufficient resources available to address the basic issues associated with implementing an FPGA based drive. Instead, a reasonable hybrid technique was developed and applied to a traditional three phase drive architecture. (See literature [72] for complete catalog of drive development). Figure 4.1 shows the complete block diagram. Note that features are requiring low sampling rates are acquired using a low-cost 16-bit USB data acquisition board [76]. Features requiring high frequency sampling are acquired using a Tektronix 3014b. This device has a sampling rating of 1.25 GS/s with a bandwidth of 100MHz.

## 4.2.1 50 kHz Sampling for Switch Condition Monitoring

Measurement circuits, sensors, differential probes and current guns are used to measure the raw signals that are used to extract the relevant features. First to be discussed

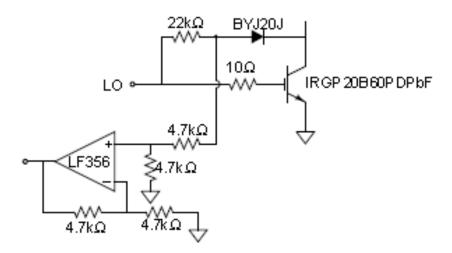

will the sensing circuits and sensors used to get the raw signals that will be fed to the 50KS/s DT9816 data acquisition board. The phase current,  $I_C$  is measured using the LTS 6-NP which is a Hall-effect transducer. The collector to emitter voltage  $V_{CE}$  is measured in the on-state only, due to difficulty in measuring said signal in its entirety.  $V_{CEON}$  is measured using a desaturation detection circuit included in gate drives to detect if an IGBT is no longer in the saturation region of operation. The reason for such an approach is due to the fact the  $V_{CE}$  is difficult to measure directly because the amplifier required would be exposed to common-mode swings on the magnitude of several hundred volts and thus analog-to-digital converter would have difficulty measuring the very low on-state voltage with adequate resolution.

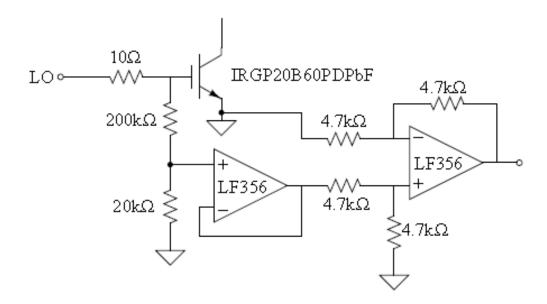

Figure 4.2: Circuit used for the measurement of on-state collector-to-emitter voltage,  $V_{CE,ON}$  in experimental drive from [72].

$V_{CE,ON}$  is measured by the circuit shown in Fig. 4.2. The voltage Vx is referred to the high voltage side of the drive and is connected to a simple amplifier subtractor circuit. Once the IGBT is conducting, Vx has the definition

$$v_X = V_D + v_{CE}(i_c) \quad 4.1$$

where *VD* is the forward voltage drop across the diode in the desaturation circuit. Since the voltage at the output of the differential amplifier in Fig. 4.2 is referenced to the high voltage bus, the circuit shown in Fig. 4.4 is used to transmit its output to the data-acquisition system. Similar isolation would be required in an FPGA-based design, but its exact location in the signal path would depend upon the specifics of the design [72].

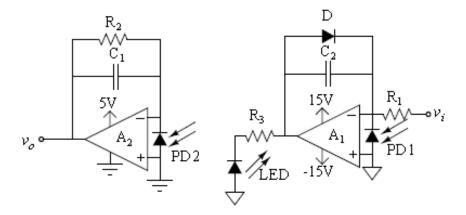

The optical transmission circuit from [14] maintains appropriate isolation when measuring  $V_{CE,ON}$ . The main component of the optical transmission circuit is the HCNR201 which is a high-linearity wide-bandwidth analog opto-coupler consisting of a high-performance AlGaAs Light Emitting Diode, LED that illuminates two closely matched photodiodes, PD1 and PD2. The input photodiode, PD1, can be used to monitor, and therefore stabilize, the light output of the LED. The non-linearity and drift characteristics normally associated with LED can be virtually eliminated. The output photodiode, PD2, produces a photocurrent that is linearly related to the light output of the LED. This allows for a highly stable linear gain characteristic of the overall optical transmission circuit [72], [77].

Figure 4.3: Analog circuit used to transmit signals from across isolation barrier.

The operational amplifier A1 adjusts the LED current, and therefore the current in PD1, IPD1, to maintain its + input terminal at 0 V. Since the + input of A1 is at 0 V, the current through R1, and therefore IPD1 is [77]

$$I_{PD1} = \frac{v_i}{R_1} \qquad 4.2$$

IPD1 depends only on the input voltage and the value of R1 and is independent of the light output of the LED.

The relationship between input optical power and the output current of the diode is linear. Thus by stabilizing and linearizing IPD1, the light output of the LED is also stabilized and linearized. Since light from the LED also falls on both of the photodiodes, IPD2 is stabilized as well. The physical package construction determines the relative amounts of light that fall on the two photodiodes and, therefore, the ratio of the photodiode currents. This results in very stable operation over time and temperature. The photodiode current ratio is expressed as a constant, K, where [72], [77]

$$K = \frac{I_{PD2}}{I_{PD1}} \qquad 4.3$$

The operational amplifier, A2 and resistor R2 form a trans-resistance amplifier that converts IPD2 back into a voltage,  $v_o$ , which is [72], [77]

$$v_0 = I_{PD2}R_2 \quad 4.4$$

Combining Eq. (4.2)-(4.4) yields a transfer function relating the output voltage to the input voltage,

$$v_o = K\left(\frac{R_1}{R_2}\right)v_i$$

4.5

Thus the relationship between  $v_i$  and  $v_o$  is constant, linear, and independent of the light output characteristics of the LED. The optical transmission circuit's gain can be adjusted

by simply changing the ratio of R2 to R1. The parameter *K* can be thought of as the gain of the opto-coupler and for this HCNR201 it is approximately 1 [72] [77].

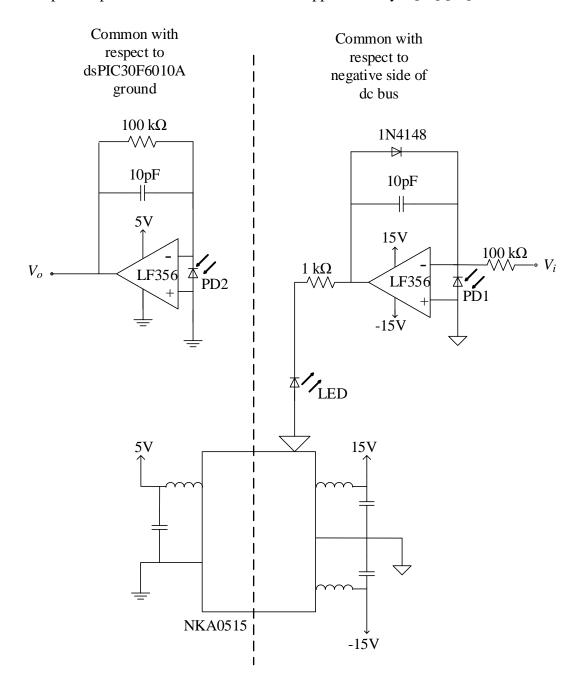

Figure 4.4: Optical transmission circuit used to provide isolation between the low voltage data-acquisition system and measurements recorded with respect to the high voltage bus. The NKA0515 provides isolated dc supplies for all of the measurement circuits included here.

Figure 4.4 shows the unity gain optical transmission circuit that was designed to measure  $V_{CE,ON}$ . Each of the measurement circuits that are referenced to the dc bus of the motor drive requires an optical transmission circuit to transmit the signal back to be acquired using the data acquisition board [72].

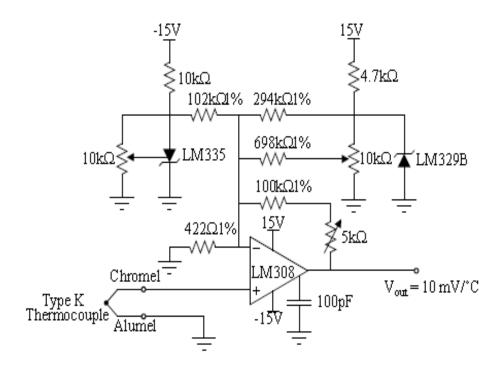

Figure 4.5 shows the circuit measuring the gate-to-emitter voltage, which is comprised of just a differential amplifier. A voltage divider was used to reduce the size of gate voltage. This is done, so that the output from the operational amplifier would be in a range so that a circuit similar to the one in Fig. 4.4 is able to transmit the output back to the data-acquisition system. For the computation of  $V_{GE,ON}$ , samples are averaged over each conduction interval for a given interval. A solid-state sensor measures the ambient temperature, and a thermocouple measures the case temperature as shown in Fig. 4.6. These measurements are also averaged over an interval of 1 second.

Figure 4.5: Circuit used for the measurement of gate-to-emitter voltage,  $V_{GE}$  in experimental drive.

Figure 4.6: Circuit used for the measurement of IGBT case temperature in experimental drive. Form [72]

## 4.2.2 100MHz Sampling for Switch Condition Monitoring

As previously stated measurement circuits, sensors, differential probes and current guns are used to measure the raw signals that are used to extract the relevant features. For this section what is to be discussed is the use of oscilloscope differential probes and current guns used to get the raw signals that will be fed to the 100 MHz sampling Tektronix 3014b oscilloscope. This is acting as a data acquisition board. The phase current,  $I_C$ , is measured using the Tektronix TPS202 current gun which is a Halleffect transducer, See Fig. 4.7 c. The gate to emitter voltage  $V_{GE}$  is measured and the voltage  $V_{X}$  across the resistor at the gate of the IGBT is measured by a low latency high voltage differential probes [Tektronix P5205] seen in Fig. 4.7 a. The gate to collector

voltage-  $V_{CE}$  is also measured by a low latency high voltage differential probe [Tektronix P5210] seen in Fig. 4.7 b.

a b

C

Figure 4.7: Measurement Device for 100 MHz Sampling. A – Tektronix P5205 High Voltage Differential probe. B – Tektronix P5210 High Voltage Differential probe. C – Tektronix TCP202 Current probe.

### 4.3 Feature Extraction

After the raw signals have been collected by the oscilloscope and data acquisition board, the relevant features must be extracted from them. The features that are extracted include  $I_{C,rms}$ , VJ,  $R_{ON}$ ,  $Q_i$ , VT and  $V_{GE,ON,AVG}$ . Several features are procured through the processing measurements of  $I_C$  and  $V_{CE}$ . Section 4.1.1 illustrates the method for measuring  $V_{CE}$ . Although the literature suggests that  $V_{CE}$  can be directly applied in fault detection, this is only true under carefully controlled conditions that do not necessarily

apply in the field. In general, the circuit model as shown in Fig 4.8 b for a conducting IGBT is a diode in series with a power MOSFET, meaning that

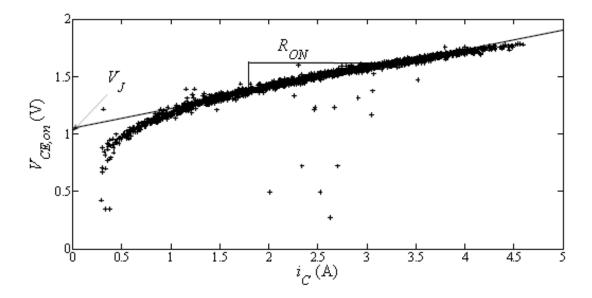

$$V_{CE.ON} = V_I + i_C R_{ON} 4.6$$

where  $R_{ON}$  is the resistance of the MOSFET channel and VJ represents the combination of the voltage drops across the p-n junction and the drift regions shown in Fig 4.8 'a' [78].

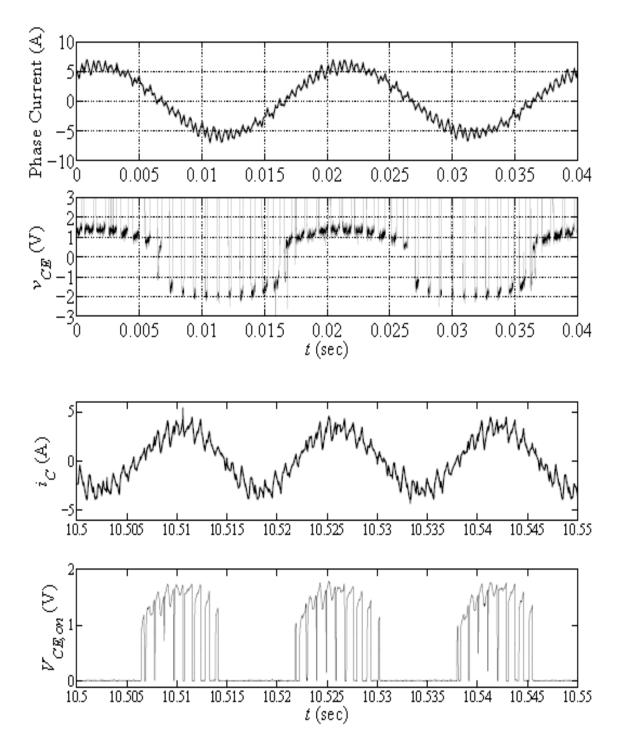

It may be difficult to distinguish between changes in  $I_C$  and true fault conditions, due to the fact that most incipient faults have only a small impact on  $V_{CE,ON}$ . This problem is further compounded by the fact that both VJ and  $R_{ON}$  are affected by temperature [78]. In variable-speed ac drives feature extraction is notably difficult in part due to the fact that the current and  $V_{CE,ON}$  are subjected to continuous variation as seen in Fig. 4.9. Figure 4.9 illustrates the effect of Eq. 4.6 in the operational drive. Typical behavior of  $V_{CE,ON}$  is that it follows the current when the IGBT is conducting. The effect of the current thus has to be isolated, such that the two parameters can be estimated separately in Eq. 4.6. This is done using a least squares approach [72].

Figure 4.8: Measurement of phase current  $I_C$  and  $V_{CE}$  for the low side IGBT under test. When  $V_{CE}$  is negative, the anti-parallel diode is conducting.

In Fig 4.9 there are 4 plots; from top to bottom showing  $I_C$ Phase,  $V_{CE}$ ,  $I_C$  and the voltage  $V_{CE,ON}$  samples during transistor conduction that are taken for approximately 1 second. [But only an interval of 0.04 is shown in Fig. 4.9] After which a linear fit on the data is performed. Figure 4.10 shows the second of relevant measured points and the best-fit line that corresponds to the data shown in Fig. 4.9. The estimated y-intercept (VJ) and the slope ( $R_{ON}$ ) are from the I-v curve developed from the conduction data of  $I_C$  transistor and  $V_{CE,ON}$ . These data point vectors VJ and Ron are ultimately extracted as features. The value RON for this particular second of data is 170.6 m and VJ is 1.053 V.

Figure 4.9: Oscilloscope measurement of phase current IC and  $V_{CE}$  and measurements of the phase current IC and  $V_{CE,ON}$  with the sensing circuits for the low side IGBT under test. When  $V_{CE}$  is negative, the anti-parallel diode is conducting. From [72]

Figure 4.10: Plot showing  $V_{CE,ON}$  versus  $I_C$  over one second. Note that a fit is performed to extract VJ and  $R_{ON}$ . From [72].

These parameters and the corresponding *rms* current are extracted. The root mean square of the phase current is calculated over the each individual period of a 60 Hz sinusoid and is defined as

$$I_{C,rms} = \sqrt{\frac{1}{N} \sum_{1}^{N} ||i_{C}||^{2}}$$

4.7

where N is the number of points equaling 833, in a 60 Hz period which for a sampling frequency of 50 kHz. The mean of the *rms* current is then computed over one second intervals. Ultimately, estimates of  $T_A$ ,  $T_C$ ,  $I_C$ , VJ, and  $R_{ON}$  are processed over one second interval and are used to create a feature vectors at time  $t_k$ . Threshold voltage and possibly other features could be included in the future.

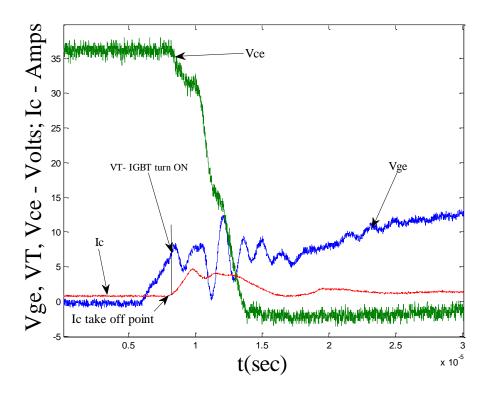

The threshold voltage is derived from sampling the raw  $V_{GE}$  signal at 100 MHz with a P5205 differential probe connected to the Tektronix 3014b oscilloscope. In order to obtain VT, the collector to emitter voltage  $V_{CE}$  was as also measured in the same fashion with a high voltage differential probe. The current flowing through the IGBT- $I_C$  was measured with current gun TCP202 also at 100 MHz frequency. A MATLAB script was written in order to detect the moment at which the threshold voltage is reached. This was done by looking at  $V_{GE}$  voltage corresponding to when the collector current began to flow. This signified the point where the transistor is turned on. (See Fig. 4.11)

Figure 4.11: Switching signal for IGBT Turn on. Figure show the signals **VT**,  $V_{CE}$ ,  $V_{GE}$ , and  $I_C$ .

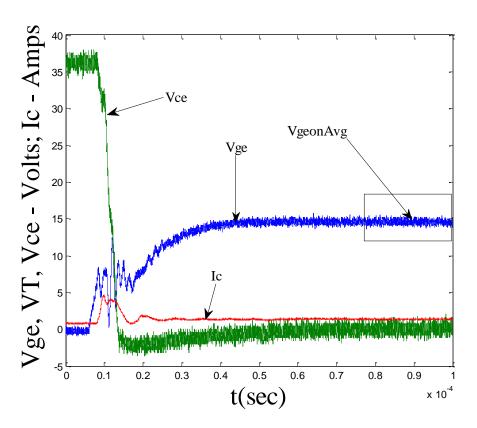

Another feature derived from the  $V_{GE}$  sampled at 100 MHZ is  $V_{GE,ON,AVG}$ .  $V_{GE,ON,AVG}$  is attained by averaging the last 1000 discrete points of the raw signal  $V_{GE}$  that

was sampled. (See Fig 4.12) It is important to know that due to the fact that some of the raw signals are being sampled at two different rates, there are two different capture rates. The data being sampled by the DT9816 data acquisition board is captured at intervals of 3 seconds and the data being sampled by the Tektronix 3014b oscilloscope is captured in 0.2 micro-second intervals. The oscilloscope is the first device to trigger based on digital logic with respect to the voltage levels of  $V_{GE}$  and the slope of  $V_{CE}$ . After the oscilloscope is triggered a control signal sent to start the sampling and data capture of the DT9816 (See Appendix A.3). In order to match the processing rate of 1 second interval for features  $T_C$ ,  $T_A$ ,  $I_C$ ,  $V_J$ , and  $R_{ON}$ ). The features  $V_T$  and  $V_{GE,ON,AV_G}$  that are obtained from data captured at 0.2 micro-second are averaged for 1 second intervals.

Figure 4.12: Show the section of  $V_{GE}$  signal that is average to obtain the KPI $V_{GE,ON,AVG}$ .

Generally speaking, multiple samples of the raw signals or input data are needed to calculate any feature. Therefore, indicators are extracted at a rate well below the sampling frequency. For this experiment it's done at an interval of one second. The various feature estimates are ultimately combined with measurements of the case temperature and passed to the remainder of the algorithm. Feature vectors computed at the time  $t_k$  are grouped into a column vector  $x_k$ . In our current implementation in the IGBT based drive, this vector includes the following features, each measured once per line cycle:

- Voltage drops across the p-n junction and drift regions, VJ

- On-state resistance of the MOSFET channel,  $R_{ON}$

- Threshold Voltage, VT

- Root-mean-squared value of the collector current,  $I_C$

- Average on-state gate-to-emitter voltage,  $V_{GE,ON,AVG}$

- Ambient temperature,  $T_A$ ,

- Case temperature,  $T_C$

These features are then placed in the health monitoring algorithm detailed in section 3.3 to determine if there is a fault developing. (See Appendix A.1 and A.2 for all code relating to feature extraction)

## 4.4 IGBT Degradation for Testing

There is the need for both healthy and degraded/faulted IGBT data collection at different operating conditions, in order to show the algorithm's ability to recognize incipient faults. As such, the motor drive was operated with the IGBT in both healthy and degraded/faulted states, in various combinations of following loading levels depending on the health of the IGBT.

- 0% loading

- 20% Loading

- 40% Loading

- 50% Loading

- 60% Loading

- 80% Loading

- 100% Loading

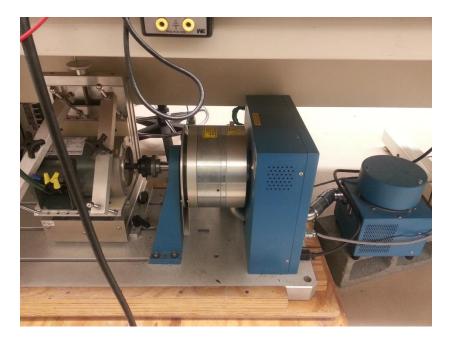

This was done controlling the power output of the motor by means of torque control. The device used for torque control was a Magtrol Model DSP6001 dynamometer as seen in Fig 4.13.

Figure 4.13: for Magtrol Dynamometer used to load Motor.

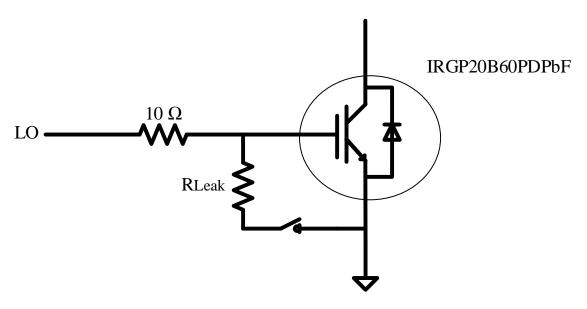

It was seen in section 2.2-2.3, that there are multiple fault mechanisms for the IGBT transistor. In this experimentation the fault mechanisms used were limited to two. A fault mechanism of the intrinsic nature, Dielectric Breakdown, and of the extrinsic nature, Latch-UP failure was chosen.

Several methods have been presented in the literature to degrade or artificially age power semiconductors [[79], [80]] to achieve these fault mechanisms. And of these Electrical and thermal stress are the two most common means by which power semiconductors are degraded. Therefore in order to simulate each of the two fault mechanisms are were selected, the methods of chronic temperature over stress and thermal cycling to induce latch-up will be used to cause Latch-Up and adding a Gate Resistor to the operating Drive will simulate Die electric Break Down due to gate leakage current. In the following sections each method will be explained in detail.

## 4.4.1 IGBT Aging due to Chronic Temperature over stress and Thermal Cycling

Multiple accelerated thermal ageing schemes are shown in the literatures [[27], [80], [81], and [82]]. Chronic temperature overstress and thermal cycling are the most prevalent thermal stress methods. Thermal overstress subjects the transistor to high temperatures for extended periods of time and can be artificially created by switching the transistor without proper heat sinking. The transistor is operated in extreme temperatures well beyond the safe operating area of the device. The transistor is aged by placing it into a Class-A amplifier and the case temperature is monitored with a temperature sensor. A controller is used to keep the temperature of the case at a constant value for an extended period of time [72].

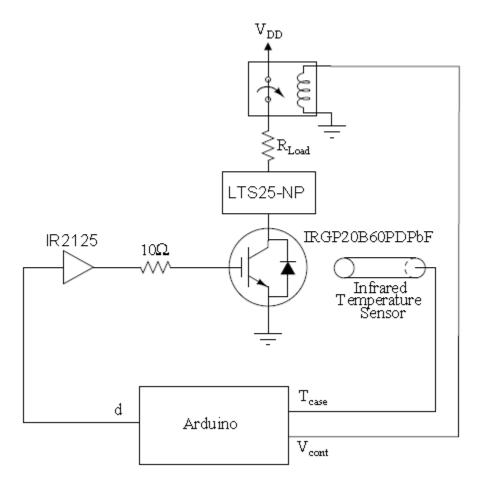

Figure 4.14: Shows a schematic of the testing setup that is used to age the IGBTs by creating latch-up. The IGBTs after degradation are then used in the motor drive for fault detection.

Figure 4.14: Circuit used to perform accelerated aging of the IGBT.

The gate signal in this circuit is a 1 kHz square waveform with a 40% duty ratio, D and a 15 Volt amplitude. The collector current,  $I_C$ , is controlled using the load resistor,  $R_{LOAD}$ , such that current flowing through the IGBT creates the wanted power dissipation in the device. The power dissipated by the IGBT is defined as

$$P_{diss} = V_{CE,ON}I_CD + P_{sw} 4.8$$

Where  $V_{CE,ON}$  is the on-state collector-to-emitter voltage and Psw the power loss due to the low switching frequency.

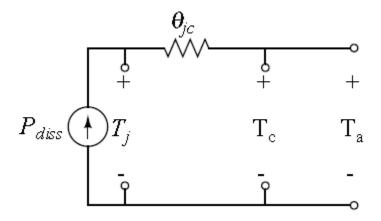

Figure 4.14: Thermal equivalent circuit for IGBT when placed in thermal degradation circuit.

The thermal circuit in Fig. 4.15 models the thermal conduction of the IGBT in the degradation circuit. Note that without the power dissipated in the IGBT, *Pdiss* due to thermal conduction is

$$P_{diss} = \frac{T_{j} - T_{C}}{\theta_{jc}}$$

4.9

where  $T_j$  is the junction temperature,  $T_c$  is the case temperature, and  $\theta_{jc}$  is the junction-to-case thermal impedance in  ${}^{\circ}\text{C/W}$  specified by the manufacturer.  $T_{j,set}$  is the desired junction temperature during the first degradation test and it is set to 125% of the maximum operational junction temperature defined by the manufacturer. For the IRGP20B60PDPbF the maximum operational junction temperature is 150 C so therefore  $T_{j,set}$  is 187.5 C. Since the junction temperature is not easy to measure the case temperature,  $T_{c,set}$  is actually set to desired value using Eq.(4.8) and Eq.(4.9) and is defined as

$$T_{c,set} = T_{j,set} - P_{diss}\theta_{jc}$$

4.10

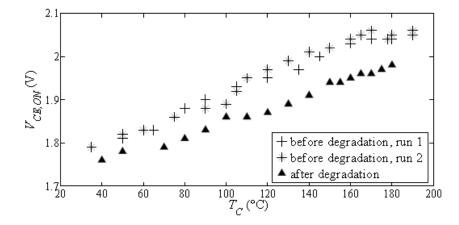

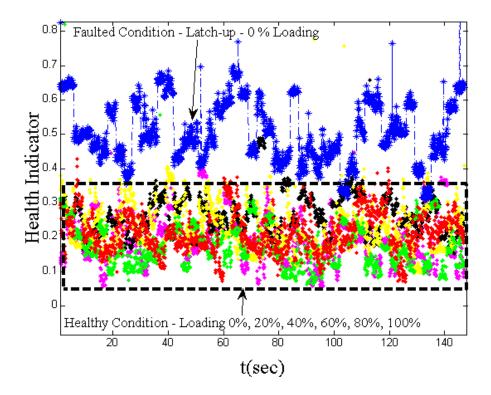

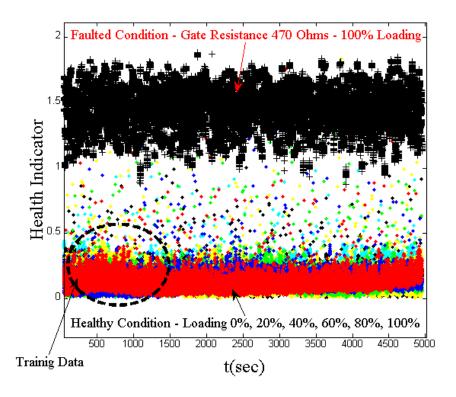

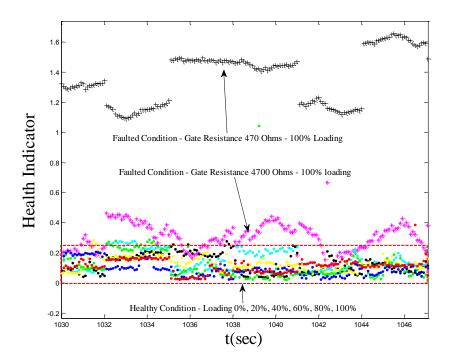

During degradation, the Arduino micro-controller, controls the case temperature at Tc,set by raising from room temperature and also monitors IC to insure the IGBT does not latch up. If the IGBT latches up during degradation VDD is disconnected using the relay which is also controlled by the Arduino. This allows the junction temperature to start falling. The IGBT is immediately tested for a short between the collector and the emitter which indicates a latch up event has occurred. After the IGBT has cooled to room temperature the IGBT is again tested for a short. If there is still a short, then the device has been permanently failed and is thus not useable for further testing. If there is no short present the degradation is restarted again after the junction temperature has been reduced but with Tj,set reduced to 50°C. This is done to ensure the latch up event has cleared and to check if gate control is still present, thus ensuring a successful degradation. The failure mechanisms that can be caused by a thermal over- stress include die-attach failures [82], gate latch-up [27], and time-dependent dielectric breakdown [72].