# PYDAC: A DISTRIBUTED RUNTIME SYSTEM AND PROGRAMMING MODEL FOR A HETEROGENEOUS MANY-CORE ARCHITECTURE

by

### Bin Huang

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2014

| Approved by:           |

|------------------------|

| Dr. Ronald R. Sass     |

| Dr. James M. Conrad    |

| Dr. Bharat Joshi       |

| Dr. Jennifer W. Weller |

© 2014 Bin Huang ALL RIGHTS RESERVED

#### ABSTRACT

BIN HUANG. PyDac: a distributed runtime system and programming model for a heterogeneous many-core architecture.

(Under the direction of DR. RONALD R. SASS)

Heterogeneous many-core architectures that consist of big, fast cores and small, energy-efficient cores are very promising for future high-performance computing (HPC) systems. These architectures offer a good balance between single-threaded performance and multithreaded throughput. Such systems impose challenges on the design of programming model and runtime system. Specifically, these challenges include (a) how to fully utilize the chip's performance, (b) how to manage heterogeneous, unreliable hardware resources, and (c) how to generate and manage a large amount of parallel tasks.

This dissertation proposes and evaluates a Python-based programming framework called PyDac. PyDac supports a two-level programming model. At the high level, a programmer creates a very large number of tasks, using the divide-and-conquer strategy. At the low level, tasks are written in imperative programming style. The runtime system seamlessly manages the parallel tasks, system resilience, and intertask communication with architecture support. PyDac has been implemented on both an field-programmable gate array (FPGA) emulation of an unconventional heterogeneous architecture and a conventional multicore microprocessor. To evaluate the performance, resilience, and programmability of the proposed system, several micro-benchmarks were developed. We found that (a) the PyDac abstracts away task communication and achieves programmability, (b) the micro-benchmarks are scalable on the hardware prototype, but (predictably) serial operation limits some micro-benchmarks, and (c) the degree of protection versus speed could be varied in redundant threading that is transparent to programmers.

# ACKNOWLEDGMENTS

I would like to thank my parent, whose deep love fueled my courage to pursue this degree.

# TABLE OF CONTENTS

| LIST C                              | F TAB                                         | ELES                                                    | vii  |  |

|-------------------------------------|-----------------------------------------------|---------------------------------------------------------|------|--|

| LIST C                              | F FIG                                         | URES                                                    | viii |  |

| CHAP                                | ΓER 1:                                        | INTRODUCTION                                            | 1    |  |

| 1.1                                 | CMOS                                          | S Technology                                            | 2    |  |

| 1.2                                 | Progra                                        | amming Paradigms                                        | 4    |  |

| 1.3                                 | Propo                                         | sed Approach                                            | 5    |  |

| 1.4                                 | Thesis                                        | s Question                                              | 6    |  |

| CHAPTER 2: BACKGROUND               |                                               |                                                         | 11   |  |

| 2.1                                 | Basics                                        | s of CMOS                                               | 11   |  |

| 2.2                                 | Architectural Trends                          |                                                         |      |  |

|                                     | 2.2.1                                         | Homogeneous Architecture vs. Heterogeneous Architecture | 13   |  |

|                                     | 2.2.2                                         | Memory Wall                                             | 15   |  |

| 2.3                                 | Hardy                                         | vare-Software Codesign at OS Level                      | 16   |  |

| 2.4                                 | Progra                                        | amming Model                                            | 18   |  |

| CHAPTER 3: GREEN-WHITE ARCHITECTURE |                                               | 24                                                      |      |  |

| 3.1                                 | Modeling Techniques                           |                                                         | 24   |  |

| 3.2                                 | Theoretical Model of Green-White Architecture |                                                         |      |  |

| 3.3                                 | An Implementation of Green-White Architecture |                                                         |      |  |

|                                     | 3.3.1                                         | Hardware Simulation                                     | 30   |  |

|                                     | 3.3.2                                         | Hardware Prototype                                      | 31   |  |

| CHAP                                | ΓER 4:                                        | DESIGN OF PYDAC PROGRAMMING FRAMEWORK                   | 34   |  |

| 4.1                                 | Programming Model                             |                                                         |      |  |

|                                     | 4.1.1                                         | Divide-and-Conquer Strategy                             | 36   |  |

|                                     | 4.1.2                                         | Two-Level Programming Model                             | 37   |  |

|                                     | 4.1.3                                         | Fibonacci Algorithm Coding Example                      | 39   |  |

|                       |                        |                        |                                                  | V1 |

|-----------------------|------------------------|------------------------|--------------------------------------------------|----|

|                       | 4.2                    | Design                 | n of PyDac Runtime                               | 40 |

|                       | 4.3                    | Concl                  | uding Remarks                                    | 43 |

| CHAPTER 5: EVALUATION |                        |                        | EVALUATION                                       | 45 |

|                       | 5.1                    | Performance Evaluation |                                                  |    |

|                       |                        | 5.1.1                  | Benchmark Suite                                  | 45 |

|                       |                        | 5.1.2                  | Scalability                                      | 46 |

|                       |                        | 5.1.3                  | Resilience                                       | 47 |

|                       | 5.2                    | Evalua                 | ating Programming Productivity by Case Study     | 55 |

|                       |                        | 5.2.1                  | Strassn's Algorithm                              | 55 |

|                       |                        | 5.2.2                  | Symmetrical Tridiagonal Eigenvalue Decomposition | 56 |

|                       |                        | 5.2.3                  | Recursive FFT                                    | 58 |

|                       |                        | 5.2.4                  | Analysis                                         | 60 |

| C                     | CHAPTER 6: CONCLUSION  |                        |                                                  | 67 |

| C                     | CHAPTER 7: FUTURE WORK |                        |                                                  | 70 |

| REFERENCES            |                        |                        | 72                                               |    |

# LIST OF TABLES

TABLE 3.1: Summary of the hardware prototype.

32

# LIST OF FIGURES

| FIGURE 1.1:  | High-level block diagram of conventional runtime system.                        | 8  |

|--------------|---------------------------------------------------------------------------------|----|

| FIGURE 1.2:  | High-level block diagram of distributed runtime system.                         | 8  |

| FIGURE 3.1:  | High-level block diagram of the green-white architecture.                       | 27 |

| FIGURE 3.2:  | High-level block diagram of a green core.                                       | 28 |

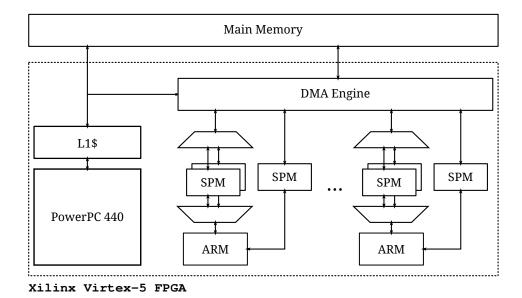

| FIGURE 3.3:  | $\operatorname{High-level}$ diagram of green-white prototype on an FPGA device. | 32 |

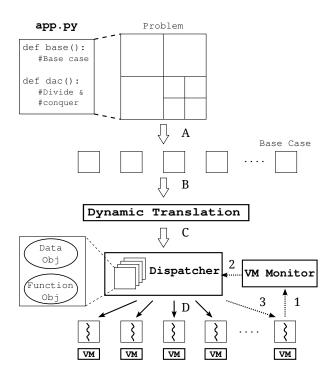

| FIGURE 4.1:  | PyDac algorithm template                                                        | 38 |

| FIGURE 4.2:  | Fibonacci algorithm implemented in PyDac.                                       | 40 |

| FIGURE 4.3:  | Proposed resilient runtime system on green-white architecture.                  | 41 |

| FIGURE 4.4:  | Control flow of user-level thread library                                       | 42 |

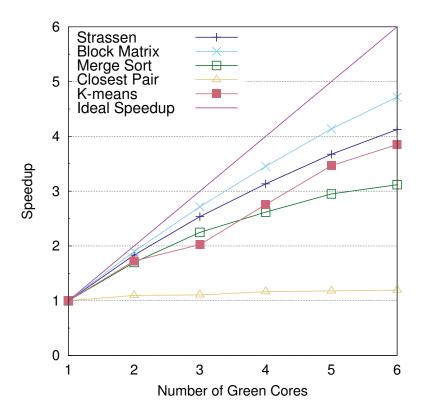

| FIGURE 5.1:  | Speedup on green-white architecture.                                            | 48 |

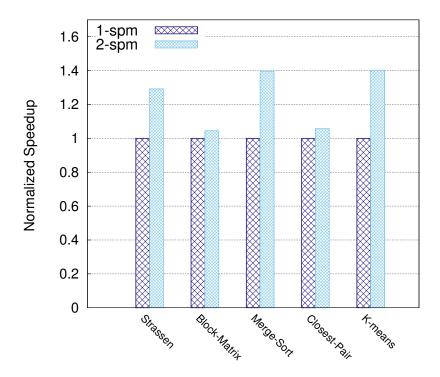

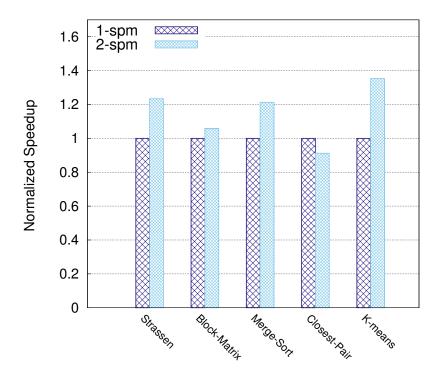

| FIGURE 5.2:  | Performance impact of adding second SPM: one green core                         | 49 |

| FIGURE 5.3:  | Performance impact of adding second SPM: six green cores                        | 50 |

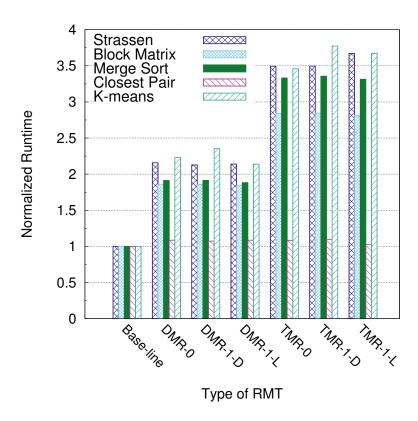

| FIGURE 5.4:  | Normalized runtime on green-white architecture.                                 | 53 |

| FIGURE 5.5:  | Strassen's algorithm                                                            | 56 |

| FIGURE 5.6:  | Strassen's algorithm implemented in PyDac                                       | 57 |

| FIGURE 5.7:  | Symmetric Tridiagonal Eigenvalue Algorithm                                      | 58 |

| FIGURE 5.8:  | Symmetric Tridiagonal Eigenvalue PyDac Implementation                           | 59 |

| FIGURE 5.9:  | A Divide-and-Conquer Algorithm for Radix-2 FFT                                  | 60 |

| FIGURE 5.10: | Recursive FFT implemented in PyDac                                              | 61 |

#### CHAPTER 1: INTRODUCTION

The technologies used to implement integrated circuits have profound impacts on computer system design and programming paradigm design. For many decades, the dominant technology—complementary metal oxide semiconductor (CMOS)—has enabled frequency scaling and doubling transistor density. This has kept computer architecture research narrowly focused on making single core faster, year after year, which also reinforced a sequential programming paradigm.

Although CMOS technology is slowing in terms of clock frequency growth rate, it is still expected to double the number transistors per chip every two years for many generations [1]. Moore's Law, a trend observed by Gordon Moore [2], states that the density of transistors on a chip doubles every two years. Moore's Law has fundamentally fueled the advancement of computing technology in the past.

Three notable changes in the fundamental assumption with CMOS technology have occurred. First, the Dennard Scaling [3], which states that the reduction in the transistor feature size is accompanied by improvement in power efficiency, had reached its end in the 2000's. Secondly, the reliability of CMOS has become more difficult to sustain, primarily due to process variation and single-event upset. Thirdly, the energy cost of moving data has become comparably more expensive than computation. Because of these changes, the characteristics of future computing devices are likely to be very different, leading to dramatically different chip architectures. Moreover, the new chip architectures have already required new programming paradigms, or at least a renewed emphasis on parallel programming paradigm. We will take a closer look at the impacts next.

#### 1.1 CMOS Technology

Due to the end of Dennard Scaling, power efficiency has emerged as a first-class design constraint. The chip industry has attacked this problem at different levels, such as voltage scaling and architectural innovation. For example, research has shown that aggressive supply voltage scaling greatly improves the energy efficiency of a single processing unit [4]. For another example, the chip industry introduced multicore microprocessor chips [5, 6] to work around the power efficiency issue. However, the introduction of multicore technology was not completely satisfactory. Esmaeilzadeh et. al [7] have predicted transistor under-utilization on future chips due to a stringent power budget. They suggest radical micro-architectural innovations beyond CPU-like or GPU-like multicore designs. Examples of such unconventional chip architecture have been proposed with a heterogeneous mix of complex and simple cores [8, 9, 10]. The heterogeneous many-core architecture promises a good balance between single-threaded performance and multithreaded throughput. More importantly, it utilizes transistors in an energy-efficient manner by dedicating resources to an individual application or a group of applications sharing common compute kernels.

In addition to power, reliability will be more difficult to sustain in the future. First, advantages of low-power techniques (e.g., aggressive supply voltage scaling) are not free. There is a tradeoff between power and reliability; specifically, power efficiency from voltage scaling is achieved at a cost of an increasing soft error rate [11]. Secondly, parameter variation will pose a major challenge for the design of future high performance microprocessors [12]. One serious consideration that must be addressed is the ability of applications of interest to run through a variety of failures. Current high-performance computing (HPC) systems rely on checkpoint/restart (C/R) to recover from faults. As system size continues to grow, the overhead of global C/R will likely become a significant percentage of an application's run time [13, 14]. In order to save the overhead, local fault confinement and recovery mechanisms have

been proposed [15]. Not only does C/R suffer from high overhead, but it also deals with a subset of possible faults. Silent data corruption (SDC) is a specific class of fault that the C/R technique could not mitigate [16]. Failing to detect SDC could significantly undermine the fidelity of simulation results, because invalid results may still be reported to end users. Replication techniques can detect and mitigate SDC but have been prohibitive for adoption by HPC systems due to high overhead. As the system-level size of HPC systems continue to grow, replication techniques have reignited research interest. Ferreira et al. [14] simulated an HPC system with more than 20,000 sockets and proved that replication is a viable alternative to the traditional C/R approach.

Thirdly, data movement will overtake—if it has not already—the floating-point operation as the major contributor to power usage [17]. The energy cost of data movement will limit the usage of hardware design techniques, such as out-of-order execution. These techniques have been successfully used in high-performance microprocessors in the past. To further save energy cost of data movement, a more aggressive memory management scheme may be needed, e.g., only moving data when it contributes to the solution. One mechanism that has been proposed is to use named memory segments and make the movement of data more explicit to the programmer [18]. These authors [18] and others [19] also advocate the use of a form of scratch-pad memory (i.e., software-controlled memory). Scratch-pad memory does not implement a tag RAM and complex comparator logic that are found in conventional direct or set-associative caches, which saves transistors and power. (Low-power embedded systems have long been leveraging scratch-pad memory [20, 21].) In addition, it reduces cache contention, further minimizing unnecessary data movement. Adopting scratchpad memory was reported to significantly improve energy efficiency in one case of high-end computing [19].

Assuming there is no miraculous technological breakthrough, these trends suggest

that future devices and architectures will be astonishingly different. Most likely, future CMOS chips will (a) consist of a large mix of heterogeneous computing cores, (b) use a radically different memory subsystem, and (c) experience higher rates of faults.

#### 1.2 Programming Paradigms

All architectural changes will have a profound impact on how human programmers interact with future computing machines. For a good example, explicitly parallel programming paradigms have become more mainstream with the industry introduction of multicore microprocessor chips [5, 6]. We will take a closer look at the impacts on programming paradigm design next.

First, parallel programming paradigms have replaced the sequential programming paradigm. Before the multicore era, the sequential programming paradigm was so central to every computing system that every piece of software—from applications to libraries to operating systems—could assume compatibility with future devices. In addition, the frequency scaling granted a "free lunch" that software programmers have enjoyed for many years [22]. Due to the free performance lunch, software programmers added layers of abstractions into their software. This free ride mitigated or hid the performance overhead involved with adding layers of abstractions. More importantly, the resulting portability and programming productivity paid off the performance overhead many times. For example, high productivity programming languages, such as Java and Python, are built on top of extra software layers—virtual machines that provide portability to cross-platform programming. The end of free performance lunch now makes the use of extra layers of abstractions in software less viable. More importantly, while removing abstractions from the software stack may benefit performance, such actions will reduce programming productivity.

Moreover, software has become more fragile than before. Generally, software programmers could assume infallible hardware, which greatly simplifies software de-

velopment. However, it is becoming more difficult to assume infallible hardware. The overhead of maintaining infallibility will become a significant percentage of an application's run time [13, 14]. Therefore, recent programming framework provides application programming interfaces (APIs) to programmers for expressing resilience concerns explicitly [15]. Such APIs clearly impose more burdens on programmers.

#### 1.3 Proposed Approach

Combining these facts and trends together, one may wonder how to design more effective computer systems and programming paradigms. Consequently, the invention of a novel programming paradigm and an associated runtime system is critical. Complicating this investigation is the fact that the exact nature of these future computing machines is far from clear, which means that human understanding of the hardware and software will have to co-evolve. We believe that the best way to address these issues is to think of them "organically". In other words, we would like to look at this problem from a hardware-software codesign perspective. This dissertation focuses on the software aspect of this evolution.

We chose one of the most well-known parallel design patterns—divide-and-conquer—to begin this research. Design patterns are useful concepts for programmers, strongly encouraging and enabling the reuse of successful designs and proven techniques. Each design pattern describes a problem that repeatedly occurs and then describes the core of the solution [23]. Not only are design patterns established in sequential programming paradigm, there are also design patterns for the development of parallel applications [24, 25].

Specifically, we designed a two-level programming model and a runtime system based on the divide-and-conquer strategy. Divide-and-conquer is a well-known strategy for designing algorithms in the computer science community. Three steps are usually involved in this technique: divide, conquer, and combine. The divide-and-conquer strategy recursively decomposes a problem into smaller sub-problems, which

in turn are decomposed into sub-sub-problems, and so on. Generating a very large number of parallel tasks without a great deal of programming effort is possible with this strategy. The two-level programming model is implemented in Python language as a library extension. It hides task communication, load-balancing, and resilience from programmers. A runtime system built on distributed Python virtual machines maps the two-level programming model to heterogeneous many-core architecture. Due to independent and parallel tasks, the runtime system is able to gracefully degrade when the hardware is hit by a fault. In particular, the runtime system monitors hardware for potential soft errors. If necessary, it resets a faulty core and reissues the task. However, this is not always enough. For example, output data may be corrupted, requiring a different technique for the runtime system to detect. In that case, the runtime system runs multiple copies of identical tasks and checks the results of those tasks for output data corruption. If data corruption is detected, the runtime system can either reissue a task or use a voting mechanism to determine the correct result if enough copies are available.

#### 1.4 Thesis Question

To evaluate the proposed programming model and runtime system, we present a novel architecture called *green-white* architecture meant to stand in for some future "unconventional" chip architecture. It features a mix of simple and complex cores and a much flatter memory subsystem. Specifically, our model consists of two types of processor cores. It has many simple, energy efficient—and inherently less reliable—processor cores (called "green cores") and a few more robust, protected processor cores (called "white cores"). The white cores have a conventional memory hierarchy while the green cores treat the main memory as a collection of write-once memory segments. The white cores have a conventional symmetric multiprocessing (SMP) operating system and runtime while the green cores run independently with a "close to metal" runtime. To test the spectrum, we also have an implementation for conventional SMP

architecture.

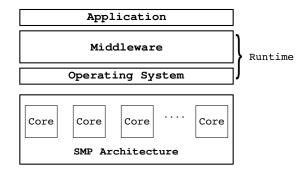

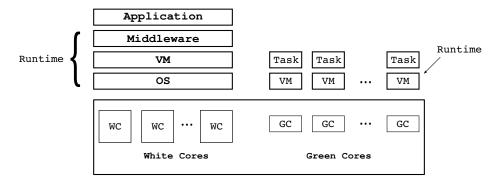

The key thesis question can be phrased as follows: Is a programming model and a runtime system built upon distributed virtual machines superior to monolithic runtime on an architecture under the cross-cutting constraints of performance, resilience, and productivity? The comparison is illustrated in Figure 1.1 and Figure 1.2. In Figure 1.1, the conventional runtime system is built entirely upon a monolithic operating system and SMP hardware. Adding layers of abstractions to the middleware in a vertically integrated system has been successful. Figure 1.2 presents the proposed programming model and runtime system built upon a set of decoupled distributed virtual machines. The choice of virtual machine is motivated by the fact that it is the foundation for many high productivity languages. In addition, adopting a virtual machine in the design of a runtime system provides software compatibility across various architectures.

The thesis question is broken down into three subordinate questions as follows.

- 1. Does a runtime system built upon a set of decoupled distributed virtual machines deliver good performance? Performance is measured by time-to-completion for a given task. In the context of this work, we measure performance under two different scenarios: (a) the absolute performance of adding more resources to the system (a.k.a. strong scaling), and (b) the relative performance under faults. Achieving a linear speedup is usually very difficult due to the incurred overhead of resource management. Our reasoning is that if there is no speedup in the first scenario or there is a significant overhead in the second scenario, then the proposed design is not viable. To answer this question, we will run multiple micro-benchmarks to measure performance numbers in both a fault-free environment and a faulty environment.

- 2. Does a runtime system built upon a set of decoupled distributed virtual machines sustain transient faults? A conventional monolithic runtime system itself is a

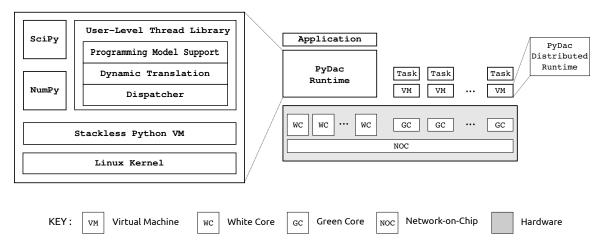

Figure 1.1: High-level block diagram of conventional runtime system. The runtime system is entirely built upon a monolithic operating system and SMP hardware. The runtime system may be "bloated" because of too many abstractions in the software stack.

Figure 1.2: High-level block diagram of distributed runtime system. The runtime system is built upon distributed virtual machines. White cores have a conventional SMP operating system and runtime while green cores run independently with a "close to metal" runtime. Virtual machines provide support to high-level programming language and software compatibility across different architecture.

single point of failure. A transient fault could easily cause the monolithic runtime system to crash. Therefore, the monolithic runtime system heavily relies on the C/R technique to recover from a fault. However, as the system size and the degree of parallelism continue to grow, the C/R technique is expected to be inefficient. A runtime system that can sustain transient faults gives the system an opportunity to gracefully degrade while increasing resilience. To answer this question, we will use a fault injection mechanism to emulate transient faults on hardware and observe how the runtime system behaves.

3. Is the programming paradigm supported by the runtime system productive? Programming productivity is equally important to system performance. The conventional programming paradigm in high-performance computing features low-level language, such as C. While it is easier for programmers to control the behavior of a machine, it is also counter-productive to express algorithms. High-level languages have been observed to be preferred when quick implementation is required. Low-level languages are involved in rewriting the code only when additional performance is required. Since programming productivity is less measurable than other system indices (e.g., power and performance), case studies will be conducted to indirectly evaluate the effectiveness of the proposed programming model. We will present the source code of multiple micro-benchmarks and rely on the reader's judgment to assert our point.

To demonstrate the feasibility and quantify the behavior of the proposed approach, we implement a hardware prototype of green-white architecture on an field-programmable gate array (FPGA) device. This hardware is used to represent a mix of energy-efficient, simple cores and fast, conventional processor cores. We evaluated the proposed programming model by running multiple micro-benchmarks on the hardware prototype. In addition, we used a fault injection mechanism to emulate transient faults on the hardware and measured the recovery cost.

In addition to the central purpose of this thesis, there are several practical contributions:

- A runtime system based on a set of decoupled distributed virtual machines sustains transient faults on unreliable heterogeneous hardware through local fault recovery.

- Designing a runtime system that combines full-fledged virtual machine and "bare-metal" virtual machine for heterogeneous hardware is feasible.

- Programming a distributed runtime system with a two-level programming paradigm does not undermine programming productivity.

The rest of the dissertation is organized as follows. Chapter 2 presents technology trends that have fundamental impacts on chip architecture and reviews the related works. Chapter 3 details the design of green-white architecture and the hardware prototype. Chapter 4 shows the design of the PyDac programming model and the runtime system. Chapter 5 evaluates the proposed system from the perspective of performance, resilience, and programmability. Chapter 6 summarizes this dissertation and Chapter 7 discusses future works.

#### CHAPTER 2: BACKGROUND

This chapter first reviews the technological trends of CMOS in recent years. Then, it examines the advent of many-core technology and related design issues. Thirdly, this chapter inspects some hardware-software codesigns from the perspective of the operating system. Lastly, it reviews parallel programming models and compares them to the proposed PyDac programming model.

#### 2.1 Basics of CMOS

CMOS will likely remain the dominant technology for integrated circuit design for another ten years [1]. For the advancement of CMOS technology, Gordon Moore observed that the transistor density doubles every two years [2]. Engineers have been able to reduce the transistor feature size and improve power efficiency for many generations of CMOS technology. Power efficiency was improved by reducing the total capacitance—as seen by the gates' outputs—and lowering the supply voltage, which is also known as Dennard Scaling [3]. This scaling resulted in a constant power density—a key factor in the design of computer architecture. The return of Dennard Scaling began to diminish in the early 2000's. Specifically, supply voltage is close to the threshold voltage and has leveled off [26]. Further reduction of supply voltage is costly; it requires a reduction in the threshold voltage, which has a negative impact on lost power from leakage current [27]. In addition, supply voltage that levels off has a negative impact on maximum operation frequency. The frequency is roughly linear to the supply voltage. Given a constant threshold voltage, the lower the supply voltage is, the longer it takes a signal to propagate. The maximum operation frequency must decrease accordingly to avoid timing violation. Consequently, the end of Dennard Scaling forced the chip industry to shift into a new design paradigm. The old paradigm that focused on improvement of single-threaded, sequential programs' performance was replaced by a new one that focuses on multithreaded, parallel programs.

The reliability of CMOS transistors is more difficult to sustain as the feature size continues to shrink. Parameter variation poses a major challenge to the design of future high performance microprocessors [12]. For example, random dopant fluctuation (RDF), which means that the dopant atoms implanted in the transistor are unevenly distributed, is a significant variation source [28]. Such variation may lead to an increase in intermittent or permanent faults, which may result in unexpected timing violations. The other major cause of the reliability issue is single event upsets (SEUs). An SEU taking place in dynamic random-access memory (DRAM) may be caused by high-energy particles (e.g., cosmic rays), which penetrates the die surface and creates a bit-flip [29]. Logic also becomes more susceptible to SEUs, because of the reduction in critical charge of logic circuits and the decrease in the feature size [30].

Data movement, which is significantly distance-dependent, continues to become more expensive than compute in terms of energy consumption. For instance, for 40-nanometer technology, moving 64 bits of data just from off-chip to on-chip would cost a few nanojoules; or moving 64 bits of data for a few millimeters on-chip would cost hundreds of picojoules. However, performing a double-precision fused multiply add (FMA) would cost only tens of picojoules [31]. An alternative technology, optical interconnect, shows that energy consumption is not dependent on distance. However, optical technology is not ready for production [17], and distance-dependent data movement poses a challenge to energy-efficient computing.

We have discussed four major technology trends in this section. As Moore's Law predicts, CMOS feature size will continue to decrease. For pragmatic reasons, transistors are not getting any faster. In addition, CMOS will become less reliable because of parameter variation and SEUs. Lastly, data movement will cost more energy than

compute. The impacts of these trends on chip architecture will be discussed in next section.

#### 2.2 Architectural Trends

Chip architectures synthesize what technology grants into compute power. Before the end of Dennard Scaling, uniprocessor architecture dominated the mass market, and a software ecosystem had been built on it. The end of Dennard Scaling forced the industry to shift to the multicore design paradigm. Now parallel architectures are ubiquitous, from low-end mobile processors to high-end server-class processors. It is not yet clear whether homogeneous architecture or heterogeneous architecture is better. We discuss major architectural trends in this section.

#### 2.2.1 Homogeneous Architecture vs. Heterogeneous Architecture

When chip vendors introduced their first multicore microprocessors [5, 6], adding an identical copy of processor core to the design was a natural choice. Homogeneous architecture usually contains tens of processor cores. These cores are connected by a network-on-chip (NOC) with a cache-coherent memory hierarchy. The IBM POWER7 processor [32] is an eight-core design with a large on-chip embedded dynamic random-access memory (eDRAM) caches. Each core supports a four-way simultaneously multithreaded operation, and the eight cores provide 32 concurrent threads in total. To reduce power, the Power7 operates at a modest frequency and focuses on microarchitecture innovation for high performance. The Tilera's TILEPro64<sup>TM</sup>processor [33] features 64 simple, three-way very long instruction word (VLIW) processor cores (tiles) connected by an on-chip mesh interconnect. Each tile can run a full Linux independently, or a group of tiles can run a full SMP Linux. Intel Core<sup>TM</sup>i7 processor [34] is a high-performance general-purpose processor featuring out-of-order speculative microarchitecture.

While the homogeneous architectures have made significant impacts, many researchers and experts suggest heterogeneous many-core architectures as the future direction [8, 35]. Such a statement is based on an empirical observation called Pollack's rule [36, 37], which states that performance increase is roughly proportional to the square root of the increase in chip area. Due to the stringent power constraint and the energy cost of data movement, the return of architectural techniques (e.g., deep pipelining) diminishes. Therefore, computer architects leveraged Pollack's rule in a way that designs are smaller in terms of area and simpler in terms of data path. Such smaller and simpler designs consequently deliver less performance per unit. To further limit power consumption, chips have to run at relatively low clock speeds, which are expected to remain close to a few GHz, not utilizing the full potential. (Running at the full speed makes it uneconomical to cool [1].) Hence, there will be many small, simple, and slow processor cores on the chip [38].

In addition, there are conventional processor cores that are designed for high single-thread performance. The processor cores are coupled with the small, simple, and slow processors cores. These may leverage speculative execution and out-of-order techniques, which bring several benefits: (a) they compensates single-threaded performance and (b) they may provide a familiar software ecosystem to programmers (e.g., x86).

Taking these factors into consideration, future architecture is expected to combine both big, complex cores and small, simple cores to achieve good design trade-offs. Obviously, such architecture is heterogeneous. In fact, it has been shown that, for many workloads, heterogeneous hardware achieves better performance and power efficiency than conventional, general-purpose hardware [39].

System-on-chip (SoC) designs, which target mobile phones and embedded systems, are already heterogeneous and usually have a very tight power budget and expect a good performance. For example, the TI OMAP 5432 [40] uses two ARM Cortex-A15 processors for general-purpose applications and ARM Cortex-M4 processors for real-time applications. To process graphics and video applications, it has one dedi-

cated graphics accelerator and video accelerators. ARM's big.LITTLE<sup>TM</sup> architecture [41] combines high-performance Cortex-A15 processors and energy efficient Cortex-A7 processors. Cortex-A7 is an in-order processor that has a pipeline length between eight stages and ten stages. Cortex-A15 is an out-of-order processor with a pipeline length between 15-stages and 24-stages. ARM's report shows that the average performance of Cortex-A15 is two times as much as that of Cortex-A7, while the average energy efficiency of Cortex-A7 is three times as much as that of Cortex-A15. As a result, the big.LITTLE system enables threads to be executed on the processing resource that is most appropriate. From a programmer's perspective, the difference between Cortex-A15 and Cortex-A7 is hidden by the operating system.

For high-end computers, the power budget is still tight but less stringent. Accelerators are usually implemented as discrete components to provide higher performance [42, 43, 44]. These accelerators usually require a host computer for a software environment that is familiar to users. The Cell processor [45] combines processors optimized for performance per transistor on compute-intensive applications, with a more conventional processor architecture. The Cell processor also introduces software-controlled memory to allow overlapping computation with memory transfer. The SARC architecture [46] reuses Cell Synergistic Processing Elements but adds application-specific instructions.

#### 2.2.2 Memory Wall

The exponential improvement of CMOS transistor and architectural innovation results in a tension between processor and main memory (i.e., "memory wall"). For economic reasons, the manufacturers of main memory have been focusing on the density instead of the performance [1, 47]. For a long time, memory latency has improved slower than the chip clock rate. Although the flattening of clock rate has a positive impact on "memory wall," the increasing number of cores continues to generate more concurrent memory requests and thus intensify this issue. The sheer number of par-

allel cores in future chips will continue to overwhelm current memory hierarchies, creating a situation where memory subsystems limit the rate of computation, but not the availability of parallelism or clock rate. To address this, some have suggested software-controlled data movement (rather than hardware-controlled) in the memory hierarchy [48]. Other recent developments suggested a programming model based on message passing through non-cache-coherent shared memory [49]. Others have proposed radically new memory hierarchies. In the Fresh Breeze project, Dennis et al. propose a view of main memory as a collection of write-once memory chunks [18]. The write-once principle frees programmers from maintaining the consistency of shared objects and leads to a functional view of memory, because one parallel task will not overwrite the internal memory of another task. It also enables active Checkpoint/Restart—the ability to concurrently checkpoint, while the application continues to progress.

#### 2.3 Hardware-Software Codesign at OS Level

Operating system (OS) is arguably the most important software layer in runtime system. Heterogeneous architectures poses design challenges to the OS. Reconfigurable Computing community has long been successfully leveraging FPGA technology to deploy architecture that combines conventional processor cores and reconfigurable accelerators, using hardware-software codesign methodologies [50, 51, 52]. One of the most important codesign process aspects is to determine the boundary between the hardware and the software. A proper boundary normally tries to meet certain requirements. First, the boundary needs to be well understood by both software and hardware engineers to reduce non-recurring engineering cost. Secondly, the reconfigurable accelerators need to be treated as first-class citizens for efficiently utilization. Codesign methodology often takes advantage of the standardized semantics, such as UNIX semantics [51] and Pthreads [52], which greatly ease the interaction between the software and the hardware.

Hthread [52] proposed the design of hardware thread that complies with Pthreads APIs. In the hthread model, programmers specify their applications as a set of concurrent threads using the Pthreads semantics. A hardware thread shares memory with other threads and uses Pthreads synchronization primitives for communication.

ReconOS [53] also exploited thread-level parallelism as hthread does. In particular, the hardware threads are written in hardware description language (HDL) instead of being generated from a sequential language. When a hardware thread is created at runtime, a dedicated software thread is also created to represent its hardware counterpart. The dedicated software thread can communicate with other software threads through OS primitives.

BORPH [51] proposed the design of hardware process that conforms to the standard UNIX process semantics. A hardware process has a peer-to-peer relationship with software processes or other hardware processes and may communicate with its peers through UNIX file pipe which provides a one-way flow of data.

However, Moore's Law will grant more processing units per chip, which will force programmers to invest in parallelization techniques to increase the performance of their algorithms. In a multithreaded environment, programmers retrofit fine-grain locking to parallelize applications. Linux is the de facto OS in high performance computing. Since the chip industry shifted the paradigm from multicore architecture to many-core architecture, Linux has undergone many improvements addressing scalability issue. Big Kernel Lock (BKL) was first introduced into Linux to ease the transition to SMP systems. Essentially, the BKL is a global lock that only one thread in the kernel space can hold it. The BKL was later replaced by fine-grained locking mechanisms, such as mutex, spin-lock, and Read-Copy Update (RCU) [54]. More recently, an example of scalability efforts includes an analysis of Linux scalability to a 48-core machine [55]. In a high core count system, finding an optimal lock granularity for threads can be very challenging. The scalability issue in Linux has motivated

several new operating system designs. Factored operating systems (FOS) [56] factors OS services into a set of communicating servers that are bound to distinct processing cores. An application sends messages to a server, which then executes the OS code and returns the result. Such design completely avoids global cache-coherent shared memory and the use of hardware locks. Multikernel [57] treats the machine as a network of independent cores and assumes no inter-core sharing at the lowest level. Each core holds a replication of the machine state. These new OS designs highlight the pressure a conventional monolithic kernel suffers. In addition, future hardware will be more difficult to sustain its reliability due to the parameter variation [12]. It is not clear if conventional monolithic kernel, which is a single point of failure, will be able to handle faults efficiently.

Our approach differs from these works in that we choose semantics of Python byte code as the core of our codesign. In the green-white architecture, we synthesize reconfigurable resources into soft processors to run distributed, lightweight Python virtual machines. Each lightweight Python virtual machine is capable of executing a parallel task represented by Python byte codes. Parallel tasks are independent in a way that a faulty green core is recovered locally without interrupting the application.

#### 2.4 Programming Model

Programming models are roughly divided into three categories [58]: pseudo-comment directives approaches, language-based approaches, and library extension approaches. PyDac falls into the library extension category by providing programmers with a Python library to map tasks to the distributed Python virtual machines. The library approach ensures portability of the PyDac framework and eases the adoption of the framework by domain scientists.

Message passing interface (MPI) is currently the dominant programming model in HPC arena. With the emergence of the chip multiprocessors, a hybrid model called "MPI+X" is expected to better utilize hierarchical features of the hardware. For

example, "MPI+OpenMP" [59], which combines the library extension approach and the pseudo-comment directive approach, builds a distributed memory programming model on top of a shared-memory programming model. To leverage increasingly popular heterogeneous hardware, OpenACC is proposed as an OpenMP-like directive set that supports accelerators, which is based on the concept of separate host and accelerator memory but emphasizes implicit memory management, which reduces programming burden on programmers. However, this hybrid model still requires programmers to invest a great amount of coding effort to utilize cores effectively [60]. In addition, MPI requires the number of processes to be specified when an application is launched. In the proposed programming model, the number of processes can be determined through the runtime system by dynamically adjusting the base case size.

OpenMP [61] is a popular programming paradigm for multicore SMP architectures. It inspires many similar programming models, such as CellSs, StarSs, and OmpSs. CellSs [62] is a programming model specifically designed for the Cell/BE processor. Similar to OpenMP, CellSs uses the pseudo-comment directives approach to create parallel tasks. However, when programmers annotate functions that need to be offloaded to accelerator cores, the annotation does not necessarily indicate parallel execution of a code section but a candidate for parallel execution. CellSs also features a source-to-source compiler by which applications are composed of two types of binaries. In fact, CellSs is contained in StarSs [63] as one of the instantiations. The StarSs programming model supports a wider range of architectures including multicore processor, GPU, Cell/BE, and cluster. Therefore, it provides a more natural support for heterogeneity than OpenMP, while the portability is not compromised. StarSs views architectures that feature separate memory spaces (i.e., host and device memories) as a two-level memory hierarchy and provides a software layer that implements memory coherence policies. The runtime system of StarSs automatically handles the data movement in its two-level memory hierarchy.

Sequoia [64] and Merge [65] introduce new language constructs to support mapreduce patterns. Sequoia abstracts a memory hierarchy as a tree of distributed memory modules and constrains the compute kernels to operate on leaf nodes. Task

variants are generated statically by the compiler to be portable across levels of memory hierarchy. In contrast to using a task variant to suit different levels of memory

hierarchy, PyDac focuses on a flatter memory hierarchy and generates tasks that

specifically run on the scratch-pad memory. Merge, on the other hand, maps an application to a library of function-intrinsics that encapsulate accelerator-specific code.

Merge's runtime automatically distributes computation to accelerators. In addition,

Merge's framework removes OS and driver layers for accelerators. Similar to Merge,

PyDac removes OS and driver layers on green cores to eliminate software bloat. However, PyDac allows tasks to migrate between cores by leveraging virtual machine byte

codes.

Intel Thread Building Blocks (TBB) [24] is a C++ template library that is based on a work-stealing scheduler and provides control on low-level parallelism. It supports many popular design patterns, such as pipeline and divide-and-conquer. It abstracts away the complexity of using native threading packages (e.g., Pthreads). However, TBB only aims at shared memory architecture. In contrast, PyDac targets not only shared memory but also a novel memory subsystem that supports write-once memory model.

Intel Concurrent Collections (CnC) [25] is a programming model that provides higher level abstraction than TBB. CnC separates the development of parallel applications into two distinct stages. The first stage requires a domain expert, who understands data dependency and control dependency in an application but may not be an experienced parallel programmer, to write program in terms of high-level application-specific operations. The second stage relies upon tuning experts, who have expertise in extracting maximum performance from the computer, to tune the

program for a specific architecture. In fact, CnC could be built on top of TBB as an approach to leverage shared memory computers. CnC imposes several important rules on domain experts. For example, computation (called "step collection" in CnC) may not reference any global values. Data (called "item collection") is referenced by value instead of by its location. In addition, dependency should be explicitly stated. Such rules are not existent in serial languages, such as C/C++. These rules together eliminate race condition at the domain expert level and deliver explicit and useful constraints to tuning experts. Similarly, PyDac requires a base case to be referentially transparent. Each green core may reference data by its value instead of by location. While CnC provides a higher level abstraction to programmers that may require additional software support, PyDac intends to bring high-productivity programming closer to the hardware. In addition, PyDac focuses on the divide-and-conquer design pattern and provides a direct hardware support.

Microsoft's Accelerator [66] hides the GPUs details from programmers by providing C# APIs (each associated to one array operation) and uses just-in-time compilation. PyDac does not use just-in-time compilation technique but requires some C libraries running on green cores to be statically compiled.

Parallex [67] is a programming model specifically designed for extreme-scale computing systems. Parallex has a view of global address space where objects (e.g., data and code) are identified by globally immutable names. Parallel threads in Parallex are first class objects with immutable names. As such, it is possible to move computation to data, which may reduce data movement and save energy. Instead of statically allocating threads, ParalleX dynamically schedules multiple threads using message-driven mechanisms for moving the work to the data.

More recently, there is a renewed interest in task-based parallel programming models [68]. Programmer are responsible for identifying which parts of the application can be computed in parallel. A runtime environment maps these parallel runnable

computations to the available processors in the system. Cilk [69] is a widely available extension of C, which is a popular example of task-based parallel programming. Cilk uses keywords, such as *spawn* and *sync*, to identify safely runnable parallel computations. It does not specify any limitation on the size or the simplicity of these parallel tasks. Atlas [70] is a Java-based runtime system that adapts the Cilk programming model, extends work-stealing of Cilk scheduler with a hierarchy, and borrows fault tolerance mechanism from Cilk-NOW [71]. Satin [72] is also a Java-based runtime system that extended work-stealing with a cluster-aware capability. To the best of our knowledge, these runtime systems have not yet supported for heterogeneous many-core architecture with software-controlled memory.

Another important aspect of programming models is productivity. A group of parallel languages based on Partitioned Global Address Space (PGAS) include UPC [73], Titanium [73], Co-array Fortran [74], X10 [58], and Chapel [75]. PGAS enables writing codes in the global view style in which programmers express their algorithms and data structures as a whole. These languages tend to provide much more fine-grain control support.

X10 [58] is Java-based language with new language constructs for high-productivity high-performance parallel programming. Designed for concurrent and distributed programming, X10 supports notions of non-uniform data access across nodes, partitioning its global address into a set of places. A place contains a collection of data and activities that operate on the data. Mapping between places and physical locations is separate from the X10 program. Regarding data access, each activity reads and writes a shared-memory location synchronously within a place. To read or write remote data (i.e., another place), an activity may spawn new activity at a remote place to perform data access. Specifically, asynchronous activity is created and synchronized by language constructs async and finish. Nested async and finish allow more than one level of a divide-and-conquer phase. It also provides more fine-grain

control on the activity with construct future.

Chapel [75] is a productivity-oriented programming language. Instead of giving programmers access to the threads via low-level fork/join mechanisms and naming, it provides high-level abstractions for parallelism using anonymous threads. It relies upon the programmers instead of the compiler to identify parallelism. To make parallel programming friendly to programmers who are more familiar with sequential languages, Chapel provides a rich set of built-in data structures and broad-market features. To manage data distribution and locality, it provides locality-specific construct locale for tasks that have uniform access to the machine's memory.

PyDac also emphasizes programming productivity by coding in a global view style. In PyDac, each green core has it own address space, but these spaces do not form a global address space. Another approach is to combine productivity-level languages and efficiency-level languages. SEJITS [76] leverages just-in-time technique to dynamically generate efficiency-level code from productive-level code. PyDac does not use just-in-time compilation technique but requires some C libraries running on green cores to be statically compiled. PyCUDA and PyOpenCL [77] are toolkits that improve GPU programming productivity by GPU runtime code generation within Python language. PyDac also intends to leverage Python programming language for programming heterogeneous hardware (e.g., the green-white architecture).

#### CHAPTER 3: GREEN-WHITE ARCHITECTURE

This chapter introduces a novel heterogeneous many-core chip architecture—

"green-white" architecture. PyDac programming framework and green-white architecture are two aspects of a novel hardware-software codesign. The green-white architecture intends to ride technological trends into the era of heterogeneous many-core computing. PyDac focuses on solving consequent technological issues, including performance, resilience, and productivity.

To construct a model of the green-white architecture, we take advantage of two approaches—simulation and hardware emulation. This chapter discusses the advantages and disadvantages of each approach, presents the design of green-white architecture, and shows a hardware prototype of green-white architecture, which serves as an experimental setup for evaluating PyDac.

#### 3.1 Modeling Techniques

Computer architects rely on modeling techniques to gain insights about how well their design may work. Modeling techniques could be divided into three main categories, depending on cost and accuracy: analytical modeling, simulation, and emulation.

Analytical modeling is usually applied in the earliest stages of design and focuses on one or more essential mathematical computer system design formulas. In addition, this technique intentionally ignores most of the design details, making it both faster and more inaccurate than other techniques. However, the inherent inaccuracy does not undermine the importance of this technique. Analytical modeling helps designers to make high-level design decisions and often leads to insights. For example, Hill et al. extend Amdahl's law to many-core processor design [35]. Based on a simple hard-

ware cost model, they explore three different many-core designs (i.e., homogeneous, heterogeneous, and dynamic). Despite its simplicity, they came to an insightful conclusion that the heterogeneous architecture results in better performance than the homogeneous architecture. In fact, Hill et al.'s analytical modeling motivates this research.

Simulation generates more accurate results than analytical modeling by taking many design parameters into the model for consideration. It is also relatively cheaper compared to building hardware prototypes. In addition, some simulators provide software developers with a fully controlled environment. The developers may stop code execution and examine machine states freely. Such a feature is very helpful for debugging code; therefore, computer architects extensively apply simulation. For example, the gem5 simulator [78] allows complete software stacks, including unmodified commercial OS to run on the simulator.

In general, emulation can be divided into two groups: (a) emulation through software and (b) emulation through hardware. While the difference between simulation and emulation through software might seem obscure, the latter approach closely resembles the behavior of real systems (i.e., target designs). For example, QEMU [79] is a machine emulator that dynamically translates target CPU instructions into host instructions. Also, computer architects commonly use emulation through hardware (or hardware emulation). Both industry and academia use many different hardware emulation approaches. Here, we follow a taxonomy presented in Lieven Eeckhout's lecture [80]. A functional emulator is a circuit that is functionally equivalent to a target design, but does not provide any insight on specific design metrics. Its advantages include faster emulation speed than software simulation, because it can execute code at hardware speed. A model is a representation that is functionally equivalent and logically isomorphic with the target design. It allows for some abstraction, which simplifies model development. A prototype is also a functionally equivalent and log-

ically isomorphic representation of the target design. However, it implements the same structure (i.e., the same hardware description language code) as in the target design. Because a prototype can be used to project performance, it is a useful vehicle for studying the scalability of software. In particular, many computer architects implement their prototypes through FPGA devices.

An FPGA device is an integrated circuit in which hardware configuration can be done after manufacturing process. A user may use hardware description language to program an FPGA device and implement desired hardware functions. Because an FPGA device can be re-programmed many times, its non-recurring engineering cost is relatively lower than an application-specific integrated circuit (ASIC) design. In addition, FPGA devices also benefit from Moore's Law. Therefore, the density of FPGA devices is able to grow with newer generations, which allows designers to emulate more sophisticated designs. Moreover, FPGA emulation is often hundreds of times faster than simulation, especially when application software and system software need to run against hardware design.

#### 3.2 Theoretical Model of Green-White Architecture

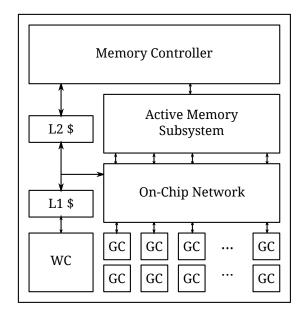

Based on technology advancements and trends, this work is motivated to prepare for a hardware design that is: (a) heterogeneous many-core, (b) combined with scratch-pad memory, (c) likely to experience higher rates of faults, and (d) supported by a flat memory hierarchy. One such chip architecture is called green-white architecture, as illustrated in Figure 3.1.

This architecture assumes a view of main memory that is similar to Fresh Breeze [18]. Specifically, it assumes a flatter memory hierarchy coupled with a set of special compute cores that are denoted as *green core* (GC) in Figure 3.1. An on-chip network connects the active memory subsystem, which actively manages chunks of memory, to the green cores. Each green core consists of a simple processor and multiple, multiplexed banks of scratch-pad memories (locally byte-addressable blocks of memory)

Figure 3.1: High-level block diagram of the green-white architecture.

that are actively managed. This is in stark contrast to the conventional memory subsystem, which consists of multiple layers of reactive caches. If the cores are oversubscribed with tasks, the proposed arrangement allows the memory subsystem to actively manage data transfer to one bank while a task is executing out of another bank, effectively overlapping memory movement and computation [48]. This allows for better utilization of off-chip memory bandwidth, helps hide latency, and reduces energy consumption.

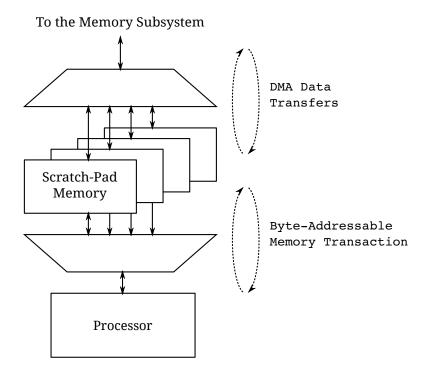

The management of data transfer is illustrated in Figure 3.2. The processor inside a green core accesses one of the banks of scratch-pad memories in byte-addressable transaction. Such transaction is the same as the transaction between the level-one cache and a processor core in conventional designs. The cost of switching between banks is usually negligible, and latency for accessing a bank is very low. Therefore, enough banks of scratch-pad memories keep the processor busy continuously, because the processor is never starved for data. From the processor's perspective, it never has a cache miss and need not go fetch data from a level-2 cache (which is why the memory is flat). The data transfer between the scratch-pad memories

Figure 3.2: High-level block diagram of a green core.

and the memory-subsystem is through direct memory access (DMA). Typically, a few kilobytes of data can be moved within one DMA transfer. From an active memory subsystem's perspective, one DMA transfer may contain one memory chunk or multiple memory chunks.

The active memory subsystem is co-designed with a programming model from the beginning. Briefly, the programming model allows programmers to decompose a problem into sub-problems. The process ends when a sub-problem is small enough that a fast direct solution (called a base case in the divide-and-conquer strategy) is possible. The major criterion for a basic case is that it "fits" into the scratch-pad memory of a green core. High degree of parallelism fundamentally enables latency hiding through multiple scratch-pad memories. In addition, with a large number of parallel tasks that fit into the scratch-pad memory, enough memory transactions will be available for the memory subsystem to efficiently use the memory bandwidth and keep green cores busy. These parallel tasks are independent from each other

and run on the green cores in the green-white architecture. The working data set for each task essentially is one or multiple memory chunks managed by the active memory subsystem. Restricted by the programming model, tasks are allowed to read a memory chunk many times but to write only once. Since multiple tasks may "subscribe" to the same memory chunk simultaneously, the active memory subsystem uses reference counting technique to track the number of subscribers. This number is important, because it allows the active memory subsystem to move a memory chunk up and down in the memory hierarchy and keeps the most needed memory chunk always on-chip. In addition, coherence issue is eliminated through a write-once policy. If one green core subscribes to a memory chunk, then any attempt of writing to the memory chunk by other green cores creates a new memory chunk instead of overwriting on the old one.

The processor core inside the green core is slow, small, and simple, presenting itself to provide increased system throughput (tasks completed per second). Conceptually, these processor cores incorporate low-power techniques (low clock rate, no protection) and feature a simpler design (e.g., reduced pipeline depth, no branch-prediction) to save silicon footprint and reduce power. To achieve the power efficiency (performance per watt), these processor cores are designed to be more application-specific and less reliable.

The chip architecture also includes one or more very fast, complex cores—denoted as white core (WC). The white cores are present to reduce the latency of sequential tasks and might be hardened to protect against faults. Conceptually, these cores incorporate the latest advances in single-thread performance and incorporate techniques (higher power, protection, hardened) to increase reliability. The on-chip network connects the green cores to a memory subsystem, providing direct access to the blocks of write-once memory. The white cores have a conventional memory hierarchy. The two memory subsystems share (off-chip) DRAM memory resources through a multi-ported

memory controller.

In summary, the main assumption is that future devices will be a mix of simple and complex cores. There will be many simple cores (because they are smaller) and they will use less energy. However, these advantages come at the expense of reliability. In contrast, the complex cores (which are very expensive in terms of energy and resources) will be essential for sequential code and as a safe haven for critical operations. The active memory subsystem manages data transfer for multiple, multiplexed banks of scratch-pad memories in green cores so that the processor in the green core never starves.

## 3.3 An Implementation of Green-White Architecture

This section describes how to construct a model of the green-white architecture through a combination of two approaches — simulation and hardware emulation. The green core is first simulated as a subsystem for debugging and software development. Then, a hardware prototype of green-white architecture is implemented on an FPGA device.

### 3.3.1 Hardware Simulation

ARMv2a soft processor (called Amber [81]) is chosen to represent the processor in the green core because its source code is freely available. The ARMv2a processor has a three-stage pipeline, a unified instruction and data cache, and is capable of 0.75 DMIPS per MHz. The green core simulator incorporates one ARMv2a processor core and several peripheral cores, such as a timer, an interrupt controller, and a UART. The ARMv2a processor core's HDL code and peripheral cores can be synthesized into an FPGA device. The green core simulator also incorporates some modules that can not be synthesized into an FPGA device. These modules include scratch-pad memories and a clock generator. The green core simulator uses ModelSim<sup>TM</sup> and VCS<sup>TM</sup>.

The green core simulator also provides a sophisticated interface to software devel-

opers. A software developer with the knowledge about the hardware configuration of the green core simulator may write a wide range of applications and quickly verify applications. These applications may include a test that consists of tens of lines of assembly code or a Linux OS. When the simulation is launched, the green core simulator first invokes an ARM cross-compiler. The ARM cross-compiler compiles the application into an executable. The information that could not be executed, such as comments and debugging information, are then stripped to save memory space for the simulator. After that, a custom tool converts the reduced executable into a memory image, with which the testbench of the green core simulator is initialized. Once the ARMv2a processor core is reset, it fetches the first instruction from the memory and starts execution. With the green core simulator, software development could start very early, which reduces the risk of debugging a very complex software system on a hardware prototype. In fact, the virtual machine for green core is developed and debugged on the green core simulator before it is tested on the hardware prototype.

Even though the green core simulator only simulates a portion of the envisioned green-white architecture, the software developed on this simulator is easily reusable. This is because the proposed programming model decomposes a problem into many stateless tasks. In other words, the output of each task only depends on its inputs. When such task is developed on the green core simulator, the main goal is to verify that the output of the task is correct. Once it passes verification, it becomes a "black box" to the final runtime system running across both green cores and white cores. Later, if a software bug is suspected on the task running on the green core, the programmer only needs to examine the input of this task.

## 3.3.2 Hardware Prototype

In order to evaluate the proposed programming model and the runtime system, a prototype of the green-white architecture was emulated on a Xilinx Virtex 5 FPGA device on an ML-510 developer board, as illustrated in Figure 3.3. An overview of

Figure 3.3: High-level diagram of green-white prototype on an FPGA device.

Table 3.1: Summary of the hardware prototype.

| FPGA Board    | Xilinx ML510                 |

|---------------|------------------------------|

| White Core    | 1 PowerPC440 at 400 MHz      |

| Green Cores   | 6 ARM (v2a) cores at 50 MHz  |

|               | Each with 160 KB scratch-pad |

|               | memory                       |

| Memory System | DMA assisted by software     |

| Interconnect  | Bus                          |

this prototype is presented in Table 3.1. This prototype combines two type of cores (one of which owns multiple, multiplexed scratch-pad memories) and features a flat memory hierarchy.

Each green core is equipped with an ARM processor core and a 160 KB scratch-pad memory. The ARM processor is clocked at 50 MHz. The prototype has six ARM processor cores. The available on-chip resources of the FPGA limits the number of cores. The scratch-pad memories are single-cycle latency on-chip memories. The 160 KB scratch-pad memory is further divided into three banks: one 128 KB bank and two 16 KB banks. The three banks are all dual-ported: one port interfaces to the DMA engine and the other interfaces to the ARM processor core. From the perspective of the runtime system, the 128 KB bank and 16 KB bank are designed for

different purposes, and therefore, they show different memory access patterns. The 128 KB bank holds virtual machine executable and ephemeral contents (e.g., heap and stack) for the ARM processor core. Therefore, the DMA engine only accesses the 128 KB bank for initialization and fault recovery. Unlike the 128 KB bank, the two 16 KB banks that hold the content of parallel tasks are multiplexed on both ports. The DMA engine frequently accesses the 16 KB banks for moving tasks and data around without interfering with execution on the ARM processor core. These 16 KB scratch-pad memories allow overlapping communication with computation.

The white core is a PowerPC 440 core clocked at 400 MHz, with 2.0 DMIP-S/MHz performance [82]. The PowerPC 440 core integrates a superscalar seven-stage pipeline, separate instruction and data caches, and a memory management unit (MMU). The Xilinx Virtex 5 FPGA device on the ML-510 developer board provides two PowerPC 440 hard cores. However, only one PowerPC 440 core is utilized in this work, due to the capability of the OS. A bus and a DMA engine are implemented as the system interconnect, because it was more expedient than a network-on-chip.

The active memory subsystem discussed in the previous chapter is greatly simplified in the prototype. The DMA is a bidirectional streaming engine transferring data between the scratch-pad memories and the main memory. This engine takes the "starting address" and "data length" as input, and streams the data without involving the white core or the green core. A memory chunk anticipated by the active memory subsystem is emulated through data segments specified by the "starting address" and "data length." A software module in the runtime system actually manages data transfer between main memory and scratch-pad memories without a fully active memory subsystem.

### CHAPTER 4: DESIGN OF PYDAC PROGRAMMING FRAMEWORK

A programming framework normally includes application programming interfaces (APIs), necessary libraries, compilers, and a runtime system. It provides an abstraction layer to users who develop application-specific software. Such abstraction visible to programmers is also known as a programming model. The runtime system also plays an important role. A runtime system, which is not visible to users, interfaces to programming model and hardware and provides several responsibilities: (a) it abstracts the underlying hardware, (b) it implements the core behavior of programming model and programming language, and (c) it maps the core behaviors of programming model and language to hardware and manages resources to meet requirements, such as power and performance.

Heterogeneous many-core architectures (e.g., green-white architecture) offer a good balance between single-threaded performance and multithreaded throughput. Such systems impose many challenges on the design of a programming model and a runtime system. Specifically, these include: (a) how to fully utilize the chip's performance, (b) how to manage heterogeneous, unreliable hardware resources, and (c) how to generate and manage a large amount of parallel tasks.

In this chapter, details are first given about a Python-based programming model called PyDac, which supports a two-level programming model based on the divide-and-conquer strategy. This programming model supports green-white architecture. To test the spectrum, PyDac also runs on conventional SMP architecture. We then present the design of a runtime system that is specifically co-designed with green-white architecture. The runtime system seamlessly manages the parallel tasks, system resilience, and all inter-task communication with architecture support.

## 4.1 Programming Model

The primary goal of the programming model is to make it possible to write programs that generate a very large number of parallel tasks without a great deal of programming effort. A functional style of programming [83] is very good at this but is generally viewed as difficult for computational scientists to use. In addition, there is a popular belief that the functional programming style leads to a mediocre performance. Pankratius et al. countered this belief through an empirical study evaluating Scala—a multi-paradigm programming language—and Java [84]. Their controlled study showed that programmers whose programs result in superior performance wrote about half their programs in a functional style and the other half in an imperative style. The result indicates the promise of the combination of the functional and the imperative programming styles. This is because using the imperative style may compensate the functional style for the potential performance loss.

The main idea in this programming model is to implement a two-level programming paradigm. It borrows the concept of the divide-and-conquer strategy from the functional programming style to decompose data and create tasks. The two-level programming paradigm uses the imperative style for individual tasks. The PyDac programming model is implemented with the Python programming language. Python is considered an easy language to learn, it supports both the functional and imperative styles, and it has popular modules to support scientific applications. (However, there is no reason that other high-level programming languages could not be used for this model.) Specifically, a programmer who wants to use this programming model needs to learn two concepts. The first is the divide-and-conquer strategy, and the second is how to express it in Python. In this section, a two-level programming model that suits both the SMP platform and a heterogeneous many-core platform is presented. Cases are studied to illustrate how applications are developed under this model.

# 4.1.1 Divide-and-Conquer Strategy

Divide-and-conquer is a well-known technique for designing algorithms in the computer science community. Three steps are usually involved in this technique: divide, conquer, and combine. In other words, the divide-and-conquer strategy recursively decomposes a problem into smaller sub-problems, which in turn are decomposed into sub-sub-problems, and so on. The process ends when a sub-problem is small enough that a fast direct solution is possible. Many algorithms based on this strategy have a clear performance model described by the Master theorem [85] when base case sizes are equal. For many algorithms based on this strategy, the number of base cases grows exponentially with input size, which helps to uncover a significant large amount of parallel tasks through a finite number of statements in the program.

The divide-and-conquer strategy is also widely applicable. The applications based upon this strategy include fast Fourier transform (FFT) [86], sorting [87], many linear algebra problems [88, 89], data visualization [90], biological sequence alignment [91], pattern recognition [92], neural network [93], image processing [94], graph algorithm [95], search algorithms, and geometry functions. There are other important algorithm design paradigms, such as dynamic programming. We focused on the divide-and-conquer strategy in this work, and other algorithm design paradigms are beyond the scope of this dissertation.