# FAULT-TOLERANT DESIGN FOR CONTINUOUS REAL-TIME MONITORING AND MODULATION OF THE HUMAN BRAIN

by

# Ipsita Acharya

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2015

| Approved by:          |

|-----------------------|

| Dr. Bharat Joshi      |

| Dr. Yogendra Kakad    |

| Dr. Hitten Zaveri     |

| Dr. Jiang (Linda) Xie |

| Dr. Arindam Mukherjee |

| Dr. Pinku Mukherjee   |

©2015 Ipsita Acharya ALL RIGHTS RESERVED

#### **ABSTRACT**

IPSITA ACHARYA. Fault-tolerant design for real-time monitoring and modulation of the human brain. (Under the direction of DR. BHARAT JOSHI)

An era of brain implantable devices has been ushered in recent years. These devices are currently being used to treat neurological disorders such as Parkinson's depression and epilepsy and are increasingly being proposed for a wide range of neurological and neuropsychiatric disorders including chronic-pain and post-traumatic stress disorder. Given the seriousness of these brain disorders the accurate operation of these brain implantable devices is critical to the well-being of a patient. For example, a brain implantable device may be the only thing that may prevent a patient from entering depression or experiencing and acting on suicidal ideations. Hence, these devices are critical and need fault-tolerance.

In recent years, the design of brain implantable devices has also been driven by an increasing need for dense sensor arrays together with a need for a fully implantable signal monitoring and modulating circuitry that consumes low power ( $\approx$  few  $\mu$ Watts), occupies a small area ( $\approx$  few mm²) and has the ability to wirelessly communicate with the external environment while monitoring bio-potential signals *in vivo*. The rapid scaling of CMOS technology in recent years has assisted this need for a low area-power design criteria in becoming a reality. However, it has also added a fresh set of reliability issues to the existing implantable designs which surprisingly do not incorporate fault-tolerance strategies which are *de rigueur* for other critical engineering devices.

This dissertation presents an argument for the inclusion of fault-tolerance in brain implantable devices to extend their dependability, and addresses the issue by proposing

possible fault-tolerant designs for these devices. A systems approach has been adopted to achieve the proposed fault-tolerant designs for the brain implantable system. This system includes an array of electrodes also known as the Multi-electrode Array or MEA to sense the underlying neural activity and, an implantable electronic circuitry to process and transmit the captured neural activity to an external recording and monitoring unit. Such an implantable device can also possess the ability to stimulate neurons or deliver drugs locally based on feedback received from the external unit. A hardware redundancy approach has been employed to provide a possible long-term solution to resolve the reliability issues in such implantable systems that are chronically implanted for long periods of time.

Two redundancy based solutions are proposed to improve the dependability of the brain implantable MEA. The first solution uses rows or columns of spare units to replace primary faulty sensors within the device. The second solution uses space redundancy with local reconfiguration capability. Here spare sensors are placed in interstitial sites and can replace neighboring primary faulty sensors. Different fault-tolerant solutions with varying degrees of redundancy and the equivalent graph models for these solutions are described. A maximum matching algorithm is described to match faulty primary to available spare modules for reconfiguration.

Three fault-tolerant designs are proposed to increase the reliability and availability of the brain implantable device. The fault-tolerant designs are analyzed and compared in terms of the area occupied, the power consumed and the overall system reliability to a benchmark design proposed for future brain implantable designs. The performance of these solutions is analyzed under different fault conditions to characterize the dependability of a fault-tolerant implantable system as a function of the redundancy introduced. The area-

power trade-off versus the degree of reliability included in the fault-tolerant device has been analyzed for a standard 0.18µm CMOS process. Results of the analyses demonstrate that a considerable improvement in the reliability of an implantable system can be achieved with a well-designed increase in redundancy.

# DEDICATION

To my parents, my bou and nana and my ever-supportive and loving husband, Anup.

#### **ACKNOWLEDGMENTS**

I would like to take this opportunity to express my sincere gratitude to my advisor, Dr. Bharat Joshi, for his constant guidance, support and encouragement during the course of this endeavor. This work would not have been possible without his wisdom and able mentorship.

I would like to thank Dr. Hitten Zaveri of Yale University, for generously sharing his knowledge and ideas and for reviewing my work and providing me with useful feedback. He has been a great source of inspiration throughout the course of my research.

I would like to thank Dr. Yogendra Kakad for the support and guidance that he gave me during my initial years in graduate school.

I would like to thank the Department of Electrical and Computer Engineering and the Graduate School at UNC Charlotte for the GASP award, which helped me financially during the course of my Ph.D. studies.

I would like to thank my sisters, Susmita and Subrata for their encouraging words, and my husband, Anup, for his unwavering love and support and for being a pillar of strength during some of the gloomiest days of this journey. I would like to thank my parents, my *bou* and *nana*, for their undying faith in me, I think they often had more faith in my ability to finish this endeavor than I had myself.

# TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                                                                                 | 1          |

|---------------------------------------------------------------------------------------------------------|------------|

| 1.1. Importance of Continuous Real-time Monitoring and Modulation of Neural Activity of the Human Brain | 1          |

| 1.2. Demands and Challenges of Next Generation Brain Implantable Devices                                | 3          |

| 1.3. Dissertation Contribution                                                                          | $\epsilon$ |

| CHAPTER 2: BACKGROUND                                                                                   | 11         |

| 2.1. Fault-tolerance and Dependability                                                                  | 11         |

| 2.2. Existing Neural Signal Monitoring Techniques                                                       | 12         |

| 2.3. Brain Implantable Architectures                                                                    | 16         |

| 2.3.1. Multi-Electrode Arrays                                                                           | 17         |

| 2.3.2. Neural Monitoring and Modulating Circuits                                                        | 17         |

| CHAPTER 3: DESIGN OF FAULT-TOLERANT MULTI ELECTRODE ARRAYS                                              | 20         |

| 3.1. Row or Column Redundancy                                                                           | 21         |

| 3.2. Interstitial Redundancy                                                                            | 24         |

| 3.3. Reconfiguration of Interstitial Redundancy Arrays                                                  | 25         |

| 3.4. Maximum Matching Algorithm                                                                         | 26         |

| 3.5. Reliability Analysis of Interstitial Redundancy Arrays                                             | 29         |

| 3.5.1. Reliability Analysis of a (1, 4) IRA                                                             | 30         |

| 3.5.2. Reliability Analysis of a (1, 6) IRA                                                             | 32         |

| 3.5.3. Reliability Analysis of a (2, 6) IRA                                                             | 34         |

| 3.5.4. Reliability Analysis of a (4, 4) IRA                                                             | 35         |

| 3.5.5. Comparing the System Reliabilities of (1, 4), (1, 6), (2, 6), and (4, 4) IRA MEA Designs         | 38         |

| 3.5.6. Simulating a (4, 4) IRA MEA                                            | 40 |

|-------------------------------------------------------------------------------|----|

| 3.6. Design Summary                                                           | 43 |

| CHAPTER 4: DESIGN OF A FAULT-TOLERANT BRAIN IMPLANTABLE DEVICE                | 45 |

| 4.1. Fault-tolerant Architecture Design 1                                     | 50 |

| 4.2. Fault-tolerant Architecture Design 2                                     | 52 |

| 4.3. Fault-tolerant Architecture Design 3                                     | 53 |

| 4.4. An Architectural Benchmark for Next Generation Brain Implantable Devices | 56 |

| 4.5. Design Analysis of Proposed Fault-tolerant Architectures                 | 58 |

| 4.5.1. System Reliability Analysis                                            | 59 |

| 4.5.2. System Reliability Analysis with Graceful Degradation                  | 66 |

| 4.5.3. Area-Power Analysis                                                    | 67 |

| CHAPTER 5: CONCLUSIONS                                                        | 71 |

| 5.1. Future Work                                                              | 74 |

| 5.2. Final Thoughts                                                           | 76 |

| REFERENCES                                                                    | 78 |

#### **CHAPTER 1: INTRODUCTION**

1.1. Importance of Continuous Real-time Monitoring and Modulation of Neural Activity of the Human Brain

Understanding how the trillions of neural impulses of the brain's billions of neurons produce our thoughts, perceptions, and actions is one of the most intriguing challenges of the 21<sup>st</sup> century science. The ability to translate these neural communications to more interpretable electrical signals has presented new opportunities to treat a variety of neural disorders using neural prosthetic devices. For instance, epilepsy is one of the most common neurological disorders that affects 0.4% to 1% of the world's population [1]. Pharmacology, the first line of treatment for epilepsy, is helpful for controlling seizures in approximately 64% of patients [2]. For the remaining approximately 10-20 million patients worldwide with uncontrolled seizures a second line of treatment, where available, is brain surgery [3], and a third line of treatment which has emerged in recent years is the use of brain implantable devices [4]. Currently brain implantable devices employ electrical stimulation to control seizures [5], [6], [7]. Other implantable devices under development seek to warn of an impending seizure, deliver drugs locally or cool the brain to control seizures. Epilepsy surgery may require multi-day intracranial monitoring of the brain to locate the source of seizures and brain implantable devices to control seizures require permanent monitoring of brain activity to detect or predict a seizure. Parallel to this effort in epilepsy is an independent effort to develop a brain machine interface (BMI) to detect brain activity and typically activate an external actuator such as a robotic arm or make a

decision [8]. In the BMI field the effort is primarily focused on detection and analysis of single unit or multi-unit activity and to a lesser extent on the measurement and analysis of the local field potential.

Though there are differences between the epilepsy and BMI fields, there are also similarities in that both fields endeavor to measure neuronal activity directly from the brain and increasingly for a long period of time up to the life of the patient. There is also mounting evidence that the sensing solution in these efforts will involve increasingly larger numbers of electrode contacts which are often placed in a dense arrangement [9], [10]. For example, a first generation implantable device has 96 contacts in a dense 2D array arrangement. Among the second generation devices which are being proposed are some which will have 1,000 or more contacts arranged in a dense 2D grid. Recent years have witnessed the development of micro-fabricated neural probes such as the Utah and Michigan arrays that have been in use in experimental labs as well as in clinical applications for brain-machine interface for treating patients with paralysis [11].

As it would be true for any portable or implantable device, these neural-activity recording systems require miniature electronics locally in order to amplify the weak neural signals, filter out noise and out-of-band signals and digitize the amplified neural signal for transmission to an external monitoring unit. The recent advancements in modern semiconductor technology has sparked significant research activity in the development of such miniature electronics, particularly in the last decade [12], [13], [14], [15], [16], [17], [18], [19], [20], [21].

More recent efforts have been spurred by Defense Advanced Research Projects Agency (DARPA, an agency of the United States Department of Defense) programs funded by the

presidential Brain Research through Advancing Innovative Neurotechnologies (BRAIN) initiative. This initiative has been recently undertaken to improve our understanding of the human brain, the most complex biological structure in the known universe. The BRAIN initiative funded DARPA programs include Systems-Based Neurotechnology for Emerging Therapies (SUBNETS) and Restoring Active Memory (RAM). DARPA SUBNETS seeks to improve the health of U.S. service members, veterans, and civilians from the effects of neuropsychological illness brought on by war, traumatic injuries, and other experiences while the RAM program is targeted towards military personnel and civilians suffering from Traumatic Brain Injury (TBI). In addition to DARPA, the NIH, NSF, FDA, and IARPA have also announced brain initiative programs towards the goal of improving our understanding of the human brain. These agencies are following a 12 year plan outlined in the BRAIN 2025 report with the first several years being focused on developing the tools and technologies needed to make the next leap in understanding the human brain [22].

## 1.2. Demands and Challenges of Next Generation Brain Implantable Devices

A close look at a typical brain implantable device shows that it consists of two layers – the layer nearest to the neural tissue is a group of sensors or electrodes. The second layer includes a neural signal processing block. The sensing layer consists of an array of electrodes that are either distributed or concentrated to capture the underlying neural activity. And, the neural signal processing block usually includes an analog-front-end unit which consists of three main blocks: (1) the bio-potential amplifier, (2) a band pass filter, and (3) a unity gain buffer. Recent years has witnessed a growing demand for small size, low-power, and ambulatory physiological signal acquisition system [23]. In addition to

these constraints/requirements the details of the electrode material, the electrode-tissue interface and the type of neural signal itself present further challenges to the implanted microelectronics. The observed neural signals contain an electrode offset potential as well as extracellular action potentials (EAPs) and local field potentials (LFPs). The EAPs typically have amplitudes of 25µV- 1mV with a signal band of 100Hz – 3KHz, whereas the LFPs have amplitudes up to 5mV with a signal band of 0.5 – 300 Hz. Additionally, the electrode-electrolyte interface introduces an offset that can be several 100's of mV, with the microelectrodes themselves contributing thermal noise due to their relatively high impedance [24]. All the above factors, in particular the desire to make such systems implantable (i.e. enabling wireless communication with an external unit) dictate the limits on the size and thermal dissipation (to avoid tissue damage) of the implantable system. And, with the next generation neural interfaces targeting 100s to 1000s of channels and requiring continuous real-time monitoring, resource constraints for implantable systems in such applications will be extremely stringent.

Unlike other critical applications, the currently available as well as the proposed solutions for continuous real-time monitoring of the electrical activity of the brain are all intolerant to faults [25]. There are several aspects of an implantable sensing device which can fail. These include the reference electrode, sensors, signal conditioning and digitization circuitry, and computation, power and communication sub-systems. Faults can arise either in the sensing electrodes or in the neuroelectronic circuitry. Faults which affect sensing can arise because of sensor failure due to mechanical stress on the sensor or the connecting wires during surgery to place electrodes or due to stress from changes in the brain and the surrounding milieu thereafter. Sensor failure can also arise due to the brain tissue response

to chronically implanted sensors possibly resulting in encapsulation of a sensor due to gliosis, which can further lead to neuronal death at the sensing site [26]. In case of erroneous behavior of the implanted sensor or the neuroelectronic circuit, the electrical activity recorded will not be observed correctly, thereby impairing the purpose of the implanted device. For epilepsy surgery this may require the approximation of information from neighboring sensors if they exist, and a second surgery to replace failed sensors in extreme instances. In the case of a seizure control device the failure of error free monitoring of the electrical activity of the brain may necessitate surgery to remove the malfunctioning sensor and re-implantation of a new set of electrodes or a new implantable device altogether. While the initial surgery to place sensors carries a risk, surgery to replace sensors and a device can involve further risk with associated morbidity and mortality which remain to be determined but is expected to be equal to or greater than that of the surgery to place the first set of sensors.

While there is a need to monitor the brain in real-time for extended periods of time with very densely spaced sensors, the progress in developing such systems has been limited by semiconductor technology. It is well known that there is a massive complementary metal-oxide semiconductor (CMOS) scaling effort that will continue to shrink device size. However, there is an increasing performance gap between CMOS device technology and its ability to deliver performance that is proportional to the device density. Moreover, power consumption and heat dissipation pose additional challenges. Recognizing that these factors may render Moore's law of scaling less attractive in future, researchers have started to focus on the nanoelectronics research, such as carbon nanotube transistors, molecular electronics, and spintronics. These emerging technologies together with the scaling of the

CMOS devices are expected to revolutionize biomedical systems, including brain implantable devices. But as the electronic devices get smaller and enter nanoscale levels, these nanodevices will have higher manufacturing-defects leading to higher number of errors in the implantable neuroelectronic circuits. This together with the need for continuous real-time monitoring of neural activity of brain for extended periods of time has created an urgent need to address the issue of inability to tolerate faults in such systems. Thus effective fault tolerant strategies have to be incorporated into the architecture to tolerate intermittent and permanent faults so that the systems can be used reliably for extended periods of time. It is imperative to believe that reliable sensing of the human brain for an extended period of time necessitates fault-tolerant design to assure reliability of the implantable design. That is, fault-tolerance should be incorporated into the architecture of the implantable device.

#### 1.3. Dissertation Contribution

This dissertation presents an argument to incorporate fault-tolerance into the architecture of brain implantable devices. Reliability analysis of a system must be preceded by the knowledge of the level of abstraction for the possible faults that are anticipated to occur in the system. The analyses in this piece of work involves a fully implantable integrated chip that includes a neural interface to sense the underlying neural activity, its corresponding microelectronic circuit to process the signals in order to monitor and record them at an external unit, and a feedback mechanism to enable neural stimulation or local drug delivery. The choice of the level of abstraction for faults should be decided such that, it permits a manageable reliability analyses without losing much information. Hence, only functional-level faults are considered in this work.

A hardware-redundancy philosophy is adapted to incorporate fault-tolerance in the implantable device. Redundancy at the system level will possibly lead to a fault reconfiguration which will be time-consuming, expensive and risky (due to the need for re-surgery to replace the faulty system) to achieve. Redundancy at the circuit-level will need a highly complex fault-detection and location mechanism to achieve system reconfiguration from faults. In between the above two extreme layers of abstraction of the system, lies the component-level, in which, the fault-detection and diagnosis is easier to achieve than at the circuit-level and the fault-reconfiguration process will be faster, cheaper and safer than at the system-level. Hence, a component-level redundancy approach is adopted to increase the dependability of brain implantable devices intended to be used chronically for long periods of time.

Every component in the integrated device will have a specialized function to achieve. If the fault-tolerant mechanism detects a functional failure in the component a reconfiguration mechanism will be initiated to replace the faulty component. For example, the neural interface of the implantable system will include additional spare electrodes that can replace the primary electrodes in case of a failure of the primary electrode(s). Multiple configurations have been explored to place the spare electrodes in the primary grid and the reliability of each of the explored configuration has been analyzed. The neural microelectronic circuitry incorporates fault-tolerance by including redundant units of the major components such as the neural-front-end, and the analog-to-digital converter.

Five fault-tolerant solutions have been proposed to increase the dependability of brain implantable devices. They can be broadly categorized into two groups based on the location where the redundant units are incorporated in the implantable system. The first two fault-tolerant solutions are aimed towards increasing the dependability of MEAs. The MEA consists of a grid of spare and primary modules, where each module has a sensor and the corresponding signal conditioning circuitry. The first solution utilizes rows or columns of spare modules to replace faulty primary modules. The second solution uses space redundancy with local configuration capability where spare modules are placed in the interstitial sites of the MEA and can replace their neighboring faulty primary modules [27]. A patent related to this piece of work has been filed and published [28].

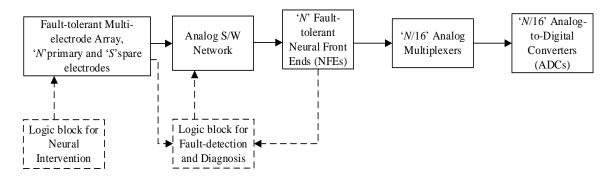

A second category of fault-tolerant solution is proposed in which the sensor array and its accompanying signal conditioning circuits are considered to be separate entities and have different degrees of redundancy. This category offers three fault-tolerant architecture designs. The first architecture includes redundant electrodes in the sensor array. This architecture includes the least amount of redundancy hence it is more attractive as a relatively low cost design focusing on enhancing the dependability of the device by increasing the reliability of the sensor array, that typically includes inactive components such as metal contacts to capture the neural activity.

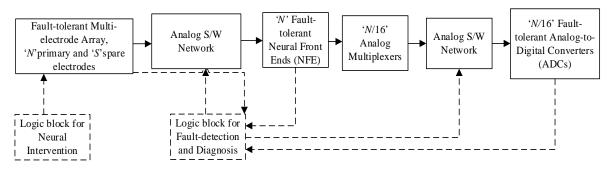

The second fault-tolerant architecture proposed introduces redundancy in the neural-front-end (NFE) unit of the fully implantable neuroelectronic circuitry in addition to the redundancy in the sensor array. The neural-front-end unit is responsible to amplify and filter the neural signals, without which the monitoring of the weak neural data captured by the underlying sensors will not be possible. This fault-tolerant design can have multiple variations depending on the level of redundancy involved in the design. The possible variations of this fault-tolerant architecture are further discussed in detail in Chapter 4.

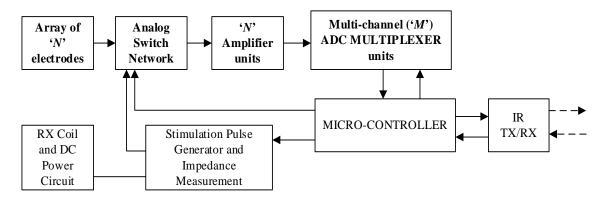

A third fault-tolerant architecture proposed involves the idea of hardware redundancy in the sensor array, the neural-front-end and analog-to-digital-converter units of the neural microelectronics layer. In comparison with the two above-mentioned fault-tolerant designs this design is believed to have the highest degree of reliability. However it might not be cost effective due to the fact that incorporating redundancy in all the major neuroelectronic components might be expensive. Chapter 4 includes an analysis of the reliabilities of each of the proposed fault-tolerant architectures. Therein, the performance parameters, such as area, power and reliability of the proposed fault-tolerant architectures fabricated on a 0.18µm CMOS technology are calculated and compared to a benchmark design that is proposed for future brain implantable architectures, in order to justify the feasibility of the proposed fault-tolerant architectures and to highlight the possible advantages of the proposed designs.

The fault-tolerant strategy will include a built-in system testing methodology that can test the major components of the device in real-time to detect faults in the system. Once a fault is detected the fault reconfiguration algorithm is initiated that isolates the faulty unit and replaces it with a spare if available for the failed unit. This dissertation considers fault-tolerant approaches for intermittent and permanent faults only. A permanent fault is one which exists indefinitely in absence of a corrective action while an intermittent fault is one which appears and disappears repeatedly. A transient fault exists for a limited duration. Transient faults typically do not require system reconfiguration and thus are not considered.

The remaining of the dissertation is organized as follows: Chapter 2 introduces fault-tolerance and describes the existing neural signal monitoring and modulating techniques for brain implantable devices. Chapter 3 describes and analyzes two proposed

fault-tolerant solutions designed to improve the reliability of a fully implantable multielectrode array. Chapter 4 describes and analyzes three other fault-tolerant designs aimed to improve the dependability of implantable neural devices with different levels of redundancy in the sensing and the neural signal monitoring and modulating circuitry of a brain implantable device. The design of the benchmark architecture that is used in our work for comparison and analyses of the proposed fault-tolerant architectures, is also discussed in Chapter 4. And finally, Chapter 5 concludes the presented work with possible future work and some final thoughts on this work.

#### **CHAPTER 2: BACKGROUND**

## 2.1. Fault-tolerance and Dependability

Fault tolerant operation can be defined as the process by which a system continues to perform its specified tasks correctly in the presence of faults. These faults could occur either in the hardware or the software, and can be caused by faults due to manufacturing defects, wear and tear and environmental effects. They could also be caused by external environments or simply due to ageing of the components. The goal of fault tolerant design is to improve system dependability which is defined as the ability of a system to deliver a service at an acceptable level of confidence. Dependability is most commonly characterized in terms of the attributes of reliability and availability [29]. A fault-tolerant solution requires the use of redundancy in some form or the other. The amount of redundancy can be quantified by the redundancy ratio of a fault-tolerant design, which is defined as the ratio of the number of spares to the number of primaries in the fault-tolerant unit. We define the reliability of a system as the conditional probability that the system performs its tasks correctly during a time interval  $(t_0, t)$ , given that the system was performing them correctly at time  $t_0$ . And, the availability of a system is defined as the probability that the system is available to perform its tasks correctly at time t. It is evident that any type of fault tolerance technique requires the use of some form of redundancy, incorporating which will increase both the cost and the development time of the system. Furthermore, redundancy can also have impact on the system's performance, power

consumption, size and weight. Thus a good fault tolerant design requires a trade-off between the level of dependency provided and the amount of redundancy used. The amount of redundancy incorporated can be effectively quantified by the redundancy ratio of the fault-tolerant system.

## 2.2. Existing Neural Signal Monitoring and Modulating Techniques

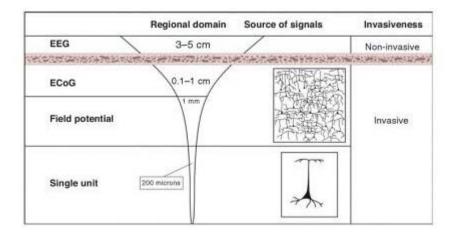

Acquiring brain signals from within the brain requires the presence of a neural interface in a brain computer interface (BCI) system, which is a piece of hardware that detects brain signals so that the sensed neural signals can be sent to the neural signal conditioning components of the BCI for analysis and translation into useful commands. BCI neural interfaces can be broadly classified into three categories: (i) Electroencephalographic (EEG) scalp electrode arrays, that attach non-invasively to the skin to record field potentials with relatively low information content from very large and widely distributed sets of neurons and synapses; (ii) Electrocorticographic (ECoG) electrode arrays that are surgically positioned on the surface of the brain i.e. on the cerebral cortex, to record field potentials with moderate information content from smaller more localized sets of neurons and synapses; and (iii) miniaturized microelectrode arrays that are surgically inserted into the cerebral cortex to record neuronal action potentials (APs or spikes) from individual neurons and/or local field potentials (LFPs) from small highly localized sets of neurons and synapses and that yield high information content. Figure 1 shows the recording domains of different types of neural interfaces.

Figure 1: Neural recording domains for single unit, LFP, ECoG and EEG recordings [30].

EEG signals present a relatively poor signal characteristics, i.e. few centimeters in spatial resolution and a bandwidth of 0-70 Hz, with respect to ECoG, LFPs and APs. This poor signal characteristics is due to volume conduction through the tissue between the brain and the electrode, which makes the signals spread and blur as it passes through the dura, fluids, skull and skin. Hence, in order to achieve sensing resolution required to seamlessly operate a BCI system and the ability to provide a possible feedback (ex. local drug delivery or to provide neural stimulation), invasive neural recording techniques are required.

Electrocorticography (ECoG), which is also known as intracranial EEG or iEEG represents a midway between scalp recorded EEG signals at one end and intracortically recorded single unit action potentials (APs) and local field potentials (LFPs) at the other. ECoG signals can be recorded either from the surface of the dura mater (i.e. epidurally) in which the electrodes are placed on the dura or from beneath the dura (i.e. subdurally) in which the electrodes are placed directly on the surface of the brain [10].

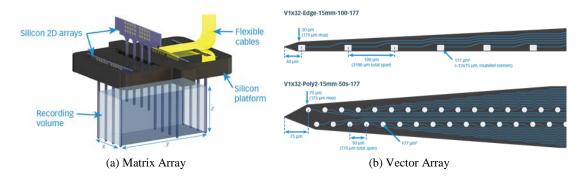

There are two types of implantable microelectrode arrays for BCIs: microwire electrodes and silicon micro machined electrodes. Microwire electrodes (*Tucker Davis*

technologies) consist of an array of thin wires soldered to a connector in two or more rows with a wire diameter of 25-50 µm, having only one recording location at the tip of each wire and are capable of recording from deep cortex (up to 5 mm) [31]. The silicon based micro machined probes involve microfabrication of silicon and polymer structures for miniaturized sensors, actuators and integrated microsystems. Two of the most well-known silicon probes are the Utah Electrode Array and the Michigan-Style Probe. Like the Microwire Array, the Utah Electrode Array has only one recording tip at every electrode site [32]. The Michigan-Style Probe has multiple electrode sites located on the sides of each of the penetrating shanks [33], [34]. Although the microelectrode arrays are capable of providing high spatial and temporal resolution of neural activity, the recording signalto-noise-ratio (SNR) gradually degrades over time and uniformly fails over time with a life-time ranging from several-weeks to several-months, due to the brain-tissue response to the implanted microelectrode arrays [35]. These devices can potentially cause hemorrhage and inflammatory tissue responses from immediate insertion and if implanted for long periods of time, due to the rigidness of the penetrating electrodes which are incapable of conforming to the movements of the brain. In order to obtain stable, long-term recordings from a large population of neurons from across the brain some BCI researchers have indicated the advantages of flexible electrode arrays of subdural electrodes that can maintain signal quality over extended periods of time [36], [37].

In order to acquire the signals picked up by the implanted microelectrode array of electrodes, the weak neural signals first needs to be amplified. To do so, researchers at University of Utah produced a skull-mounted interface electronics for neural signal acquisition, called the Integrated Neural Interface (INI1 and INI2). In which, the Utah

Electrode Array was connected to the skull-mounted interface electronics called the *head-stage*, via a thin wire cable through a tiny hole in the skull [12], [32]. However, the INI1 and INI2 chips were not stand alone devices and required a number of external components for operation, that involved tethering of the subject to external neural signal decoding electronics and had to be powered from a battery source. An improved version of the INI chip, the INI3 was developed to overcome the shortcomings of the previous versions of the chip such as dependency on external devices that limit the mobility of the subject under study, the need for a low-power IC to reduce surrounding tissue damage and the necessity for a wireless link for communications [38]. To acquire neural signals from the Michigan-style electrode array, the penetrating shanks are integrated with a thin-film ribbon cable, which is then integrated with a silicon substrate containing the bond-pads. This is then bonded to a connector which interfaces to an instrumentation system [39], [40]. The invivo performance of the Michigan-style probe is described well in [41], [42] and [43].

The benefits that a fully-implantable wireless BCI system presents includes elimination of the risk of infection due to any percutaneous connections, reduction in the mechanical vulnerability of a skull-mounted unit to accidental impacts (example: an epileptic patient), and a host of clinical and health care benefits such as possibilities of 'scaling-up' the available recording sites to access larger brain locations, non-tethering of the patient to external devices, and design flexibility to enable bidirectional communication with the brain. To avail the benefits of fully implantable wireless BCI systems researchers at Brown University have demonstrated an implantable concept known as '*Braingate*', a fully-implantable neural signal acquisition device that can support a maximum of 100

recording channels [44], [45], [46], [47], [48]. A similar motivation is evident in the work of [49], [50], [51].

There is mounting evidence that the future of neural sensing solutions will involve increasingly larger numbers of electrode contacts which are often placed in a dense arrangement [9], [10]. For example, a first generation implantable device has 96 contacts in a dense 2D array arrangement. Among the second generation devices which are being proposed are some which will have 1,000 or more contacts arranged in a dense 2D grid. The demand for monitoring higher number of recording channels than before will evidently increase the area consumed by the implantable device and the power-dissipated by it into the surrounding tissue. Fortunately, due to the advancements in semiconductor technology it is possible that the implantable IC can be implemented at smaller feature size, thereby achieving the size constraints applicable in such devices. However, an increase in temperature of the surrounding tissue cannot be allowed, because even a mere 1.0 °C can result in neuronal death. Hence, to achieve a dense recording with fully implantable wireless signal acquisition systems have been proposed in [12], [44], [52], [53], [54], [55], [56], [57], [58], [59]. To ensure that such stems can operate continuously for long periods of time, the individual components of the implantable integrated circuit (IC) that processes the neural signals must consume very low-power and occupy a small area. Several efforts have been proposed to achieve the area-power limitations in [12], [18], [60], [61], [62].

## 2.3. Brain Implantable Architecture

Typically the architecture of a brain implantable device used for recording neuronal activity of the brain consists of a group of sensors connected to an amplifier to amplify the weak neural signals captured by the sensors, an analog multiplexer to route the signals from

multiple sensing sites to the next processing unit, and an analog-to-digital converter to convert the neural signals from analog domain to the digital domain so that it can be easily transmitted to an external monitoring unit where further analysis can be done on the neural signals. The same architecture may include other electronic circuits required for neural modulation and computation.

The architecture of the implantable device, considered here, consists of a MEA with multiple electrode contacts (sensors) and circuitry to condition and digitize the sensed signals. Each sensor in the sensor grid is connected to signal conditioning and processing circuitry that includes an amplifier, one or more filters, an A/D converter and a D/A converter, if one is needed. For simplicity, a modular design is considered, where a sensor and its accompanying signal conditioning and processing circuitry are considered to be a module. This circuitry may be connected to additional modules for computation, communication and intervention.

## 2.3.1. Multi-electrode Array

A multi-electrode array or as it will further be referred as MEA in this document is an array of electrodes that is a vital block for any brain implantable device that is designed to monitor the underlying neural signals and in some cases for stimulating areas of brain to facilitate a treatment procedure and/or to enable a local cooling mechanism via drug delivery.

#### 2.3.2. Neural Activity Monitoring and Modulating Circuit

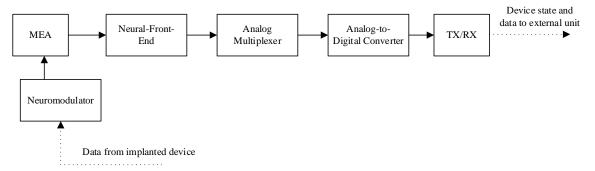

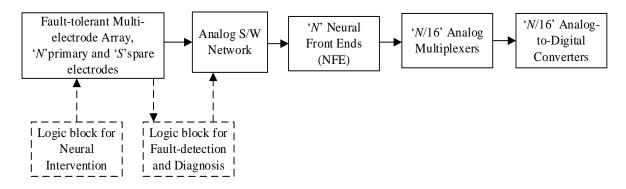

Figure 2, represents the block diagram of neural microelectronic circuitry that is expected to monitor and modulate neural activity. Monitoring the neural signals occurs in

the direction of the flow of the directed arrows. Modulation or stimulation signals are directed to the electrodes in the MEA from a neuromodulator block.

Figure 2: Block diagram of a basic neuroelectronic circuit for monitoring and modulating neural activity

The neuroelectronic circuit is responsible for processing the weak neural signals captured by the array of electrodes in the MEA. In addition to the low strength of the sensed physiological signals, the recording electrodes may pick up many other unneeded interferences or artifact signals. Hence, a low-noise-amplifier (LNA) is necessary at the first stage of the neural signal processing block in order to amplify the weak neural signal level from sub-mV to 10's of mV, so that the later stages can have relaxed noise performance. Although the LNA can provide first order low pass filtering, dedicated bandpass filters are used to (1) reject the out-of-band LFPs (high pass), and (2) prevent aliasing (low pass). The high pass cut-off frequency is typically set between 100-300 Hz and low pass cut-off frequency is between 3- 10 kHz. A dedicated unity-gain-buffer may be used before the next stage of neural signal processing which is the analog multiplexer. The low-noise-amplifier (LNA), the band-pass filter (BPF) and the unity-gain-buffer (UGB) create the neural-front-end also referred to as the NFE.

The next stage is the analog multiplexer which communicates the neural signals from the NFE to the analog-to-digital-converter (ADC) to obtain a digital version of the

captured physiological signal. The main design parameter for ADC is the resolution and sampling rate which is typically 8-10 bits and 16-32kS/s respectively [24]. Next, this digital data is processed by a microprocessor, typically located on the exterior of the patient's body and is then transmitted to an external monitoring and recording device.

# CHAPTER 3: DESIGN OF FAULT-TOLERANT MULTI ELECTRODE ARRAYS (MEAs)

This chapter presents fault-tolerant solutions for multi electrode arrays (MEAs) based on hardware redundancy, wherein the goal is to detect and locate a faulty primary module and reconfigure the MEA after isolating and replacing the faulty primary module with a working spare module. For simplicity, a modular design is considered, where a an MEA grid comprises of sensing electrodes and its accompanying signal conditioning and processing circuitry, and is considered to be a single module on the grid. This circuitry may be connected to additional modules for computation, communication and intervention.

This type of reconfiguration strategy is appropriate since recent observations indicate surprising amount of redundancy within the spatial representation of information on the cortex and in sub-cortical structures. Based on these we consider the spatial structure to take the form of a neuronal ensemble or network structure [2], as opposed to discrete representation. Thus, the quality of information extracted from the measurements after reconfiguration will not be compromised. The term *fault detection* in this article is defined as the process by which it is recognized that a fault has occurred in the system under analysis. *Fault location* is defined as the process of determining where the fault has occurred within the system and *reconfiguration* is defined as the process of isolating a faulty component from the remainder of the system and restoring the system performance to an acceptable level of operation. The two fault-tolerant techniques discussed in this work follow a hardware redundancy approach for fault-tolerance by incorporating redundant

modules within the implantable device. In the first approach spare rows and/or spare columns are placed around the electrode grid array while in the second approach spare modules are integrated within the grid based on a defined geometry. The fault-tolerant methods are designed with cold spare modules, where a spare module is switched on only if it is brought on-line during reconfiguration. Cold spare reconfiguration helps conserve power, facilitate thermal management, and increase the efficiency of the implantable device.

#### 3.1. Row or Column Redundancy

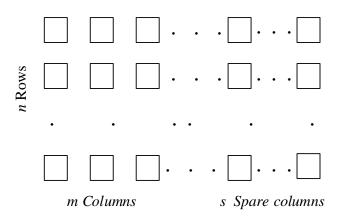

We assume the implanted MEA consists of n rows and m columns of primary modules as shown in Figure 3. In the first solution, we will incorporate s columns of spare modules in addition to the primary modules.

Figure 3: An n-by-m array of modules with s spare columns placed to the right of the array of primary modules.

The motivation for this solution is derived from [63], [64], [65], [66]. The spare columns or rows can be located at the edge of the MEA or within the MEA. Here, for simplicity of exposition, it is assumed that spare columns are located at the right edge and spare rows, if incorporated in the design, are located at the bottom edge of the MEA. Once a faulty primary module is identified a reconfiguration process is initiated in which the faulty module is replaced by its nearest fault-free spare neighbor on the right. Under this

reconfiguration scheme, sensor (i, j) can be connected to one of the following modules: (i, j), (i, j+1), ... (i, j+s), where s is the number of spare columns. To evaluate the reliability of the system it is assumed that the system is operating in the useful life phase of the bathtub curve [29]. In this piece of work, the failure rate, that is failures per unit time, is considered to have a constant value,  $\lambda$ . Under this assumption it can be shown that the reliability of each module is given by the following equation:

$$R_{m}(t) = e^{-\lambda t}$$

Equation (1)

This exponential relationship between module reliability and time is known as the exponential failure law. It states that when the failure rate function is a constant, reliability is proportional to a decaying exponential as a function of time. If the MEA can tolerate r failed modules, for the (m + s) modules in each row, where (r < m + s), then the reliability of each row of modules is

$$R_{row}(t) = \sum_{i=0}^{r} {m+s \choose i} R^{m+s-i}(t) (1-R(t))^{i}$$

Equation (2)

where,

$${m+s \choose i} = \frac{(m+s)!}{(m+s-i)!i!}$$

In this research it is assumed that module failures occur independently. If k rows have to be operational, where  $k \le n$ , then the reliability of the MEA is

$$R(t) = \sum_{j=0}^{n-k} {n \choose j} R_{row}^{n-j}(t) (1 - R_{row}(t))^{j} C$$

Equation (3)

Where 'C' represents the fault coverage.

Fault coverage, C, is a measure of system's ability to recover from faults and continue to operate correctly. It is expressed as the probability that the system recovers

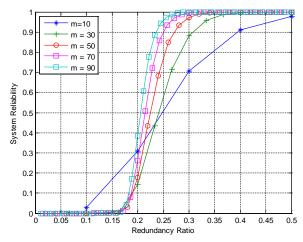

from the fault given the existence of the fault. As an example, we simulated the performance of the proposed solution for a MEA with the number of rows fixed at 100 and fault coverage C = 1. In this evaluation, module reliability (i.e., the probability that primary module is working in the time interval ( $t_0$ , t), was assumed to be 0.9, and k = n, i.e. all the rows had to be operational. Figure 4 shows the reliability of MEAs with the number of columns ranging from 10 to 90 and redundancy ratio ranging between 0 and 0.5. As indicated above a higher redundancy ratio implies that a higher percentage of modules in the MEA are spares.

Figure 4: Reliability as a function of redundancy ratio for a fault-tolerant solution which incorporates spare columns in the MEA. Here the number of rows, n = 100, fault coverage C = 1, k = n, and module reliability is assumed to be 0.9.

For example, a redundancy ratio of 1 implies there is a spare module for each primary module. We observe that the reliability increases for a given redundancy ratio with increasing non-spare columns. This suggests that with this solution it is possible to create a highly reliable MEA using a lower percentage of spare modules. Spare columns are used in this solution for the above example. However, the method can be modified to incorporate both spare columns and spare rows. While the reconfiguration is systematic, i.e. a faulty module is replaced by the nearest fault-free module to its right (or below if spare rows are

used), the reconfiguration will likely involve replacement of several fault-free primary modules in addition to the faulty primary module. This increases the hardware overhead. In order to address this inefficiency, a second redundancy solution, known as interstitial redundancy, is discussed in the next section. This second design reconfigures a faulty MEA without reconfiguration of fault-free modules.

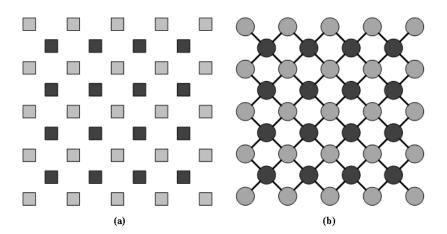

#### 3.2. Interstitial Redundancy

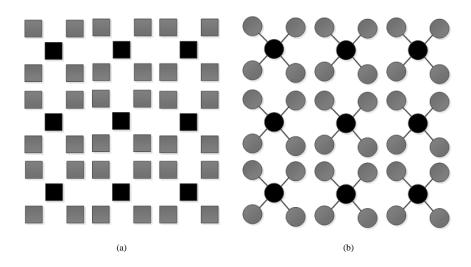

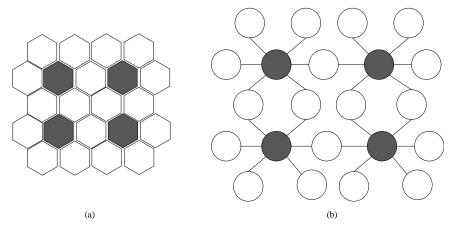

Figure 5(a) shows a (m, n) array of primary modules (gray) where m is the number of rows and n is the number of columns. Embedded within this array of primary modules is an array of spare modules (black). The spare modules are placed in interstitial sites between primary modules. Such a fault-tolerant MEA architecture is referred as a (s, p) interstitial redundancy array (IRA). In a (s, p) IRA, each non-boundary primary module can be replaced by one of s spare modules and each non-boundary spare module can serve as a spare for p primary modules. IRAs can have a different degree of redundancy depending on the number and location of spare modules.

Figure 5: (a) An example of (4, 4) IRA with spare modules (black) at the interstitial sites of the primary modules (gray), (b) The corresponding graph model for the (4, 4) IRA shown in (a) where each node in the graph represents a primary or spare module. Note, in the graph representation each primary module is connected to the spare modules which can replace it, and each spare module is connected to the primary modules it can replace.

For example, consider the (4, 4) IRA shown in Figure 5(a) where each non-boundary primary module can be replaced by any one of the four available spare modules adjacent to it, and each spare module is available to its four neighboring primary modules. Furthermore, each of the four corner primary modules can be replaced by one spare module and the remaining boundary modules can be replaced by one of two spare modules. This relationship can be effectively captured by a graph model for this IRA. Figure 5(b) shows the graph model of the (4, 4) IRA shown in Figure 5(a). As before, gray nodes in the graph represent primary modules while black nodes represent spare modules. If a spare node can replace a primary node, then there is an edge between the two nodes in the graph. It can be observed that no two gray nodes are neighbors in the graph since a primary module cannot replace another primary module. Further, an undirected graph G(V, E) is defined as a structure which consists of a set of vertices  $V = \{v_1, v_2, \cdots\}$  and a set of edges  $E = \{e_1, e_2, \cdots\}$  each edge e is incident to the elements of an unordered pair of vertices (u, v) which are not necessarily distinct.

## 3.3. Reconfiguration of Interstitial Redundancy Arrays

In the interstitial redundancy scheme of fault-tolerance design, we place spare modules in interstitial spaces of the MEA. This allows the use of a local approach for reconfiguration in the presence of faults. Here, when a faulty primary module is identified a reconfiguration procedure is initiated and the detected faulty primary module is replaced by an available neighboring fault-free spare module. The reconfiguration procedure that is employed to make the implantable system tolerant to faults is based on a graph matching approach. A *maximum matching algorithm* is used in this reconfiguration solution and is described in the next section.

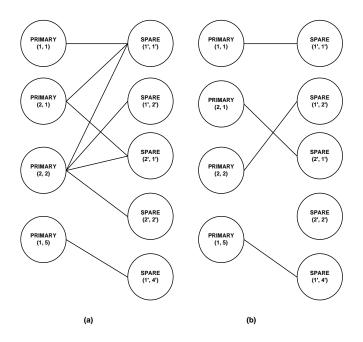

## 3.4. Maximum Matching Algorithm

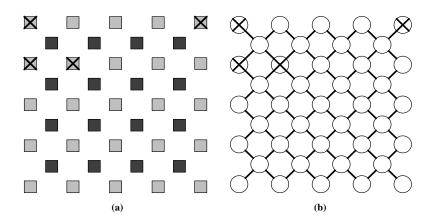

The replacement of a faulty primary module by a spare module can be performed in an optimum manner by using a maximum matching algorithm from graph theory [67]. The reconfiguration procedure can be further illustrated through an example. Consider, for example the (4, 4) IRA and its graph model shown in Figures 6(a) and 6(b), respectively. This is a 5 x 5 MEA with 16 spare modules arranged in a 4 x 4 array. Four of the primary modules are faulty and none of the spare modules are faulty.

Figure 6: (a) A (4, 4) IRA with an example set of faults. Here, primary modules (1, 1), (2, 1), (2, 2), and (1, 5) are faulty. Faulty modules are marked with an 'X'. (b) The corresponding graph model for the (4, 4) IRA shown in (a).

Definition 1: Given an undirected graph G = (V, E), a matching is defined as a subset of edges  $M \subseteq E$  such that for all vertices  $v \in V$ , at most one edge of M is incident on v. A vertex v is matched by matching M if some edge in M is incident on v; otherwise v is unmatched. And, an edge e is a free edge if and only if  $e \notin M$ .

Definition 2: A maximum matching is a matching of maximum cardinality, that is, a matching M such that for any matching M',  $|M| \ge |M'|$ .

From the graph model of an IRA (Figure 6(b)) a subgraph can be constructed consisting of nodes corresponding to faulty primary modules and spare modules that can potentially replace these faulty nodes as shown in figure 7(a). In this subgraph an edge

between a primary node and a fault-free spare node exists if and only if the spare node can replace the primary node. It can be observed that this graph is a bipartite graph since no two primary nodes and no two spare nodes are adjacent.

Figure 7: (a) A subgraph for the (4, 4) IRA with four faulty primary modules shown in Figure 6(a) and 6(b) and the spare modules which can replace the faulty modules. This sub-graph is a bipartite graph. (b) A maximum matching solution of the bipartite graph.

Definition 3: A bipartite graph is a graph in which  $V = X \cup Y$  and  $X \cap Y = \emptyset$  and each edge has one end vertex in X and one in Y.

For a given set of faulty primary modules, we can construct the bipartite graph of the IRA with the vertex set partition  $\{X,Y\}$ , and the edge set E, where X is the set of faulty primary nodes and Y is the set of all the neighboring fault-free spare nodes. Note, that in such a bipartite graph, any pair of matched vertices incident on an edge e,  $e \in M$  will consist of one faulty primary module and one spare module such that the spare module corresponding to the matched node can replace the corresponding faulty primary module. It is evident from definitions 1 and 2 that the maximum matching involves finding  $\delta$ , the maximum number of mutually disjoint edges in E, such that, no two edges share the same

node, implying that a spare module can replace no more than one primary module at any given time and a given faulty primary module cannot be replaced by more than one spare module. For this work, the interest is in determining if  $\delta = |X|$  that is, whether every faulty primary module can be replaced by a fault-free spare module.

A maximum matching for a bipartite graph can be obtained using any method that is based on the following theorem.

Theorem 1: The number of edges in a maximum matching of a bipartite graph G is equal to the maximum flow, F, in its corresponding network, N(G) [67].

The key idea here is to construct a network N(G) whose directed graph  $\bar{G}(\bar{V}, \bar{E})$  is defined as follows:

$$\overline{V} = \{s, t\} \bigcup V$$

, Equation (4)

And,

$$\overline{E} = \{s \to u \mid x \in X\} \bigcup \{y \to t \mid y \in Y\} \bigcup \{x \to y \mid x - y \text{ in } G\}.$$

Equation (5)

There is an edge from node s to every node x,  $x \in X$ . Similarly, an edge exists from every node y,  $y \in Y$  to node t. As an example, consider the (4, 4) IRA with four faulty primary modules (see figure 6(a)). The corresponding graph model is shown in figure 6(b). Bipartite graphs for the sub-graph containing the faulty primary nodes and connected spare nodes are shown in Figure 7(a) and Figure 7(b). The directed graph of the network N(G) is shown in Figure 8.

Figure 8: Directed graph of the network of the bipartite graph shown in Figure 7(a).

Any algorithm for maximum flow can be applied to the directed bipartite graph in Figure 8 to determine the maximum flow from S to T [68]. From Theorem 1 the maximum flow will give the maximum matching. For example, Dinic's algorithm for maximum flow, which runs in  $O(\sqrt{V}E)$  when applied to the directed graph of Figure 8 leads to a maximum matching graph, such as the one shown in Figure 7(b).

A fault-identifying procedure is used to continuously examine module performance to detect a fault. Once a fault is detected a second algorithm may be used, if necessary, to locate the faulty module. These algorithms can run on a controller that is embedded in the fault tolerant MEA or implantable device or on an external computer which can communicate with the MEA. The location of a fault triggers the reconfiguration process wherein the faulty module is disconnected and replaced with a healthy and available spare module.

### 3.5. Reliability Analysis of Interstitial Redundancy Arrays (IRAs)

This section introduces four IRA designs with redundancy ratios ranging from 0.25 to 1.0. The reliability of the IRAs are then evaluated analytically to prove that an incorporating hardware redundancy will improve the dependability of the system. Each of

the IRA designs are compared with the other designs in terms of the reliabilities to conclude with the highest reliable design. Further in this chapter the reliability analysis is simulated for the 'best' possible IRA design.

## 3.5.1. Reliability Analysis of a (1, 4) IRA

In a (1, 4) IRA (Figure 9(a)) each primary module can be replaced by a spare module, while each spare module can replace one of four primary modules. The redundancy ratio for a (1, 4) IRA is 0.25.

Figure 9: (a) An example of (1, 4) IRA with spare module (black) at the interstitial sites of the primary modules (gray), and (b) the corresponding graph model.

In this analysis, unless indicated otherwise, it is assumed that the primary and the spare modules have equal failure rates since both have the same structure and function. As indicated above, the failure rate for each module is considered to be a constant value,  $\lambda$ , with the reliability,  $R_m$ , specified by equation (1).

Let the grid of primary modules be of size  $m \times n$  where m and n are even numbers. There are, then, mn clusters each with four primary modules and one spare module. The reliability of each cluster is given by:

$$R_{cluster(1,4)}(t) = \sum_{i=0}^{1} {5 \choose i} R_m^{5-i}(t) C (1 - R_m(t))^{i}$$

Equation (6).

Thus the reliability of a (1, 4) IRA of size  $m \times n$  is given by

$$R_{(1,4)}(t) = \left(\sum_{i=0}^{1} {5 \choose i} R_m^{5-i}(t) C (1 - R_m(t))^i \right)^{\frac{mn}{4}}$$

$$= \left(R_m^5(t) + 5R_m^4(t) (1 - R(t))\right)^{\frac{mn}{4}}$$

Equation (7).

Where the fault coverage, *C*, is assumed to be 1.

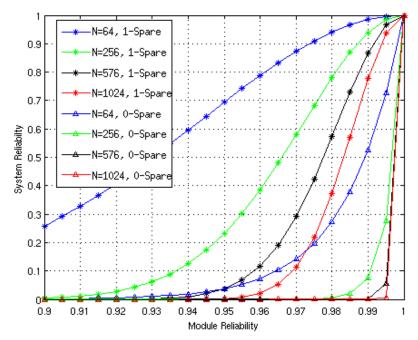

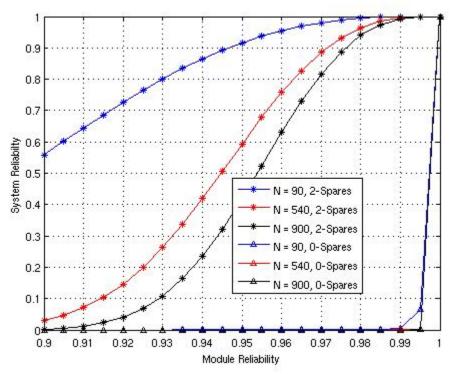

Figure 10 shows the reliability of a (1, 4) IRA for different values of  $R_m$  and N, where N = mn. Compare the reliability of an N module redundant MEA with its corresponding N module MEA without redundancy.

Figure 10: The reliability of (1, 4) IRA MEA with redundancy ratio of 0.25, C = 1, and N = mn = 64, 256, 576 and 1024. The (1, 4) IRA MEAs are compared to the corresponding MEAs without redundancy. It is evident that there is an increase in MEA reliability MEA reliability with the IRA solution.

It can be observed that interstitial redundancy improves MEA reliability. From the plots it may appear that the MEA becomes less reliable when the number of electrodes increases. This is true only when it is assumed that the MEA is considered to be operational when each cluster is operational, i.e., not more than one electrode can fail. However, it should be noted that the total number of faults tolerated are higher for larger MEAs. Moreover, if graceful degradation is acceptable, then larger systems tend to have better performance.

### 3.5.2. Reliability Analysis of a (1, 6) IRA

In a (1, 6) IRA (figure 11(a)) each primary module can be replaced by a spare module, while each spare module can replace one of six primary modules. The redundancy ratio for a (1, 6) IRA is 0.1667.

Figure 11: (a) (1, 6) IRA grid design, (b) the corresponding graph model. The gray nodes represent primary modules and the black nodes denote spare modules.

Like the (1, 4) IRA a (1, 6) IRA can be viewed as a combination of N/6 identical clusters where N is the number of primary modules in the system and it is an integral multiple of 6. Each cluster consists of 6 primary modules and one spare module. Reliability of each cluster is the likelihood of having at most one failed module among the seven modules in the cluster.

$$R_{cluster(1,6)}(t) = \sum_{i=0}^{1} {7 \choose i} R_m^{7-i}(t) C(1 - R_m(t))^{i}$$

Equation (8).

The reliability of the (1, 6) IRA scheme with N primary modules is given by:

$$R_{(1,6)}(t) = \left(\sum_{i=0}^{1} {7 \choose i} R_m^{7-i}(t) c (1 - R_m(t))^i \right)^{\frac{N}{6}}$$

$$= \left(R_m^7(t) + 7R_m^6(t)(1 - R_m(t))\right)^{\frac{N}{6}}$$

Equation (9).

Figure 12 shows the reliability of (1, 6) IRA for different values of  $R_m(t)$  and N, and compares with the reliability of the corresponding systems without redundancies. Once again, it can be concluded that adding interstitial redundancy has the potential to improve system reliability.

Figure 12: The reliability of (1, 6) IRA MEA with redundancy ratio of 0.1667, C = 1, and N = mn = 90, 540 and 900 compared to the corresponding MEAs without redundancy.

## 3.5.3. Reliability Analysis of a (2, 6) IRA

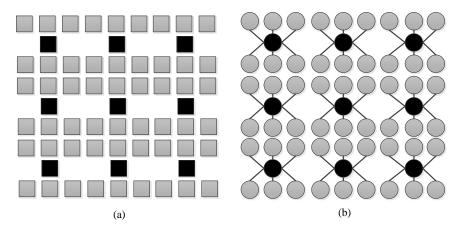

Figure 13(a) represents the grid layout of a (2, 6) IRA configuration and figure 13(b) represents the corresponding graph model for the configuration. For fault-tolerant designs with higher redundancy ratio, such as the (4, 4) and (2, 6) IRAs, analytical modeling to determine the reliability of a system is not straightforward due to the complex assignment of spare modules. However, the cluster based technique used above for the (1, 4) and (1, 6) IRA designs can still be used to derive approximate expressions for MEA reliability.

Figure 13: (a) (2, 6) IRA grid design, (b) the corresponding graph model. The gray nodes represent primary modules and the black nodes denote spare modules.

$$R_{cluster(2,6)}(t) = \sum_{i=0}^{2} {8 \choose i} R_m^{8-i}(t) c (1 - R_m(t))^i$$

Equation (10).

$$R_{cluster(2,6)}(t) = R_m^8(t) + 8R_m^7(t)(1 - R_m(t)) + 28R_m^6(t)(1 - R_m(t))^2$$

Equation (11).

Assuming that the (2, 6) IRA with N primary modules can be approximately divided into N/6 clusters, and the failures are independent, the reliability of the (2, 6) IRA system can be estimated by:

$$R_{(2,6)}(t) = \begin{pmatrix} R_m^8(t) + 8R_m^7(t)(1 - R_m(t)) \\ +28R_m^6(t)(1 - R_m(t))^2 \end{pmatrix}^{N/6}$$

Equation (12).

Figure 14 shows the reliability of (2, 6) IRA for different values of  $R_m(t)$  and N, and compares with the reliability of the corresponding systems without redundancy. As expected, interstitial redundancy improves system reliability.

Figure 14: The reliability of (2, 6) IRA MEA with redundancy ratio of 0.33, C = 1, and N = mn = 90, 540 and 900, and the reliability of the corresponding MEAs without redundancy.

### 3.5.4. Reliability Analysis of a (4, 4) IRA

To analyze the reliability of a (4, 4) IRA design consider the IRA design of figure 5, where the redundancy ratio is 1.0. For  $am \times n$  (4, 4) IRA, the number of primary modules, p is mn and the number of spare modules, s is (m - 1)\*(n - 1). The reliability,  $R_{(4,4)}(t)$ , of a (4, 4) IRA with fault coverage C can be approximated by equation (13) considering it as a p-out-of-(p + s) system, that is, an mn-out-of-(mn + (m-1)(n-1)) system:

$$R_{(4,4)}(t) = \sum_{i=0}^{s} {s+p \choose i} R_m^{s+p-i}(t) C(1 - R_m(t))^i$$

Equation (13).

A second approximation introduced is that while four spare modules are available to replace each non-boundary primary module, each of the four corner primary modules can be replaced by only one spare module and each of the remaining primary modules on the boundary can be replaced with two spare modules. The corner modules can be considered as a 1-out-of-2 system. Thus, the reliability of the sub-system of four corner primary modules can be given by:

$$R_{corner(4,4)}(t) = \left(\sum_{i=0}^{1} {2 \choose i} R_m^{2-i}(t) C(1 - R_m(t))^i \right)^4$$

Equation (14).

Among the remaining boundary primary modules and their corresponding spare modules, there is one set of 2(m-2) primary modules with 2(m-3) spare modules and one set of 2(n-2) primary modules with 2(n-3) spare modules. The reliability of the subsystem consisting of these modules can be approximated by 2(m-2) out-of-(4m-10) and 2(n-2) out-of-(4n-10) systems. Thus, the reliability of such a subsystem is given by equations (15), (16) and (17):

$$R_{boundary(4,4)}(t) = R_{boundary(4,4)}(t)R_{boundary(4,4)}(t)$$

Equation (15).

Where,

$$R_{boundary1(4,4)}(t) = \sum_{i=0}^{2(m-3)} {4m-10 \choose i} R_m^{4m-10-i}(t) C \left(1 - R_m(t)\right)^i$$

Equation (16).

And,

$$R_{boundary2(4,4)}(t) = \sum_{i=0}^{2(n-3)} {4n-10 \choose i} R_m^{4n-10-i}(t) C \left(1 - R_m(t)\right)^i$$

Equation (17).

Finally, the reliability of the sub-system consisting of the remaining set of (m-2)\*(n-2) primary modules with (m-3)\*(n-3) spare modules can be approximated as a (m-3)\*(n-3) out-of-(2mn-5m-5n+13) system, given by:

$$R_{other(4,4)}(t) = \sum_{i=0}^{(m-3)(n-3)} {2mn - 5m - 5n + 13 \choose i} R_m^{2mn - 5m - 5n + 13 - i}(t) C(1 - R_m(t))^i$$

Equation (18).

Thus, the reliability of a (4, 4) MEA can be obtained by combining all the subsystem reliabilities, as shown in (19):

$$R_{(4,4)}(t) = R_{corner(4,4)} R_{boundary1(4,4)} R_{boundary2(4,4)} R_{other(4,4)}$$

Equation (19).

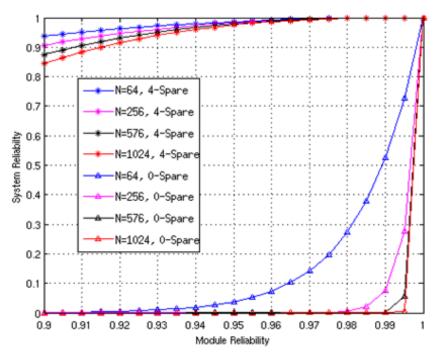

Figure 15 shows the reliability of a (4, 4) IRA for different values of  $R_m$  and N, and compares it to the reliability of the corresponding MEA without redundancy.

Figure 15: The reliability of (4, 4) IRA MEA with redundancy ratio of 1, C = 1, and N = mn = 64, 256, 576 and 1024 compared to the corresponding MEAs without redundancy.

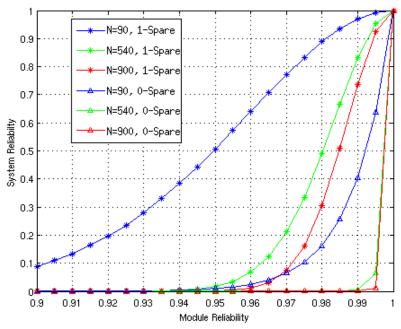

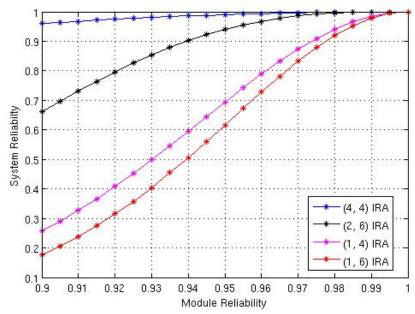

3.5.5. Comparing the System Reliabilities of (1, 4), (1, 6), (2, 6) and (4, 4) IRA MEA Designs

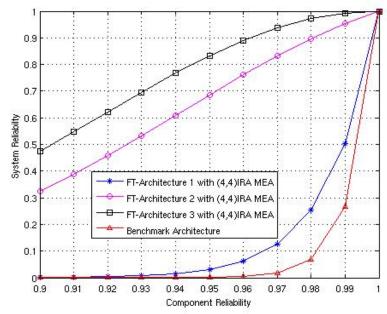

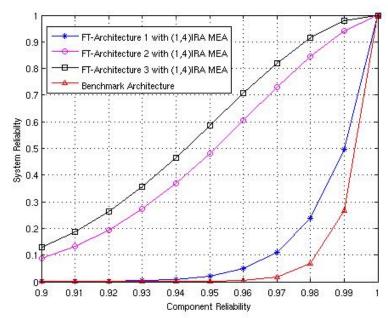

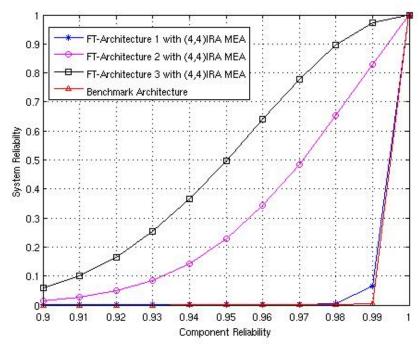

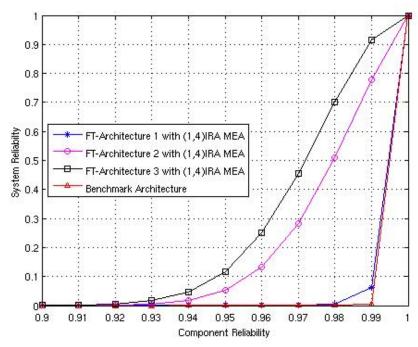

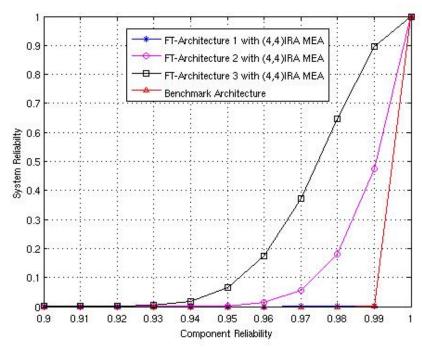

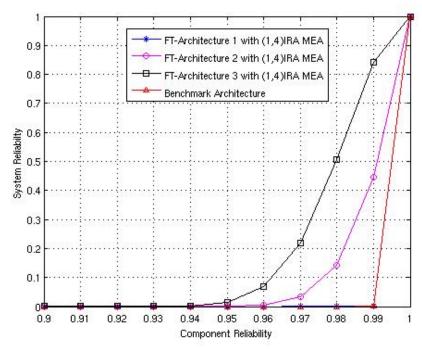

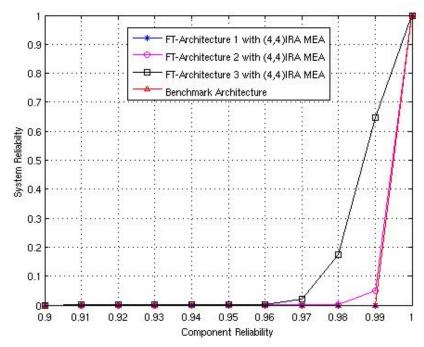

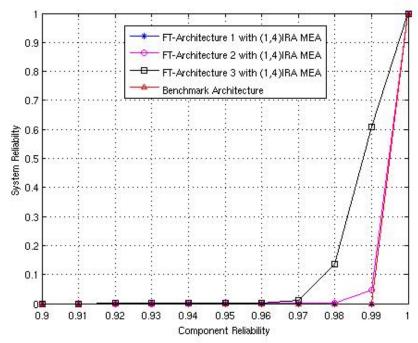

Figure 16 shows the effect of module reliability on the system reliability of (4, 4), (2, 6), (1, 4) and (1, 6) fault-tolerant MEA designs with primary modules 'N' = 64 and a fault coverage, C of 1.

From figure 16 it can be concluded that the system with a higher level of redundancy, such as the (4, 4) IRA, should be used when module reliability is low while systems with lower redundancy can be used when module reliability is high.

The IRAs considered here had redundancy ratios ranging from 0.16 to 1.0. We note that a redundancy ratio higher than one is possible (such an IRA would have more spare than primary modules), and the design and analysis developed here can be readily extended to such IRAs. Further, as indicated above, we have considered a MEA to be fault-free after reconfiguration if the number of working modules used is equal to the number of primary modules. However, a higher value of reliability can also be obtained if a smaller number of working modules suffices to achieve the desired function, that is, a graceful degradation of MEA function is acceptable.

Figure 16: Reliability comparison of (4, 4), (2, 6), (1, 4), and (1, 6) IRA designs with N = 64 and C = 1 for different values of module reliability.

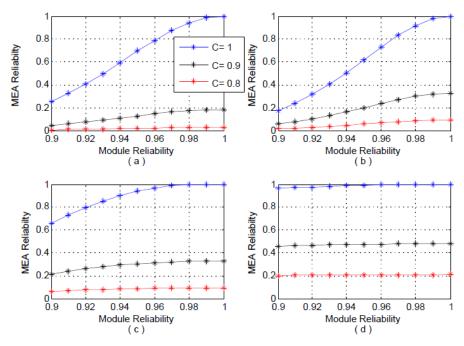

Further analysis suggests that, given a situation where the fault coverage, C, is less than 1, the fault-tolerant system continues to perform better than a system without redundancy. Figure 17, shows the reliability analysis of different IRA designs with 64 primary modules for C = 1, 0.90 and 0.80. It can be noted that a system with higher fault coverage factor should be used with lower sensor module reliability and a system with lower fault coverage factor could be used when the sensor module reliability is high to achieve desired level of overall reliability.

Figure 17: Reliability comparison of a different IRA design with coverage factors C = 1, 0.9, and 0.8 and varying module reliability in a MEA of size N = 64. (a) (1, 4) IRA design, (b) (1, 6) IRA design, (c) (2, 6) IRA design, (d) (4, 4) IRA design.

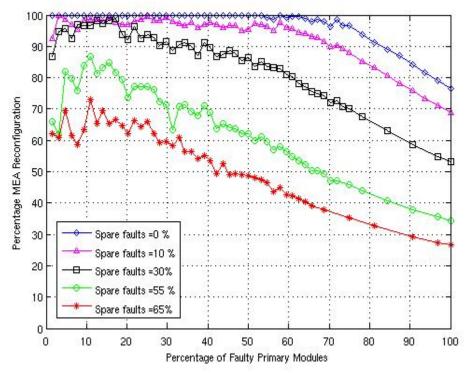

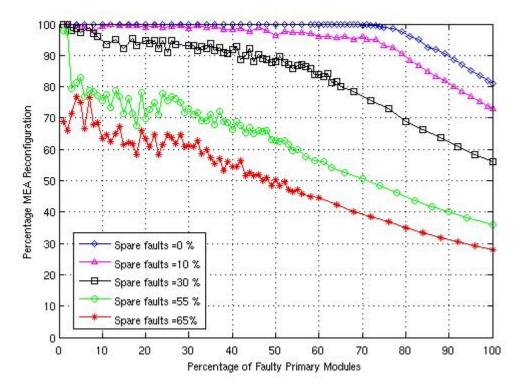

## 3.5.6 Simulating a (4, 4) IRA MEA

An extended simulation of the (4, 4) IRA MEA solution is presented in Figures 18 and 19. In this simulation random faults were injected in both primary and spare modules of the MEA and using the fault-reconfiguration algorithm the MEA was reconfigured. The evaluation corresponding to each data point is repeated 15 times, and then the percentage of instances that resulted in a successful reconfiguration of the MEA was determined. A successful reconfiguration implies that each failed module could be replaced by a functioning spare. Figure 18 shows the effect of faults in primary and spare modules of a (4, 4) IRA, with MEA sizes N = 64 and 100. The percent system reconfiguration obtained is plotted as a function of percentage of faulty primary modules with the percentage of faulty spare modules varying from 0 to 65%. Faults were injected in a random pattern within the IRA, and the simulation was run to compute the percentage of fault

reconfiguration using the maximum-matching algorithm, as described in Section 3.4. Though this analysis is performed for the (4, 4) IRA, the results can be easily extended to other IRA configurations.

Figure 18: Simulation of fault reconfiguration for a (4, 4) IRA with for s = 64, with a fault coverage factor of C = 1

Observing Figures 18 and 19, it is evident that there is a steady decrease in percentage MEA reconfiguration with increasing percentage of primary faults. A (4, 4) IRA MEA can tolerate a large number of faults and continue to be fully functional. As the number of faults increases there is a graceful degradation in the capability of the MEA.

Figure 19: Simulation of fault reconfiguration for a (4, 4) IRA with for N = 100, with a fault coverage factor of C = 1

It can be noted that the percent fault reconfiguration has a higher variance when the percentage of primary faults are low and percentage of spare faults are high as compared to the case when the percentage of primary faults are high and the percentage of spare faults are low. This is because in the presence of spare faults the percentage MEA reconfiguration varies depending on the spatial relationship between primary and spare faults. If most of the faulty primary sensors are surrounded by faulty spare sensors, the MEA reconfiguration encounters a 'worst-case' scenario. In contrast if most of the faulty primary sensors are surrounded by healthy spare sensors the system reconfiguration encounters a 'best-case' scenario. Due to these two extreme cases, the variance in the average MEA reconfiguration is much higher when the percentage of spare faults is considerably greater than the percentage of primary faults. We can also observe that percentage MEA reconfiguration is

nearly 90% when spare faults are between 0-30% and primary faults are between 0 and 50%. With increasing percentage of spare faults there is a decrease in MEA reconfiguration as may be expected. When the number of primary faults is greater than 50%, we observe, in Figures 18 and 19, a decrease in the variance of the average MEA reconfiguration. This is because as increasing numbers of primary modules become faulty there is a decrease in the difference between the best-case and the worst-case scenarios. Eventually, the variance in MEA reconfiguration minimizes. However, it is important to note that the proposed MEA offers better reliability (percent system reconfiguration  $\approx$  30%) even with a high percentage of spare faults ( $\approx$  65%) and very high primary faults ( $\approx$  90%), as compared to a MEA without redundancy.

# 3.6. Design Summary

The two fault-tolerant solutions have different degrees of reconfiguration complexity and overhead. The reconfiguration strategy for the row or column based solution is simple. It does not require, for example, a graph based matching to obtain a result. The reconfiguration for the spare row or column solution may require replacement of fault-free modules. The reconfiguration for the interstitial redundancy array is more complex; however, it does not involve replacement of fault-free modules. A fault tolerant scheme can also be proposed where row or column based and interstitial redundancy can be used together. That is, the difference in complexity and overhead of the two solutions can be used to advantage.

The fault-tolerant strategies described in this Chapter are developed for a 2D MEA. However, these solutions can readily be extended to other form-factors. For example, the concepts described here can be extended to a linear MEA with spare sensors integrated

with primary sensors on the linear array. The concepts described here can also be extended to the inner or outer surface of a tube. To do this we consider a fault tolerant sensor array to be placed on a 2D rectangular surface as described here. This rectangular surface can then be considered to be rolled so that two opposite edges of the 2D rectangular surface touch each other. A surface rolled in this manner will form a tube. The sensing array may be placed on the inner and/or outer wall of this tube. The concepts developed here can also be extended to the surface of other 3D structures such as a sphere with primary and spare sensors placed at different latitudinal or longitudinal points on the surface of the sphere. The reconfiguration algorithm described here can readily be extended to these non-2D form factors so that there is continuity across the entire surface of sensors.

# CHAPTER 4: DESIGN OF A FAULT-TOLERANT BRAIN IMPLANTABLE DEVICE

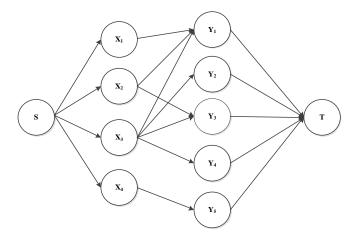

An ideal brain implantable device or a brain-machine interface should include a neural signal processing block that assists in recording and monitoring the underlying neural activity and a neuromodulator which if required, can trigger a signal to stimulate the underlying brain tissue or deliver drugs locally to intervene an undesirable neural activity such as a seizure. Therefore, a brain implantable device should include (i) electronic circuits that can assist in processing and recording the weak neural signals captured by the array of electrodes in the implanted multi-electrode array (MEA) and (ii) a logic block which can analyze the incoming signals and trigger an intervening mechanism deliver local drugs to stall the progression of harmful neural progression.

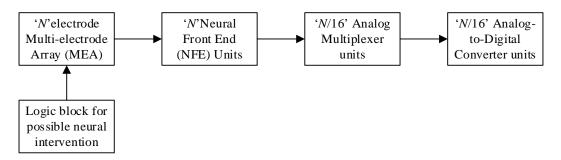

A block diagram of a typical neural signal monitoring and modulating circuit has been discussed earlier in figure 2, Chapter 2. Referring to figure 2, it is evident that the neural activity monitoring occurs in the following three blocks: (1) the neural-front-end (NFE); (2) the analog multiplexer; (3) and the analog-to-digital-converter (ADC). The NFE includes a low-noise-amplifier (LNA) to provide a first level of amplification to the weak neural signals, a band-pass filter to select the frequency band of signals that are of interest and a unity gain buffer to further amplify and strengthen the weak neural signals that are required for monitoring and hence need further processing. Figure 20 represents a block diagram of a brain implantable device that includes real-time neural signal monitoring and modulating blocks, comprising of an array of electrodes (MEA), an amplifying and

filtering unit (NFE), a digitizing unit (ADC), and a logic block that acts upon data received from the implanted device to execute neural signal intervention in order to subside a potentially harmful neural activity.

Figure 20: Block diagram of a brain implantable device with neural signal monitoring and modulating or neural intervening capability.

In this architecture, for an 'N' electrode multi-electrode-array (MEA), where 'N' is the number of electrodes in the MEA, the neural signal processing block consists of 'N' neural-front-end units. According to earlier IC designs to observe brain activity [69], demonstrates that, each electrode is designed to have its own dedicated neural-front-end unit to process the weak neural signals captured by the respective electrodes instead of using an analog multiplexer to timeshare a single amplifier between multiple electrodes.

The key motivation behind allocating each electrode with its own dedicated low-noise-amplifier is that the time constants inherent in the amplifier dynamics are typically much longer than the multiplexer switching time required catching the brief neural activity across an array of many electrodes. Another piece of literature which focuses on optimizing the power and area in the design of *in vivo* integrated neural systems [60], demonstrate that irrespective of the circuit topology and process technology used in the design of such systems the optimal multiplexing ratio which makes the systems power-area product minimum is 16. Hence, to achieve an area-power optimal design, this work includes one

multiplexing unit and one ADC for every 16 electrodes the basic brain implantable system design. Figure 20 represents this for an 'N' electrode brain implantable system, i.e. for a system with 'N' electrodes in the multi-electrode array; the minimum area-power product in the design can be achieved with 'N/16' analog multiplexers and 'N/16' analog-to-digital converters.