# POWERLINE COMMUNICATIONS THROUGH SERIES CONNECTED SWITCHED MODE POWER CONVERTERS TO BE USED IN SOLAR MICROINVERTERS

by

# Daniel Wade Evans

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2018

| Approved by:        |

|---------------------|

| Dr. Robert Cox      |

| Dr. Babak Parkhideh |

| Dr. Thomas Weldon   |

| Dr. Aidan Browne    |

©2018 Daniel Wade Evans ALL RIGHTS RESERVED

#### ABSTRACT

DANIEL WADE EVANS. Powerline communications through series connected switched mode power converters to be used in solar microinverters. (Under the direction of DR. ROBERT COX)

Modern photovoltaic converters and energy storage modules are shifting to a cascaded or distributed module-level inverters to reduce the required voltage output of each module and thereby optimizing production costs. The switch to an AC-stacked architecture, where all modules are in series, requires a method of synchronization of the voltage and current output of each module to the grid since each module has no direct connection to the grid as to acquire such synchronization. Many different methods for communicating the zero crossing to each photovoltaic converter module are currently available but either increases plant level costs from running additional wiring for wired mediums or are susceptible to remote interference in wireless communication mediums potentially disrupting operation by either loss of synchronization or inaccurate timing of synchronization to the zero crossing of the grid.

This research develops a current-mode based methodology for powerline communication and synchronization by which the photovoltaic converter and energy storage modules may detect the zero crossing and synchronize the converter operation to the grid. Included in the methodology is the use of series connected power electronics as a communications medium for the current-mode based means of power line communications. The developed communications model, generalized for all series connected power electronics, establishes a foundation for part the physical layer in the OSI model. This model is implemented and performance analyzed in synchronization of a physical system consisting of series connected inverters used in solar power conversion. The approach has been used to allow an 8-module,  $120V_{RMS}$  string to operate in the field for over six months without any synchronization or controls-related failures.

#### ACKNOWLEDGEMENTS

I want to acknowledge SineWatts, Incorporated (Inc.) and the chief executive officer (CEO), Shibashi Bowhmik, for opportunity to work with and help develop the technology used in the panel level optimized solar inverters deemed the SineWatts 'Molecule'. Hardware design, whether it be for research or product development, involves a significant financial cost that must be paid upfront. SineWatts, Inc. has borne those costs throughout this dissertation and has made it possible for this work to be completed.

I also want to acknowledge my advisor, Dr. Robert Cox, for all the insight he has provided over the years. His knowledge and experience in the design of electronics has been invaluable. He has also put forth a lot of effort to see the completion of the designs presented in this dissertation, even spending nights and mornings working with me in the lab.

I also want to acknowledge my coworkers Paul O'Connor, John Troxler, Deepak Somayajula, and Saurabh Trivedi as well as Hamid Jafarian, Mehrdad Biglarbegian, Iman Mazhari, Shahriar Nibir, and Dr. Babak Parkhideh at UNC Charlotte that participated on the project. They have greatly assisted in the setups and testing with the communications.

## **DEDICATION**

This work is dedicated to my family. My father, Wade Evans, has sacrificed a lot to help put me through school. My mother, Billie Evans, has been a constant source of love and encouragement. No matter what was going on, I could always visit and enjoy a home cooked meal. I enjoyed visiting my brother and my sister-in-law, Brent and Tamara Evans, and their children. The role of crazy uncle is a blast playing with my niece and nephew. Watching them grow up, I see how quickly anyone can learn when they focus. During the later stages of research and writing, two major experiences changed my look on life. My brother had a blocked artery in his heart and had a stint put in. Afterward, I became an uncle to a second nephew. Events like this tends to put life back into perspective. I am glad to have more time to spend with my family.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                               | ix  |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| LIST OF TABLES                                                                                                                | XV  |

| LIST OF ABBREVIATIONS                                                                                                         | xvi |

| CHAPTER 1: INTRODUCTION                                                                                                       | 1   |

| 1.1. Progression of Switched Mode Converters Used in Photovoltaic Converters                                                  | 1   |

| 1.2. Overview of the SineWatts Architecture                                                                                   | 7   |

| 1.3. Importance of Grid Synchronization                                                                                       | 13  |

| 1.4. Comparison of Synchronization Methodologies                                                                              | 16  |

| 1.5. Conceptual Overview of Grid Synchronization Through the<br>Power Line                                                    | 19  |

| 1.6. Research Contribution                                                                                                    | 20  |

| 1.7. Organization of Dissertation                                                                                             | 21  |

| CHAPTER 2: LITERATURE REVIEW                                                                                                  | 22  |

| 2.1. Overview of Power Line Carrier Communications                                                                            | 23  |

| 2.2. Power Line Carrier Communications Through Series Connected<br>Switched Mode Converters Used in Solar Converters          | 24  |

| 2.3. Specifications of Grid Synchronization Through a Power Line Carrier                                                      | 25  |

| CHAPTER 3: IMPLEMENTATION OF THE PHYSICAL ACCESS LAYER FOR THE RECEIVER AND TRANSMITTER WITH SIM-ULATED AND EMPIRICAL RESULTS | 27  |

| 3.1. Design and Simulation of the Physical Access Layer                                                                       | 27  |

| 3.2. Implementation of the Physical Receiver Layer                                                                            | 35  |

|                                                                                                                    | vii |

|--------------------------------------------------------------------------------------------------------------------|-----|

| 3.3. Implementation of the Physical Transmitter Layer                                                              | 49  |

| 3.4. Empirical Results of the Physical Access Layer                                                                | 52  |

| CHAPTER 4: COMMUNICATIONS CHANNEL MODEL UTILIZING SERIES-CONNECTED POWER ELECTRONIC MODULES                        | 61  |

| 4.1. Understanding the Physical System Propagation Effects                                                         | 61  |

| 4.2. Modeling of the Switched Mode Power Converters                                                                | 64  |

| 4.3. Modeling of the Powerline Impedance                                                                           | 70  |

| 4.4. Modeling of the Grid Impedance                                                                                | 71  |

| 4.5. Communications Channel Model                                                                                  | 72  |

| 4.6. Empirical Results of Communications Channel Model                                                             | 75  |

| CHAPTER 5: CHARACTERIZATION OF NOISE IN THE COMMUNICATIONS CHANNEL MODEL AND EFFECT ON RELIABILITY                 | 77  |

| 5.1. Noise Characterization in the AC-Stacked Inverter Architecture                                                | 79  |

| 5.2. Noise Measurements in the AC-Stacked Inverter Architecture                                                    | 85  |

| 5.3. Reliability of Communications                                                                                 | 92  |

| CHAPTER 6: RESULTS OF THE POWER LINE CARRIER WITH RUNTIME OPERATION OF SWITCHED MODE POWER CONVERTERS              | 97  |

| 6.1. System Operation of the AC-Stacked Switched Mode Power Converters with the PLC on a Separate Line             | 98  |

| 6.2. System operation of the AC-Stacked Switched Mode Power Converters with the PLC Integrated with the Power Line | 101 |

| 6.3. Analysis of the AC-Stacked Inverter Architecture's Total Harmonic Distortion with PLC Integration             | 103 |

| 6.4. Field Test Results                                                                                            | 106 |

| CHAPTER 7: SUMMARY, CONCLUSION AND FUTURE WORK                                                                     | 108 |

|                                                                                    | viii |

|------------------------------------------------------------------------------------|------|

| REFERENCES                                                                         | 111  |

| APPENDIX A: SOURCE CODE FOR MATLAB SIMULATION OF THE COMMUNICATIONS PHYSICAL LAYER | 119  |

| APPENDIX B: SOURCE CODE FOR MATLAB SIMULATION OF THE ENCODING SCHEME               | 122  |

| APPENDIX C: SOURCE CODE FOR THE MATLAB SIMULATION OF THE PLL IN THE RECEIVER       | 130  |

# LIST OF FIGURES

| FIGURE 1.1: Representation of a central inverter.                                                                                          | 2  |

|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 1.2: Representation of a string inverter.                                                                                           | 3  |

| FIGURE 1.3: Representation of a multi-string inverter.                                                                                     | 4  |

| FIGURE 1.4: Representation of a microinverter.                                                                                             | Ę  |

| FIGURE 1.5: Representation of a DC optimizer.                                                                                              | 5  |

| FIGURE 1.6: Representation of PV inverter topologies.                                                                                      | 6  |

| FIGURE 1.7: Representation of the SineWatts inverter Molecule.                                                                             | 8  |

| FIGURE 1.8: Representation of the SineWatts inverter Molecule in a string.                                                                 | Ć  |

| FIGURE 1.9: Steady state model of the SineWatts architecture.                                                                              | 10 |

| FIGURE 1.10: Simplified internal structure of the SineWatts Inverter Molecule $^{\rm TM}$ .                                                | 10 |

| FIGURE 1.11: Circuit model for a generator.                                                                                                | 14 |

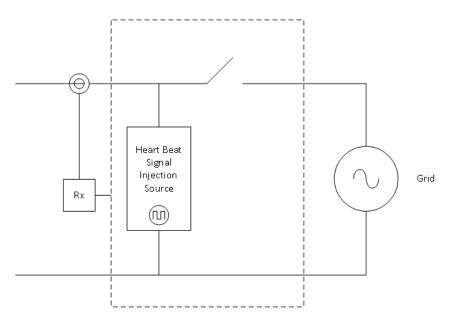

| FIGURE 1.12: Visualization of the basic synchronization structure is series connected architectures.                                       | 17 |

| FIGURE 1.13: Representation of the grid connection for the AC-stacked string.                                                              | 19 |

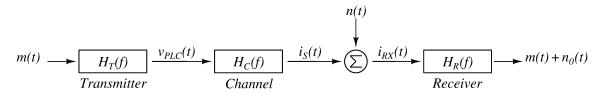

| FIGURE 2.1: Typical PLC communications receiver and transmitter circuitry.                                                                 | 23 |

| FIGURE 2.2: Typical PLC communications configuration where all devices are connected in parallel across the grid.                          | 24 |

| FIGURE 2.3: PLC communications setup in series representing the communication modules on each switched mode power converter in the string. | 25 |

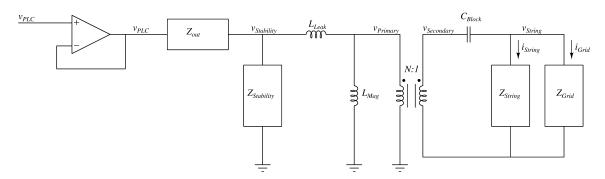

| FIGURE 3.1: Preliminary modeling of the impedance seen by the PLC current injection.                                                       | 28 |

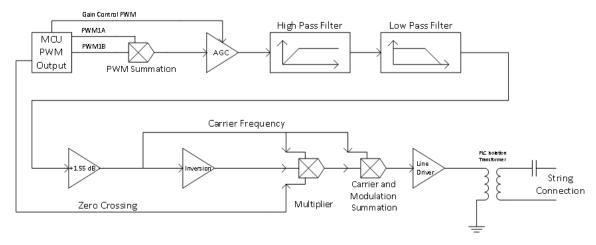

| FIGURE 3.2: Simplified block diagram of the modulation technique for the PLC communications.                                         | 29 |

|--------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 3.3: Ideal carrier waveform used for the PLC and the inverted carrier utilized for the phase shift keying.                    | 30 |

| FIGURE 3.4: Simulation of the BPSK modulation of the PLC.                                                                            | 30 |

| FIGURE 3.5: Grid zero cross detection scheme.                                                                                        | 31 |

| FIGURE 3.6: Block diagram of the physical receiver layer.                                                                            | 32 |

| FIGURE 3.7: Simulation of the PLL for the demodulation circuit.                                                                      | 32 |

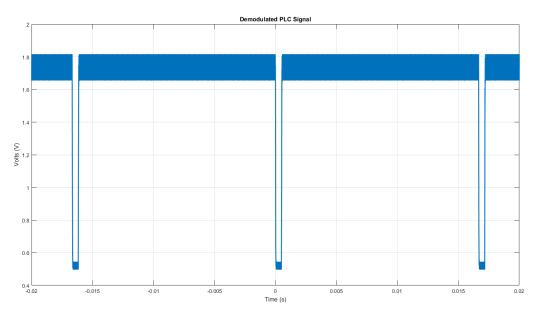

| FIGURE 3.8: Simulation of the ideal demodulation before filtering.                                                                   | 33 |

| FIGURE 3.9: Simulation of the ideal demodulation after filtering.                                                                    | 34 |

| FIGURE 3.10: Simulation of the ideal demodulation final TTL output.                                                                  | 35 |

| FIGURE 3.11: Block diagram of the full PLC receiver showing the different modules to detect and demodulate the communication signal. | 36 |

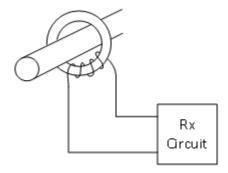

| FIGURE 3.12: The receiver coil wraps around the power line to couple the PLC signal to the receiver circuit.                         | 37 |

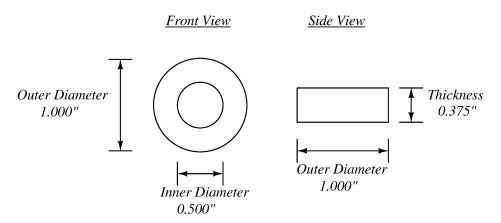

| FIGURE 3.13: Physical drawing of the nylon spacer used for the implementation of the receiver coil.                                  | 37 |

| FIGURE 3.14: Physical drawing of the nylon spacer used for the implementation of the receiver coil.                                  | 37 |

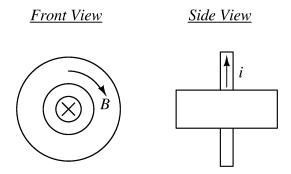

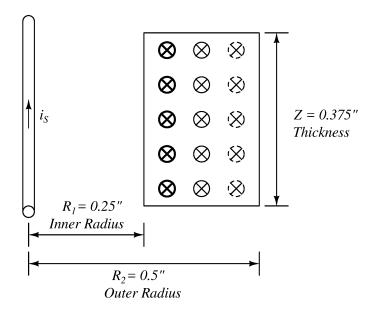

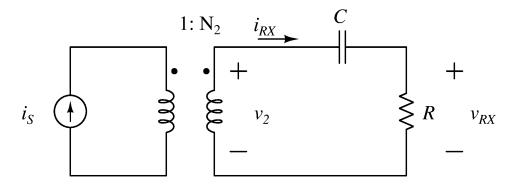

| FIGURE 3.15: Drawing of the B field inside a cross section of the receiver coil.                                                     | 38 |

| FIGURE 3.16: Circuit model for the actual current transformer and its interface circuit.                                             | 40 |

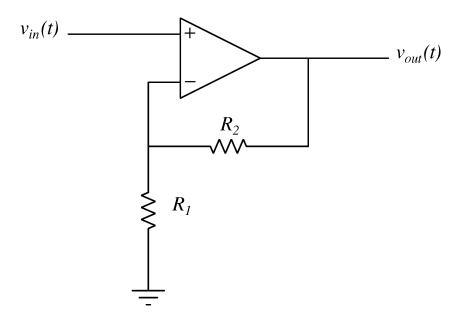

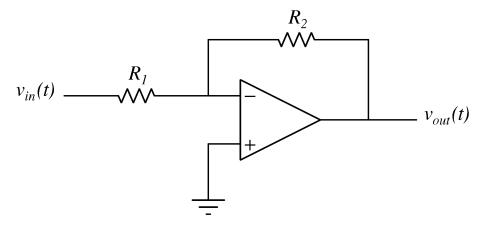

| FIGURE 3.17: A non-inverting amplifier configuration used in the design of the gain stages.                                          | 41 |

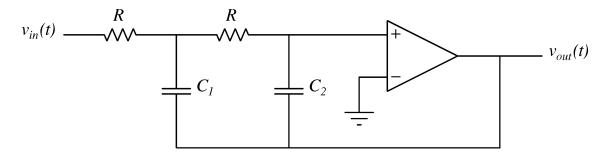

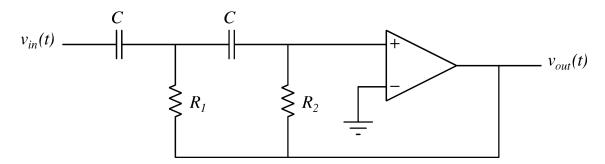

| FIGURE 3.18: A second order Sallen-Key low pass filter used to implement the low pass filtering blocks.                              | 41 |

|                                                                                                                                                                                | X  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 3.19: A second order Sallen-Key high pass filter used to implement the high pass filtering blocks.                                                                      | 42 |

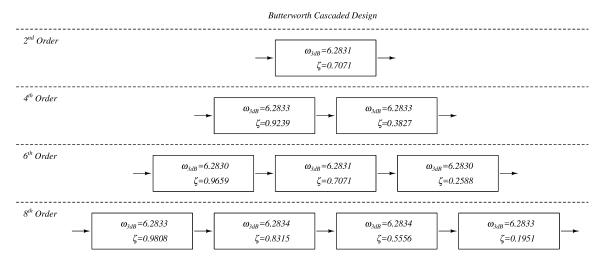

| FIGURE 3.20: Design parameters for cascaded Butterworth filter designs utilized for the high and low pass filters.                                                             | 45 |

| FIGURE 3.21: Switching strategy for gain control to produce a fundamental frequency of the input voltage with a gain reduction proportional to the duty cycle.                 | 45 |

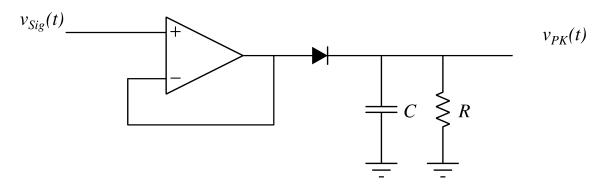

| FIGURE 3.22: A peak rectifier circuit utilized to determine the magnitude of the signal.                                                                                       | 46 |

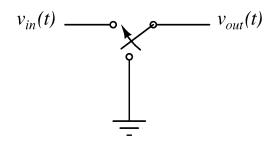

| FIGURE 3.23: Switch-based multiplier used to mix the received signal with the carrier. The resulting process, along with a low pass filter, will recover the modulated signal. | 47 |

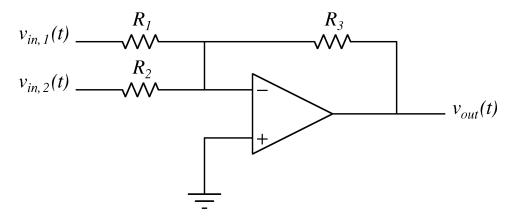

| FIGURE 3.24: An inverting amplifier configuration used in the PLL multiplication stage of the receiver.                                                                        | 48 |

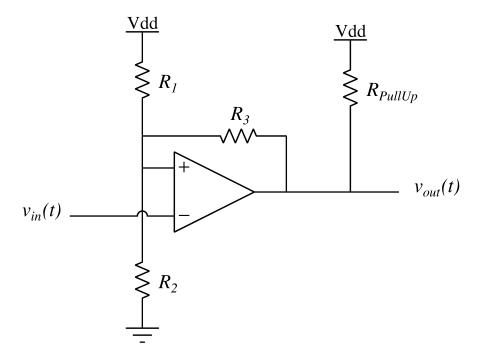

| FIGURE 3.25: The Schmitt trigger implementation for conversion of the demodulated signal to a TTL output.                                                                      | 48 |

| FIGURE 3.26: Block diagram of the full PLC transmitter showing the different modules to create the carrier and modulate the communications signal.                             | 49 |

| FIGURE 3.27: A summation amplifier configuration used in the carrier generation from the PWM signals of the microcontroller.                                                   | 50 |

| FIGURE 3.28: The receiver frontend detects the synchronization signal through the current transformer.                                                                         | 52 |

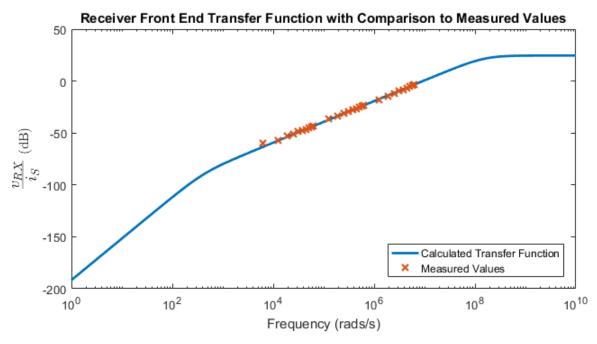

| FIGURE 3.29: Predicted (solid line) and measured frequency response of the receiver front end over a range from 1 kHz to 1 MHz.                                                | 53 |

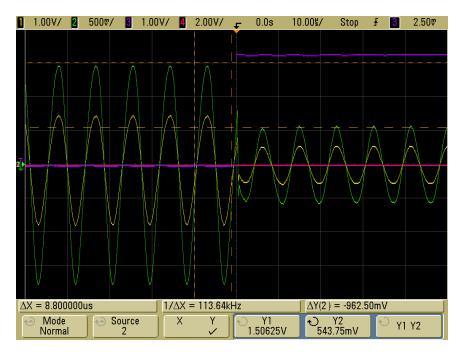

| FIGURE 3.30: Implementation results of the automatic gain control.                                                                                                             | 54 |

| FIGURE 3.31: Implementation results of the receiver's demodulation block.                                                                                                      | 55 |

|                                                                                                                                                                                |    |

FIGURE 3.32: Implementation results for the communications carrier

generation from the PWM channels of the DSP.

56

|                                                                                                                                                                                                                   | xii |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| FIGURE 3.33: Implementation results for the transmission circuit gain control.                                                                                                                                    | 57  |

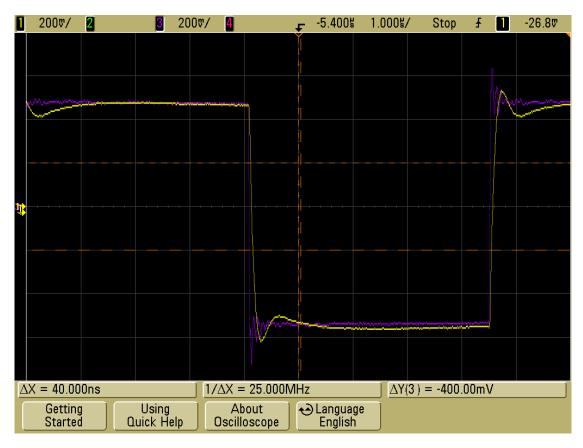

| FIGURE 3.34: Step response of the line driver circuit with stability network.                                                                                                                                     | 58  |

| FIGURE 3.35: Modulation of the transmitter circuit showing the encoding of the carrier at the line driver.                                                                                                        | 59  |

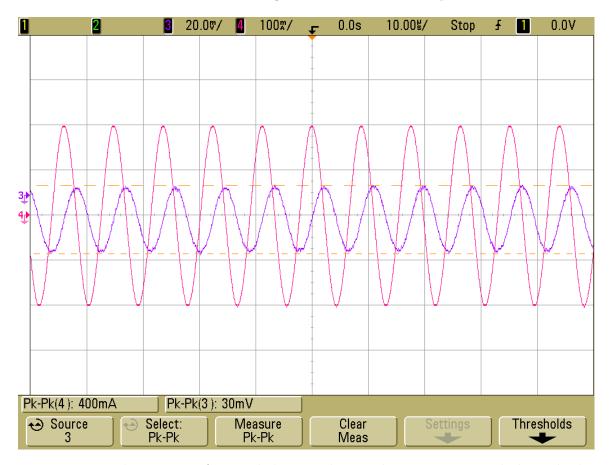

| FIGURE 3.36: Current outputs from the line driver circuit and the isolation transformer for the transmission circuit.                                                                                             | 59  |

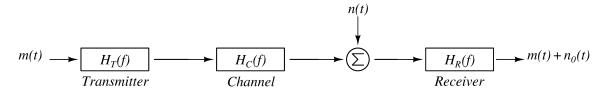

| FIGURE 4.1: Generic communication channel model to be adapted for utilizing series connected power electronic modules.                                                                                            | 61  |

| FIGURE 4.2: Traditional power line communications tend to have a transmission path that can branch to various locations across the distribution network requiring a multipath model for the communication system. | 62  |

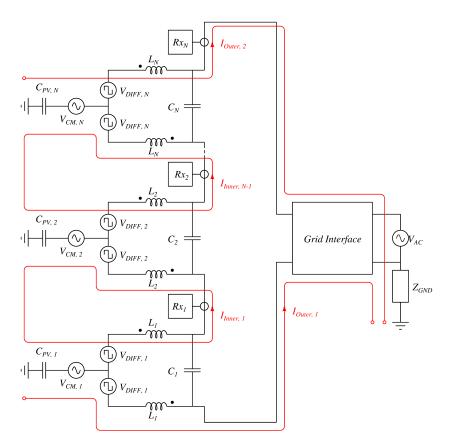

| FIGURE 4.3: Conceptual circuit model for the AC-stacked inverter system.                                                                                                                                          | 63  |

| FIGURE 4.4: Generalized schematic for a DC-Optimizer. The output of the converter is series-connected and allows the PLC current to pass through the output filter as its medium.                                 | 65  |

| FIGURE 4.5: Generalized schematic for a cascaded H-bridge. The output does not contain a filter to direct the PLC current when series-connected and instead sees the impedance of the switches.                   | 65  |

| FIGURE 4.6: Generalized schematic for the AC-stacked inverter hardware. Like the DC-Optimizer, the inverter contains the LC filter at the output which makes the impedance modeling the same.                     | 66  |

| FIGURE 4.7: Circuit model for the inverter module output filter to determine the impedance of the converter with respect to the communications current.                                                           | 69  |

| FIGURE 4.8: Lumped transmission line model for the wiring impedance.                                                                                                                                              | 70  |

FIGURE 4.9: Circuit model for the grid interface hardware.

72

|                                                                                                                                                                                                      | xiii |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| FIGURE 4.10: Communication channel model for utilizing the series connected power electronic modules.                                                                                                | 73   |

| FIGURE 4.11: Circuit model for the transmission hardware used to develop the transfer function of the line driver voltage output to the string current.                                              | 73   |

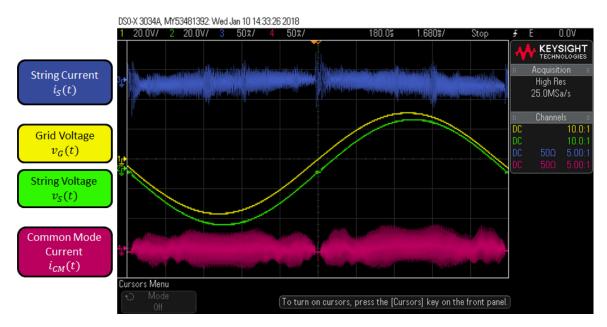

| FIGURE 5.1: Currents under open-circuit switching in a two-inverter string: total current current leaving one inverter (blue) and common-mode current (pink).                                        | 79   |

| FIGURE 5.2: Ground current leakage paths exist in the AC-stacked architecture causing additional noise in the receiver.                                                                              | 80   |

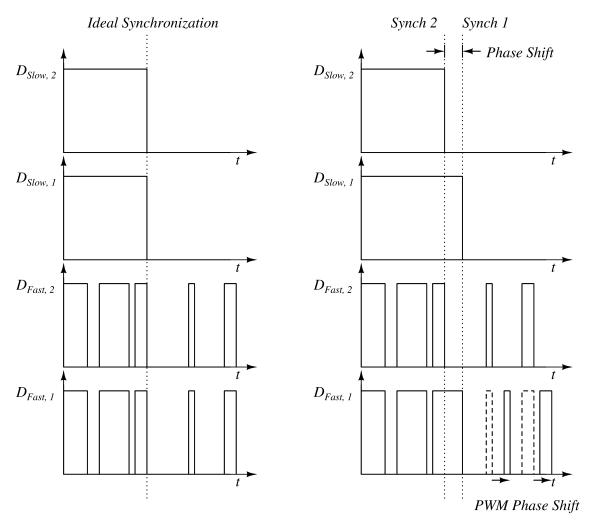

| FIGURE 5.3: PWM alignment example showing the offset that occurs due to synchronization variance.                                                                                                    | 81   |

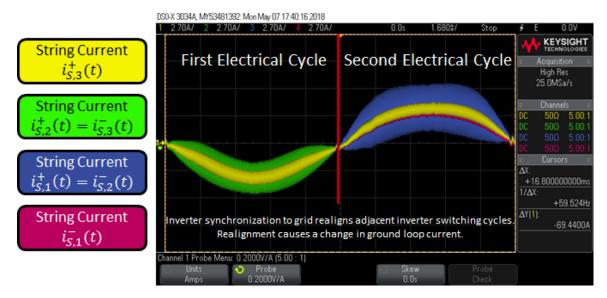

| FIGURE 5.4: Total current measured in each wire connecting the outputs of a three module AC-stacked inverter system.                                                                                 | 82   |

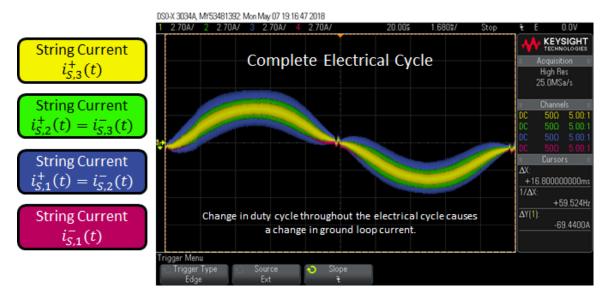

| FIGURE 5.5: A complete electrical cycle showing the leakage currents vary in magnitude due to changing duty cycle throughout the electrical cycle causing the leakage current to be cyclostationary. | 82   |

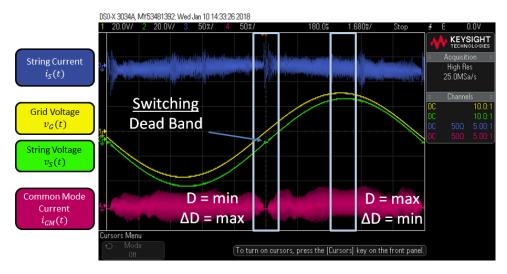

| FIGURE 5.6: Visual portrayal of the time slices of the duty ratio control of the inverter's switches are at the upper and lower limits.                                                              | 83   |

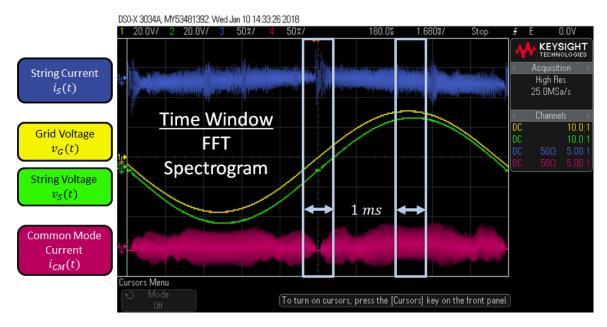

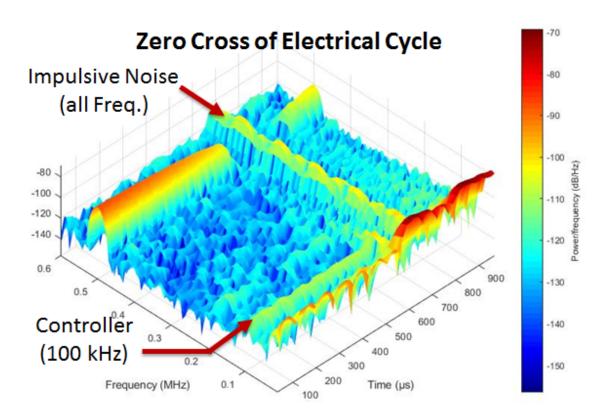

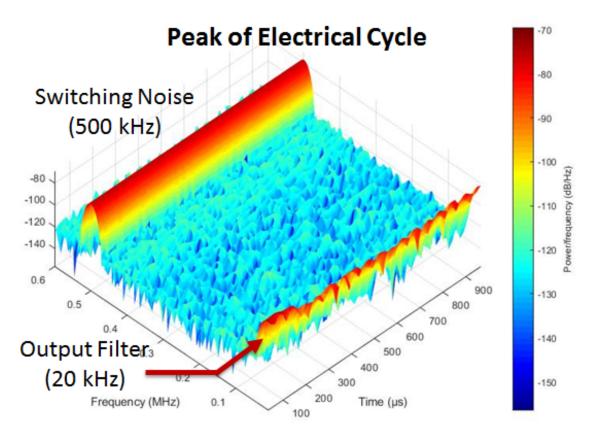

| FIGURE 5.7: Visual portrayal of the time slices of the noise is taken for the FFT window and the spectrogram analysis.                                                                               | 86   |

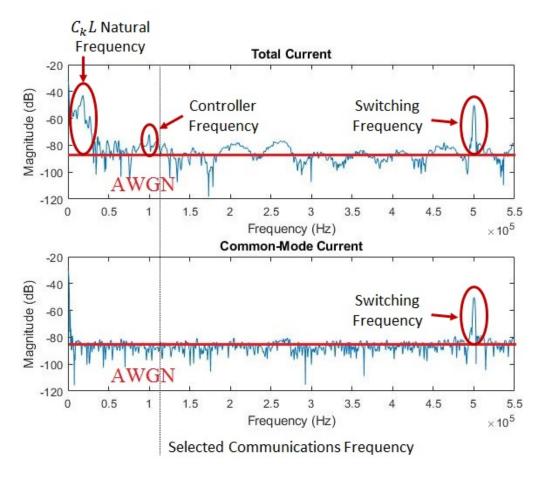

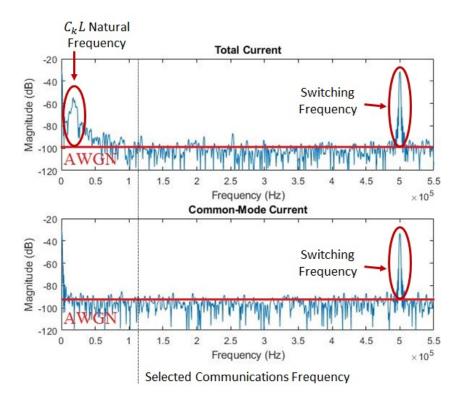

| FIGURE 5.8: Fast Fourier transform (FFT) of the currents of figure 5.1 showing the frequency spectrum of the noise that occurs centered at the zero crossing of the electrical cycle.                | 87   |

| FIGURE 5.9: Fast Fourier transform (FFT) of the currents of figure 5.1 showing the frequency spectrum of the noise that occurs centered at the peak of the electrical cycle.                         | 88   |

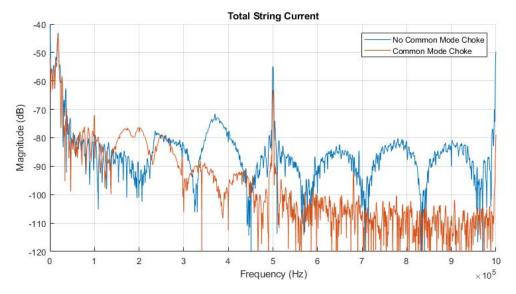

| FIGURE 5.10: Reduction of common mode noise as seen in the total sting current with the addition of a common mode filter at the output of the inverter module.                                       | 89   |

|                                                                                                                                                                                                                                   | xiv |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

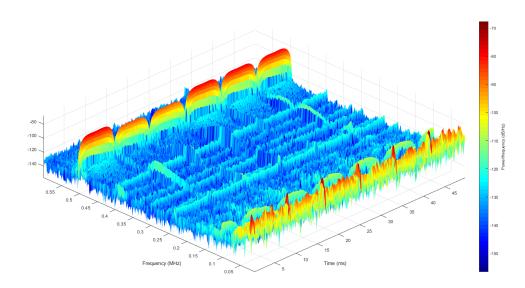

| FIGURE 5.11: Spectrogram showing the power spectral density (PSD) of the noise across three electrical cycles of the AC-stacked inverter system during switching operation but without generating power into the electrical grid. | 90  |

| FIGURE 5.12: Spectrogram showing the power spectral density (PSD) of the noise zoomed in at the zero crossing of the electrical cycle.                                                                                            | 91  |

| FIGURE 5.13: Spectrogram showing the power spectral density (PSD) of the noise zoomed in at the peak of the electrical cycle.                                                                                                     | 92  |

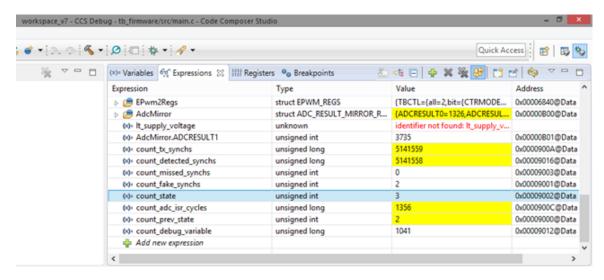

| FIGURE 5.14: Debug mode of Texas Instruments embedded development software showing the running counters of the bit error rate test.                                                                                               | 94  |

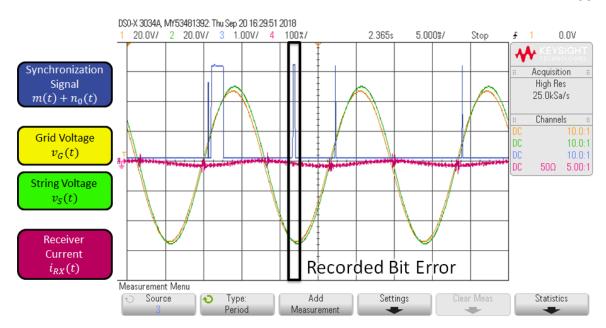

| FIGURE 5.15: Observed bit error in the receiver during operation of the AC-stacked inverter system.                                                                                                                               | 95  |

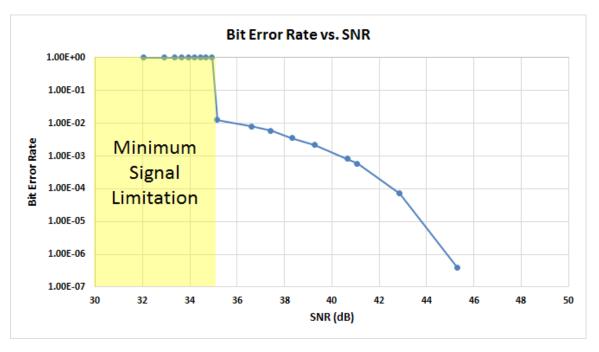

| FIGURE 5.16: Plot of the observed bit error rate compared to the signal to noise ratio of the communications current detected by the receiver.                                                                                    | 95  |

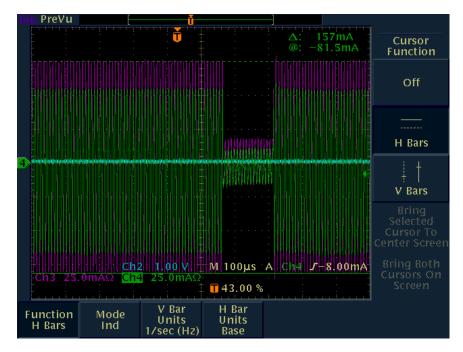

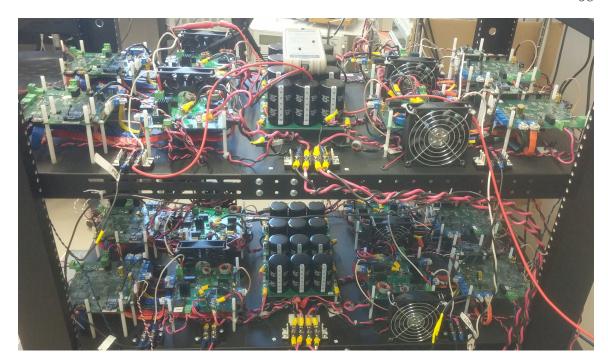

| FIGURE 6.1: Laboratory prototype of the AC-stacked inverter architecture. This prototype system was used to verify the model for the transmission model presented for series-connected power electronics.                         | 98  |

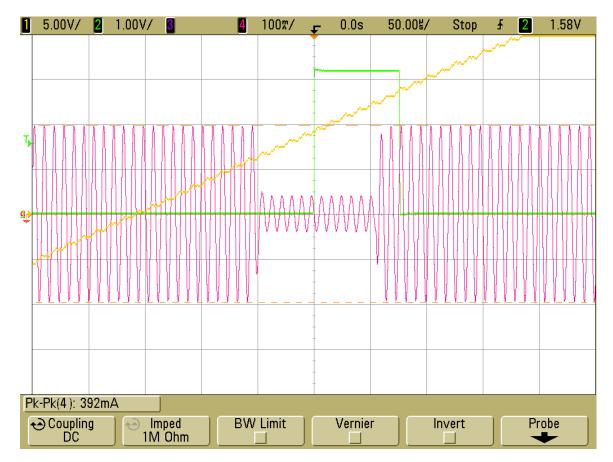

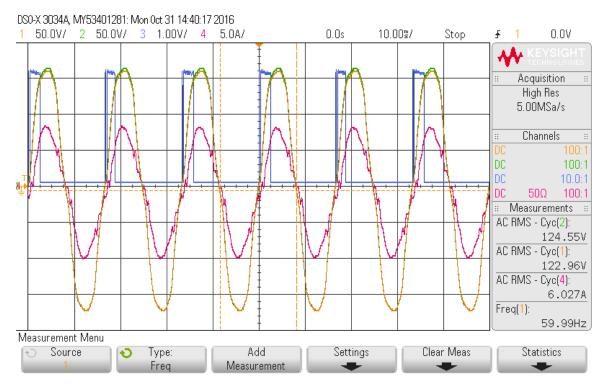

| FIGURE 6.2: Operation of the communication system in the AC-stacked inverter architecture using a separate wire.                                                                                                                  | 99  |

| FIGURE 6.3: AC-Stacked inverter architecture operating utilzing current-mode powerline communications on a separate wire.                                                                                                         | 100 |

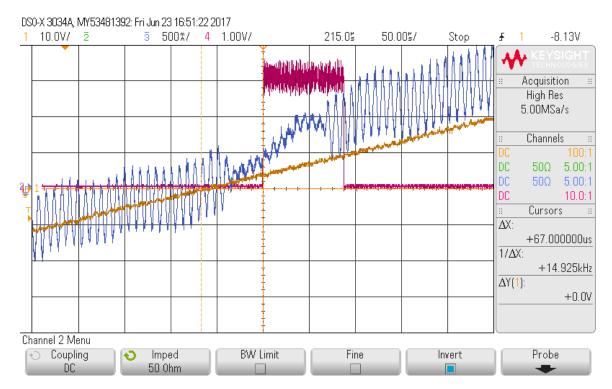

| FIGURE 6.4: Operation of the communication system in the AC-stacked inverter architecture using the powerline.                                                                                                                    | 101 |

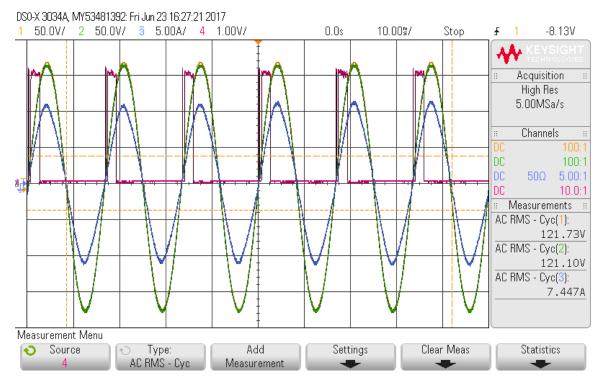

| FIGURE 6.5: AC-Stacked inverter architecture operating utilzing current-mode powerline communications on the powerline                                                                                                            | 102 |

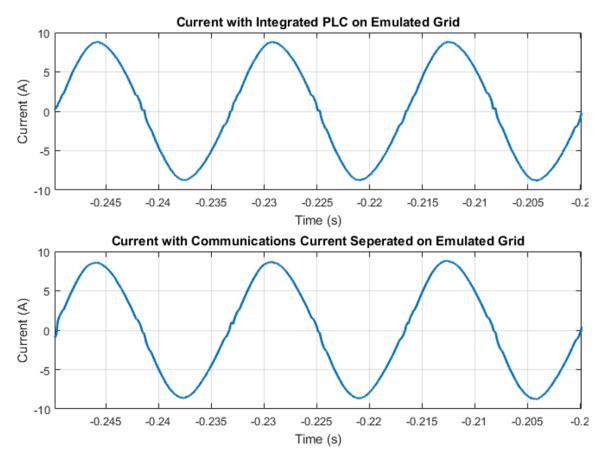

| FIGURE 6.6: Time domain comparison of string currents to show impact of communications current on the current controller.                                                                                                         | 104 |

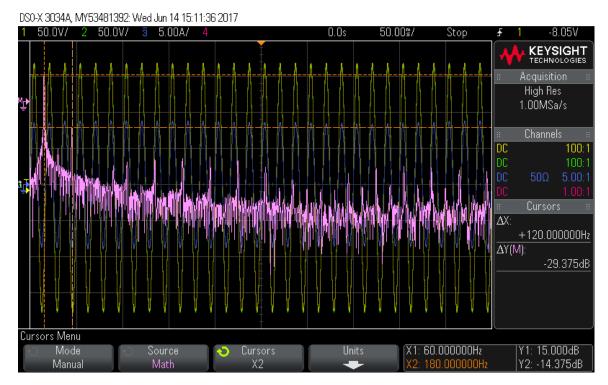

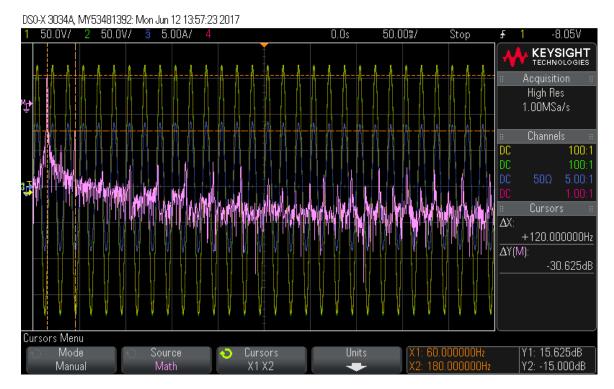

| FIGURE 6.7: FFT of the string current during operation with powerline communications on a separate wire.                                                                                                                          | 105 |

| FIGURE 6.8: FFT of the string current during operation with powerline communications on the powerline.                                                                                                                            | 106 |

107

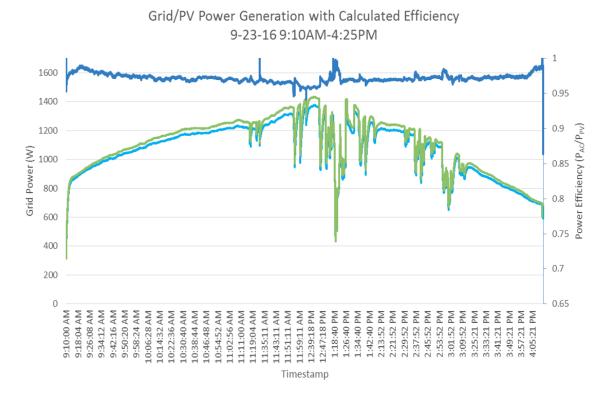

FIGURE 6.9: Field test results of the AC-stacked inverter architecture deployed in Alamabama.

| LIST OF TABLES                                                                                                                        |     |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| TABLE 3.1: Design parameters and component values for the 2 <sup>nd</sup> order Sallen-Key high pass filter used in the PLC receiver. | 44  |

| TABLE 3.2: Design parameters and component values for the 6 <sup>th</sup> order Sallen-Key low pass filter used in the PLC receiver.  | 44  |

| TABLE 6.1: Comparison of the string current THD to see any impact of the communications integration to the powerline.                 | 105 |

xvi

## LIST OF ABBREVIATIONS

AC alternating current

ADC analog to digital converter

AGC automatic gain control

ANT Advanced and Adaptive Network Technology

AWGN additive white Gaussian noise

BPSK binary phase shift keying

CAN controller area network

CSV comma-separated values

DC direct current

DSP digital signal processor

FET field effect transistor

FFT fast Fourier transform

IC integrated circuit

KCL Kirchhoff's current law

KVL Kirchhoff's voltage law

MLPE module level power electronics

MOSFET metal oxide semiconductor field effect transistor

MPPT maximum power point tracking

NASA National Aeronautics and Space Administration

OFDM orthogonal frequency division multiplexing

OSI open system interconnection

PCB printed circuit board

PF power factor

PLC power line carrier

PLL phase locked loop

PRIME Powerline Intelligent Metering Evolution

PSD power spectral density

PV photovoltaic

PWM pulse width modulation

QPSK quadrature phase shift keying

SNR signal to noise ratio

SPI serial peripheral interface

THD total harmonic distortion

TI Texas Instruments

TTL transistor-transistor logic

UNC University of North Carolina

VCO voltage controlled oscillator

#### CHAPTER 1: INTRODUCTION

Since the dawn of time, man has relied on the sun's energy to survive. In 1941, Ohl patented the first silicon solar cell in the United States with an efficiency of less than 1 % [1–3]. As effiency increased, the National Aeronautics and Space Administratin (NASA) became interested in using the solar cells for the purpose of powering satellites and proceeded to launch the Vanguard 1 [4]. Since then, efficiency of the silicon PV cells have increased to 26.7% [5] and commercially available silicon solar panels have now risen to 22.7% [6]. It is noted that new solar cells, such as III-V class materials and multi-junction manufacturing, are being investigated for manufacturing besides traditional silicon cells, but are not commercially available. The highest reported efficiency of these types of solar cells is 46% [5].

Once the solar panels have converted solar energy into electrical energy, the distribution and use of the electrical energy is considered in the design of a photovoltaic converter. For the purpose of generating large amounts of power into the electrical grid, switched mode converters have been employed with the first 1-megawatt power station, and ARCO Solar design, being commissioned during 1982 in Hisperia, California [4].

#### 1.1 Progression of Switched Mode Converters Used in Photovoltaic Converters

Photovoltaic (PV) power generation is currenting expanding at a rate of 43% year-over-year in the United States [7], with total penetration expected to reach at least 178 GW by 2040 [8]. Depending on the impact of policies such as the Clean Power Plan (CPP), this growth could potentially be much larger [8]. Current growth is largely fueled by the ever-decreasing costs of PV modules and associated equipment,

with some developers claiming that installed costs on utility-scale systems will be less than \$1 per  $W_{DC}$  in 2017 [9]. This explosive growth has led to the several commercially available inverter topologies, including central, string, and module-level solutions [10–14]. These various architectures can be compared and evaluated in terms of power conversion efficiency, maximum power point tracking (MPPT) efficiency, reliability, and cost.

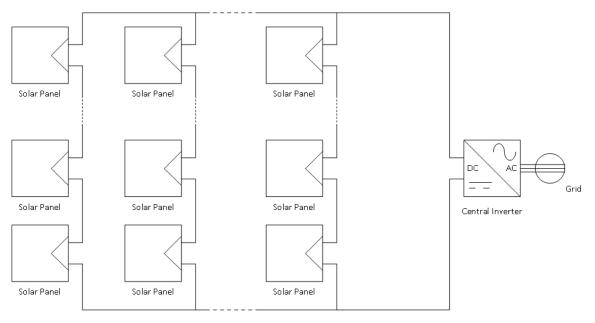

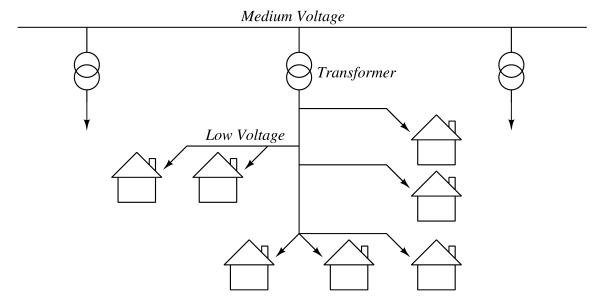

Figure 1.1: A central inverter operating at a plant level by converting power from all strings of solar panels at the grid interface only.

The first converter is a central inverter, an inverter that has multiple strings of solar panels connected together with the direct current (DC) to alternating current (AC) conversion at the grid interface [11] and can be seen in figure 1.1. This is the most common type of solar converter used by electrical utilities and has a power conversion efficiency, as high as 98.5% [15]. Such a system does not contain any type of individual panel MPPT and suffers from a single point of failure design [11] but does have very high reliability by having a minimum amount of electronics for the system. The price for the converter averages €0.05/W or \$0.058/W, the lowest of all converters [15].

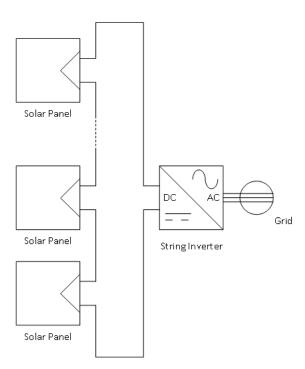

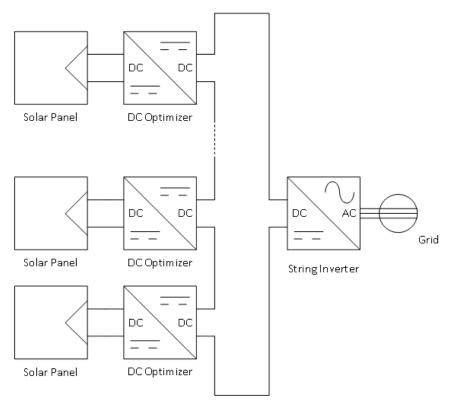

The second converter is a string inverter, an inverter that has a single string of solar panels connected with the DC to AC conversion at the grid interface [11] and can be seen in figure 1.2. This is the second most common type of solar converter used by electrical utilities and has a power conversion efficiency, as high as 98% [15]. Such a system also does not contain any type of individual panel MPPT and instead will sweep for the maximum point in the entire string [11]. The plant does not suffer from a single point of failure due to having a large number of string inverters, but does have reduced reliability by having more power converters in the plant. The price for the converter averages €0.06-0.017/W or \$0.069-0.20/W, the second lowest of all converters [15].

Figure 1.2: A string inverter coverts power from a single string of series connected solar panels.

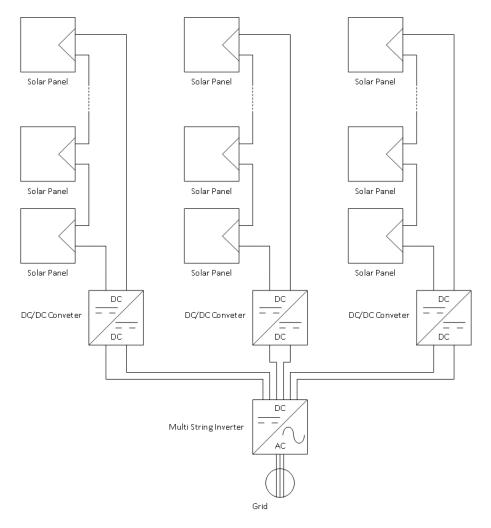

The string inverter family of inverters also include multi-string inverters as seen in figure 1.3. These types of inverters include a DC/DC converter between the string of PV panels and the inverter at the grid interface. This system is designed for three phase connections but the industry is typically references these with the generic name

string inverter.

Figure 1.3: A multi-string inverter consists of two stages of power conversion, a DC/DC converter at each string of series connected solar panels and a DC/AC inverter at the grid interface.

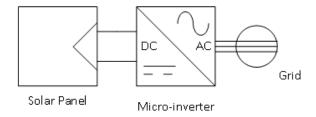

The transition to module level power electronics (MLPEs) brought about the micro inverter, an converter that has a single solar panels connected to the grid by implementing a DC/AC power conversion that boosts the output voltage [11] and can be seen in figure 1.4. This type of solar converter has not had large adoption rate by electrical utilities primarily due to the high cost per watt. The converter has a power conversion efficiency in the range of 90% to 95% [15]. This MPLE converter implements MPPT such that each panel [11]. The plant does not suffer from a single

point of failure due to each panel having its own converter, but such a system has caused the price for the plant level system to increase significantly to approximately €0.28/W or \$0.32/W, the highest of all converters [15].

Figure 1.4: A micro inverter coverts power from a single solar panel directly to the grid.

Figure 1.5: A DC optimizer is DC/DC converter at each solar panel before connecting in a string with a DC/AC inverter at the grid interface such that the maximum power can be obtained from each individual panel.

The newest commercially available MLPE is referred to as a DC optimizer, a DC/DC converter that attaches to each solar panel operating as a low voltage step down converter [11] and can be seen in figure 1.5. This type of solar converter works

in conjunction with the string inverters to obtain MPPT on each indivual panel. The converter has a power conversion efficiency up to 98.8% [15]. This MPLE converter implements MPPT such that each panel [11]. Reliablity depends on whether the DC optimizer can be bypassed in a failure or not but there are concerns with the ease of replacement of the DC optimizer module. The increased electronics in the system does cause the price for the plant level system to increase to approximately  $\leq 0.09$ /W or 0.10/W, but does not include the string converter at the grid interface [15].

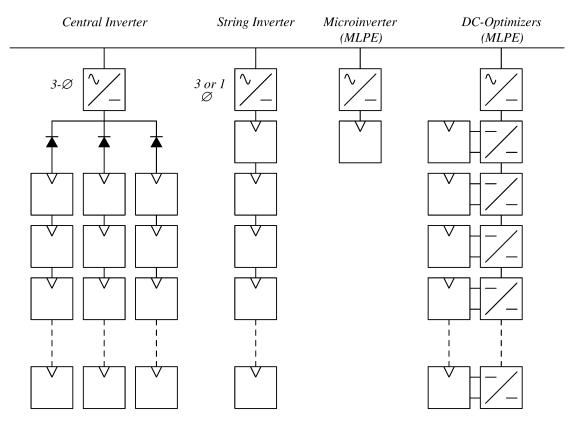

Figure 1.6: Representation of PV inverter topologies (a) The central inverter is characterized by having multiple strings of solar panels connected in parallel at a DC to AC converter with protection diodes to protect against reverse bias conditions. (b) The string inverter is characterized by having only one string of panels attached to a converter enabling it to preform string level maximum power point tracing. (c) The micro-inverter operates at the panel level interfacing each panel to the grid. (d) DC-Optimizers contain panel level converters to tract the maximum power point at each panel while leaving it up to an inverter at the end of the string to interface to the grid.

As a final recap of the PV converters, a major component of any grid-connected PV installation is the DC-to-AC inverter that conditions the DC power provided by the module such that it can be coupled into the AC grid. The two most critical functions of these inverters are to maximize energy harvest and to control the relative phase of the current injected into the grid. Figure 1.6 shows the most common inverter topologies. The least expensive and most common variety is the central inverter, which interfaces multiple strings of series-connected PV modules and can support capacities upwards of several MW. The fact that central inverters use only one power stage to interface so many modules to the grid means that they offer extremely high reliability. By the same token, however, the inverter can only extract the maximum amount of power from the combination of strings connected on its DC-side, meaning that differences between panels resulting from soiling or long-term wear can dramatically reduce the potential energy yield [16,17]. To combat this issue and to increase penetration in the commercial and residential markets, manufacturers have introduced string inverters which are essentially smaller scale central inverters that handle only a few series-connected strings.

#### 1.2 Overview of the SineWatts Architecture

Recently, there has been significant interest in MLPE. With the ability to optimize the power flow from each panel, MLPE solutions offer the highest overall yield [17]. In addition, MLPE solutions provide an opportunity to rapidly shutdown each panel in a rooftop array during fire conditions and thus provide the best means to meet aggressive new requirements for protecting first responders during emergencies [18]. The additional flexibility provided by MLPE does not come without drawbacks in current commercially offered solutions. Most notably, efficiency is lost either because multiple power conversion stages are required or a high step-up ratio is needed [16]. Additionally, MLPE solutions have a higher cost per Watt because of the sheer number of components required in each installation [19]. That said, the cost for such

systems has dropped dramatically, and the leading manufacturers are experiencing as much as 300% annual growth in units shipped [19].

From a technical perspective, MLPE is clearly the best pathway for the PV industry. To optimize efficiency and reduce costs, the research community has explored approaches that allow inverters to be mounted to the back of individual panels so that the inverter outputs can be directly combined before interfacing to the grid. One such approach relies on the cascaded H-Bridge topology, in which individual inverters are connected to the back of individual panels whose AC-side outputs are combined in series [20,21]. Among several drawbacks of this approach is the fact that the operation of each individual inverter must be coordinated by a central controller. Essentially, each inverter must send and receive signals during each switching cycle. It is well known that communication delays can be extremely problematic in distributed control systems with many nodes communicating so frequently [22]. This practical problem has precluded the widespread adoption of such techniques.

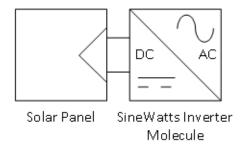

Figure 1.7: The SineWatts inverter molecule attaches individually to the solar panel like the microinverter but does not connect directly to the grid.

SineWatts, Inc. recently patented several new approaches to solve the problems associated with decentralizing of the inverter functionality [23]. Figures 1.7 and 1.8 shows the SineWatts architecture. Note that each module provides a low-voltage AC output waveform synchronized to the grid voltage. As discussed in later sections of this dissertation, this approach allows for significantly lower voltage power semiconductors that can switch at frequencies on the order of several hundred kHz. This

latter fact is important because it implies that component count and size can be reduced so that nearly the entire inverter can be placed on a single silicon die. Key to the SineWatts approach is a simple control scheme that relies only on low-bandwidth signals broadcast over the powerline.

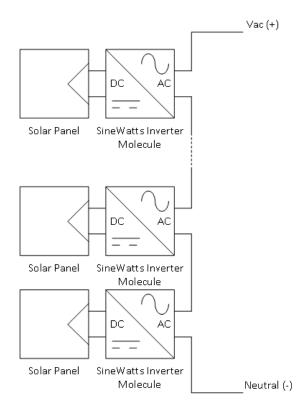

Figure 1.8: The SineWatts inverter molecule outputs an AC voltage that will add together in a string to build up to the grid voltage. This topology is referred to as an AC-stacked inverter system.

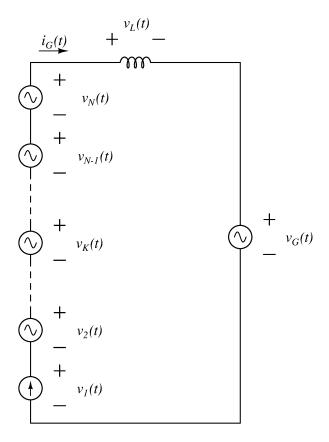

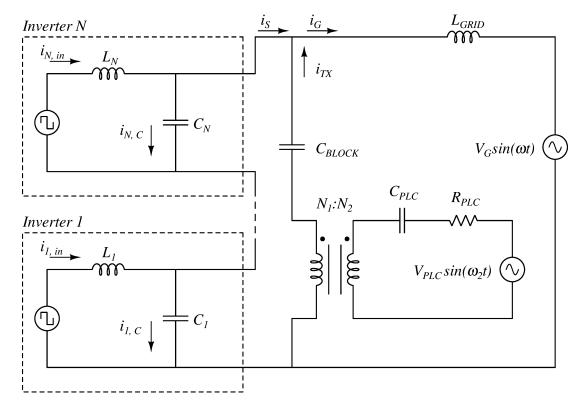

In the SineWatts architecture presented in figure 1.8, each PV module has its own low-voltage inverter. Given that the inverter functionality is distributed to individual panels, each power converter is called an Inverter Molecule<sup>TM</sup>. Although there are multiple ways to instantiate the architecture, figure 1.9 shows the most common approach, with N-1 of the series-connected inverters operating in a voltage-source mode. Assuming a grid voltage of the form  $V_G sin(\omega t)$ , then the peak voltage provided by each voltage-mode molecule (VMM) is approximately  $V_G/N$ . The remaining inverter operates in a current-controlled mode.

Figure 1.9: Steady state model of the SineWatts architecture.

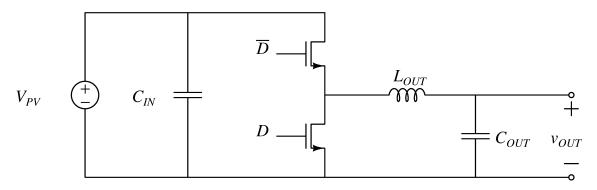

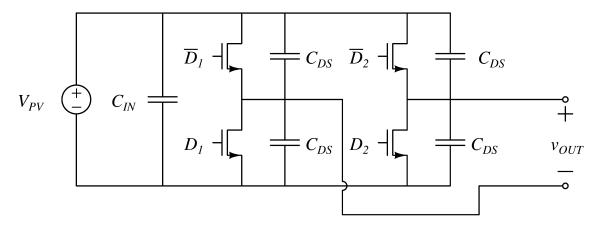

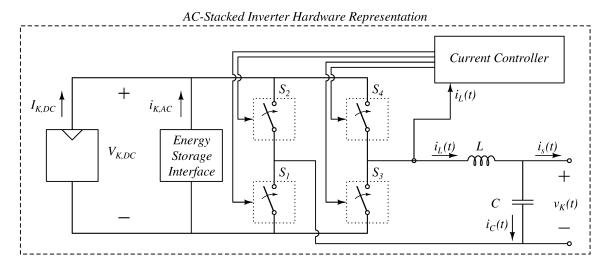

Figure 1.10: Simplified internal structure of the SineWatts Inverter Molecule $^{\mathrm{TM}}$ .

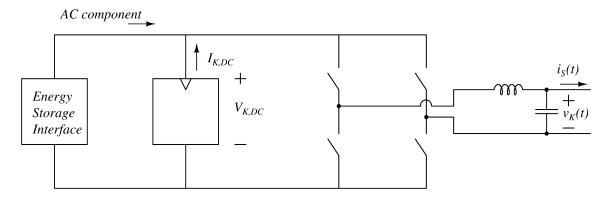

Figure 1.10 shows the simplified internal operation of each molecule. The full-bridge inverter utilizes pulse-width modulation (PWM) to create a sinusoidal waveform at the output of the low-pass filter. Each sinusoid is synchronized to the grid voltage such that the output of the  $k^{th}$  molecule has the form  $v_K(t) = V_K sin(\omega t)$ . Assuming

the AC-side current has the form  $I_G sin(\omega t)$  and ignoring any higher-order switching effects, the AC-side power at the  $k^{th}$  molecule is given in equation 1.1 below.

$$p_K(t) = v_K(t)i_G(t) = \frac{V_K I_G}{2} [1 + \cos(2\omega t)]$$

(1.1)

Since instantaneous power balance requires the power at the DC-side of the full-bridge to match the AC-side output power, a capacitive storage element is added as shown in figure 1.10 to source the AC component in equation 1.1. The average power at the AC side matches the PV input power, and thus in terms of the variables presented in figure 1.10, the average power is described in equation 1.2 below.

$$\langle p_K(t)\rangle = \frac{V_K I_G}{2} = V_{K,DC} I_{K,DC} \tag{1.2}$$

A local controller in each Molecule continuously tracks the maximum power point of its PV module. From the perspective of the N-1 VMMs, the AC-side current is fixed, and thus each controller must vary the amplitude of its output voltage to maintain the module at its maximum power. To do so, it varies the modulation index of the inverter, which is defined in equation 1.3 below [24].

$$m_K = \frac{V_K}{V_{K,DC}} \tag{1.3}$$

Given that that the amplitude of the current is essentially constant from the perspective of each VMM, equation 1.2 in combination with the maximum power point tracking ensures that the steady-state amplitude of the output voltage will always be defined as seen in equation 1.4.

$$V_K = \frac{2V_{K,DC}I_{K,DC}}{I_G} \tag{1.4}$$

If for some reason the steady-state current changes while the environmental conditions on  $k^{th}$  panel do not, the amplitude of the  $k^{th}$  output voltage will thus scale accordingly.

The behavior of the current-controlled molecule, which is known as a current-administrator/voltage compensator (CAVC), is like that of the VMMs except that it controls the AC-side current amplitude to match the maximum power point. Average power balance in the CAVC thus dictates that the AC-side current is related as seen in equation 1.5.

$$I_G = \frac{2V_{K,DC}I_{K,DC}}{V_1} \tag{1.5}$$

Given the operation of the N-1 VMMs, the amplitude  $V_1$  at the CAVC output is fixed in steady-state and its value is given by summing the voltages around the loop in figure 1.9, as seen in equation 1.6.

$$v_1(t) = v_G(t) + v_L(t) - \sum_{K=2}^{N} v_K(t)$$

(1.6)

Note that a change in the voltage from any one of the VMMs will thus reduce  $V_1$  and ultimately force a corresponding change in the current  $I_G$ . Note that appropriate steady-state behavior requires the number of panels to be selected per the given grid voltage. For a typical 60-cell PV module having a maximum power point voltage between 25 and 30V [25], each Molecule will provide approximately 15VAC under steady-state conditions.

While the dynamic operation and start-up characteristics of the SineWatts architecture are outside of the scope of this work, the steady-state analysis presented here is sufficient for describing the requirements of the communications system. Even though control is distributed in the SineWatts architecture, the communications requirement is vastly simplified. Information about the required power flow from each Molecule is communicated through simple circuit constraints set by Kirchhoff's Laws.

In each Molecule one of the two terminal variables is always fixed in steady-state such that other terminal variable can naturally fluctuate as needed to maintain maximum power transfer. During normal operations, the only required communications signal is a broadcast transmission that synchronizes the PWM switching clock in each molecule to the AC grid voltage. This signal must be transmitted approximately once every AC line cycle as opposed to once every switching cycle. This signal must be reasonably free of delay and have minimal error. Furthermore, an effective scheme requires a low-cost implementation.

# 1.3 Importance of Grid Synchronization

The generation of power from a plant into the electrical utility's grid involves the control of the amplitude and phase of the plants current relative to the utilities voltage. This relation specifies the apparent power of the system, including the real and reactive power components and can be seen in equations 1.7 to 1.9 below [26]. When examining the relation of the angle of the current to the angle of the grid voltage, it shows how as the angle difference varies between 0° and 360°, the amount of real power that is supplied to the grid changes changes from its maximum value, to zero, and then eventually to a negative value meaning that power flow has been reversed.

$$S = V_{rms} \angle \theta_v I_{rms} \angle -\theta_i = P + jQ \tag{1.7}$$

$$P = V_{rms}I_{rms}\cos\left(\theta_v - \theta_i\right) \tag{1.8}$$

$$Q = V_{rms}I_{rms}\sin\left(\theta_v - \theta_i\right) \tag{1.9}$$

When generating power to the grid, an impedance must be inserted between the generator and the grid to control the current flow. The difference between the generator and grid voltage is divided by the impedance of the inductor to obtain the current

that flows. Theoretically, as the inductance value is reduced approaching zero, the current magnitudes increase toward infinity. Utilizing this known inductance, the generators voltage can be controlled relative to the grid's voltage and phase to control the current and hence the power generation [27].

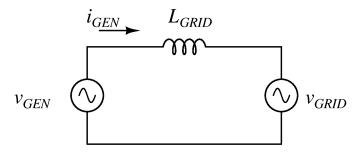

Figure 1.11: Circuit model for a generator injecting current into the grid through an inductance.

Derived from figure 1.11 is the power generation equations of the generator. Below in equations 1.10 to 1.12 are the time domain definitions of the values labeled in figure 1.11. These will be transformed to the steady state equations for the rest of the derivation.

$$v_{qrid} = V_{GRID,PK}\cos(\omega t) \tag{1.10}$$

$$v_{GEN} = V_{GEN,PK} \cos(\omega t + \delta)$$

(1.11)

$$i_{GEN} = I_{GEN,PK} \cos(\omega t + \phi) \tag{1.12}$$

The analysis begins with the Kirchhoff's voltage law (KVL) to get a relation for the current through the inductor.

$$-v_{GEN} + v_{L,GRID} + v_{GRID} = 0 ag{1.13}$$

$$-v_{GEN} + j\omega L_{GRID}i_{GEN} + v_{GRID} = 0 (1.14)$$

$$i_{GEN} = \frac{v_{GEN} - v_{GRID}}{j\omega L_{GRID}} \tag{1.15}$$

Then looking at the apparent power equation, the relation for the inductor current can be substituted in.

$$s_{GRID} = \frac{1}{2} (v_{GRID}) (-i_{GEN})^*$$

(1.16)

$$s_{GRID} = (v_{GRID}) \left( -\frac{v_{GEN} - v_{GRID}}{j\omega L_{GRID}} \right)^*$$

(1.17)

Then substituting in the frequency domain versions of the grid and generator voltage.

$$s_{GRID} = \frac{V_{GRID}}{2} \left( \frac{V_{GRID} - V_{GEN} e^{j\delta}}{j\omega L_{GRID}} \right)^* \tag{1.18}$$

$$s_{GRID} = \frac{V_{GRID}}{2} \left( j \frac{V_{GRID} - V_{GEN} e^{j\delta}}{j^2 \omega L_{GRID}} \right)^* \tag{1.19}$$

$$s_{GRID} = \frac{V_{GRID}}{2} \left( \frac{jV_{GRID} - jV_{GEN}e^{j\delta}}{-\omega L_{GRID}} \right)^* \tag{1.20}$$

The derivation continues by rearranging the equation to get rid of the conjugate.

$$s_{GRID} = \frac{V_{GRID}}{2} \left( \frac{jV_{GEN}e^{j\delta}}{\omega L_{GRID}} - \frac{jV_{GRID}}{\omega L_{GRID}} \right)^* \tag{1.21}$$

$$s_{GRID} = \frac{V_{GRID}}{2} \left[ \left( \frac{jV_{GEN}e^{j\delta}}{\omega L_{GRID}} \right)^* - \left( \frac{jV_{GRID}}{\omega L_{GRID}} \right)^* \right]$$

(1.22)

$$s_{GRID} = \frac{V_{GRID}}{2} \left[ \frac{-jV_{GEN}e^{-j\delta}}{\omega L_{GRID}} + \frac{jV_{GRID}}{\omega L_{GRID}} \right]$$

(1.23)

Finally, applying Euler's formula to transform the exponential into sin and cosfunctions can the apparent power formula be completed.

$$s_{GRID} = \frac{j \left( V_{GRID} \right)^2}{2\omega L_{GRID}} - \frac{j V_{GRID} V_{GEN} \left[ \cos \left( -\delta \right) - j \sin \left( -\delta \right) \right]}{2\omega L_{GRID}}$$

(1.24)

$$s_{GRID} = \frac{j \left( V_{GRID} \right)^2}{2\omega L_{GRID}} - \frac{V_{GRID} V_{GEN} \sin\left(\delta\right)}{2\omega L_{GRID}} - \frac{j V_{GRID} V_{GEN} \cos\left(\delta\right)}{2\omega L_{GRID}}$$

(1.25)

The real and reactive power can then be split from the apparent power equation.

$$s_{GRID} = P_{GRID} + jQ_{GRID} (1.26)$$

$$P_{GRID} = -\frac{V_{GRID}V_{GEN}}{2X_{LGRID}}\sin(\delta)$$

(1.27)

$$Q_{GRID} = \frac{(V_{GRID})^2}{2X_{L,GRID}} - \frac{V_{GRID}V_{GEN}}{2X_{L,GRID}}\cos(\delta)$$

(1.28)

From the final equations derived, the phase difference of the string voltage has a direct relationship to the power generated into the grid. This means that for a set power harvested from the solar panels in the AC-stacked architecture, the phase of the generated voltage must be maintained. Hence, the inverters must be synchronized to the grid.

### 1.4 Comparison of Synchronization Methodologies

Synchronization in remote connected power electronics is essential for proper operation as shown in the previous section. This notion is true for all modular architectures that have AC output with various examples as:

- Modular multilevel converters

- Cascaded H Bridges

- AC stacked converters

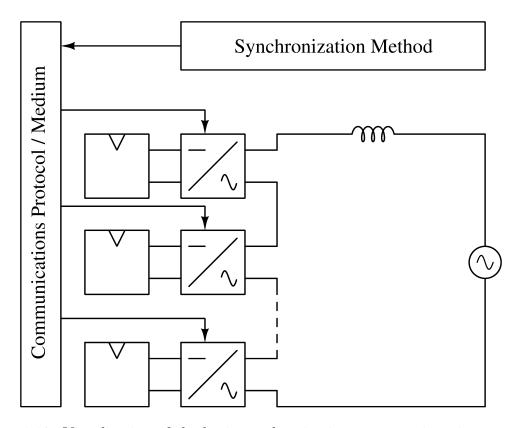

The basic structure of the synchronization is having a central unit coordinate the synchronization time and then use a communication protocol and medium to communicate the synchronization to the other power electronic modules. This concept is visualized in figure 1.12. The communications protocol and hence the medium can be selected as appropriate for the requirements. The two fundamental mediums of communication are wired and wireless communication where each has a wide range of protocols.

Figure 1.12: Visualization of the basic synchronization structure is series connected architectures. A synchronization method is provided by a central unit that communicates this information to the remote power electronics in the system through a selected protocol and medium. Shown is the AC-stacked inverter architecture but the concept is the same for all series connected power electronic modules.

Synchronization can be provided in several different protocols such as controller area network (CAN) and serial peripheral interface (SPI) for a wired medium or "Advanced and Adaptive Network Technology" (ANT) for a wireless medium. In the AC-stacked architecture, one needs to synchronize only at the line frequency, which greatly simplifies the synchronization process. This was shown in the architecture introduction earlier in the chapter. Utilizing this information, several examples of synchronization is found.

One CAN example shows a modular multilevel inverter being used for wind power generation in which the modules are synchronized at the switching frequency [28]. The individual inverters switching frequency is 333 Hz with a sampling frequency of

16 kHz. The CAN bus sends the synchronization signal such that the variance in synchronization is  $\pm 25\,\mu s$  allowing for power operation of the system with minimal impact. In comparison with the AC-stacked inverter architecture, the synchronization frequency is higher and the variance between converters is appropriate for grid synchronization.

Another CAN protocol example shows the PWM synchronization in a cascaded H-bridge multilevel inverter where the wired medium is a fiber optic communication link [29]. The optical communication allows for the communication to occur with the reference voltage of each inverter at a different operating level. The system is a 1400 kW induction motor drive operating at 6600 V. The reported time difference in synchronization between two modules, hence the variance, is  $83 \,\mu s$ . This is a higher variance than the first reported CAN example [28], but is still very low compared to the grid frequency in an AC-stacked inverter architecture.

There is a reported cascaded multilevel inverter with H-bridge implementation that synchronizes with an SPI protocol while using conventional wiring with optoisolators [30]. The SPI protocol is utilized in synchronizing a 4 kHz PWM reference signal for synchronization as well as the three phase line voltages. The allowable error in the system is 5% which for 4 kHz is  $12.5 \,\mu s$ . This is comparable to the CAN latency [28].

Besides the reported use of fiber optics for the reference voltage difference of the modular inverters [29], often communications signals are provided via fiber optic cables to avoid problems from EMI [30]. EMI on wired media utilizing electrical signals are not only avoided by utilizing light in fiber optics cables but also by the use of wireless communication medium. There has been development of a synchronous medium access approach via wireless, known as the ANT protocol, to synchronize wireless sensors [31]. Reported using this protocol is a method of ranging wireless sensors based on the latency between the wireless synchronization and the latency of a sound through air from the transmitter to receiver when transmitted at the same

time. This is possible due to the variance of the wireless modules having a variance of  $3 \mu s$ . Such variance is lower than the wired mediums [28,29] and would be appropriate for use in the modular multilevel converters or AC-stacked inverter architecture.

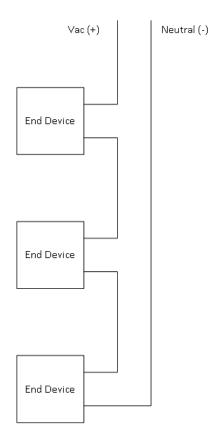

### 1.5 Conceptual Overview of Grid Synchronization Through the Power Line

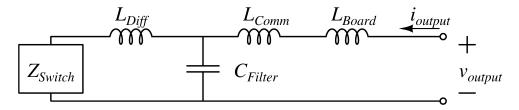

The AC-stacked inverter architecture still utilizes an interface when connecting to the electrical utilities. This interface does not contain any power conversion hardware since the power is already conditioned by the solar inverters at the panels. Instead, the grid interface contains an electronic relay and an interface inductor enabling a higher system efficiency than the DC-optimizers as there is no power conversion. Figure 1.13 shows a representation of this grid interface. Besides the interface hardware, the grid interface contains a number of sensors to measure both the grid and string voltage and current values. The measurements from these sensors allow the grid interface to provide proper protection for the AC-stacked inverter architecture. There is anti-islanding, under and over voltage protection, over current protection, and other fault protection built in [32–34].

Figure 1.13: The grid connection of the AC-stacked inverters connects to the grid through a system, referred to as the termination box, consisting of a controlled electronic relay, AC filter, measurement circuitry and communication framework.

This grid interface provides all the hardware necessary for the measurement of the grid zero crossing and provides a connection point to the powerline of the string of AC-stacked inverters. The grid interface can add communication hardware to the string connection point without impacting any functional operation of the grid interface. The general idea of communicating the zero cross information of the grid is to for this communication hardware to send a pulse to represent the positive zero grid crossing. The receiver board then detects this pulse and sends it to the controller on the inverter hardware such that it then has the timing to synchronize to the grid voltage. The actual implementation details will be shown later in this dissertation.

#### 1.6 Research Contribution

Previously reported results for the AC-stacked inverter architecture employed the use of a digital signal between the grid interface and the AC-stacked inverter modules with the use of an optoisolator for coupling between the different voltage references [32, 34–37]. This wiring does not allow the power electronic modules to be practically implemented in a commercial solution as the excessive wiring to each and every MLPE. The development of successful prototype depends on finding a new means of communicating the zero cross information to the individual inverters without requiring a change in infrastructure to existing installation methods and can operate in a reliable manner without being subject to outside interference. The current-mode powerline communications developed in this research does just that.

This research also advances the development of powerline communications in a new direction of current-based powerline communications and then uses this advancement to enable a completely decentralized AC-stacked inverter operation. No such commercial solution for a current-mode powerline communications exists which made the development quite difficult. This research shows how a current-mode powerline communications can still propagate down the communications line even though the series connected power electronics separate the wiring into sections in the system. This is

done by utilizing the series connected power electronics as a physical medium for PLC communications.

### 1.7 Organization of Dissertation

Chapter 2 conducts a literature review of current PLC commercially offered solutions and their relation to the current-mode PLC developed. This chapter also defines the specifications used in the design of the low latency grid synchronization signal. Chapter 3 shows the theoretical and physical implementation of the physical access layer. Empirical results are compared to the theoretical for the physical access layer before any channel modeling is performed. Chapter 4 then develops the channel model from transmitter to receiver whereby the current-mode PLC is utilizing series connected power electronic modules as a transmission medium. The chapter includes a relation for the string and grid connections in the development of the channel model. Chapter 5 examines the noise characteristics in the communication channel model as well as the hardware requirements for a signal to noise ratio (SNR). Chapter 6 presents the runtime results of the AC-stacked inverter architecture utilized by SineWatts whereby the current-mode PLC is utilized for grid synchronization. Results for the system include a six month field deployment in Birmingham, Alabama. Chapter 7 concludes the dissertation with suggestions for further work on expanding the current-mode PLC communications.

### CHAPTER 2: LITERATURE REVIEW

Power line communications market has greatly expanded in recent years to a market capital of \$5.47 billion dollars in 2017 with an estimated \$9.43 billion dollars in 2018 [38]. Two specific areas addressed are broadband communications mainly targeted for residential customers looking to provide network capabilities inside buildings utilizing existing electrical wiring instead of installing new network cabling, and secondly narrowband communications utilized by electrical utilities to reduce communication costs and while providing long range communications solution utilizing the existing grid wiring [39]. The narrowband communications has been largely implemented by protocols such as G3-PLC and PRIME and with the regulatory bodies of the FCC in the United States and CENELEC in Europe overseeing the frequency bands availability and restrictions [39].

Even with such a large and expanding market, power line communications has not adapted to a current-mode communications means for the physical layer but instead has relied on the traditional voltage mode communications for the parallel connections found in traditional wiring. As continuous efficiency improvements in electronics has occurred, new system architectures have been explored as means of reducing converter losses in systems by utilizing a series connection of power electronics to avoid multiple power loss conversion stages. This emerging market currently consists of DC-optimizers [40, 41], stacked H-bridges [10, 42], and AC-stacked inverter architecture [23, 35–37, 43–48] in the solar market alone. Other industries are experiencing a paradigm shifts in the way to optimize power conversion for total system efficiency as well. Currently, the server industry is also looking at the use of series connected server architecture in which each server in a rack operates at ratio of the DC bus power to

the server rack to the number of servers in the rack with load balancing techniques and auxiliary power converters for load balancing when needed [49]. Other architectures based on the differential power processors may as well be utilized as a communication medium for a current based PLC communications [50,51].

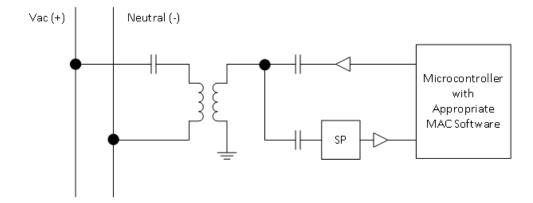

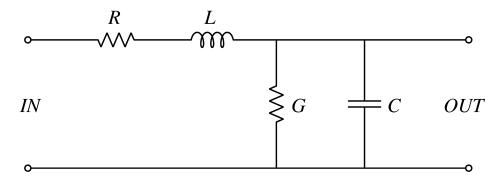

### 2.1 Overview of Power Line Carrier Communications

Available power line carrier communications for narrowband communication has many reference designs from various companies. Observed here is one from Texas Instruments [52] but others follow a similar design. This system is portrayed in figure 2.1. The communications utilize a unified transmitter and receiver design with grid interface by means of an isolation transformer. This isolation transformer typically includes several blocking capacitors to make sure low frequency voltage does not cause large currents through the transformer. The transmitter has the carrier and modulation generated by a microcontroller following one of the communication protocols. The transmitter then buffers the voltage signal by means of a line driver. This line driver ensures the transmitter can maintain the output signal despite loading conditions by providing large amounts of current. The signal propagates into the secondary of the isolation transformer and out of the primary into the line. The receiver obtains its signal from the isolation transformer as any signal on the line propagates through the primary and out of the secondary. The signal then passes

Figure 2.1: Typical PLC communications receiver and transmitter circuitry.

Figure 2.2: Typical PLC communications configuration where all devices are connected in parallel across the grid.

through some filtering blocks to remove noise and is amplified if needed. The same microcontroller used for the transmitter then samples the received signal and demodulates the signal and recovers the transmitted information.

The devices connected to the grid all have the same line and neutral connection. They see the same voltage. At a basic approximation, the receiving devices see the same voltage signal that is transmitted out one. This approximation is made by assuming an ideal conductor such that the devices are in parallel as seen in figure 2.2 and hence the voltage on the line is constant across all devices. Such an approximation though does not represent a real system but does display the justification for using voltage for the signal [53].

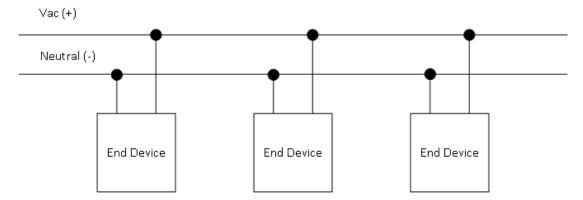

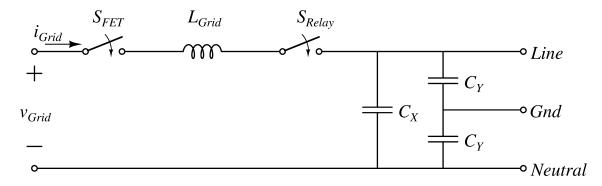

# 2.2 Power Line Carrier Communications Through Series Connected Switched Mode Converters Used in Solar Converters

The connection for modular power electronic converters is a series connection, not the parallel connection for the typical power line communication devices. Such a system is portrayed in figure 2.3 for comparison. For the series connection, a voltage based signal originating at the line and neutral connection would be reduced based on the number of devices in the series connection. A voltage based signal is not ideal then for a PLC communications scheme in series connected devices. Utilizing the analysis from chapter 1 for the AC-stacked inverter architecture, it has been shown that the current through the devices is the same such that decentralized control. Since the current will be the same through the devices, why not use that current for communications as well? The development of this current-mode PLC communications and the application of this developed communications for synchronization in the AC-stacked inverter architecture is the focus of this dissertation and will presented in later chapters.

Figure 2.3: PLC communications setup in series representing the communication modules on each switched mode power converter in the string.

### 2.3 Specifications of Grid Synchronization Through a Power Line Carrier

Any communications scheme designed to synchronize the operation of the previously descried AC-stacked inverter module, must meet the following general specifications:

- The same signal must be broadcast to each AC-stacked inverter module.

- There must be minimal delay between the transmission and the reception at each AC-stacked inverter module.

- There must be minimal variance of the received signal at different AC-stacked inverter modules.

- The error rate should be a minimal.

These general specifications of delay and variance must have some type of ceiling though for reliable system operation even though the further reduced these become, the better it would be for the system. To quantify the ceiling, the power factor (PF) and the grid protection response time must be explored.

The desired power factor of the AC-stacked inverter architecture operating at peak power is  $PF \geq 0.98$ . This value means that the zero crossing of the current may be within  $\pm 333 \mu s$ . Since the grid interface will be measuring the zero crossing and then transmitting once the crossing is detected, this maximum delay is specified as the delay from the grid zero crossing to the reception at the AC-stacked inverter's controller. The variance is specified as being 10% of this value or  $\pm 33.3 \mu s$ .

# CHAPTER 3: IMPLEMENTATION OF THE PHYSICAL ACCESS LAYER FOR THE RECEIVER AND TRANSMITTER WITH SIMULATED AND EMPIRICAL RESULTS

### 3.1 Design and Simulation of the Physical Access Layer

The first layer of a communication system in the open systems interconnection (OSI) model is the physical layer with specifies the transmitter, receiver, encoding techniques, and data rates. The physical layer here will be modeled for a simplex communication system in which the grid interface is transmitting the zero crossing information of the grid. One way to meet these goals is to transmit a current that contains information about the phase of the grid voltage as described in chapter 2. To transmit a current to each molecule, a transmitter circuit is connected at the grid interface.

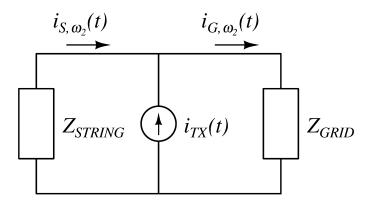

This transmitter is transformer-coupled into the AC line. One can analyze the steady-state behavior of this circuit using superposition. Assuming the communications frequency  $\omega_2$  is not equal to the line frequency  $\omega$ , then the string current,  $i_s(t)$ , and the grid current,  $i_g(t)$ , are

$$i_s(t) = i_{s,\omega}(t) + i_{s,\omega_2}(t)$$

(3.1)

$$i_g(t) = i_{g,\omega}(t) + i_{g,\omega_2}(t)$$

(3.2)

where the subscripts  $\omega$  and  $\omega_2$  indicate the line and communication components at the two different frequencies. At line frequency, the communications current source can conceptually be shorted such that no line-frequency current flows into the transmitter. The line-frequency components of the gird and string currents are thus equal as

expressed in equation 3.3 below.

$$i_{s,\omega}(t) = i_{g,\omega}(t) \tag{3.3}$$

At the communications frequency, the analysis leaves the communications current source and the impedances of the string and grid. Figure 3.1 shows one way to represent the resulting circuit. By Kirchhoff's current law (KCL), we note that relation expressed in equation 3.4.

$$i_{s,\omega_2}(t) + i_{TX} = i_{q,\omega_2}(t)$$

(3.4)

Figure 3.1: Preliminary modeling of the impedance seen by the PLC current injection by applying superposition to analyzed only the transmitted current.

To minimize power dissipation and any grid-side interference issues, we desire to have  $i_{TX} = -i_{S,\omega_2}$ . To ensure this, we must have  $Z_{GRID} >> Z_{STRING}$  at  $\omega_2$ . Each inverter module is designed to have the same output filter components and thus the impedance of each module at  $\omega_2$  is estimated as seen in equation 3.5 below. This will be assumed for the rest of the communication physical layer design and then analyzed later in the channel model of chapter 4.

$$Z_K = j\omega_2 L_{OUT} || -j/(\omega_2 C_{OUT})$$

(3.5)

The overall string impedance is thus estimated quickly as  $Z_{STRING} = NZ_K$  where

N is the number of inverter modules in the string. During the inverter design, the frequency  $\omega_2$  and the components  $L_{OUT}$  and  $C_{OUT}$  are selected appropriately. Given the requirements of the power stage, the values are approximately  $5\mu H$  and  $10\mu F$ , respectively. Selecting the communications frequency to be at least 100 kHz thus assures that one is in a range where  $C_{OUT}$  dominates the assumed string impedance. Literature on classic, voltage-based powerline-carrier communications indicates that grid impedances in this frequency range are at least an order of magnitude higher than that of the series combination of  $10\mu F$  capacitors [53,54] As a result,  $i_{G,\omega_2}=0$ . Note, this is only an estimate for the start of the physical layer design, the actual analysis is found in chapter 4.

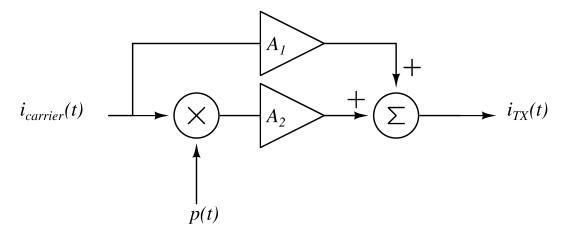

Figure 3.2: Simplified block diagram of the modulation technique for the PLC communications.

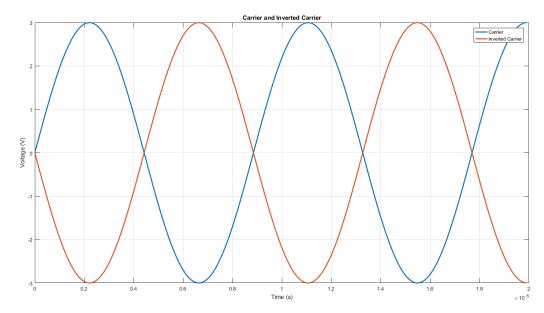

The transmitter design scheme is shown in figure 3.2. The carrier signal is a sinusoidal waveform with the frequency selected of 113 kHz. The carrier signal will be added to itself such that part of the carrier is available for the receivers phase locked loop (PLL) will be able to stay locked. The modulation occurs, the inverse of the carrier signal is added to the carrier and the summation of the two will be transmitted. The ideal carrier signal and its inverse is seen in figure 3.3. The gains applied in the transmitter simulation are  $A_1 = 1$  and  $A_2 = 0.7$ .

Figure 3.3: Ideal carrier waveform used for the PLC and the inverted carrier utilized for the phase shift keying.

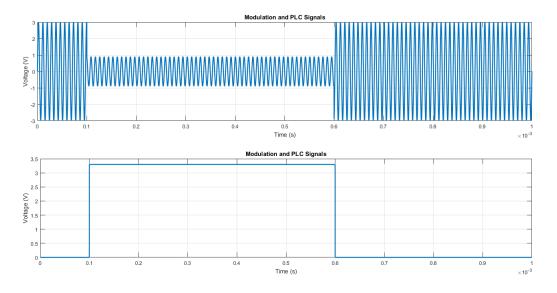

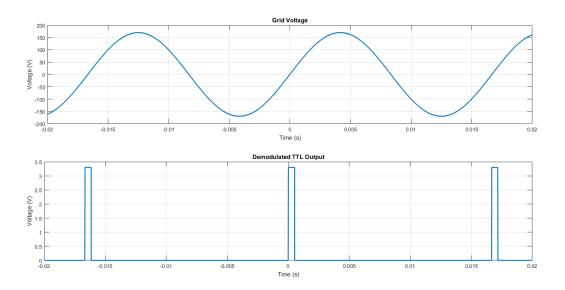

To indicate the phase of the grid voltage, a system connected at the grid interface locates zero crossings. Specifically, a digital filtering algorithm in the microcontroller at the grid interface [11] generates a short pulse every time the grid voltage crosses from negative to positive. Figure 3.4 shows this process.

Figure 3.4: Simulation of the BPSK modulation of the PLC.

Note that the synchronization pulse changes state for a brief time  $\Delta$  at the beginning of each line cycle. This signal is thus modeled as equation 3.6.

$$p(t) = \begin{cases} 1, & nT < t < n(T\Delta) \\ -1, & \text{otherwise} \end{cases}$$

(3.6)

where T is the period of the line voltage and n is an integer. The pulse train p(t) is then transmitted to the inverters using binary phase shift keying (BPSK) to yield a transmitted current of the form in equation 3.7 [55]. The final simulation of the transmitter with three BPSK modulations from the grid zero crossing is shown in figure 3.5. The simulations are carried out with voltage values and is expected to be implemented with an integrated circuit (IC) that converts the system voltages to a current.

$$i_{TX}(t) = I_1 p(t) \cos(\omega_s t) + I_2 \cos(\omega_s t)$$

(3.7)

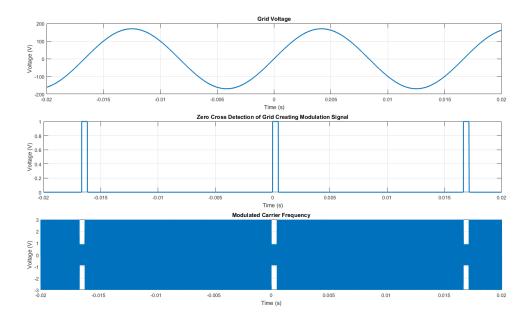

Figure 3.5: Grid zero cross detection scheme. The negative to positive zero crossing is of the grid, top plot, is detected and forms a modulation signal, middle plot, which is used to modulate the carrier frequency creating a BPSK signal for synchronization.

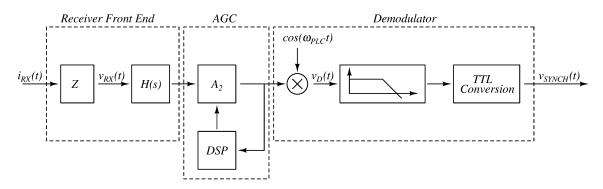

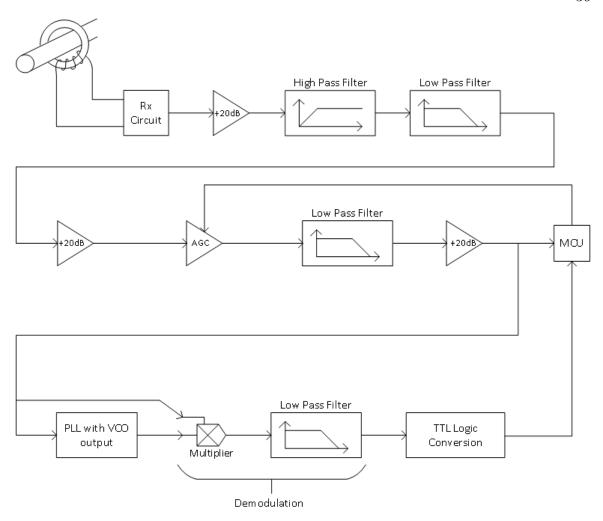

Figure 3.6 shows the block diagram of the prototype system designed and implemented to meet the specifications provided in the previous section. This prototype has three major subsystems, namely the front end, the demodulator, and the automatic gain controller (AGC).

Figure 3.6: Block diagram of the physical receiver layer.

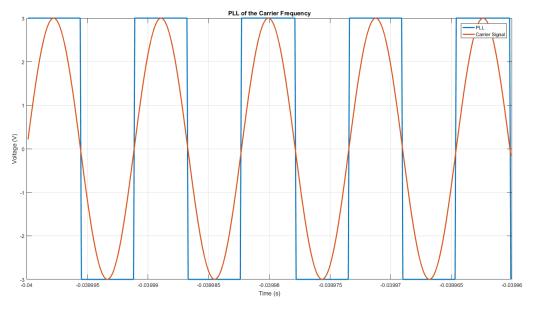

Figure 3.7: Simulation of the PLL for the demodulation circuit to detect the carrier frequency.

For the purpose of designing the demodulation scheme, on the demodulator is simulated. The PLL block is implemented by locking a square wave to the carrier frequency detected by the receiver as seen in figure 3.7. This square wave multiplication is the same as depicted in the block diagram since the square wave contains

a fundamental sinusoid of the same frequency of the carrier, but also includes higher order harmonics of the carrier frequency. This is seen by the trigonometric Fourier series of the square wave as seen in equation 3.8 where  $V_{PLL}$  is the peak voltage [56].

$$v_{PLL}(t) = V_{PLL} \frac{4}{\pi} \left( \cos(\omega_2 t) - \frac{1}{3} \cos(3\omega_2 t) + \frac{1}{5} \cos(5\omega_2 t) - \frac{1}{7} \cos(7\omega_2 t) + \dots \right)$$

(3.8)

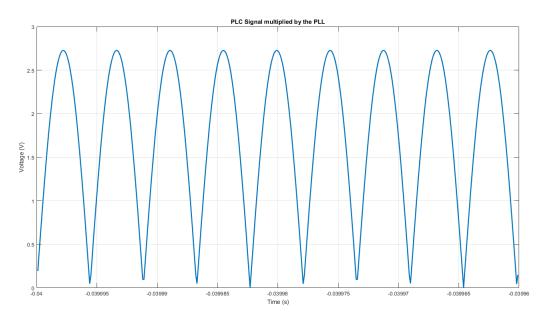

Figure 3.8: Simulation of the ideal demodulation before filtering.

The resulting multiplication of the received carrier without any BPSK modulation is shown in figure 3.8. This waveform can visually be seen to be the scaled absolute value of the carrier signal. Equation 3.9 describes this mathematically.

$$v_D(t) = V_{PLL} \left| v_{in}(t) \right| \tag{3.9}$$

Even though the expression as the absolute value is simplistic, it does not allow for the mathematical analysis of the low pass filter following the multiplication. To see this analysis, the multiplication must be rewritten as in equation 3.10 and then transformed by the sum to product identity as seen in equation 3.12 [57].

$$v_D(t) = V_{in}\cos(\omega_2 t)V_{PLL}\frac{4}{\pi}\left(\cos(\omega_2 t) - \frac{1}{3}\cos(3\omega_2 t) + ...\right)$$

(3.10)

$$v_D(t) = \frac{4V_{in}V_{PLL}}{\pi} \left( \cos(\omega_2 t) \cos(\omega_2 t) - \frac{1}{3}\cos(\omega_2 t) \cos(3\omega_2 t) + \dots \right)$$

(3.11)

$$v_D(t) = \frac{2V_{in}V_{PLL}}{\pi} \left( 1 + \cos(2\omega_2 t) - \frac{1}{3}\cos(2\omega_2 t) - \frac{1}{3}\cos(4\omega_2 t) + \dots \right)$$

(3.12)

Modifying the values in the product to sum transformation of equation 3.12 to terms of the of the received current transmitter, the final equation is expressed in equation 3.13.

$$v_D = ZA_2 \left[ \frac{I_1}{2} p(t) + \frac{I_1}{2} p(t) \cos(2\omega_S t) + \frac{I_2}{2} + \frac{I_2}{2} \cos(2\omega_S t) \right]$$

(3.13)

Figure 3.9: Simulation of the ideal demodulation after filtering.

Sizing the low pass filter such that the DC component of the output is allowed but the higher frequencies are attenuated will leave the necessary component to recover the BPSK modulation. The low pass filter is designed with a low pass cut off frequency of approximately 16 kHz. The result of the low pass filter while functioning as the demodulator is seen in figure 3.9.

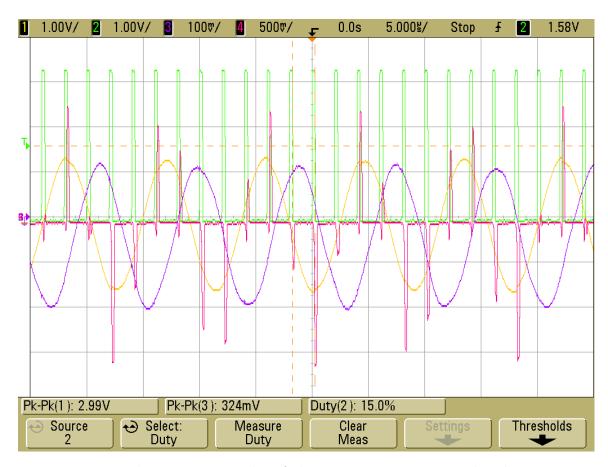

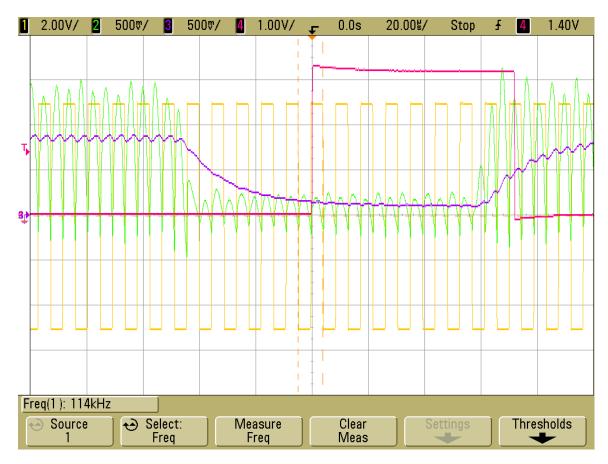

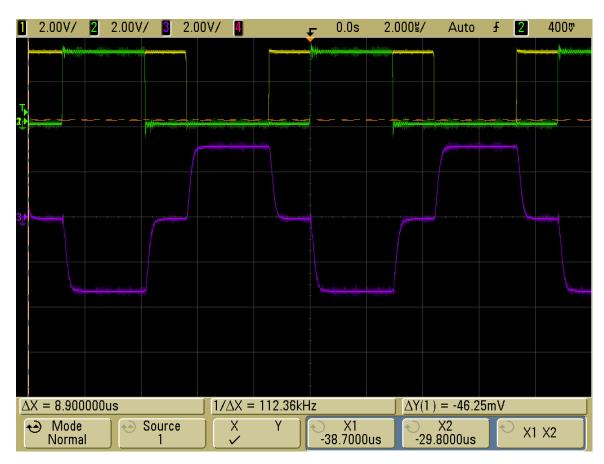

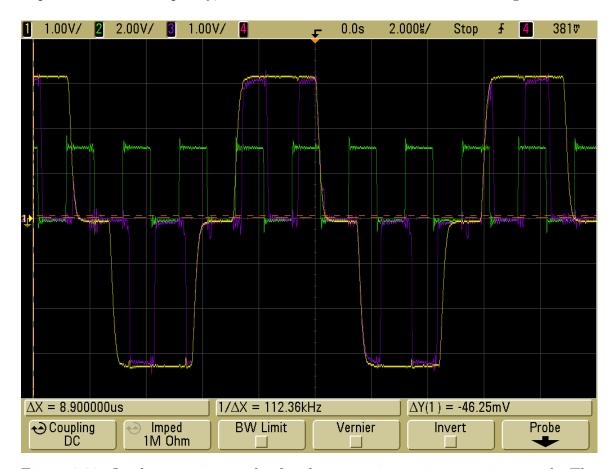

The final step in the demodulation process is the determination of the bit output of the filter output. This deterministic selector is simulated using a Schmitt trigger where the signal level has to drop below the determined value before the output bit is toggled, and then rise above a higher value before resetting the output bit. This keeps the output from possibly bouncing if the signal approaches the threshold values. The final output of the simulation showing the resulting demodulation is shown in figure 3.10.