# AN EFFICIENT DESIGN SPACE EXPLORATION FRAMEWORK TO OPTIMIZE POWER-EFFICIENT HETEROGENEOUS MANY-CORE MULTI-THREADING EMBEDDED PROCESSOR ARCHITECTURES

by

#### **Kushal Datta**

A dissertation submitted to the faculty of the University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree Of Doctor of Philosophy In Electrical and Computer Engineering

Charlotte

2011

| Approved by:          |

|-----------------------|

| Dr. Arindam Mukherjee |

| Dr. Arun Ravindran    |

| Dr. Bharat S. Joshi   |

| Dr. Kazemi Mohammed   |

© 2011 Kushal Datta ALL RIGHTS RESERVED

#### **ABSTRACT**

KUSHAL DATTA. An efficient design space exploration framework to optimize power-efficient heterogeneous many-core multi-threading embedded processor architectures. (Under the direction of DR. ARINDAM MUKHERJEE)

By the middle of this decade, uniprocessor architecture performance had hit a roadblock due to a combination of factors, such as excessive power dissipation due to high operating frequencies, growing memory access latencies, diminishing returns on deeper instruction pipelines, and a saturation of available instruction level parallelism in applications. An attractive and viable alternative embraced by all the processor vendors was multi-core architectures where throughput is improved by using micro-architectural features such as multiple processor cores, interconnects and low latency shared caches integrated on a single chip. The individual cores are often simpler than uniprocessor counterparts, use hardware multi-threading to exploit thread-level parallelism and latency hiding and typically achieve better performance-power figures. The overwhelming success of the multi-core microprocessors in both high performance and embedded computing platforms motivated chip architects to dramatically scale the multi-core processors to many-cores which will include hundreds of cores on-chip to further improve throughput. With such complex large scale architectures however, several key design issues need to be addressed. First, a wide range of microarchitectural parameters such as L1 caches, load/store queues, shared cache structures and interconnection topologies and non-linear interactions between them define a vast non-linear multi-variate micro-architectural design space of many-core processors; the traditional method of using extensive in-loop

simulation to explore the design space is simply not practical. Second, to accurately evaluate the performance (measured in terms of cycles per instruction (CPI)) of a candidate design, the contention at the shared cache must be accounted in addition to cycle-by-cycle behavior of the large number of cores which superlinearly increases the number of simulation cycles per iteration of the design exploration. Third, single thread performance does not scale linearly with number of hardware threads per core and number of cores due to memory wall effect. This means that at every step of the design process designers must ensure that single thread performance is not unacceptably slowed down while increasing overall throughput. While all these factors affect design decisions in both high performance and embedded many-core processors, the design of embedded processors required for complex embedded applications such as networking, smart power grids, battlefield decision-making, consumer electronics and biomedical devices to name a few, is fundamentally different from its high performance counterpart because of the need to consider (i) low power and (ii) real-time operations. This implies the design objective for embedded many-core processors cannot be to simply maximize performance, but improve it in such a way that overall power dissipation is minimized and all real-time constraints are met. This necessitates additional power estimation models right at the design stage to accurately measure the cost and reliability of all the candidate designs during the exploration phase.

In this dissertation, a statistical machine learning (SML) based design exploration framework is presented which employs an execution-driven cycle-

accurate simulator to accurately measure power and performance of embedded many-core processors. The embedded many-core processor domain is *Network* Processors (NePs) used to processed network IP packets. Future generation NePs required to operate at terabits per second network speeds captures all the aspects of a complex embedded application consisting of shared data structures, large volume of compute-intensive and data-intensive real-time bound tasks and a high level of task (packet) level parallelism. Statistical machine learning (SML) is used to efficiently model performance and power of candidate designs in terms of wide ranges of micro-architectural parameters. The method inherently minimizes number of in-loop simulations in the exploration framework and also efficiently captures the non-linear interactions between the micro-architectural design parameters. To ensure scalability, the design space is partitioned into (i) core-level micro-architectural parameters to optimize single core architectures subject to the real-time constraints and (ii) shared memory level microarchitectural parameters to explore the shared interconnection network and shared cache memory architectures and achieves overall optimality. The cost function of our exploration algorithm is the total power dissipation which is minimized, subject to the constraints of real-time throughput (as determined from the terabit optical network router line-speed) required in IP packet processing embedded application.

#### **ACKNOWEDGMENTS**

First of all, I thank my parents Mr. Kalyan Kumar Datta and Mrs. Tamali Datta for providing me love, strength, support, inspiration, knowledge, wisdom and independence. I feel an endless sense of pride and emotion as I acknowledge and appreciate their contribution in my life. I feel equally blessed to have my elder sister Mrs. Kabita (Datta) Hazra and her beloved husband Mr. Susovan Hazra and thank them from the bottom of my heart for providing me support and friendship all throughout my life no matter how dire the situation. I also would like to thank my late grandmother Mrs. Kamala Datta and her sister-in-law Mrs. Bimala Bala Datta for being such a big part of my life during my adolescent years — loving me endlessly and teaching me to confront every adversity with pride, faith and love. I also thank my late uncle Mr. Kuber Datta for teaching me to be enthusiastic and full of life and freedom.

I would like to thank the rest of my family, all my cousin brothers and sisters, especially Kaushik Dutta and my dear friends Jong-ho Byun, Aby Kuruvilla and Rewa S. Tikekar, who have been there through my toughest times and knocked sense into me every now and then.

I would especially like to thank my advisor Dr. Mukherjee for being my friend, philosopher and guide. He will always be a source of inspiration to me. I also thank my committee members, Dr. Arun Ravindran and Dr. Bharat S. Joshi for their continuous support, for reviewing my work and providing me with useful feedback.

### TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                                      | 1  |

|--------------------------------------------------------------|----|

| 1.1 Embedded Many-core Processors                            | 1  |

| 1.2 Demands of High Performance Packet Processing Routers    | 2  |

| 1.3 Micro-architectural Domain of Network Processors         | 4  |

| 1.4 Dissertation Contribution                                | 5  |

| CHAPTER 2: BACKGROUND                                        | 10 |

| 2.1 Processor Simulators                                     | 10 |

| 2.2 Multi- and Many-core Design Space Exploration            | 14 |

| 2.3 Statistical Machine Learning for System Optimization     | 17 |

| CHAPTER 3: EMBEDDED NETWORK PROCESSING BENCHMARK (ENEPBENCH) | 19 |

| CHAPTER 4: CASPER PROCESSOR SIMULATOR                        | 25 |

| 4.1 Processor Model                                          | 26 |

| 4.2 Performance Measurement                                  | 30 |

| 4.3 Verification                                             | 31 |

| 4.4 Deep Chip Vision – Area and Power/Energy Measurement     | 33 |

| 4.5 Design of HDL Models                                     | 33 |

| 4.5.1 Area and Power Estimation                              | 34 |

| 4.5.2 Modeling Activity Factor                               | 39 |

| 4.5.3 Design Trade-offs in case of SPECWEB2005               | 43 |

| 4.5.4 Design Trade-offs in case of EnePBench                 | 50 |

|    | ٠ |   |   |

|----|---|---|---|

| ٧/ | ı | ı | ı |

| CHAPTER 5: DYNAMIC POWER MANAGEMENT TECHNIQUES IN CASPER             | 54  |

|----------------------------------------------------------------------|-----|

| 5.1 Abstract                                                         | 54  |

| 5.2 Introduction                                                     | 55  |

| 5.3 Dynamic Voltage and Frequency Scaling (DVFS)                     | 56  |

| 5.4 Hardware Controlled DPM in Commercial Embedded Processors        | 58  |

| 5.5 Our Contribution                                                 | 58  |

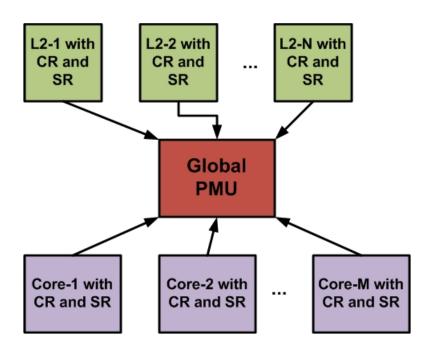

| 5.6 Power Management Unit Architecture                               | 60  |

| 5.7 The Experimental Setup                                           | 62  |

| 5.8 Existing Global Power Management Policies                        | 63  |

| 5.8.1 Chip-wide DVFS                                                 | 64  |

| 5.8.2 MaxBIPS                                                        | 66  |

| 5.8.3 SmartBIPS Power Management Scheme                              | 68  |

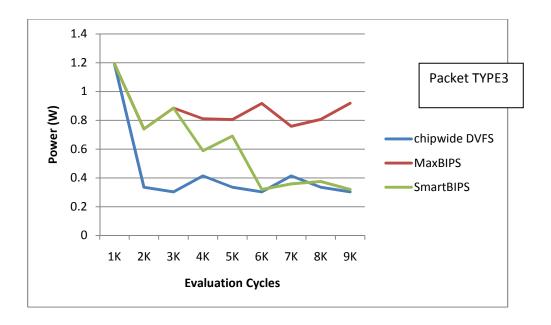

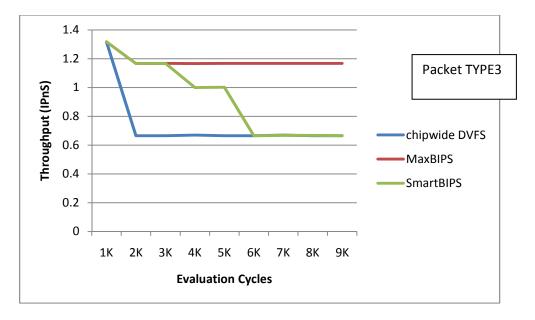

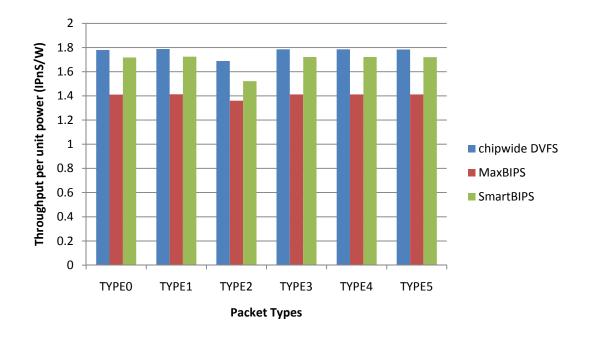

| 5.9 Experimental Results                                             | 75  |

| 5.10 Conclusion                                                      | 83  |

| CHAPTER 6: MODELING OF THROUGHPUT AND POWER DISSIPATION OF CORES     | 86  |

| 6.1 Theory of Statistical Curve Fitting                              | 86  |

| 6.2 Micro-architectural Parameters used in statistical curve-fitting | 86  |

| 6.3 Regression Models and Error Analysis                             | 89  |

| CHAPTER 7: EXPLORATION ALGORITHM                                     | 99  |

| CHAPTER 8: CONCLUSION                                                | 113 |

| REFERENCES                                                           | 115 |

#### **CHAPTER 1: INTRODUCTION**

#### 1.1 Embedded Many-core Processors

Recent years have witnessed a dramatic transition in the complexities and capabilities of embedded processors. Examples include Cisco 40 core Quantum Flow network processor [1], Freescale QorlQ series network processors with upto to 8 cores [2], Netlogic XLP316L 16 core quad-issue processor with 4 hardware threads per core [3], Netronome Network Flow Processor with 40 IXP cores with 4-threads per core [4], NVIDIA Tesla 10 core GGPGPU with 24 scalar stream processors per core [5], and PicoChip 250-300 core picoArray digital signal processor [6]. Similar to high performance processor vendors, those in the embedded domain are permanently altering their existing roadmaps to incorporate hundreds of cores on the same chip in the coming decade - the embedded However, embedded computing many-core processor. fundamentally different from its high performance counterpart because of the need for low energy and real-time operation required in complex embedded applications such as networking, smart power grids, battlefield decision-making, consumer electronics and biomedical devices, to name a few. To satisfy these performance requirements, conceivably the future embedded many-core processor will have hundreds of heterogeneous cores on chip, some of which will be fine grained multi-threaded RISC cores to exploit embedded task level parallelism, and some highly application-specific cores – all connected to hierarchies of distributed on-chip memories by high speed networks-on-chip (NoCs). While the industry focus is on putting higher number of cores on a single chip, the key challenge is to optimally architect these embedded many-core processors for low energy operations while satisfying area and often stringent real-time constraints. With such complex many-core architectures, the traditional approach to processor design through extensive simulations is no longer viable due to the large design space that must be explored in-order to optimize power-performance.

Future generation embedded applications are expected to grow even more complex consisting of a large volume of computational and data intensive real time bound tasks sharing large data structures. To methodically study the power-performance trade-offs of embedded many-core processors to be designed to satisfy the requirements of such complex embedded applications, we focus on Network Processors (NePs) executing the functions of *IP packet processing* as the representative processor domain. Our idea is to thoroughly investigate the high degree of task level parallelism, shared data structures and real-time operations present in packet processing application and establish a modeling and design exploration framework for NePs in this dissertation. The methodology can be easily extended to design complex embedded and high performance many-core platforms.

#### 1.2 Demands of High Performance Packet Processing Routers

Internet demand is growing at an explosive rate. A large volume of

technology consumer products such as personal computers, workstations, webenabled mobile devices and multimedia-enabled smart-phones are used to connect to various websites on a regular basis. Also, an increased use of websites offering online voice and video services such as Hulu, Youtube and Facebook to name a few, has resulted in a surge in overall network traffic. The total network traffic in North America (the highest IP-traffic generating region) is predicted to be approximately 19.0 exabytes per month by 2014 [7]. With such an explosive increase in data demand, existing edge routers used to interface between different communication networks and core routers which constitute the backbone of the internet, are identified to be the bottlenecks in the next generation ultra high speed networks [8]. The Network Processors (NePs) powering these routers can support maximum line speeds of 10 to 100 gigabits per second [9-14], which is insufficient for handling the predicted volume of data in the future. Power is also a critical concern in the design of high performance NePs. Cost is increased by the requirements of larger power supplies and cooling systems. Reliability is compromised by thermal hot-spots on chip. Power increase also adversely affects operating environment features by driving higher utility costs and higher installation and maintenance costs. Cool running NePs pack more ports into a smaller space within thermal operating limits, and have the capability of staying online longer in a battery back-up mode when main power fails. As a result, next generation NePs must be architected to achieve throughput that can support terabit per second (TBPS) line speeds, and yet operate under low power budgets so that the overall operating cost can be

minimized and reliability can be improved.

NePs execute real-time Internet Protocol (IP) packet processing applications, which consist of compute-bound and data-bound tasks [15-17]. Compute-bound tasks include cyclic redundancy error checking codes, blockciphering and likewise. Data-bound tasks include traffic monitoring, IP table lookups, packet fragmentation, Reed Solomon's error checking codes, deep packet inspection and others. Incoming packets in a router are classified as either high priority hard real-time constrained conversational voice packets for example, or lower priority soft real-time constrained non-critical video and other content-delivery packets [18]; the incoming packets are scheduled on the NePs according to their priorities. Once error-checking and route calculations are completed, the packets are sent to the outward queues. Two critical shared data structures in this system are the routing table and the traffic monitoring table. The routing table contains millions of forward route entries which are read by incoming packets to look-up the next destinations. It is rarely updated. On the other hand, the traffic monitoring database is updated with the details of every incoming packet.

#### 1.3 Micro-architectural Domain of Network Processors

Existing high-performance network processors are based on the following micro-architectures: superscalar (SS), streaming single instruction multiple data (S-SIMD), chip multi-processor (CMP), and simultaneous multi-threading (SMT) [10, 11, 14, 19]. While SS exploits instruction level parallelism (ILP), it does not take advantage of the high degree of task (packet) level parallelism (TLP)

inherent in IP packet processing. S-SIMD implements a systolic array of packet processing kernels and the packet data is streamed from one stage to another. However the benefit of pipelining of the packet operations is mitigated by stalls encountered at the shared data structure read/write stage for every incoming packet. Although network processors designed with SMT are able to process packets with high throughput and meet real time constraints, they have high power dissipation and hence are not always cost-effective. Commercial network processor architectures combine these paradigms along with ASIC acceleration engines. For example, EzChip's TopCore technology uses an array of superscalar processors with customized instruction sets [20]; Intel's Next Generation Microengine Architecture combines CMP and multithreading along with inter-processor pipelined operation using next neighbor registers [21]; Netronome's NFP-3240 network flow processor is an array of 40 1.4GHz microengine RISC processor [4].

#### 1.4 Dissertation Contribution

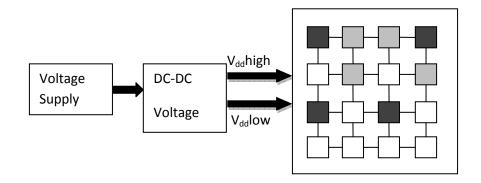

Our design philosophy to achieve a low power TBPS network processor is to use shared memory many-core architecture. Low latency on-chip shared cache memories helps us to minimize off-chip accesses as the large shared data structures (IP lookup table and Traffic monitoring table) are read or updated for all packets. All the processor cores are in-order and use hardware multi-threading; the thread selection policy is fine-grained multi-threading (FGMT). In-order FGMT [22] utilizes simple six stage pipeline shared between the hardware threads, enabling us to achieve (i) high throughput per-core by *latency hiding* and

(ii) minimize the power dissipation of a core by avoiding complex microarchitectural structures such as instruction issue queues, re-order buffers and

history-based branch predictors typically used in superscalar or other types of

hardware multi-threading techniques. Also, to achieve better power-performance

points we make the processor cores structurally heterogeneous. This way more

hardware resources are invested into processor cores designed to compute more

resource-hungry tasks and overall on-chip hardware resources are optimally

utilized. Dynamic power-saving mechanisms such as power-gating and dynamic

voltage and frequency scaling (DVFS) are used at the core level to minimize

power dissipation in case of idle cores. Inside the cores, clock-gating is enabled

at all pipeline stages to minimize dynamic power dissipation. A high level of

packet-level parallelism is achieved due to the large number of cores, which also

overcomes the well-known power wall problem.

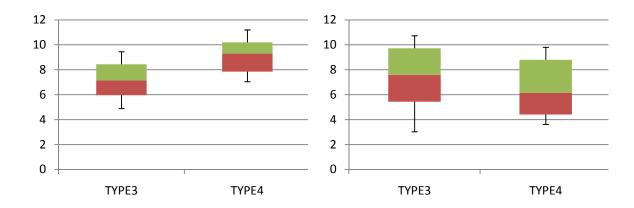

In this dissertation we present an efficient and scalable statistical machine learning based design space exploration framework. Our first step includes the design and development of an instruction trace-driven cycle-accurate many-core processor simulator used to measure throughput (in terms of cycles per instruction) of candidate many-core designs for different combinations of various micro-architectural parameters belonging to this design space. The simulator called Chip Multi-threading Architecture Simulator for Performance Energy and ARea Analysis (CASPER) is a SPARCV9 instruction set based processor simulator. To simultaneously measure power dissipation of candidate designs along with throughput, CASPER is empowered with power estimation models of

each micro-architectural block enabling us to accurately measure power dissipation every cycle. Our literature survey of existing functional and cycle-accurate multi-core simulators and network processor simulators in Chapter 2 show that to the best of our knowledge no such large scale simulation platform exist which can accurately measure power and performance of many-core designs cycle-by-cycle. In addition, a well-established Solaris 5.10 software stack on top of CASPER enables us to execute any embedded or high performance application on this simulation platform.

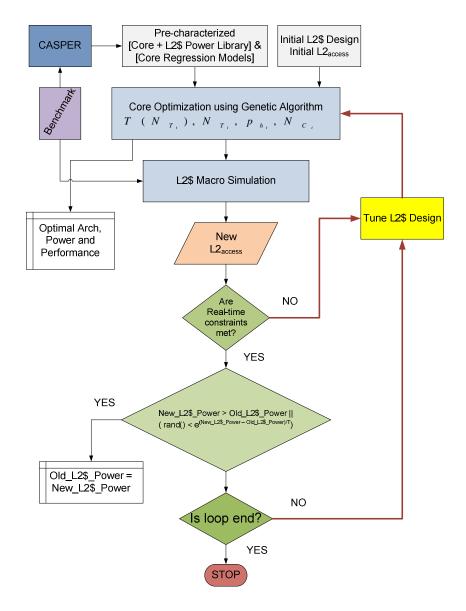

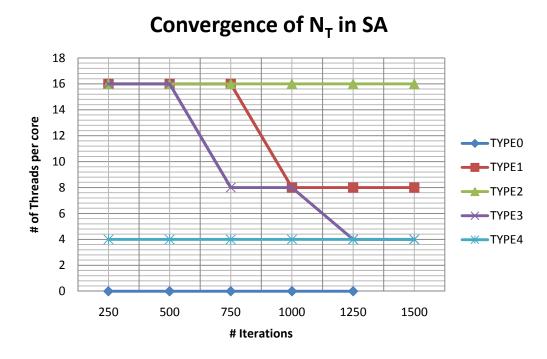

Once we have a validation platform, our second step is to apply a divide and conquer method to explore the design space in a stepwise fashion. Our many-core micro-architectural design space is defined by the core-level parameters which include level one (L1) instruction and data (I/D) cache sizes and number of hardware threads per core, pipeline depth, I/D miss queues and store buffers. The chip-level parameters include number of cores, interconnection architecture, shared second level memory (L2) queue size, L2 organization and access times. Although all of the above micro-architectural parameters are tunable in CASPER to simulate different configurations, it is not practical to use in-loop simulation while exploring the vast micro-architectural design space. To resolve this issue we first optimize the core architectures. The objective of this step is to design a core in such a way that it processes a packet within the realtime boundary and the power dissipation is minimized. Several packet types exist according to which the sequence of functions used to process a packet varies. Hence the micro-architecture of a core optimized for a particular packet type also

varies from other cores designed for other packet types. Using linear statistical regression, the power and performance regression models of the cores are derived using randomly chosen values of the core-level micro-architectural parameters. Once the models are derived, they are used instead of in-loop simulation in a Genetic Algorithm based heuristic to find optimal core micro-architectures for all packet types.

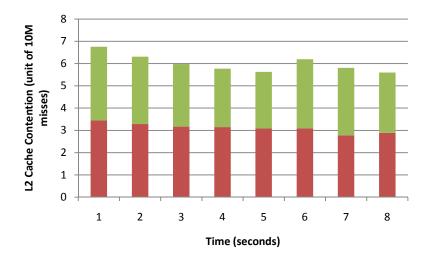

At this point of our exploration, chip-level parameters still not been used. Our third step involves core interaction modeling and shared cache optimization. We estimate the number of cores required for processing a particular distribution of packet types. For a given choice of the interconnection network (for example, crossbar), we build a predictive model for the contention (and hence the associated L2 cache access time) and power dissipation, and the L2 cache banks. The predictive models are built from training data obtained through the macro-simulator L2MacroSim implemented in CASPER. Only the core to L2 cache and L2 cache to memory reply/acknowledgement packets are simulated. The inputs to the L2 MacroSim are L2 cache input queue size per core, cache bank size, line size, associativity, number of L2 banks, L1 I and D cache sizes, line sizes and associativities and instruction trace files for each thread in each core. The individual core parameters are set to their optimal values from previous step. The L2MacroSim enables significant savings in simulation time while capturing the interaction between the cores. The predictive models for core interaction are used to optimize the power dissipation of the L2 cache banks while satisfying the real-time constraints. If the L2 access time constraints cannot be satisfied, we choose the next best core for each packet type and repeat steps two and three.

The rest of the dissertation is organized as follows. Chapter 2 describes existing processor simulators and architecture exploration algorithms. Chapter 3 explains the embedded network packet processing benchmark which we use in this research. Chapter 4 and 5 discusses the structural details and organization of a many-core processor simulator CASPER. Our exploration algorithm is elaborated in Chapter 5 and 6. Results of our research are presented and analyzed in Chapter 6, and finally in Chapter 7 we present our conclusions.

#### CHAPTER 2: BACKGROUND

#### 2.1 Processor Simulators

Virtutech Simics [23] is a full-system scalable functional simulator for embedded systems. The released versions support microprocessors such as PowerPC, x86, ARM and MIPS. Simics is also capable of simulating any digital device and communication bus. The simulator is able to simulate anything from a simple CPU + memory, to a complex SoC, to a custom board, to a rack of multiple boards, or a network of many computer systems. Simics is empowered with a suite of unique debugging toolset including reverse execution, tracing, fault-injection, checkpointing and other development tools. Similarly, Augmint [24] is an execution-driven multiprocessor simulator for Intel x86 architectures developed in University of Illinois, Urbana-Champagne. It can simulate uniprocessors as well as multiprocessors. The inflexibility in Augmint arises from the fact that the user needs to modify the source code to customize the simulator to model multiprocessor system. However both Simics and Augmint are not cycle-accurate and they model processors which do not have open-sourced architectures or instruction sets; this limits the potential for their use by the research community. Another execution-driven simulator is RSIM [25] which models shared-memory multiprocessors that aggressively exploit instruction-level parallelism (ILP). It also models an aggressive coherent memory system and

interconnects, including contention at all resources. However throughput intensive applications which exploit task level parallelism are better implemented by the fine-grained multi-threaded cores that our proposed simulation framework models. Moreover we plan to model simple in-order processor pipelines which enable thread schedulers to use small-latency, something vital for meeting real-time constraints.

General Execution-driven Multiprocessor Simulator (GEMS) [26] is an execution-driven simulator of SPARC-based multiprocessor system. It relies on functional processor simulator Simics and only provides cycle-accurate performance models when potential timing hazards are detected. GEMS Opal provides an out-of-order processor model. GEMS Ruby is a detailed memory system simulator. GEMS Specification Language including Cache Coherence (SLICC) is designed to develop different memory hierarchies and cache coherence models. The advantages of our simulator over the GEMS platform include its ability to (i) carry out full-chip cycle-accurate simulation with guaranteed fidelity which results in high confidence during broad microarchitecture explorations, and (ii) provide deep chip vision to the architect in terms of chip area requirement and run-time switching characteristics, energy consumption, and chip thermal profile.

SimFlex [27] is a simulator framework for large-scale multiprocessor systems. It includes (a) Flexus – a full-system simulation platform and (b) SMARTS – a statistically derived model to reduce simulation time. It employs systematic sampling to measure only a very small portion of the entire application

being simulated. A functional model is invoked between measurement periods, greatly speeding the overall simulation but results in a loss of accuracy and flexibility for making fine micro-architectural changes, because any such change necessitates regeneration of statistical functional models. SimFlex also includes FPGA-based co-simulation platform called the ProtoFlex. Our simulator can also be combined with an FPGA based emulation platform in future, but this is beyond the scope of this work.

MPTLsim [28] is is a uop-accurate, cycle-accurate, full-system simulator for multi-core designs based on the X86-64 ISA. MPTLsim extends PTLsim [29], a publicly available single core simulator, with a host of additional features to support hyperthreading within a core and multiple cores, with detailed models for caches, on-chip interconnections and the memory data flow. MPTLsim incorporates detailed simulation models for cache controllers, interconnections and has built-in implementations of a number of cache coherency protocols.

NePSim2 [30] is an open source framework for analyzing and optimizing NP design and power dissipation at architecture level. It uses a cycle-accurate simulator for Intel's multi-core IXP2xxx NPs, and incorporates an automatic verification framework for testing and validation, and a power estimation model for measuring the power consumption of the simulated NP. To the best of our knowledge, it is the only NP simulator available to the research community. NePSim2 has been evaluated with cryptographic benchmark applications along with a number of basic testcases. However, the simulator is not readily scalable to explore a wide variety of NP architectures.

McPAT [31] is an integrated power, area and timing modeling framework for multi-core and many-core architectures. At the core level it includes models of micro-architectural components such as in-order, out-of-order processor cores while at the chip level it consists of shared caches, multiple clock domains, memory controllers and NoC. The critical path timing models, area models and leakage power model at the circuit level enables McPAT to estimate power dissipation of a simulated design. However, McPAT is a static power dissipation model and does not contain any cycle-accurate behavior.

Although the available processor simulators are effective for exploring different micro-architectural design spaces, CASPER provides us the flexibility to interchangeably tune impactful micro-architectural parameters such as number of threads in a core, pipeline depth, multiple clock domains, number of cores, interconnection network, shared L2 cache size, associativity and line size. Such a wide range of tunable parameters are not found in other simulators. Also, none of the available simulators provide power estimation for simulated designs. The built-in scalable HDL models of all the micro-architectural blocks in our design such as arithmetic unit, queues, caches and arbiters along with technology libraries ranging from 90nm to 22nm are used to accurately model delay, dynamic and leakage power in CASPER. This is an extremely powerful feature enabling us to accurately measure power dissipation of candidate designs right at the design stage. A stripped down version of the Solaris 5.10 OS kernel is ported onto CASPER which enables us to study a wide range of high performance embedded benchmarks. The details of the simulator and microarchitectural features are described in Chapter 4.

#### 2.2 Multi- and Many-core Design Space Exploration

Exploring the many-core processor design space through exhaustive cycle-accurate simulation is not practical due to the prohibitively long simulation time and its superlinear increase as the numbers of cores are scaled. Several techniques have been proposed that avoids exhaustive simulations in effectively exploring the uniprocessor [32-35] and many-core [36-38] design space. We first review recent research on modeling and exploring multi- and many-core architectures.

Lee et al. [36] minimize many-core simulation times in estimating performance through composable regression models for baseline uniprocessor performance, cache contention, and delay penalty. Their unicore simulation platform is an execution driven, cycle accurate IA-32 simulator modeling a superscalar, out-of-order architecture. Long instruction traces derived from a variety of application areas ranging from digital home to the server are used as benchmarks. The uniprocessor regression model predicts the baseline performance of each core while the contention regression model predicts interfering accesses to shared resources from other cores. Uniprocessor and contention model outputs are composed in a penalty regression model that considers the contention as a secondary penalizing effect. A trace simulation is stated to be sufficient for developing the contention and penalty models, thus greatly reducing the overall simulation time. A median CPI error of 6.6% is reported for quad-core processors. The major advantage of their work is the

scalability of the methodology to hundreds of cores. The authors have only focused on developing regression models for predicting CPI and not for power estimation.

lpek et. al. [37] use artificial neural networks to predict performance of a multi-core processor using a small sized training set drawn from the processor design space. Partial simulation techniques based on SimPoint where only certain application intervals or simulation points are modeled, are employed to reduce the simulation time. Benchmarking applications are derived from the SPEC OMP and parallel NAS benchmarks. An average predicted IPC error of 4-5% is reported when the neural network is trained using a 1% sample drawn from a multi-core design space of 8 cores with 250K points and up to 55x performance swings among different system configuration. Similar to Lee et. al. the authors do not model processor power dissipation. More importantly, the authors do not consider chip level shared micro-architectural components such as shared L2 cache and interconnect network which may critically affect performance and power due to the contention in the shared resources. Kang and Kumar [39] treat the multi-core processor design space exploration problem as a classic search and optimization problem with a simulation-in-the-loop approach and use of a rule based machine learning algorithm to prune the search space. The optimization algorithms include steepest ascent hill climbing and genetic algorithms. The machine learning algorithms includes 1-tuple tagging based on the complexity of the cores (simple, moderate, and complex), and 5-tuple tagging based on architecture parameters (Simple, D-cache intensive, I-Cache intensive,

Execution units intensive, and Fetch Width intensive). The objective functions for the optimizations are performance, power, and area. Simulations are done using a modified version of SMTSim. Power and area estimates are obtained for different hardware structures from existing literature. The benchmarks are drawn from SPEC2000, IBS, Olden, and Mediabench. The authors report that their search/machine learning approach achieves within 1% of the performance compared to an exhaustive simulation approach for a 4 core system while being 3800 times faster. However, similar to lpek et. al. the authors do not consider chip level shared micro-architectural components. Also, their power estimation approach does not allow the study of the dependence of power dissipation on architectural parameters. Regarding exploration of network processor architectures, Wolf and Tillman [40] present an analytical model performance model for predicting the performance, chip area, and power consumption for a prototype network processor parameterized using the Commbench network processing benchmark; Mysore et. al, [41] propose a sensor network benchmark, WiSeNBench, and use an ARM simulator to identify some of the key characteristic behaviors; Lin et. al, [42] use a combination of analytical models and simulations to explore core-centric network processor architectures; Salehi et. al, [43] optimize of a superscalar MIPS network processor through exhaustive simulation. Modeling many-core architecture with an analytical approach requires many simplifying assumptions about the architecture while simulations-only approach suffers from the drawbacks mentioned earlier. Dubach et. al. [33] presents an approach that co-designs an optimizing compiler and architecture

using a machine learning approach. Their framework consists of the Xtrem simulator for the Intel XScale architecture, gcc for the compilier, MiBench for the benchmark, and Support Vector Machines (SVM) for modeling the design space. The best design achieves significant performance increases resulting in a 13% improvement in execution time, 23% savings in energy and an energy-delay product (ED) of 0.67. However, their work is limited to unicore processor architectures. Although, our methodology can incorporate compiler optimizations, these optimizations alone may not achieve sufficient performance on many-core processors.

#### 2.3 Statistical Machine Learning for System Optimization

Statistical machine learning (SML) algorithms can be used to model multivariate data sets. The basic framework in machine learning based optimization includes tunable specification, observables identification, training data collection and data analysis. Brewer [44] uses a linear regression to select the best data partitioning scheme for a given problem size; Vuduc [45] employs support vector machines to construct a non-parametric model of the shape of the partitions of the input space of sparse matrix kernels; Cavazos et. al. [46] use a logistic regression model to predict the optimal set of compiler flags for the SPEC benchmark suite; Ganapathi et. al. [47] use Kernel Canonical Correlation Analysis to effectively identify the relationship between a set of optimization parameters and a set of resultant performance metrics to explore the search space for stencil algorithms; Liao et. al. [48] evaluate several classical machine learning algorithms such as Nearest Neighbor, Naive Bayes, Decision Tree,

Support Vector Machines, Multi-layer perception and Radial Basis Function to optimize pre-fetch configurations for data center applications; Li et. a. [49] use machine learning based online performance prediction for runtime parallelization and task scheduling; Leather et. al. [50] develop a new technique to automatically generate good features for machine learning based optimizing compilation by improving the quality of a machine learning heuristic through genetic programming and predictive modeling. The successes of the above listed research efforts indicate the power of machine learning in directing program and system optimization.

## CHAPTER 3: EMBEDDED NETWORK PROCESSING BENCHMARK (ENEPBENCH)

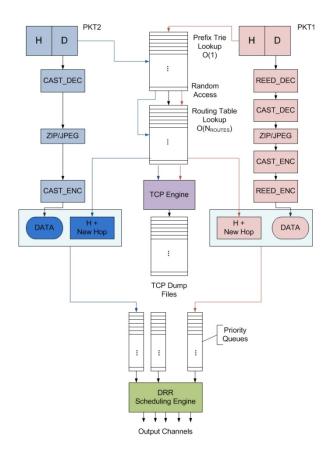

To evaluate the performance and power dissipation of candidate designs we have developed a benchmark suite called *Embedded Network Packet Processing Benchmark* (ENePBench) which emulates the IP packet processing tasks executed in a network router. The router workload varies according to internet usage where random number of IP packets arrive at random intervals. To meet a target bandwidth, the router has to (i) process a required number of packets per second and (ii) process individual packets within their latency constraints. The task flow is described in Figure 3-1. Incoming IPv6 packets are scheduled on the processing cores of the NeP based on respective packet types and priorities. Depending on the type of a packet different header and payload processing functions process the header and payload of the packet respectively. Processed packets are either routed towards the outward queues (in case of pass-through packets) or else terminated.

Figure 3-1: Pictorial representation of IP packet header and payload processing in two packet instances of different types

The packet processing functions of ENePBench are adapted from CommBench 0.5 [51]. Routing table lookup function RTR, packet fragmentation function FRAG and traffic monitoring function TCP constitute the packet header functions. Packet payload processing functions include encryption (CAST), error detection (REED) and JPEG encoding and decoding as shown in Table 3-1.

Table 3-1: ENePBench: Packet processing functions

| Function Type     | Function Name | Description          |

|-------------------|---------------|----------------------|

| Header Processing | RTR           | A Radix-Tree routing |

| Functions         |               | table lookup program |

|                                 | FRAG | An IP packet fragmentation code                                    |

|---------------------------------|------|--------------------------------------------------------------------|

|                                 | ТСР  | A traffic monitoring application                                   |

| Payload Processing<br>Functions | CAST | A 128 bit block cipher algorithm                                   |

|                                 | REED | An implementation of Reed-Solomon Forward Error Correction scheme. |

|                                 | JPEG | A lossy image data compression algorithm.                          |

| Packet Scheduler                | DRR  | Deficit Round Robin fair scheduling algorithm                      |

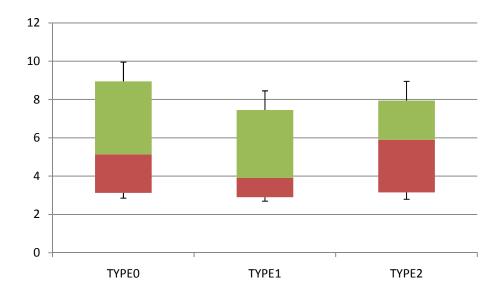

Functionally, IP packets are further classified into types TYPE0 to TYPE4 as shown in Table 3-2. The headers of all packets belonging to packet types TYPE0 to TYPE4 are used to lookup the IP routing table (RTR), managing packet fragmentation (FRAG) and traffic monitoring (TCP). The payload processing of the packet types, however, is different from each other. Packet types TYPE0, TYPE1 and TYPE2 are compute bound packets and are processed with encryption and error detection functions. In case of packet type TYPE3 and TYPE4, the packet payloads are processed with both compute bound encryption and error detection functions as well as data bound JPEG

encoding/decoding functions.

Table 3-2: Packet Types used in ENePBench

| Packet | Header         | Data Functions   | Characteristic | Type of Service  |

|--------|----------------|------------------|----------------|------------------|

| Туре   | Functions      |                  |                |                  |

| TYPE0  | RTR, FRAG, TCP | REED             | Compute Bound  | Real Time        |

| TYPE1  | RTR, FRAG, TCP | CAST             | Compute Bound  | Real Time        |

| TYPE2  | RTR, FRAG, TCP | CAST, REED       | Compute Bound  | Content-Delivery |

| TYPE3  | RTR, FRAG, TCP | REED, JPEG       | Data Bound     | Content-Delivery |

| TYPE4  | RTR, FRAG, TCP | CAST, REED, JPEG | Data Bound     | Content-Delivery |

The two broad categories of IP Packets are hard real-time termed as *real-time* packets and soft real-time termed as *content-delivery* packets. *Real-time* packets are assigned with high priority whereas *content-delivery* packets are processed with lower priorities. The total propagation delay (source to destination) of real-time packets is less than 150 milliseconds (ms) and less than 10 sec for content-delivery packets respectively.

Table 3-3: Performance Targets for IP packet type

| Application/Packet | Data Rate     | Size   | End-to-end | Description       |

|--------------------|---------------|--------|------------|-------------------|

| Туре               |               |        | Delay      |                   |

| Audio              | 4 – 64 (Kb/s) | < 1KB  | < 150 msec | Conversational    |

|                    |               |        |            | Audio             |

| Video              | 16 – 384      | ~ 10KB | < 150 msec | Interactive video |

|             | (Kb/s) |         |            |              |

|-------------|--------|---------|------------|--------------|

| Data        | -      | ~ 10KB  | < 250 msec | Bulk data    |

| Still Image | -      | < 100KB | < 10 sec   | Images/Movie |

|             |        |         |            | clips        |

Assuming maximum 10 to 15 hops are allowed per packet, worst case processing time of the packets in the intermediate routers is in the order of 10ms in case of real-time packets and 1000 ms in case of content-delivery packets respectively [52]. The network propagation delay is assumed to be negligible as optical fiber networks provide sufficient data bandwidth [8]. Table 3-3 enlists the end-to-end transmission delays associated with each packet categories. All of our candidate micro-architectures must be designed to process packets within the packet processing delay limits. In addition to processing delay per packet, we also consider total number of packets required to process per second in a TBPS router. Since IPv6 packets are of varying length we assume in average packet contains a payload of size 8KB. Hence, total number of packets to be processed is given by,

$$Packets \ per \ second = \frac{Bandwidth}{Average \ packet \ size}$$

(3 - 1)

According to Equation 3-1 approximately 70 to 100 million packets are required to be processed per second to achieve TBPS line speed. In a shared memory NeP with  $N_C$  number of cores where each core has  $N_T$  hardware threads,  $N_C * N_T$  packets are processed simultaneously.

Table 3-4: Processing time and instruction count of 5 packet types

| Packet | Processing | Instruction | Packet       |

|--------|------------|-------------|--------------|

| Туре   | Time       | Count       | Distribution |

|        | (msec)     |             |              |

| TYPE0  | 10         | 1255368     | 60%          |

| TYPE1  | 10         | 1354559     | 25%          |

| TYPE2  | 10         | 1258022     | 5%           |

| TYPE3  | 1000       | 8922987     | 5%           |

| TYPE4  | 1000       | 9124851     | 5%           |

The processing time, instruction count and packet distribution for all the packet types are enlisted in Table 3-4. For a given network bandwidth the total number of packets to be processed per second contains a distribution of different packet types. For example, if 100 packets are to be processed per second, packet distribution percentage as shown in Table 3-4 signifies that there are 60 TYPE0 packets, 25 TYPE1 packets and 5 packets of types TYPE2, TYPE3 and TYPE4.

#### CHAPTER 4: CASPER PROCESSOR SIMULATOR

CASPER is an instruction trace-driven cycle-accurate many-core processor simulator which models a shared memory heterogeneous architecture. CASPER provides the user with three key benefits — (i) entire SPARCV9 instruction set support enabling the user to run any Solaris executable on the simulator, (ii) a large set of tunable architectural parameters so that heterogeneous CMT design space can be widely explored, and (iii) deep chip vision - accurate area and performance estimations, along with cycle-accurate power and energy consumption models, which enable the user to capture energy consumption characteristics of different parts of the chip on a cycle-by-cycle basis. CASPER also provides the architect complete access to the processor and enables the monitoring of critical system events. CASPER is open-sourced under GNU GPL license [53].

CASPER is written in C++ programming language and has been flexibly parallelized using pthreads to optimally run on a wide variety of parallel processors. Functionally, it has been validated against the open-sourced functional simulator of Sun Microsystem's UltraSPARC T1 processor [54-56] - SPARC Architecture Simulator (SAM). Timing verification is done in two stages – (i) CPI and memory operations of applications executed on UltraSPARC T1 processor and a structurally similar design simulated in CASPER are matched

and (ii) number of retired instructions, required number of cycles to commit these instructions and program counter progression are matched with the precharacterized HDL models of the processor.

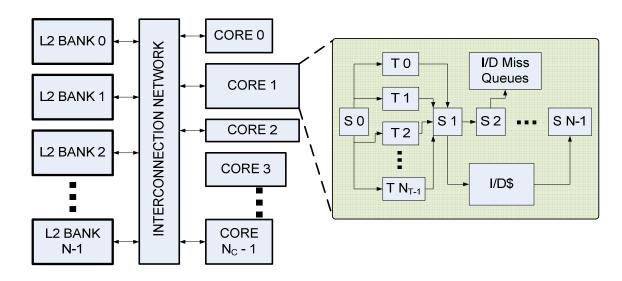

Figure 4-1: The shared memory processor model simulated in CASPER.  $N_C$  heterogeneous cores are connected to  $N_B$  banks of shared secondary cache via a crossbar interconnection network. Each core consists of  $S_0$  to  $S_{N-1}$  are the pipeline stages,  $T_0$  to  $T_{NT-1}$  hardware threads, L1 I/D cache and I/D miss queues

#### 4.1 Processor Model

The processor model used in CASPER is shown in Figure 4-1.  $N_C$  cores are connected to the shared L2 cache through a crossbar interconnection network. The unified L2 cache is inclusive and is divided into  $N_B$  banks. Each bank of L2 privately owns DRAM controllers and independently communicates with the RAM modules.  $N_C$  and  $N_B$  are parameterized in CASPER. The 64-bit pipeline is parameterized to handle  $N_T$  hardware threads and is divided into 6 main stages – Instruction-Fetch (F-stage), Thread-Schedule (S-stage), Branch-and-Decode (D-stage), Execution (E-stage), Memory-Access (M-stage) and Write-back (W-stage).

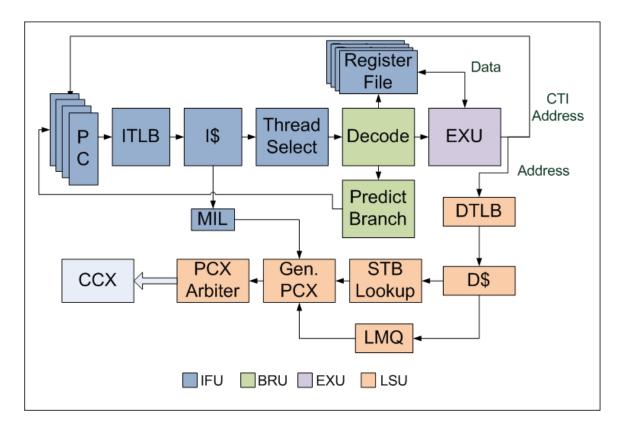

Figure 4-2: Micro-architectural structures inside a core in CASPER

Figure 4-2 shows the different stages of the in-order instruction pipeline inside a core. The Instruction Fetch Unit includes the instruction address translation buffer (I-TLB) and the instruction cache (I\$) and the thread scheduling state machine. I-TLB and I\$ are shared by the hardware threads. Each thread privately owns a register file (processor-state specific set of registers) and a set of alternate address mapped registers called ASI registers; the D-stage includes a full SPARCV9 instruction set decoder described in [57]. The E-stage includes a standard RISC 64-bit ALU, an integer multiplier and divider. Load Store Unit (LSU) is the top level module which implements the M-stage and W-stage. It also includes the data TLB (D-TLB) and data cache (D\$).

The miss path of I\$ is controlled through Missed Instruction List (MIL) and Instruction Fetch Queue (IFQ), while that of the D\$ is controlled through Load Miss Queue (LMQ) which maintains cache misses separately for each thread. Duplicate load misses are maintained in a wait buffer to reduce off-core traffic. Store Buffer (SB) serializes all the stores following the Total Store Order (TSO) model.

The Floating point Unit (FPU) which executes single and double-precision floating-point operations can either be shared across all cores or can be privately owned by a single core. In the former case, all floating point operation packets are routed to the FPU via the interconnection network. Two thread scheduling schemes are implemented in CASPER. The *small latency thread scheduling* scheme allows instructions from ready threads to be issued into the D-stage at every clock cycle [56, 58]. *Long latency scheduling* scheme allows one active thread to continue its execution till it is complete or interrupted by higher priority threads. The full list of tunable architectural parameters is given in Table 4-1.

Table 4-1: Configurable Parameters in Casper

| Name       | Range             | Description               |

|------------|-------------------|---------------------------|

| Cores      | 1: N <sub>C</sub> | Number of cores on chip   |

| Strands    | 1:N <sub>S</sub>  | Hardware threads per core |

| Strand     | 2                 | Long Latency Scheduling / |

| Scheduling |                   | Small Latency Scheduling  |

| FPU        | 1 or 0            | FPU can be shared between |

|            |                   | the cores or threads      |

| Name        | Range                                     | Description                     |

|-------------|-------------------------------------------|---------------------------------|

| I\$_C/D\$_C | 4:64 (KB)                                 | Size of L1 I-D cache            |

| I\$_B/D\$_B | 4:64                                      | Size L1 I-D cache block         |

| I\$_A/D\$_A | 2:8                                       | Associativity of L1 I-D cache   |

| I\$/D\$ Hit | 2:4 clock cycles                          | Measured in Cacti for 45nm      |

| Latency     | ,                                         | technology                      |

| IFQ         | 1N <sub>S</sub> :8N <sub>S</sub>          | Size of Instruction Fetch       |

|             | 11.0.01.0                                 | Queue                           |

| MIL         | 1N <sub>S</sub> :8N <sub>S</sub>          | Size of Missed Instruction List |

| BBUFF       | 4N <sub>S</sub> :16N <sub>S</sub> entries | Size of Branch Address Buffer   |

| LMQ         | 1N <sub>S</sub> :8N <sub>S</sub>          | Size of Load Miss Queue         |

| DFQ         | 1N <sub>S</sub> :8N <sub>S</sub>          | Size of Data Fill Queue         |

| SB          | 1N <sub>S</sub> :16N <sub>S</sub>         | Size of Store Buffer (Store-    |

|             |                                           | ordering)                       |

| L2\$_C      | 256KB:16MB                                | Size of L2 cache                |

| L2\$_B      | 8:24                                      | Size of L2 cache block          |

| L2\$_A      | 4:16                                      | Associativity of L2 cache       |

| L2\$_NB     | 4:16                                      | Number of L2 cache banks        |

In case of heterogeneous designs, the cores in CASPER are configured with different micro-architectures (one set of values of the architectural parameters) although the six functional stages of the core pipeline are fixed. The size and structure of the core-to-memory and memory-to-core request packets are also kept same across all the cores for simplicity. This is important since the

size of the interface packets usually depends on the cache block sizes. The clock signals to the heterogeneous cores are designed to be scaled so that different cores can be driven at different voltage and frequency levels. The tunable parameters in L2 cache are number of banks, bank size, associativity, block size and access latency. Arbiters in the L2 cache controllers issues one request packet from the input queues at a time.

#### 4.2 Performance Measurement

For a given set of micro-architectural parameters, CASPER uses counters in each core to measure the number of completed instructions individually for each hardware thread (Instr<sub>THREAD</sub>) and for the entire core (Instr<sub>CORE</sub>) every second. For a processor clock frequency of 1GHz, the total number of clock cycles per second is 1G. In this case the CPI-per-core is calculated as (1G/Instr<sub>CORE</sub>) while CPI-per-thread is calculated as (1G/Instr<sub>THREAD</sub>).

In addition to CPI, counters are provided in CASPER to measure (i) pipeline stalls, (ii) wait time of threads due to MIL/LMQ/SB being full, (iii) I\$ and D\$ misses, and (iv) stalls due to other long latency operations such as ASI registers writes and floating point operations. Counters are also attached to the crossbar network to measure the access frequencies of the various cores and threads in them. The input queues of the L2 cache are monitored to track the accesses occurring every clock cycle from the various cores and corresponding threads. In addition, special counters are attached to every set in the L2 cache to report utilization, number of hits/misses per core and per hardware thread, and reuse and access frequencies of the active threads running in the system [59]. Cache hit

latencies (delays) are measured using Cacti [60, 61] for a given cache size, block size, associativity and silicon technology. Miss penalties are counted in clock cycles by the counters provided in CASPER.

Another important feature used in CASPER is *Hardware Scouting*. Usually long latency operations such as ASI register load/stores, I\$ misses and D\$ load misses in an in-order thread are blocking in nature. This means the blocked thread is in a WAIT state and no further instructions are issued into the decode stage. This also means that even though the depth of the load miss gueue (LMQ) is greater than one, only one entry is effectively used. To save a few more clock cycles such that load misses following a previous load misses are also enqueued in the LMQ, hardware scouting is implemented in our pipeline which switches the state of a blocked thread to SPECULATIVE RUN state instead of WAIT state. Instructions in a thread which is in SPECULATIVE RUN state are scheduled to the decode stage, but are never committed until the first blocking load miss is resolved. Once the first load miss is resolved, the thread is switched to usual READY state and further execution continues. Arithmetic instructions appearing between two load misses are rolled back and the issuing thread is kept waiting till the first load miss is committed. In average, this enhances the performance of a single thread by 2-5%.

#### 4.3 Verification

Functional correctness of candidate designs simulated in CASPER is verified using a set of diagnostic codes which are designed to test all the possible instruction and data paths in the stages of the pipeline in a core. Additional set of

diagnostic codes are written which consist of random combinations of instructions such that different system events such as traps, store buffer full and others are also asserted. To further verify the accuracy of CASPER, we have compared the total number of system events generated while executing 10 IP packets in the ENePBench in a real-life UltraSPARC T1000 machine consisting of an UltraSPARC T1 (T1) processor (T1) [56] to an exact UltraSPARC T1 prototype (T1\_V) simulated in CASPER. UltraSPARC T1 is the closest in-order CMT variant to our CMT designs modeled in CASPER and consists of 8 cores and 4 hardware threads per core. The simulated processor in CASPER had equal number of cores, hardware threads per core, L1 and L2 caches as T1. Columns 3a, 3b, 4a, 4b, 5a, 5b and 6 of our results tabulated in Table 4-2 compare the number of instructions committed, store buffer full event, I\$ misses and D\$ misses respectively in T1 and T1\_V respectively. Column 6 shows that in average, the error in number of system events is less than 10%.

Table 4-2: Comparison between number of system events for 5 IP packets types in (i) T1000 server with an UltraSPARC T1 processor and (ii) a T1 prototype simulated in CASPER

| Packet<br>Type | Clock<br>Ticks<br>(in    |       | cnt<br>10 <sup>6</sup> ) |     | _full<br>10 <sup>3</sup> ) | е   | niss s $10^3$ |      | nisse<br>S<br>10 <sup>3</sup> ) | Avg.<br>Erro |

|----------------|--------------------------|-------|--------------------------|-----|----------------------------|-----|---------------|------|---------------------------------|--------------|

|                | <b>10</b> <sup>6</sup> ) | T1    | T1_V                     | T1  | T1_<br>V                   | T1  | T1_<br>V      | T1   | T1_<br>V                        | r (%)        |

| TYPE0          | 0.674                    | 0.255 | 0.255                    | 5.0 | 4.9                        | 2.6 | 2.6           | 1.56 | 1.59                            | 2.01         |

| TYPE1          | 0.673                    | 0.254 | 0.254                    | 5.4 | 5.6                        | 2.5 | 2.4           | 1.50 | 1.6                             | 7.35         |

| TYPE2 | 0.612 | 0.26 | 0.258 | 5.1  | 5.2  | 2.6 | 2.5 | 1.51 | 1.52 | 4.0 |

|-------|-------|------|-------|------|------|-----|-----|------|------|-----|

| TYPE3 | 2.257 | 0.90 | 0.892 | 12.9 | 12.7 | 3.5 | 3.9 | 6.84 | 6.84 | 5.7 |

| TYPE4 | 2.259 | 0.94 | 0.896 | 18.9 | 17.1 | 3.5 | 3.6 | 6.89 | 6.89 | 9.5 |

## 4.4 Deep Chip Vision – Area and Power/Energy Measurement

To accurately model the area and the power dissipation of the architectural components we (i) design scalable hardware models of all pipelined and non-pipelined components of the processor in terms of corresponding architectural parameters (Table 1), (ii) derive area and power dissipations (dynamic + leakage) of the component HDL models using industry-standard synthesis and layout tools such as Synopsys and placement and routing tools as Encounter and (iii) statistically curve-fit the area and power dissipation values of the components for increasing values of the parameter to derive linear estimation models. Derived power models are then used to estimate energy consumption of the components by capturing the *activity factor*  $\alpha(t)$  from simulation, and integrating the product of power dissipation and  $\alpha(t)$  over simulation time.

#### 4.5 Design of HDL Models

Table 4-3 summarizes the common hardware structural components used in a CMT processor and the HDL models they map to. Some of the HDL models of the components (both intra-core and chip level components such as interconnect buses and arbiters) are available in OpenSPARC [56], while others have been custom designed in our lab. The HDL models are designed to be scalable, and capture different variations in the architectural parameters.

Table 4-3: Common CPU Hardware Structures and their models used in CASPER

| Hardware<br>Structure         | HDL Model         | Affected By                                                   |

|-------------------------------|-------------------|---------------------------------------------------------------|

| I\$, D\$                      | Cache Array       |                                                               |

| Branch Predictor              | RAM + Logic       | threads-per-core (N <sub>S</sub> )                            |

| I-TLB, D-TLB                  | RAM + CAM         | -                                                             |

| Load Miss Queue               | RAM + CAM         | N <sub>S</sub>                                                |

| Missed Instruction List       | RAM + CAM         | Ns                                                            |

| Store Buffer                  | RAM + CAM + Logic | N <sub>S</sub>                                                |

| Crossbar<br>Interconnect      | Scaled CCX        | number of cores (N <sub>C</sub> )                             |

| L2 Cache Banks                | Cache Array       | N <sub>C</sub>                                                |

| FPU                           | Logic             | SPARCV9 Floating  Point Operations –  FADD, FSUB, FMUL,  FDIV |

| Integer + Float Register File | Logic             | SPARCV9 Register File                                         |

# 4.5.1 Area and Power Estimation

To accurately model the area and the power dissipation of the architectural

components we have (i) designed scalable hardware models of all pipelined and non-pipelined components of the processor in terms of corresponding architectural parameters, (ii) derived power dissipations (dynamic + leakage) of the component HDL models using industry-standard synthesis and layout tools such as Synopsys [62] which targets the Berkeley 45nm Predictive Technology Model (PTM) technology library [63] and placement and routing tools as Encounter [64] and (iii) statistically curve-fit the area and power dissipation values of the components for increasing values of the parameter to derive linear regression models. Derived power models are then used to estimate energy consumption of the components by capturing the *activity factor*  $\alpha(t)$  from simulation, and integrating the product of power dissipation and  $\alpha(t)$  over simulation time. The following equation is used to calculate the power dissipation of a pipeline stage –

$$P_{stage}(t) = P_{leakage}(t) + \alpha P_{dynamic}(t) \quad (4-1)$$

where  $\propto$  is the *activity factor* of that stage ( $\alpha$ =1 if that stage is *active*;  $\alpha$  = 0 otherwise) which is reported by CASPER, and P<sub>leakage</sub> and P<sub>dynamic</sub> are the leakage and dynamic power dissipations of the stage respectively.

The power dissipation values of the parameterized micro-architectural non-pipeline components in a core namely, the load miss queue, store buffer, missed instruction list, I/D-TLB, and I/D\$ are collected from Cadence Encounter using a 1GHz clock into lookup tables. These lookup tables are then used in the simulation to calculate the power dissipation cycle by cycle. Table 4-4 shows the area, dynamic and leakage powers of the micro-architectural blocks in a core.

Area, delay and power dissipation of caches in Table 4-4 have been modeled using Cacti 4.1 [60, 61].

Table 4-4: Post-Layout Area, Dynamic and Leakage Power of HDL Models

| HDL Model                    | Area<br>(mm²) | Dynamic Power (mW) | Leakage<br>Power (uW) |

|------------------------------|---------------|--------------------|-----------------------|

| RAM (16)                     | 0.022         | 1.03               | 17.81                 |

| CAM (16)                     | 0.066         | 3.51               | 67.70                 |

| FIFO (16) for 8 threads      | 0.3954        | 165                | 1200.00               |

| TLB (64)                     | 0.0178        | 21.11              | 92.60                 |

| Cache (32KB)                 | 0.0149        | 28.3               | -                     |

| Cache Controller             |               |                    |                       |

| Integer Register File        | 0.5367        | 11.92              | 4913.7                |

| Float Register File          | 0.0764        | 309.44             | 551.897               |

| FPU                          | -             | -                  | -                     |

| IFU                          | 0.0451        | 3280.1             | 378.39                |

| EXU                          | 0.0307        | 786.99             | 301.94                |

| LSU                          | 0.8712        | 5495.3             | 6848.30               |

| TLU                          | 0.064         | 1302.2             | 553.8458              |

| Floating Frontend Unit (FFU) | 0.0123        | 767.07             | 98.40                 |

| Multiplier                   | 0.0324        | 23.74              | 383.88                |

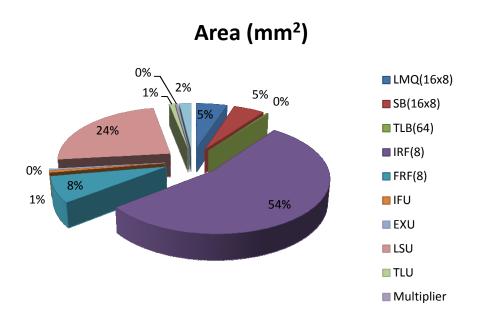

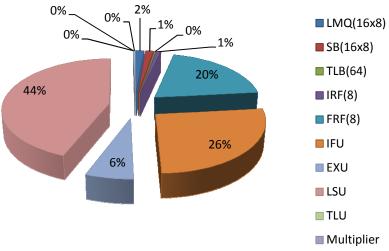

The area distribution of a 8 threaded core in CASPER is shown in Figure 4-3. The width of LMQ, SB, D-TLB are 16, 16 and 64 respectively. The D\$ is 32KB in size with 16B linesize and 4 set-associativity. The integer register file (IRF) for each thread is segregated and hence there are 8 in total. IRF is the biggest contributor of the core area.

Figure 4-3: Area distribution of the micro-architectural features of an 8-thread single core area estimation model in CASPER

# Single core power distribution (mW)

Figure 4-4: Power dissipation distribution of the micro-architectural features of an 8-thread single core area estimation model in CASPER

Figure 4-4 shows the power estimation distribution of the micro-architectural blocks of an 8-threaded core simulated for 1 million clock cycles in CASPER. The width of LMQ, SB, D-TLB are 16, 16 and 64 respectively. The D\$ is 32KB in size with 16B linesize and 4 set-associativity. As observed the load store unit or LSU is the heaviest contributor of power dissipation in a core. The operations of LSU is divided into four pipelined stages where the D-TLB, D\$ are accessed, Store Buffer (SB) is cammed and all out-going packets are resolved; hence the high power dissipation.

The structures of shared L2 cache and interconnection network is codependent on the number of cores in a candidate design which makes it immensely difficult to synthesize, place and route all possible combinations. Hence we have used *multiple linear regression* [65] to model the throughput, dynamic and leakage power dissipation of shared L2 cache and interconnection network respectively. A detailed discussion about the multiple linear and non-linear regressions method is presented in Chapter 6. Dynamic power dissipation measured in Watts of L2 cache is related to the size in megabytes, associativity and number of banks  $N_B$  as shown in Equation 4-2. The model parameters are shown in Table 4-5.

$$L2_{dynamic\ power} = c0 + c1 * Size + c2 * Associativity - c3 * N_B$$

(4-2)

R

R Square

Std. Error of Estimate

0.926

0.857

0.524

Table 4-5: L2 cache linear regresssion model parameters

Similarly, the dynamic and leakage power dissipation measure din milli-Watts of a crossbar interconnection network is given by Equation 4-3 and Equation 4-4 respectively. Note that dynamic and leakage power is exponentially related to number of cores ( $N_c$ ) and number of cache banks ( $N_B$ ). In these two cases, the R value is 0.753 and standard errors of estimates is10.64.

$$IN_{dynamic\_power} = b0 + b1 * e^{b2*Nc} + b3 * Q + b4 * e^{b5*N_B}$$

(4-3)

$IN_{leakage\_power} = b0 + b1 * e^{b2*NC+b3*Q+b4*NB}$  (4-4)

# 4.5.2 Modeling Activity Factor

It is necessary to track the activity factors of all the components and all the stages to accurately estimate the energy consumption of a design. Cycle-accurate simulation captures the switching activity of the micro-architectural components in every clock cycle. As a given instruction is executed through the multiple stages

of the instruction pipeline inside a core, the simulator tracks (i) the intra-core components that are actively involved in the execution of that instruction and (ii) the cycles during which that instruction uses any particular pipeline stage of a given component. Any component or a stage inside a component is assumed to be in two states – idle (not involved in the execution of an instruction) and active (process an instruction). For example, in case of a D\$ load-miss, the occurrence of the miss will be identified in the M-stage. The load instruction will then be added to the LMQ and W-stage will be set to an idle state for the next clock cycle.

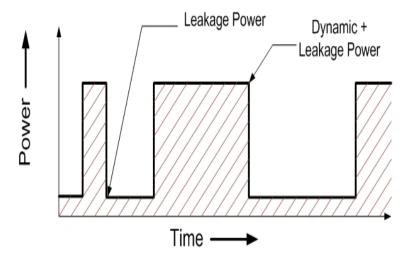

Figure 4-5: Power Dissipation transient for a single pipeline stage in a component. The area under the curve is the total Energy consumption

A non-pipelined component is treated as a special case of a single stage pipelined one. We consider only leakage power dissipation in the *idle* state and both leakage and dynamic power dissipations in the active state. Figure 4-5 shows the total power dissipation of a single representative pipeline stage in a component. Note that the total power reduces to just the leakage part in the

absence of a valid instruction in that stage (*idle*), and the average dynamic power of the stage is added when an instruction is processed (*active*).

A certain pipeline stage of a component will switch to *active* state when it receives an *instruction ready* signal from its previous stage. In the absence of the *instruction ready* signal, the stage switches back to *idle* state. Note that the *instruction ready* signal is used to clock-gate (disable the clock to all logic of) an entire component or a single pipeline stage inside the component to save dynamic power. Hence we only consider leakage power dissipation in the absence of an active instruction. In case of an instruction waiting for memory access or in the stall state due to a prior long latency operation, is assumed to be in *active* state.

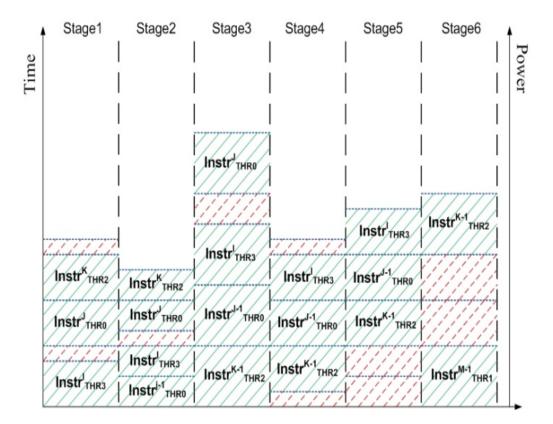

Figure 4-6: Power profile of a pipelined component where multiple instructions exist in different stages. Dotted parts of the pipeline are in idle state and add to

the leakage power dissipation. Shaded parts of the pipeline are active and contribute towards both dynamic and leakage dissipate power dissipations.

Figure 4-6 shows the power (dynamic + leakage) contributions of multiple pipeline stages (which are simultaneously processing different pipelined instructions) to generate the total power dissipation profile of a pipelined microarchitectural component. As shown in the Figure 4-6 above, for any given pipeline stage the horizontal separation lines correspond to different clock cycles during which different instructions flow through the stage. The shaded parts correspond to *active* states of the stage (dynamic + leakage power), while the dotted parts correspond to *idle* states of the stage (only leakage power). Note that different stages have different values of dynamic and leakage power dissipations. The following equation is used to calculate the power dissipation of a pipeline stage —

$$P_{stage}(t) = P_{leakage}(t) + \alpha P_{dynamic}(t)$$

(4 – 5)

where  $\propto$  is the *activity factor* of that stage ( $\alpha$ =1 if that stage is *active*;  $\alpha$  = 0 otherwise) which is reported by CASPER, and P<sub>leakage</sub> and P<sub>dynamic</sub> are the leakage and dynamic power dissipations of the stage respectively. Finally the energy consumption is found using the following equation:

$$E = \sum_{t=1}^{Simulation\ Time} P_{stage}(t) \qquad (4-6)$$

A trace of the total power dissipation of a processor under simulation is reported by CASPER by adding the power dissipation profiles of all stages of all components for every clock cycle of simulation. The area under that curve is the total energy consumption of the processor for a given benchmark. CASPER can be used to design future throughput intensive CMT architectures ranging from

real-time constrained embedded systems (such as embedded network processors) to high-performance computing (HPC) platforms (such as web/application servers). Typically, for embedded applications the objective is to minimize energy consumption subject to throughput constraints, while for high-performance applications throughput is maximized under power dissipation constraints. The following sections explain the data demand characteristics of these two application domains and how we employ CASPER to design processors for them. We use commercial benchmarks such as CommBench-0.5 (embedded network processors) and SPECJBB2005 (web/application server processors) to evaluate CMT architectures.

## 4.5.3 Design Trade-offs in case of SPECWEB2005

High-end web and applications servers process huge amounts of data simultaneously. The typical data complexity is of the order of 10-20 million simultaneous users (parallel tasks) accessing large databases and executing transactions. User processes are mapped to software threads and corresponding transaction data from the backend database servers are transferred into the local memory of the executing processor. It is possible that substantial data can be reused or shared for multiple users justifying the use of shared memory architectures to enhance performance. CMT shared-memory architectures are known to perform efficiently for such applications [54, 55, 58]. L2 cache size (maximize amount of on-chip data), number of threads per core, number of cores and other critical architectural parameters have substantial impact on processor performance. Table 4-6 lists the parameters of interest and the range of values

that can be explored in an HPC CMT processor. The benchmark used to study this class of applications is SPECJBB2005 [66].

Table 4-6: The micro-architectural parameters and their ranges used to study the design trade-offs in SPECWEB2005

| Parameter  | Range    |

|------------|----------|

| Cores      | 1:32     |

| Threads    | 4:32     |

| L1_I\$     | 4KB:64KB |

| L1_D\$     | 4KB:64KB |

| I-TLB      | 16:64    |

| D-TLB      | 16:64    |

| L2\$_Size  | 1MB:16MB |

| L2\$_banks | 4:16     |

Table 4-7: Baseline Architecture used to measure CPI for SPECJBB2005

| Parameter                | Value    |

|--------------------------|----------|

| Cores                    | 1        |

| Threads per core         | 1        |

| L1 I\$/D\$ size          | 16KB/8KB |

| L1 I\$/D\$ Associativity | 4/4      |

| L1 I\$/D\$ Block size    | 32/16    |

| I/D-TLB                  | 64/64    |

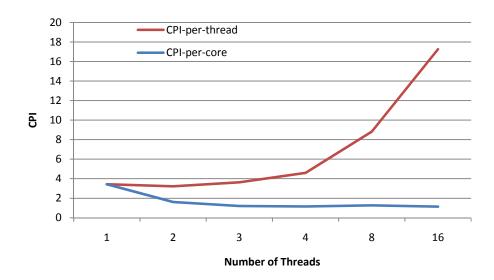

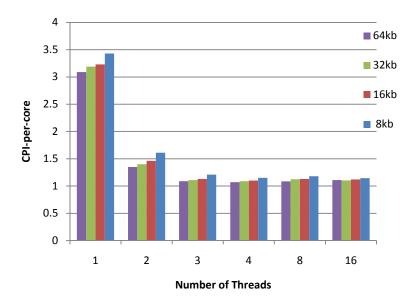

Table 4-7 shows the baseline architecture used to study the SPECJBB2005 benchmark. Figure 4-7 shows how the normalized CPI of a core and that of a strand vary with the number of threads in the core (from 1 to 16). Other architectural parameters are kept constant in baseline architecture for this experiment. As observed, performance of a core levels off as the number of threads increases, leading to more L1 cache misses due to cache thrashing.

Figure 4-7: Scalability of CPI-per-core and CPI-per-strand of a core as threadsper-core is increased from 1 to 16. SPECJBB2005 is used as benchmark.

Additional stalls occur in the LSU, where the arbiter, responsible for transferring load-store packets from the core to the shared L2 cache becomes the bottleneck. The arbiter follows a round-robin fairness scheduling scheme to issue packets into the interconnection network. The worst case wait time for an outbound load/store packet of a thread is of the order of  $O(N_S)$ , where  $N_S$  is the number of threads in the core. However, the CPI-per-strand increases considerably since a thread can wait in the worst case for  $O(N_S)$  cycles to be scheduled from the F-

stage to the D-stage. Note that Figure 6 shows the data for *small latency thread* scheduling scheme.

In Figure 4-8, we show how performance scales when two independent architectural parameters, (i) number of threads per core and (ii) size of L1 data cache, are varied together. The area and power dissipation for a 4-way set associative 16-block size cache for increasing size of cache is enlisted in Table A.1 in Appendix A. Note in Figure 4-8 that less misses in larger caches helps in increasing the effective CPI-per-core. However, as the number of threads-per-core increases, L1 cache contention reduces this benefit. However, larger cache sizes indicate larger die area and hence more power dissipation.

Figure 4-8: CPI-per-core scalability as threads-per-core is scaled from 1 to 16 and the size of a 4-way set associative 16-block sized data cache is varied from 8-64KB (with SPECJBB2005)

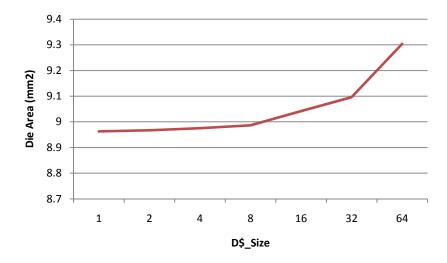

Figure 4-9: Scalability of the area of a core (consisting of 4-threads) as size of a 4-way set-associative 16-block size data cache increases (with SPECJBB2005)

Figure 4-9 shows die area (in mm²) of one core scales almost super-linearly with increasing cache sizes. In the figure we vary the data cache size from 1KB to 64KB.

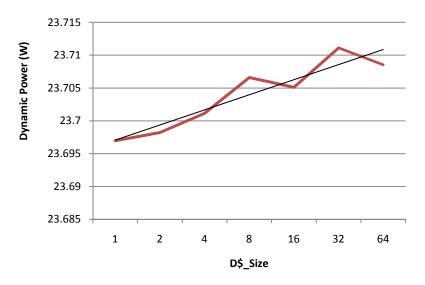

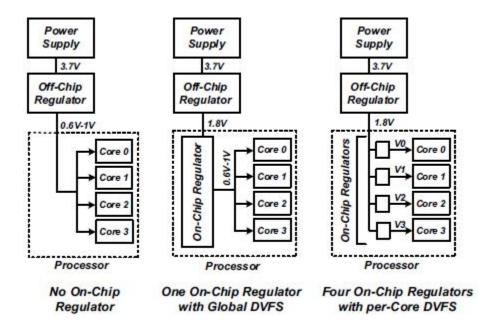

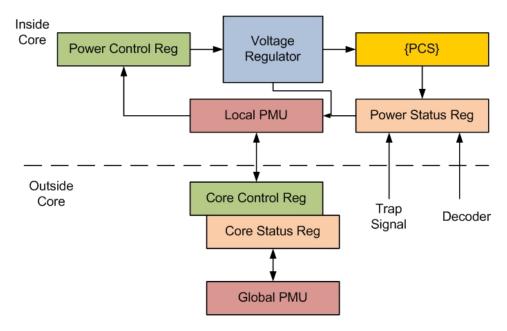

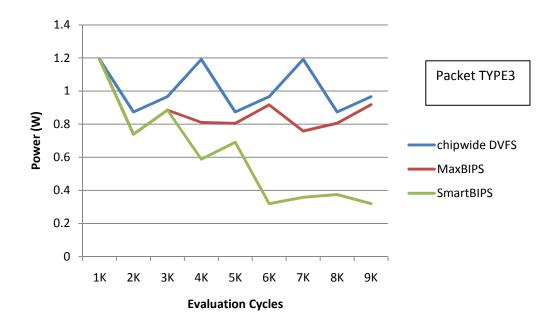

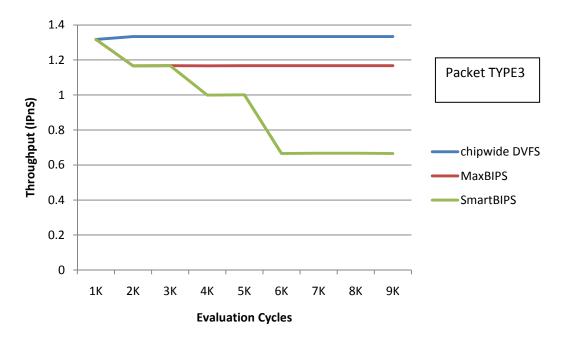

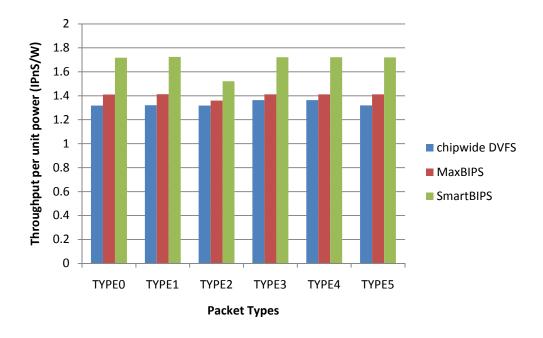

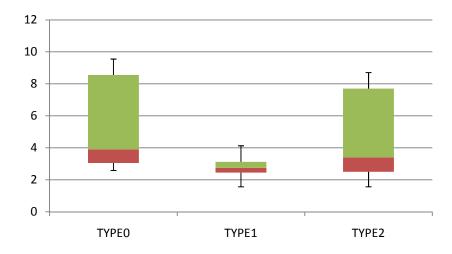

Figure 4-10: Dynamic power dissipation of a core (consisting of 4-threads) as size of a 4-way set-associative 16-block size data cache increases. The black line shows the trend (with SPECJBB2005)