# BEHAVIORAL MODELING OF ZINC-OXIDE, THIN-FILM, FIELD-EFFECT TRANSISTORS AND THE DESIGN OF PIXEL DRIVER, ANALOG AMPLIFIER, AND LOW-NOISE RF AMPLIFIER CIRCUITS

by

# Leroy Alfred Calder III

A dissertation submitted to the faculty of The University of North Carolina at Charlotte In partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2010

| Approved by:          |

|-----------------------|

| Dr. David M. Binkley  |

| ,                     |

| Dr. Arun Ravindran    |

|                       |

| Dr. Yogendra P. Kakad |

| Dr. Tom Weldon        |

|                       |

| Dr. Yasin Raja        |

©2010 Leroy Alfred Calder III ALL RIGHTS RESERVED

## **ABSTRACT**

LEROY ALFRED CALDER III. Behavioral modeling of zinc-oxide, thin-film, field-effect transistors and the design of pixel driver, analog amplifier, and low-noise RF amplifier circuits. (Under the direction of DR. DAVID M. BINKLEY)

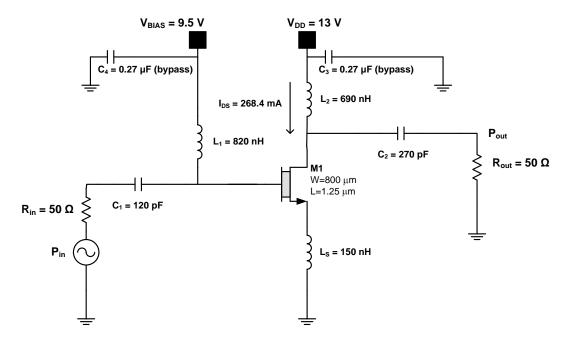

Zinc-oxide (ZnO) is of great interest due to transparent properties, high breakdown voltages, and low cost. Behavioral modeling is presented in this dissertation to model ZnO thin-film field-effect transistor (FET) drain current versus gate-source overdrive voltage. Initial findings show that in "strong inversion," saturation, the drain current equation reveals a quartic-law dependency on gate-source overdrive voltage instead of square-law dependency seen in complementary metal-oxide semiconductor (CMOS) with no mobility reduction effects. This is postulated to result from the ZnO mobility showing a square-law increase with gate-source overdrive voltage. A "strong inversion," saturation model having ±1.6% deviation from measured data is created in verilog-A to simulate and design circuits. Circuits include a fabricated and measured pixel driver circuit sinking 28 μA of current while only having a gate area of 20 μm<sup>2</sup>. This ZnO thin-film FET pixel driver is believed to have the highest current density reported at the time of this writing. Also, the first known ZnO thin-film FET analog amplifier is analytically designed for a gain of 3 V/V at 10 kHz while drawing only 8 µA of supply current. Finally, the first known ZnO thin-film FET low-noise RF amplifier is designed, utilizing scattering parameters measured at the Air Force Research Laboratory on a device with minimum channel length of 1.25 μm. This amplifier has a small-signal gain of 12.6 dB at 13.56 MHz, and a current drain of 268.4 mA at a drain voltage of 13 V.

# DEDICATION

This work is dedicated to my wife, Heather. She has been my source of hope, my source of inspiration, and my constant supporter throughout this process. No matter how frustrated or discouraged I might have become, she has always been there to show me the love and confidence of a true best friend. This work would not have been possible otherwise.

## **ACKNOWLEDGEMENTS**

I would like to thank and acknowledge Dr. David Binkley for allowing me the opportunity to work with him on the ZnO thin-film FET program. I sincerely appreciate the time he has spent with me on my visits to campus in order to make this work possible.

In addition, I would like to thank Dr. Burhan Bayraktaroglu and Dr. Kevin Leedy at the Air Force Research Laboratory for all the efforts put forth in assisting me with the fabrication of research circuits and test devices. Without their assistance this work would not have been successfully completed.

I would also like to thank Dr. Arun Ravindran for teaching and advising me earlier in my academic career as I was learning the Cadence tool and other aspects of electrical engineering. In addition, I would like to acknowledge the remainder of my committee, Dr. Tom Weldon, Dr. Yogendra Kakad, and Dr. Yasin Raja as they have patiently served on my committee for these many years. I have learned many things from each of them, too numerous to name.

Many thanks to all of the graduate students past and present for their assistance and fellowship during this long road we have traveled together. Specifically I would like to recognize Dr. Steve Tucker, Chris Wichman, Robert Crawford, Matt Davis, and Jonathan Harris. We have endured many long nights of studying and projects together.

vi

From my working colleagues who have supported my efforts at RFMD I would

most like to thank Gustavo Garcia, Darrin Walraven, and Clinton Silvis for sharing their

experience and assisting me in my research efforts.

I would also like to thank my parents, sister, and in-laws who have always been a

great support for my endeavors in academia. My greatest thanks to them would be the

faith in Christ that they have shared with me as I have grown and become an adult. That

faith has been the corner stone to get me through whatever challenge has arisen. To

God be the glory for all things I have and ever will accomplish.

Finally, my greatest thanks go to my wife and daughter who have sacrificed time

with me in order to allow completion of this degree. Thank you both!

Leroy Alfred 'Alan' Calder, III

March 5<sup>th</sup>, 2010

# TABLE OF CONTENTS

| LIST C          | )F TABL  | ES                                                        | ix   |

|-----------------|----------|-----------------------------------------------------------|------|

| LIST OF FIGURES |          |                                                           | x    |

| LIST C          | F ABBR   | REVIATIONS                                                | xiii |

| СНАР            | TER 1: I | NTRODUCTION                                               | 1    |

|                 | 1.1      | Opportunities for Zinc-Oxide Thin-Film FET Circuits       | 1    |

|                 | 1.2      | Research Contributions                                    | 3    |

|                 | 1.3      | Dissertation Organization                                 | 5    |

| СНАР            | TER 2: ( | OPERATION OF THE ZNO THIN-FILM FET                        | 6    |

|                 | 2.1      | ZnO Thin-Film FET                                         | 6    |

|                 | 2.2      | ZnO Thin-Film FET Operation                               | 7    |

|                 | 2.3      | Air Force Research Laboratory Devices                     | 8    |

| СНАР            | TER 3: E | BEHAVIORAL MODELING OF ZNO THIN-FILM FETS                 | 11   |

|                 | 3.1      | DC Device Modeling                                        | 11   |

|                 |          | 3.1.1 Derivation of the M Value                           | 11   |

|                 |          | 3.1.2 Saturation Region Modeling                          | 14   |

|                 |          | 3.1.3 Non-saturation Region Modeling                      | 19   |

|                 | 3.2      | AC Device Modeling                                        | 21   |

|                 | 3.3      | RF Device Modeling                                        | 26   |

| СНАР            | TER 4: [ | DESIGN AND EVALUATION OF A ZNO THIN-FILM FET PIXEL DRIVER | 32   |

|                 | 4.1      | Thin-Film FET Modeling Extraction                         | 32   |

|              |                                                      | viii |

|--------------|------------------------------------------------------|------|

| 4.2          | Applications of ZnO Thin-Film Pixel Drivers          | 34   |

| 4.3          | Circuit Description                                  | 35   |

| 4.4          | Analysis and Design                                  | 37   |

| 4.5          | Design Simulations                                   | 40   |

| 4.6          | Experimental Evaluation                              | 44   |

| 4.7          | Comparison of Modeled and Measured Results           | 48   |

| 4.8          | Summary and Conclusions                              | 49   |

| CHAPTER 5: [ | DESIGN OF A ZNO THIN-FILM FET ANALOG AMPLIFIER       | 52   |

| 5.1          | Circuit Description                                  | 52   |

| 5.2          | Analysis and Design                                  | 57   |

| 5.3          | Design Simulations                                   | 59   |

| 5.4          | Summary and Conclusions                              | 60   |

| CHAPTER 6: [ | DESIGN OF A ZNO THIN-FILM FET LOW-NOISE RF AMPLIFIER | 61   |

| 6.1          | Circuit Description                                  | 62   |

| 6.2          | Analysis and Design                                  | 64   |

| 6.3          | Design Simulations                                   | 68   |

| 6.4          | Summary and Conclusions                              | 78   |

| CHAPTER 7: S | SUMMARY AND CONCLUSIONS                              | 79   |

| 7.1          | Summary and Conclusions of Work                      | 79   |

| 7.2          | Proposed Future Work                                 | 81   |

| REFERENCES   |                                                      | 84   |

| APPENDIX A:  | VERILOG-A MODEL                                      | 87   |

# LIST OF TABLES

| Table 2.1 | Process steps and measurements for Air Force Research Laboratory ZnO thin-film FETs [8].             | 10 |

|-----------|------------------------------------------------------------------------------------------------------|----|

| Table 3.1 | Example set of ZnO thin-film FET small-signal parameter values.                                      | 25 |

| Table 4.1 | Comparison of current density $(I_D/W)$ between this work and previous publications.                 | 50 |

| Table 5.1 | Differential input pair M1 and M2 transistor parameters for ZnO thin-film FET analog amplifier.      | 54 |

| Table 5.2 | Diode-connected active loads M3 and M4 transistor parameters for ZnO thin-film FET analog amplifier. | 55 |

| Table 5.3 | Current mirror M5 and M6 transistor parameters for ZnO thin-film FET analog amplifier.               | 56 |

# LIST OF FIGURES

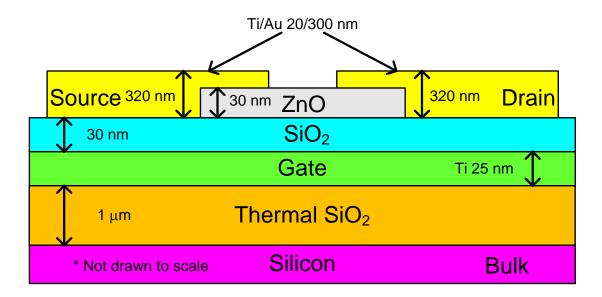

| Figure 2.1  | Air Force Research Laboratory ZnO thin-film FET fabrication layers (not drawn to scale) [8].                                                            |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

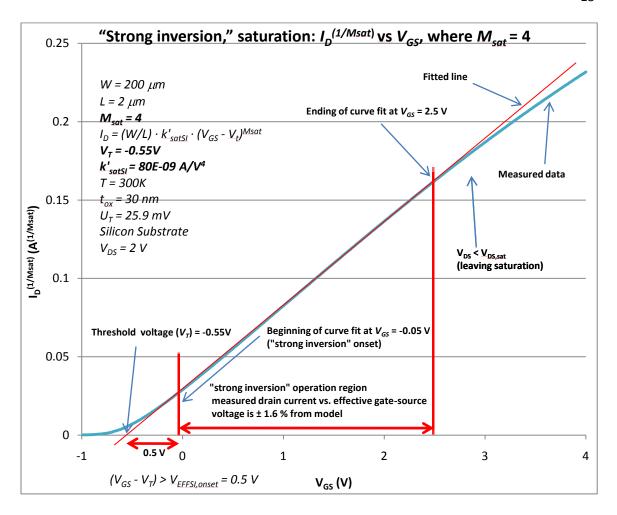

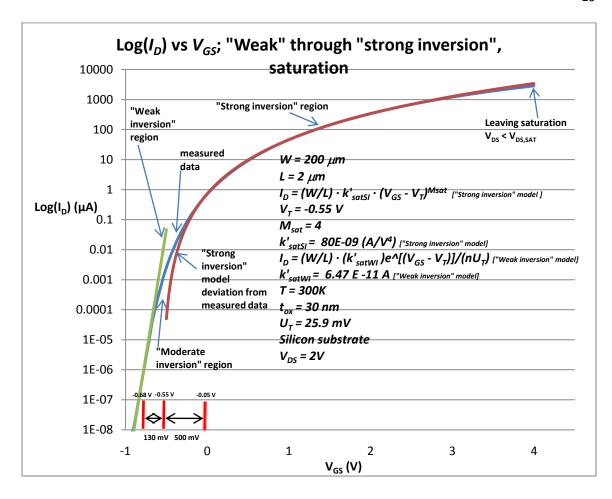

| Figure 3.1  | Measured and modeled drain current versus gate-source voltage for "strong inversion," saturation region of operation for $M_{sat}$ = 4, $V_{DS}$ = 2 V. | 15 |

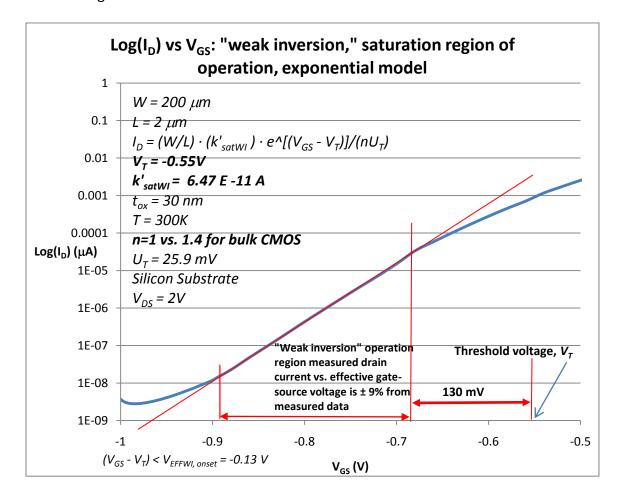

| Figure 3.2  | Measured and modeled ZnO thin-film FET mobility versus gate-source voltage at $V_{DS}$ = 0.5 V.                                                         | 16 |

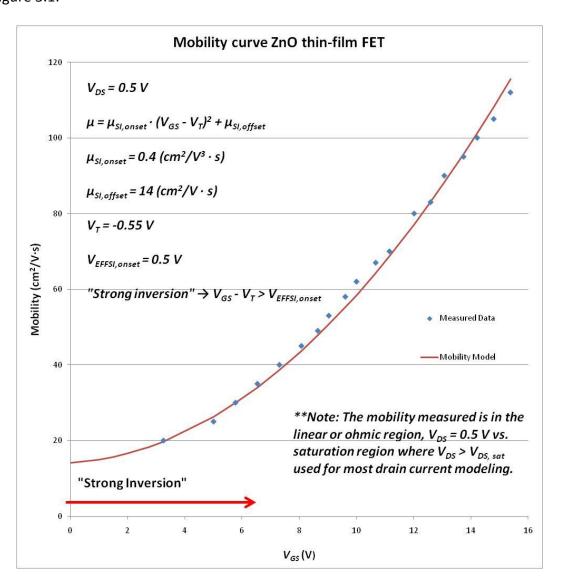

| Figure 3.3  | Measured and modeled drain current versus gate-source voltage for "weak inversion," saturation region with $V_{DS} = 2 \text{ V}$ .                     | 18 |

| Figure 3.4  | Measured and modeled ZnO thin-film FET drain current versus gate-source voltage from "weak" through "strong inversion."                                 | 19 |

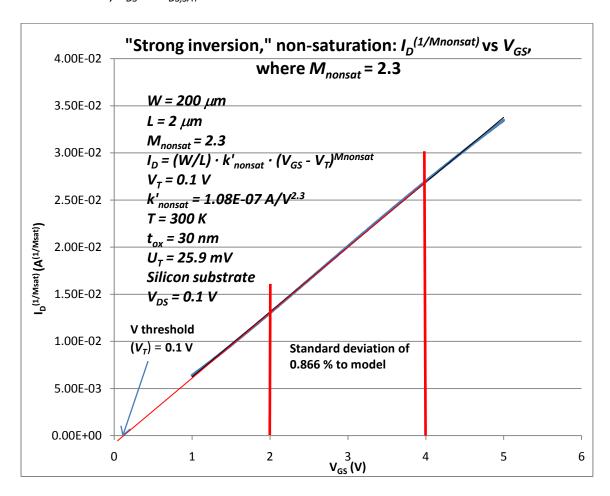

| Figure 3.5  | Measured and model drain current versus gate-source voltage for non-saturation region of operation with $M_{nonsat}$ = 2.3 and $V_{DS}$ = 0.1V.         | 20 |

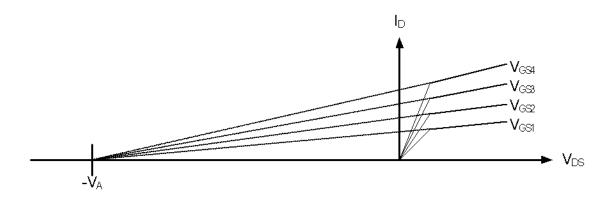

| Figure 3.6  | The graphical method of extracting the Early voltage.                                                                                                   | 22 |

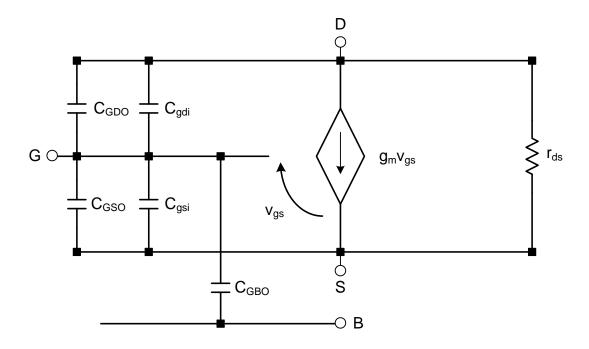

| Figure 3.7  | Small-signal model for the ZnO thin-film FET including capacitances as adapted from [19, p. 98].                                                        | 23 |

| Figure 3.8  | Fabrication layers with capacitances drawn for illustration of Figure 3.7 [8].                                                                          | 23 |

| Figure 3.9  | Non-matched $S_{21}$ showing the intrinsic gain flatness of the ZnO thin-film FET.                                                                      | 27 |

| Figure 3.10 | Input impedance sweep of the device to show the impedance of the gate at varying frequencies.                                                           | 29 |

| Figure 3.11 | Output impedance sweep on the drain of the ZnO thin-film FET to show the drain impedance at given frequencies.                                          | 29 |

| Figure 3.12 | $S_{12}$ showing the reverse isolation of the ZnO thin-film FET.                                                                                        | 30 |

| Figure 3.13 | Lumped-element RF model for ZnO thin-film FET from S-parameter measurements [2].                                                      | 31 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.1  | Threshold voltage and current constant extraction for ZnO thin-film FETs used in fabricated pixel drivers.                            | 33 |

| Figure 4.2  | Analysis of the deviation from Chapter 3 model parameters and updated model parameters for fabricated ZnO thin-film FET pixel driver. | 34 |

| Figure 4.3  | Single-transistor ZnO thin-film FET pixel driver schematic.                                                                           | 36 |

| Figure 4.4  | Selectable ZnO thin-film FET pixel driver schematic.                                                                                  | 37 |

| Figure 4.5  | Single-transistor ZnO thin-film FET pixel driver designed for a 20 $\mu m$ x 20 $\mu m$ OLED pixel.                                   | 38 |

| Figure 4.6  | Selectable ZnO thin-film FET pixel driver designed for a 20 $\mu\text{m}$ x 20 $\mu\text{m}$ OLED pixel.                              | 39 |

| Figure 4.7  | Spreadsheet drive current model data for single-transistor ZnO thin-film FET pixel driver design.                                     | 41 |

| Figure 4.8  | Verilog-A drive current model data for single-transistor ZnO thin-film FET pixel driver design.                                       | 41 |

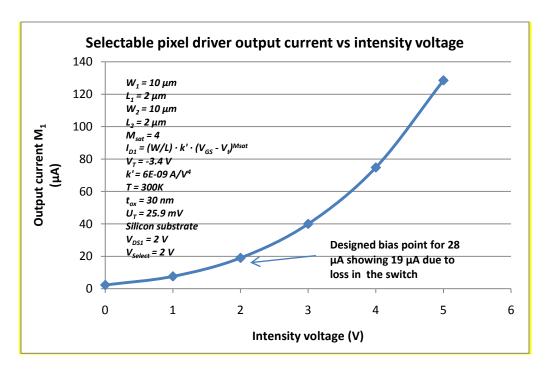

| Figure 4.9  | Spreadsheet drive current model data for selectable ZnO thin-film FET pixel driver design.                                            | 42 |

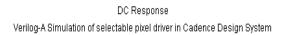

| Figure 4.10 | Verilog-A drive current model data for selectable ZnO thin-<br>film FET pixel driver design.                                          | 44 |

| Figure 4.11 | Photomicrograph of fabricated single-transistor ZnO thin-film FET pixel driver circuit.                                               | 44 |

| Figure 4.12 | Photomicrograph of fabricated selectable ZnO thin-film FET pixel driver circuit.                                                      | 45 |

| Figure 4.13 | Single-transistor ZnO thin-film FET pixel driver test circuit.                                                                        | 46 |

| Figure 4.14 | Selectable ZnO thin-film FET pixel driver test circuit.                                                                               | 46 |

|             |                                                                                                                                      | XII |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.15 | Measured data for single-transistor ZnO thin-film FET pixel driver design.                                                           | 47  |

| Figure 4.16 | Measured data for selectable ZnO thin-film FET pixel driver design.                                                                  | 47  |

| Figure 4.17 | Measured and modeled drive current for the single-transistor ZnO thin-film FET pixel driver circuit.                                 | 48  |

| Figure 4.18 | Measured and modeled drive current for the selectable ZnO thin-film FET pixel driver circuit.                                        | 49  |

| Figure 5.1  | Schematic of ZnO thin-film FET analog amplifier.                                                                                     | 53  |

| Figure 6.1  | ZnO thin-film FET low-noise amplifier including input and output matching networks and source degeneration inductance for stability. | 63  |

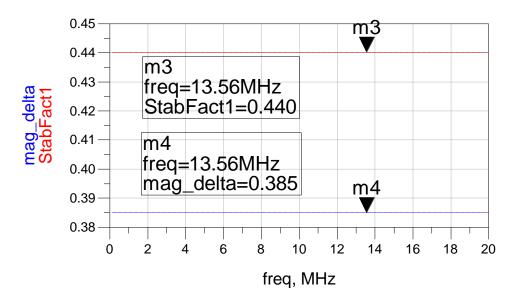

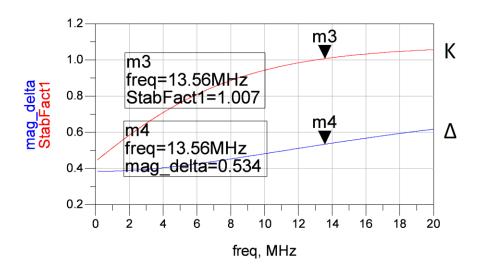

| Figure 6.2  | Rollett stability factor $K$ , as StabFact1. Also mag_delta is plotted which has previously been symbolized by $\Delta$ .            | 70  |

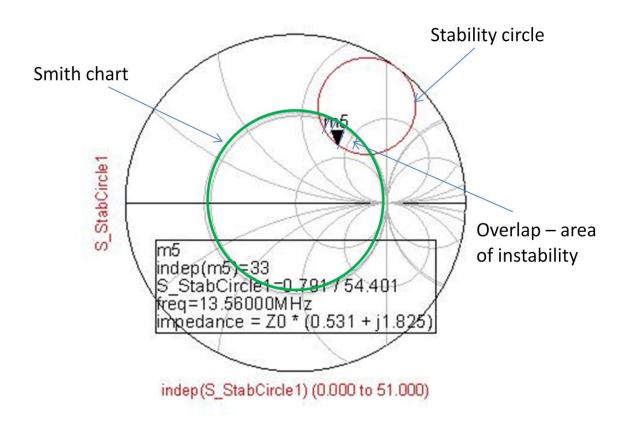

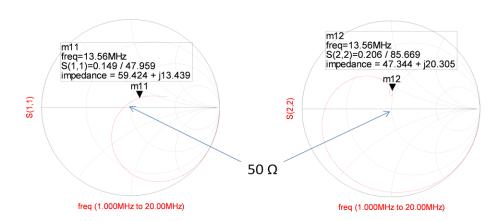

| Figure 6.3  | Source stability circle at 13.56 MHz showing operation within the real portion of the Smith chart at 13.56 MHz.                      | 71  |

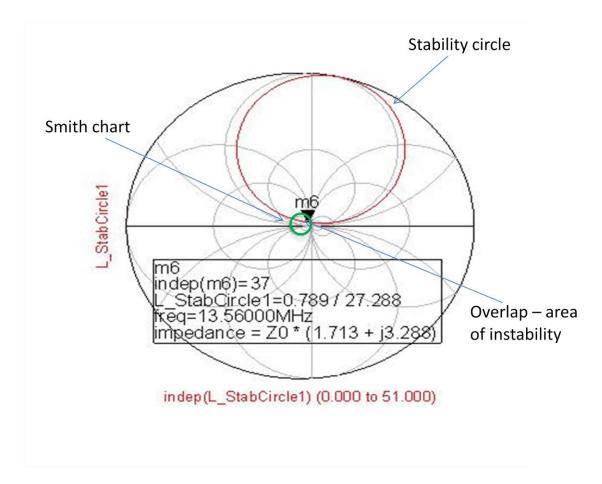

| Figure 6.4  | Load stability circle showing operation within the real part of the Smith chart at 13.56 MHz.                                        | 72  |

| Figure 6.5  | Rollett stability factor, $K$ , as StabFact1. Also mag_delta is plotted which has previously been symbolized by $\Delta$ .           | 73  |

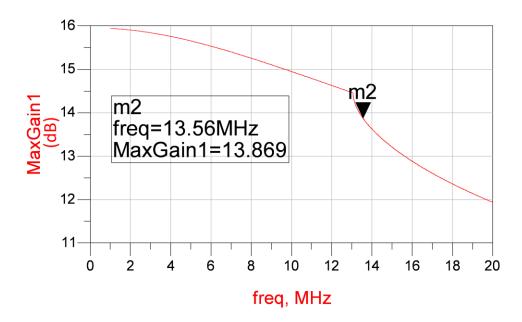

| Figure 6.6  | MAG or maximum available gain with the 150 nH source inductor present.                                                               | 74  |

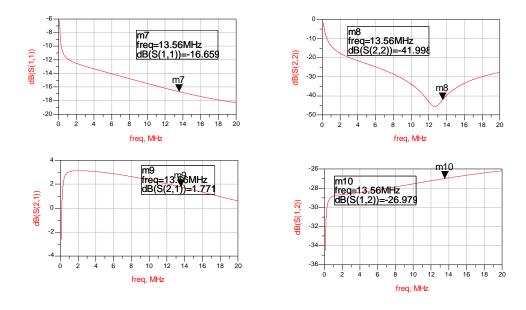

| Figure 6.7  | S-parameters of the unmatched ZnO thin-film FET including stability source inductor.                                                 | 75  |

| Figure 6.8  | ADS Smith chart plots of input and output impedance in order to show conjugate matches.                                              | 76  |

| Figure 6.9  | Simulated S-parameters of complete, matched ZnO thin-film FET LNA.                                                                   | 77  |

# LIST OF ABBREVIATIONS

ZnO Zinc-Oxide

FET Field-Effect Transistor

GaAs Gallium-Arsenide

CMOS Complementary Metal-Oxide Semiconductor

IC Integrated Circuit

eV Electron-Volt

ITO Indium Tin Oxide

LCD Liquid Crystal Display

PDP Plasma Display Panel

OLED Organic Light Emitting Display

RF Radio Frequency

LNA Low-Noise Amplifier

ADS Advanced Design System

AFRL Air Force Research Laboratory

GaN Gallium-Nitride

SiO<sub>2</sub> Silicon Dioxide

PECVD Plasma-Enhanced Chemical Vapor Deposition

MOSFET Metal-Oxide Semiconductor FET

DC Direct Current

AC Alternating Current

VNA Vector Network Analyzer

TV Television

LED Light Emitting Diode

ESD Electro-Static Discharge

FIB Focused Ion Beam

MAG Maximum Available Gain

# 1.1 Opportunities for Zinc-Oxide Thin-Film FET Circuits

Zinc-oxide (ZnO) is relatively new to the semiconductor industry. Zinc-oxide was used for centuries as part of various metallurgical activities and has found its most recent uses in applications such as rubber manufacturing, cement processing, and most commonly as a barrier cream used for nappy rash or diaper rash [1]. Recently, ZnO has found another use in the electronics industry for thin-film transistors. In this chapter, three distinct reasons are presented for use of this new material in electrical engineering and materials communities.

The primary motivation of any new technology is the economic impact. If a material is too cost prohibitive or too difficult to repeatedly manufacture, then it is unlikely to find funding to pursue research further. ZnO is an abundant material, found all over the world [2], and is less costly to fabricate in a low temperature process on various substrates such as amorphous glasses and plastics [3]. Also, when dealing with integrated electronics, ZnO thin-film field-effect transistors (FETs) are used in conjunction with gallium arsenide (GaAs) or silicon CMOS (complementary metal-oxide semiconductor) integrated circuits (IC's) easily at the module level.

The most recent area to use ZnO thin-film FETs is pixel selection and driver circuits [2]. ZnO is a II-VI compound semiconductor with a wide direct bandgap of 3.35 electron

volts (eV) [3]. Because of this wide band gap property, which results in transparency, ZnO thin-film FETs have found acceptance in the area of display electronics. ZnO is a viable alternative to the more expensive indium tin oxide (ITO), which is found in most commercial liquid crystal displays (LCD's), plasma display panels (PDP's), and organic light-emitting displays (OLED's) [4]. Due to its transparency, ZnO is able to overcome issues of size associated with most pixel driver circuits. Pixel driver circuits must be kept small in order to allow the pixel unobstructed access to the front of the display. Since ZnO thin-film FETs allow light to pass through them, larger ZnO transistors are used that are nearly the size of the pixel with very little loss of lumen performance within the display [5]. In addition to the ability to create more vivid pixels, the ZnO thin-film FET is a voltage controlled device, with little current leakage. Low current leakage translates into efficient pixel driver circuits that do not dissipate much current in the off state.

Finally, a large focus of this dissertation is in the area of military and consumer electronics using ZnO thin-film FETs. In addition to pixel driver circuits, an analog amplifier and a radio frequency (RF) low-noise amplifier (LNA) are designed. As previously mentioned, the ZnO thin-film FET has a large band gap of 3.35 eV. Advantages associated with wide band gaps include: high breakdown voltages, ability to sustain large electric fields, lower electronic noise, and high temperature and high power operation [6]. For these reasons, there is motivation to begin an investigation into applications for analog and RF electronics that would be beneficial to the military and consumer electronics community. An analog differential amplifier is designed to show micro-power performance and predictable gain for an all-NFET style operational

amplifier. In addition, the RF performance of the ZnO thin-film FET is demonstrated with a low-noise RF amplifier with high current density (335.5  $\mu$ A/ $\mu$ m), which translates to high power density [2]. The low-noise RF amplifier is designed in Agilent Advanced Design System® (ADS) using two-port measured scattering parameters (S-parameters) on a ZnO thin-film FET, with a gate-oxide thickness of 22 nm and a gate length of 1.25  $\mu$ m.

In conclusion, several factors are presented that have motivated the research in circuit design and fabrication of ZnO thin-film FETs for use in multiple applications. These applications are cost-effective pixel driver circuits, analog amplifiers, and lownoise RF amplifiers. As the technology improves, there are opportunities for numerous other circuit designs to develop which may benefit both consumer and military applications.

## 1.2 Research Contributions

The following are the novel research contributions of this dissertation:

1. A ZnO thin-film FET behavioral drain current and capacitance model to allow for hand design and simulation of circuit performance in the Cadence design suite. This drain current shows a fourth order dependency on gate-source overdrive voltage for "strong inversion," saturation, operation. The quartic-law behavioral model accurately tracks the measured performance to within ±1.6%. This quartic-law operation is in contrast to square-law operation for traditional bulk CMOS, without mobility reduction effects. Modeling is performed on the mobility that shows a square-law increase with gate-source overdrive voltage,

which is considered a possible source of the drain current quartic-law "strong inversion," saturation operation. Also, for the "strong inversion," non-saturation or ohmic operation, the drain current shows a gate-source overdrive voltage raised to the 2.3 power instead of unity as expected in bulk CMOS. The models are evaluated using Air Force Research Laboratory ZnO thin-film FETs having a minimal channel length of 2  $\mu$ m and a gate-oxide thickness of 30 nm. These FETs are also used for the design of pixel drivers and analog amplifier circuits.

- 2. A fabricated pixel driver, which can sink 28  $\mu$ A while having a gate area of only  $20~\mu\text{m}^2$ . This pixel driver is believed to be the smallest published with high current density (14.5  $\mu$ A/ $\mu$ m) at a low drain voltage of 2 V. This performance matches the drain current model of Chapter 3 and gives confidence for future pixel driver designs. Performance is confirmed with verilog-A simulation in the Cadence design suite.

- 3. A ZnO thin-film FET analog amplifier is analytically designed utilizing the behavioral model of Chapter 3. It is believed to be the first ZnO thin-film FET analog amplifier to be designed. The amplifier is designed to have a gain of 3 V/V at 10 kHz, with rail voltages of  $\pm$  5 V and a total current consumption of 8  $\mu$ A.

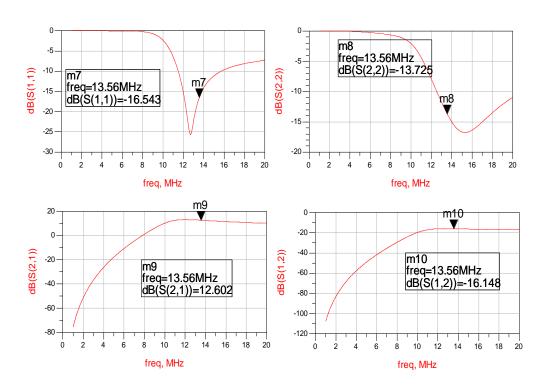

- 4. A low-noise RF amplifier is designed from scattering parameters measured at the Air Force Research Laboratory for ZnO thin-film FETs having a gate length of  $1.25~\mu m$  and a gate-oxide thickness of 22 nm. This design achieves 12.6 dB of gain while having less than 16.5 dB of input return loss, less than 13.7 dB of

output return loss and less than 16 dB of reverse isolation in a 50  $\Omega$  system. The amplifier is designed for the RFID tag frequency of 13.56 MHz.

# 1.3 Dissertation Organization

Chapter 2 gives an overview of the ZnO thin-film FET. Fabricated device layers are discussed in order to describe the operation and fabrication of the Air Force Research Laboratory (AFRL) devices used in this research. Chapter 3 describes the methodology used to extract model parameters for the ZnO thin-film FET drain current model. Model parameters are then used to create a full behavioral model of the drain current and capacitances of a ZnO thin-film FET with a gate oxide thickness of 30 nm and a gate length of 2 μm. In Chapter 4, a ZnO pixel driver circuit is designed and discussed. Measured data is collected and compared with the modeled and simulated results to show accuracy of the modeling equations. Chapter 5 presents a micro-power differential amplifier utilizing an all-NFET architecture. Design and simulation of the amplifier is discussed as it relates to the model and simulation data. Chapter 6 gives the design of a low-noise RF amplifier. Measured scattering parameters are used to simulate and design the amplifier using the newest ZnO thin-film FET technology from AFRL having 1.25 μm gate length and a gate oxide thickness of 22 nm. Finally, Chapter 7 concludes the dissertation with an overall summary and discussion of novel information discovered through this research. This chapter concludes with proposed future research for ZnO thin-film FETs. Finally, Appendix A includes the verilog-A program used to implement the ZnO thin-film FET behavioral model in the Cadence design suite with the Spectre® simulator.

#### CHAPTER 2: OPERATION OF THE ZNO THIN-FILM FET

#### 2.1 ZnO Thin-Film FET

In Chapter 1, a brief introduction of the advantages of ZnO was presented. Chapter 2 explores the fabrication of ZnO thin-film FETs, specifically Air Force Research Laboratory (AFRL) devices used in this research.

ZnO thin-film FETs have become of great interest in the electronics field due to their many advantages, such as high temperature, high power operation, and similarity in many ways to gallium-nitride (GaN) [7]. Another characteristic that is advantageous for electronic applications is the high current on/off ratio, currently greater than 10<sup>12</sup> [8]. Design of the transistors, including oxide thickness, and width and length of the channel, is very important in determining the on/off ratio, which is most important for low-leakage switching. In (2.1), a relationship is given in [9] that allows for the design of a general leakage current approximation for a ZnO thin-film FET:

$$I_{DS\ off} = \frac{\sigma W \tau}{L} V_{DS} \tag{2.1}$$

Here  $\sigma$  is the electrical conductivity,  $\tau$  is the thickness of the channel layer, W and L are the respective width and length of the conduction channel, and  $V_{DS}$  is the source-drain voltage [8]. From (2.1) it is apparent that channel thickness, width, and length must be optimized in order to provide the desired off current performance for a given source-drain voltage. Low leakage is primarily the result of the low conductivity of native ZnO.

Another advantage of the ZnO thin-film FET is the ability to have high output resistance when operating in saturation where  $V_{DS} > V_{DS,sat}$ , the drain current saturation voltage [10]. It is desirable to have high output resistance in amplifier configurations to maximize small-signal resistances and voltage gain.

Finally, as with GaN, ZnO thin-film FETs do not yet have a stable p-type FET available for complementary logic circuits. This is due to low solubility of p-type dopants and their compensation by abundant n-type impurities [11]. Previous work in [12], however, shows that a p-type material may be grown, thereby allowing for very low-power complementary logic circuits in the future. This would of course hinge upon a p-type process becoming stable for production process fabrication.

# 2.2 ZnO Thin-Film FET Operation

The understanding of possible ZnO thin-film FET accumulation operation is not conclusive. There are several theories, including the grain boundary theory, the Fermi level theory, and the ionized impurity scattering mechanism theory.

The most popular theory to date is the grain boundary theory. Due to the polycrystalline nature of ZnO channels, it is theorized that as the gate-source voltage increases, the potential of free carrier charge with respect to fixed charge increases. This increase of free carrier charge also increases the charge density of the induced free carrier, resulting in reduction of the potential barrier at the grain boundaries [13]. This is the first theory to be proposed and is still quite popular in the ZnO literature.

The second theory involves the Fermi level and carrier concentration. In [5] researchers propose that the interface states pin the Fermi level near the conduction

band, which creates an accumulation layer, at a sufficient gate-source voltage. That accumulation layer then requires a gate-source voltage below zero in order to fully turn off the device.

The last theory involves the ionized impurity scattering mechanism, which may be responsible for the accumulation operation. In [4] an experiment was conducted in which gallium was added to a ZnO channel under the assumption that the grain size would decrease and therefore would also decrease the mobility in reference to a native ZnO channel. However, this resulted in little change to the mobility and led the researchers to infer that ionized impurity scattering was responsible rather than the dominant grain-boundary mechanism theory.

# 2.3 Air-Force Research Laboratory Devices

Devices used in this work are fabricated at the Air Force Research Laboratory (AFRL) at Wright-Patterson Air Force base. An introduction to the fabrication layers of the AFRL ZnO thin-film FET is given, followed by the fabrication process parameters.

The AFRL ZnO thin-film FET fabrication layers are shown in Figure 2.1. Note that this FET design has the gate buried under the channel versus a top gate design.

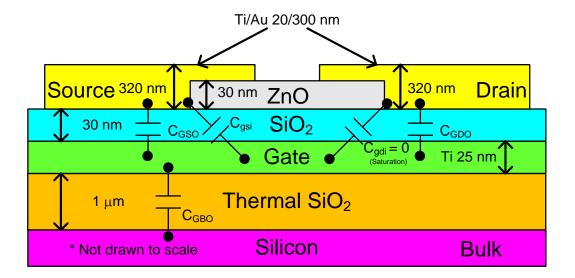

Figure 2.1. Air Force Research Laboratory ZnO thin-film FET fabrication layers (not drawn to scale) [8].

The AFRL devices are fabricated on thermally grown SiO<sub>2</sub>-covered silicon wafers [8]. ZnO films were deposited using pulsed laser deposition. The substrate is heated to 350 degrees Celsius while being rotated during deposition [8]. The bottom gate is made of titanium and is 25 nm thick. The drain and source are made of titanium/gold layers of 20 nm and 300 nm, respectively. The SiO<sub>2</sub> gate insulator is deposited using plasmaenhanced chemical vapor deposition (PECVD) to a thickness of 30 nm [8]. All annealing is done at 400 degrees Celsius. The process is outlined in Table 2.1, which lists the equipment used to complete the given step.

Measurements are taken using scattering parameters (S-parameters) to find the frequency limitations of the transistors at 2  $\mu$ m gate lengths. The  $f_T$  and  $f_{max}$  are measured to be 400 MHz and 500 MHz respectively [8]. It is estimated that when the process goes to a 1  $\mu$ m gate length,  $f_T$  and  $f_{max}$  will increase into the low GHz range.

Table 2.1. Process steps and measurements for Air Force Research Laboratory ZnO thin-film FETs [8].

| Step Descriptor                                             | Equipment                | Comments                                 |

|-------------------------------------------------------------|--------------------------|------------------------------------------|

| Intial wafer                                                | NA                       | SiO <sub>2</sub> -covered silicon wafers |

|                                                             |                          | Pulsed laser deposition                  |

|                                                             |                          | (PLD) with Krypton-Flouride              |

| ZnO film deposition                                         | Neocera Pioneer 180      | (KrF) laser                              |

|                                                             |                          | $4 \times 10^{-8}$ torr with $O_2$       |

|                                                             |                          | background gas during                    |

| Chamber base pressure                                       | chamber                  | deposition to 150 mtorr                  |

| Substrate temp at                                           |                          | 350 degrees Celsius                      |

| deposition                                                  | backside heater          | (rotated during deposition)              |

|                                                             |                          | titanium gate at 25 nm                   |

| Gate                                                        | NA                       | thick                                    |

| Gate insulator                                              | PECVD                    | 30 nm thick SiO <sub>2</sub>             |

|                                                             |                          | Class 100 clean room with                |

|                                                             |                          | 400 degrees Celsius for 10               |

|                                                             |                          | minutes                                  |

|                                                             |                          | after deposition and before              |

|                                                             |                          | source/drain contact                     |

| Annealing                                                   | NA                       | fabrication                              |

|                                                             | Agilent 4156C Precision  |                                          |

|                                                             | Semiconductor Parameter  | All dc curves taken on                   |

| DC characterization                                         | Analyzer                 | devices with an L = 2 $\mu$ m            |

|                                                             |                          | S-parameters used to                     |

| $f_{\scriptscriptstyle T}$ and $f_{\scriptscriptstyle max}$ | HP8751A Network Analyzer | determine S <sub>21</sub>                |

In conclusion, the ZnO thin-film FET fabrication process steps are presented. Each layer of the fabricated device is described and dimensions are given as these differ from standard silicon CMOS devices. The AFRL ZnO thin-film FETs discussed here are used exclusively in the remainder of this dissertation.

#### CHAPTER 3: BEHAVIORAL MODELING OF ZNO THIN-FILM FETS

This chapter describes the behavioral modeling of ZnO thin-film FETs. Behavioral models are created to describe the drain current operation, low frequency small-signal operation to include capacitance, and the RF small-signal model. Derivations and theory are used to describe how the models are created and assumptions used.

# 3.1 DC Device Modeling

#### 3.1.1 Derivation of the M value

$M_{nonsab}$  is the gate-source effective voltage power law exponent for drain current in the non-saturation region. It is determined with data from the ZnO thin-film FET in the deep ohmic region, or non-saturation region defined  $V_{DS} \ll V_{DS,sat}$ . The non-saturation data is collected with a voltage on the drain of 0.1 V.  $M_{sat}$ , is the gate-source effective voltage power law exponent for the drain current in the "strong inversion," saturation region of operation. It is determined using the saturation region, defined as  $V_{DS} \geq V_{DS,sat}$ . The "strong inversion" region is defined as  $V_{GS} - V_T > V_{EFFSI,onset}$ , where  $V_{GS} - V_T$  is the effective voltage, and  $V_{EFFSI,onset}$  is 0.5 V as observed from drain-current power law behavior versus gate-source voltage as seen later in Figure 3.1.

Before modeling ZnO thin-film FETs, a brief review of the drain-current equation for bulk CMOS is given from [14] in (3.1) for strong inversion ( $V_{GS} - V_T > 0.25 \text{ V}$ ), saturation ( $V_{DS} \ge V_{DS,sat}$ ) operation. Here the drain current is given by

$$I_D = \frac{1}{2} \cdot \mu \cdot C'_{ox} \cdot \left(\frac{W}{L}\right) \cdot (V_{GS} - V_T)^2$$

(3.1)

where  $\mu$  is the field-effect mobility,  $C'_{ox}$  is the gate capacitance per unit area, W is the width of the gate, and L is the length of the gate. In saturation,  $(V_{DS} \ge V_{DS,sat})$ , neglecting drain-source conductance,  $g_{ds}$ , effects, the drain current of a general power-law device can be expressed as

$$I_D = \left(\frac{W}{L}\right) \cdot k'_{satSI} \cdot (V_{GS} - V_T)^{M_{Sat}} \tag{3.2}$$

where

$$k'_{satSI} = constant$$

(3.3)

The transconductance  $g_m$  is found from (3.2) as

$$g_m = \frac{\delta I_D}{\delta V_{GS}} = \frac{\delta I_D}{\delta (V_{GS} - V_T)} = M_{sat} \cdot \left(\frac{W}{L}\right) \cdot k'_{satSI} \cdot (V_{GS} - V_T)^{M_{sat} - 1}$$

(3.4)

Also from equations (3.4) and (3.2) the transconductance efficiency is calculated as

$$\frac{g_m}{I_D} = \frac{M_{sat} \cdot \left(\frac{W}{L}\right) \cdot k'_{satSI} \cdot \left(V_{GS} - V_T\right)^{M_{sat} - 1}}{\left(\frac{W}{L}\right) \cdot k'_{satSI} \cdot \left(V_{GS} - V_T\right)^{M_{sat}}} = \frac{M_{sat}}{V_{GS} - V_T}$$

(3.5)

The transconductance can also be expressed as

$$g_m = \frac{g_m}{I_D} \cdot I_D = \frac{M_{sat} \cdot I_D}{V_{GS} - V_T} \tag{3.6}$$

Solving (3.2), for  $V_{GS} - V_T$  gives

$$(V_{GS} - V_T)^{M_{Sat}} = \frac{I_D}{\left(\frac{W}{L}\right) \cdot k'_{satSI}}$$

(3.7)

where

$$V_{GS} - V_T = \left(\frac{I_D}{\left(\frac{W}{L}\right) \cdot k'_{satSI}}\right)^{\frac{1}{M_{sat}}}$$

(3.8)

Substituting (3.8) into (3.6), gives another expression for the transconductance efficiency, given by

$$\frac{g_m}{I_D} = \frac{M_{sat}}{\left(\frac{I_D}{\left(\frac{W}{I_L}\right) \cdot k'_{satSI}}\right)^{\frac{1}{M_{sat}}}}$$

(3.9)

Equation (3.9) shows that  $\frac{g_m}{I_D}$  is inversely proportional to the drain current raised to the  $1/M_{sat}$  power, or

$$\frac{g_m}{I_D} \propto \frac{1}{(I_D)^{\frac{1}{M_{sat}}}} \tag{3.10}$$

Equation (3.2) shows the drain current is proportional to  $V_{GS} - V_T$  raised to the  $M_{sat}$  power, or

$$I_D \propto (V_{GS} - V_T)^{M_{Sat}} \tag{3.11}$$

Equation (3.11) shows that  $V_{GS} - V_T$  is proportional to the drain current raised to the  $\frac{1}{M_{Sat}}$  power, or

$$(I_D)^{\frac{1}{M_{Sat}}} \propto V_{GS} \tag{3.12}$$

As seen in (3.12),  $M_{sat}$  may be extracted from measured data using  $(I_D)^{\frac{1}{M_{sat}}}$  as the y-axis and  $V_{GS}$  as the x-axis. When the  $M_{sat}$  value models the performance correctly, it fits a straight line for "strong inversion," saturation operation. Assumptions are made that this performance characteristic carries over into non-saturation as well, but for a different power-law exponential,  $M_{nonsat}$ . In the following sections,  $M_{sat}$  and  $M_{nonsat}$  curve fitting is shown in a graphical format for both saturated and non-saturated conditions.

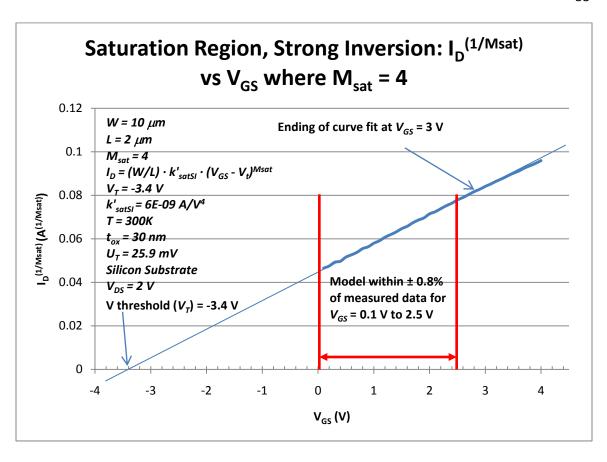

## 3.1.2 Saturation Region Modeling

To extract  $M_{sat}$ , the following conditions were used:  $V_{DS} = 2$  V and  $V_{GS} = 0.5$  V to 2.5 V, where  $V_{DS} \ge V_{DS,SAT} \approx V_{GS} - V_T$ .

Figure 3.1. Measured and modeled drain current versus gate-source voltage for "strong inversion," saturation region of operation for  $M_{sat}$  = 4,  $V_{DS}$  = 2 V. Curve fit is within ±1.6% of measured drain current for  $V_{GS}$  = -0.05 V to 2.5 V.

In Figure 3.1, the line drawn on the curve fits measured drain current within  $\pm 1.6\%$  for an  $M_{sat}$  value of 4.

Performance data of AFRL ZnO thin-film FET devices show that mobility increases as  $V_{GS}$  increases while  $V_{DS}$  is held constant. For an L=2 µm device, using a polynomial curve fit on the extracted data from [15], a mobility slope greater that unity is observed. As shown in Figure 3.2, the "strong inversion" region of operation curve fit reveals that mobility increases as the square of  $V_{GS}$  -  $V_T$ .

The mobility data in Figure 3.2 is taken with a drain voltage of 0.5 V. This puts the transistor in the ohmic region ( $V_{DS} < V_{DS,sat}$ ). For purposes of initial modeling, this ohmic region mobility is used in the saturation region. The mobility shows a square-law operation with  $V_{GS}$  -  $V_T$  and, when multiplied by a square-law FET model of (3.1) gives a consistent quartic law operation for the device drain current versus  $V_{GS}$  -  $V_T$  shown in Figure 3.1.

Figure 3.2. Measured and modeled ZnO thin-film FET mobility versus gate-source voltage at  $V_{DS}$  = 0.5 V.

The mobility has a square law operation with respect to  $V_{EFF} = V_{GS} - V_{T}$ . The mobility can be modeled by

$$\mu = \mu_{SI,onset} \left[ \frac{cm^2}{V^3 \cdot s} \right] (V_{GS} - V_T)^2 + \mu_{SI,offset} \left[ \frac{cm^2}{V \cdot s} \right]$$

(3.13)

In the mobility fitting of Figure 3.2,  $\mu_{SI,onset}$  is  $0.4 \left[ \frac{cm^2}{V^3 \cdot s} \right]$ ,  $\mu_{SI,offset}$  is  $14 \left[ \frac{cm^2}{V \cdot s} \right]$ , and  $V_T$  is -0.55 V. Based on a threshold voltage of -0.55 V, the "strong inversion" onset is believed to occur at 0.5 V effective voltage,  $(V_{GS} - V_T)$ . Equation (3.14) gives the "strong inversion" onset voltage as

$$V_{EFFSI,onset} = V_{GS} - V_T = -0.05 V - (-0.55 V) = 0.5 V$$

(3.14)

For ZnO thin-film FET "weak inversion," saturation region modeling, the bulk CMOS weak inversion, saturation region equation in (3.15) from [14] is used as an initial model.

$$I_D(WI) = 2 \cdot n \cdot \mu \cdot C'_{ox} \cdot U_T^2 \cdot \left(\frac{W}{L}\right) \cdot \left(e^{\frac{V_{GS} - V_T}{n \cdot U_T}}\right)$$

(3.15)

From this relationship in bulk CMOS, a similar drain current model is derived for ZnO thin-film FETs, where "weak inversion" is defined as  $V_{GS} - V_T < V_{EFFWI} = -0.13$  V. The "weak inversion," saturation drain current is modeled as

$$I_D(WI) = k'_{satWI} \cdot \left(\frac{W}{L}\right) \cdot \left(e^{\frac{V_{GS} - V_T}{n \cdot U_T}}\right)$$

(3.16)

where  $k'_{satWI}$  is used as the constant value for "weak inversion," saturation operation as shown in Figure 3.3.

Figure 3.3. Measured and modeled drain current versus gate-source voltage for "weak inversion," saturation region with  $V_{DS} = 2$  V. Drain current on a log scale reveals fitted exponential performance within  $\pm$  9% of measured data.

Figure 3.4 shows drain current from the "weak" to "strong inversion" regions of operation. Interestingly, the "weak inversion" and the "strong inversion" models track measured data within ±1.6% for "strong inversion," and within ±9% for "weak inversion." However, between, in "moderate inversion," both models fail to predict drain current, just as for bulk CMOS.

Figure 3.4. Measured and modeled ZnO thin-film FET drain current versus gate-source voltage from "weak" through "strong inversion."

# 3.1.3 Non-saturation Region Modeling

Equation (3.17) gives the drain current for bulk CMOS strong inversion  $(V_{GS} - V_T) \sim 0.25 \text{ V}$ , non-saturation  $(V_{DS} < V_{DS,sat})$  operation [16] as

$$I_D = \mu \cdot C'_{ox} \cdot \left(\frac{W}{L}\right) \cdot (V_{GS} - V_T) \tag{3.17}$$

Here the overdrive voltage  $(V_{GS} - V_T)$  is raised to unity, as compared to being squared for the saturation  $(V_{DS} > V_{DS,sat})$  region of operation. When referring back to the generic device equation form of (3.2), for ZnO thin-film FETs.  $M_{nonsat}$ , or the drain current power

law exponent for the non-saturation region, is extracted at 2.3, and  $V_T$  is extracted at 0.1 V. It is interesting to note that a value of  $M_{nonsat}$  = 2.3 gives a good fit, as shown in Figure 3.5, but based on the square-law characteristics of the mobility described in Chapter 2, one would assume that  $M_{nonsat}$  = 3. This suggests that more research into the device physics is required for a better understanding of ZnO thin-film FET drain current modeling. For the extraction of  $M_{nonsat}$ , shown in Figure 3.5,  $V_{DS}$  = 0.1 V,  $V_{GS}$  = 1 V to 5 V, and therefore,  $V_{DS}$  <<  $V_{DS,SAT}$ .

Figure 3.5. Measured and model drain current versus gate-source voltage for non-saturation region of operation with  $M_{nonsat}$  = 2.3 and  $V_{DS}$  = 0.1V. Curve fit is within ± 0.866% with measured data for  $V_{GS}$  = 2 V to 4 V.

# 3.2 AC Device Modeling

As with all transistors, one important aspect of modeling is the small-signal model. Small-signal analysis allows for gain calculations as well as output impedance calculations, which is very beneficial when doing power transfer efficiency calculations and RF matching.

As with bulk CMOS, in the small-signal model of Figure 3.7, the G, D, and S are correspond to the gate, drain and source, respectively. The transconductance [17], denoted as  $g_m$  is calculated for bulk CMOS in strong inversion, saturation as

$$g_m = \frac{2 \cdot I_D}{V_{GS} - V_T} \tag{3.18}$$

For the ZnO thin-film FET, measured data reveals that the transconductance is actually somewhat higher than that predicted by (3.18). Instead of multiplying the drain current by 2, the ZnO thin-film FET model multiplies the drain current by 4 using the extracted value of  $M_{sat}$  = 4. The transconductance is repeated from (3.6)

$$g_m = \frac{M_{sat} \cdot I_D}{V_{GS} - V_T} = \frac{4 \cdot I_D}{V_{GS} - V_T}$$

(3.19)

Another component is the output resistance of the device, also known as the drain-source resistance  $r_{ds}$ . As seen in [18], the output resistance is often modeled using an Early voltage,  $V_A$ , and the drain current  $I_D$ . This gives [18]

$$r_{ds} = \frac{1}{g_{ds}} = \frac{V_A + V_{DS}}{I_D} \approx \frac{V_A}{I_D}$$

(3.20)

Where the Early voltage  $V_A$  is represented as the inverse of the channel-length modulation factor  $\lambda$  as

$$V_A = \frac{1}{\lambda} \tag{3.21}$$

A graphical representation of how the Early voltage is extracted from drain current versus  $V_{DS}$  curve trace data is shown in Figure 3.6 according to [18]. Using the  $I_D$  versus  $V_{DS}$  curves of multiple  $V_{GS}$  values, a continuation line may be drawn from the saturation region portions of the curve to intersect the x-axis at a point known to be the negative of the Early voltage. The slope of those continuation lines is also known as the output impedance,  $r_{dS}$ .

Figure 3.6. The graphical method of extracting the Early voltage.

For the purposes of this dissertation, the Early voltage is extracted to be 20 V for  $L = 2 \mu m$  AFRL devices as referenced from [15].

Another important part of any AC small-signal model is the capacitances associated with the transistor, required to ascertain the frequency response of the device. It also becomes important when preparing for circuit design, which is the purpose of this work.

Figure 3.7 gives a small-signal model for ZnO thin-film FETs. As part of the bottom-gate configuration, a gate-body overlap capacitor is modeled.

Figure 3.7. Small-signal model for the ZnO thin-film FET including capacitances as adapted from [19, p. 98].

Figure 3.8 gives a picture of where each capacitance forms with each layer of fabrication. The gate-drain intrinsic capacitor,  $C_{gdi}$ , is listed, but is considered to be 0 as the model is for saturation conditions where the drain is assumed pinched off.

Figure 3.8. Fabrication layers with capacitances drawn for illustration of Figure 3.7 [8].

The first capacitance that is crucial for calculation is known as the gate oxide capacitance per unit area,  $C'_{ox}$  [19, p. 41].  $C'_{ox}$  is calculated in (3.22), which includes a convenient expression from [19, p. 41].

$$C'_{ox} = \frac{\varepsilon_{SiO_2}}{t_{ox}} = \frac{34.5 \ fF}{\mu m^2} \left(\frac{1 \ nm}{30 \ nm}\right) = 1.15 \ \frac{fF}{\mu m^2}$$

(3.22)

Here  $\varepsilon_{SiO_2}$  is the permittivity of silicon-dioxide which is used as the gate-oxide and  $t_{ox}$  is the thickness of the gate oxide, which is 30 nm for the AFRL ZnO thin-film FETs used in this research.

The total gate-oxide capacitance,  $C_{GOX}$  is given by

$$C_{GOX} = W \cdot L \cdot C'_{ox} \tag{3.23}$$

Assumptions are made in this modeling that intrinsic capacitance values are similar to that of bulk CMOS operating in strong inversion, saturation. In (3.24), the intrinsic gate-source capacitance is given for a ZnO thin-film FET in "strong inversion," saturation.

$$C_{gsi} \approx (^{2}/_{3}) \cdot W \cdot L \cdot C'_{ox} \tag{3.24}$$

The intrinsic gate-drain capacitance is assumed zero due to operation in the saturation region where the drain is pinched off [16]. There is no gate to bulk intrinsic capacitance assumed for the devices.

In (3.25), the gate-drain overlap capacitance is calculated, followed by the gate-source overlap capacitance in (3.26) and the gate-body overlap capacitance in (3.27). The gate-body overlap capacitance is included in this work due to the bottom-gate fabrication shown in Figure 3.8. The overlap capacitances are given by

$$C_{GDO} = A_D \cdot C'_{ox} \tag{3.25}$$

$$C_{GSO} = A_S \cdot C'_{OX} \tag{3.26}$$

$$C_{GBO} = W \cdot L \cdot C'_{oxsub} \tag{3.27}$$

$$C'_{oxsub} = \frac{\varepsilon_{SiO_2}}{t_{ox}} = \frac{34.5 \ fF}{\mu m^2} \left( \frac{1 \ nm}{1000 \ nm} \right) = 34.5 \cdot 10^{-3} \ \frac{fF}{\mu m^2}$$

(3.28)

$A_D$  is the area under the drain,  $A_S$  is the area under the source, and  $C'_{oxsub}$  is the capacitance per unit area of the gate with respect to the substrate. In the calculation of  $C'_{oxsub}$  value, an oxide thickness ( $t_{ox}$ ) of 1  $\mu$ m or 1000 nm is used as seen in Figure 3.8.

Table 3.1. Example set of ZnO thin-film FET small-signal parameter values.

| Transistors | Symbol              | Unit             | Value  |

|-------------|---------------------|------------------|--------|

| Example     | $I_D$               | μΑ               | 19.53  |

| Example     | $V_{GS}$            | V                | 0.7    |

| Example     | $V_T$               | V                | -0.55  |

| Example     | $V_{\it EFF}$       | V                | 1.25   |

| Example     | W                   | μm               | 200    |

| Example     | L                   | μm               | 2      |

| Example     | k'                  | A/V <sup>4</sup> | 80E-09 |

| Example     | n                   |                  | 1      |

| Example     | $V_A$               | V                | 20     |

| Example     | $g_m$               | μS               | 62.5   |

| Example     | r <sub>ds</sub>     | ΜΩ               | 1.02   |

| Example     | t <sub>ox</sub>     | nm               | 30     |

| Example     | t <sub>oxsub</sub>  | nm               | 1000   |

| Example     | C'ox                | fF/μm²           | 1.15   |

| Example     | C' <sub>oxsub</sub> | fF/μm²           | 0.035  |

| Example     | $C_{GOX}$           | fF               | 460    |

| Example     | $C_{gsi}$           | fF               | 306.67 |

| Example     | $C_{GDO}$           | fF               | 690    |

| Example     | C <sub>GSO</sub>    | fF               | 690    |

| Example     | $C_{GBO}$           | fF               | 3.45   |

Table 3.1 gives an example set of values for the small-signal analysis of a ZnO thin-film-FET utilizing the equations for the entire Section 3.2 of this Chapter.

It is important to note that the extrinsic overlap capacitances for this device are actually much larger than the intrinsic capacitances, therefore dominating the frequency response in circuit applications. The drain and source dimensions are 200  $\mu$ m by 3  $\mu$ m to give an area of 600  $\mu$ m<sup>2</sup>.

### 3.3 RF Device Modeling

In preparation for any radio frequency (RF) design, probe testing is typically done on the wafer of the transistors before dicing and packaging. During that wafer probing, scattering parameters (S-parameters) are taken that allow the designer to understand how the device operates at high frequencies (RF frequencies). These scattering parameters are a measurement of how an applied voltage signal is either reflected ( $S_{11}$  and  $S_{22}$ ) or passed through the device ( $S_{21}$  and  $S_{12}$ ). The  $S_{11}$  parameter is the ratio of the reflected to incident voltage on port 1 of the device. The  $S_{22}$  is the same definition, but on port 2 of the device. The  $S_{21}$  parameter is known as the forward gain or ratio of port 2 output voltage to port 1 input voltage. The  $S_{12}$  is known as the reverse isolation of the device or ratio of port 1 voltage resulting from an applied voltage on port 2. In most RF devices it is undesirable for the output port to couple a signal to the input port. That is why the  $S_{12}$  measurement is made.

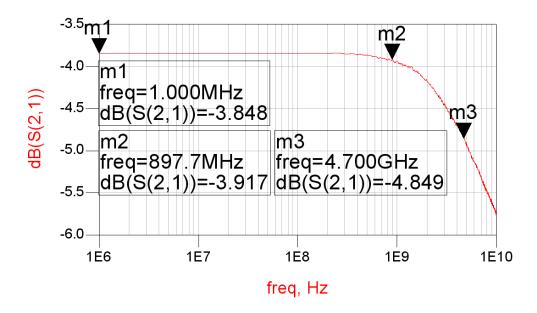

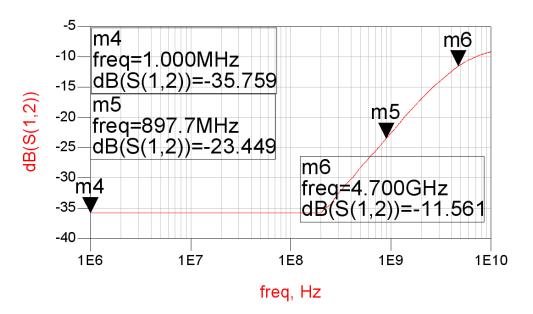

Figure 3.9. Non-matched S<sub>21</sub> showing the intrinsic gain flatness of the ZnO thin-film FET.

For the AFRL RF ZnO thin-film FETs, a base measurement was taken at the AFRL using a probe station and a vector network analyzer (VNA). For a single transistor, with 50 ohms being presented to the gate and drain of the FET the following S-parameters were taken and used to create an RF model of operation for the device. The AFRL ZnO thin-film FET used for RF S-parameter measurements had a  $W=100~\mu m$ ,  $L=1.25~\mu m$ ,  $I_D=33.55~m$ A,  $V_{DS}=13~V$ ,  $V_{GS}=9.5~V$ , and a  $t_{OX}=22~n$ m.

Notice the forward gain shown by  $S_{21}$  in Figure 3.9 of the device is less than 0 dB, which likely means that both the input and output of the device prefer to see impedances other than 50 ohms at the present biasing levels. In this case, the device was measured with 50 ohm probes. Three frequencies are marked for example

purposes. A low frequency value of 1 MHz to show the highest gain of the unmatched device, a recorded frequency of 897.7 MHz, a common cellular frequency, and a 1 dB roll-off frequency of 4.7 GHz, which shows the likely limit of usable bandwidth from a theoretical perspective. Once the device is matched for a lower frequency, this frequency will typically provide far more loss from the filtering attributes of the matching network.

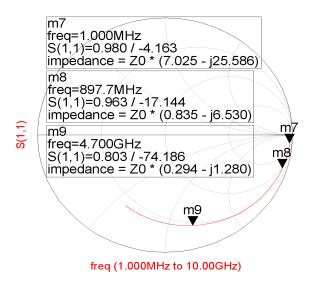

A Smith chart is a useful tool for converting values such as voltage reflections,  $(S_{11} \text{ and } S_{22})$ , to real and imaginary impedance values if the characteristic impedance  $(Z_o)$  is known. In Figure 3.10, the input impedance is given on a Smith chart by plotting the reflection data and converting to an impedance,  $Z_o = 50~\Omega$  system at the required frequency of design. The Smith chart is a graphical representation of both real and imaginary impedance values of an RF system. All input impedances are seen to have a large amount of capacitance with a series resistive component. This large capacitive value will require inductance as part of a matching network to convert the input impedance of the ZnO thin-film FET toward the characteristic impedance for maximum power transfer.

Figure 3.10. Input impedance sweep of the device to show the impedance of the gate at varying frequencies.

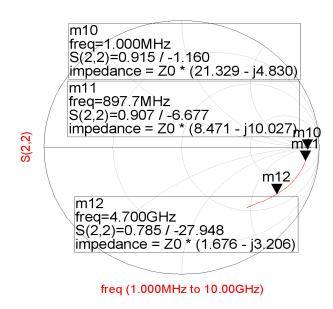

Figure 3.11. Output impedance sweep on the drain of the ZnO thin-film FET to show the drain impedance at given frequencies.

Figure 3.11 shows the output impedance sweep at the drain of the device. This measurement is very useful in determining how a device is matched for different applications. For RF amplifiers such as low noise amplifier's (LNA's) or gain blocks operating at very low power, the output is matched to 50 ohms as needed to achieve the proper noise figure or gain. In the case of a power amplifier, however, the output is purposefully matched away from 50 ohms in an attempt to succeed in some tradeoff of efficiency and output power, or in the case of a linear power amplifier, the tradeoff would be linearity and efficiency. In whatever application it may be, the output impedance sweep is instrumental in assisting the RF engineer in the creation of an output matching network to efficiently transfer power to the load.

Figure 3.12. S<sub>12</sub> showing the reverse isolation of the ZnO thin-film FET.

Most RF amplifiers must be designed to attenuate unwanted signals at the output port to the input port. For this reason, the  $S_{12}$  plot shown in Figure 3.12 is created to check for any unintended reverse amplification.

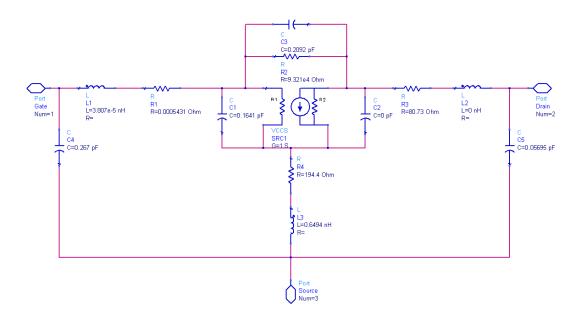

From the previous S-parameter measurements from an actual ZnO thin-film FET, a lumped-element RF device model was created using Agilent ADS software. Figure 3.13 shows this model.

Figure 3.13. Lumped-element RF model for ZnO thin-film FET from S-parameter measurements [2].

### CHAPTER 4: DESIGN AND EVALUATION OF A ZNO THIN-FILM FET PIXEL DRIVER

This chapter utilizes the modeling of Chapter 3 to design pixel driver circuits with ZnO thin-film FETs. For the design of the pixel driver circuit, test transistors were laid out separately from the circuit in order to take I-V curves to confirm the models used in the design of the circuit.

### 4.1 ZnO Thin-Film FET Modeling Extraction

For this AFRL fabrication run, a process shift occurred that causes the previous model parameters used to design the circuits from Chapter 3 to be incorrect for this run. The extracted "strong inversion," saturation threshold voltage shifted to a value of -3.4 V from a previous value of -0.55 V. This shift in  $V_T$  has effects on the pixel driver design, and a re-evaluation of the design biasing was performed to achieve the desired current sourcing capabilities.

Figure 4.1 shows how this threshold voltage was extracted as performed in Chapter 3. From this extraction, the threshold voltage is then used to extract the  $k'_{satSI}$  constant. It is interesting to note that although a process shift occurred, the  $M_{sat}$  value remained 4.

Figure 4.1. Threshold voltage and current constant extraction for ZnO thin-film FETs used in fabricated pixel drivers.

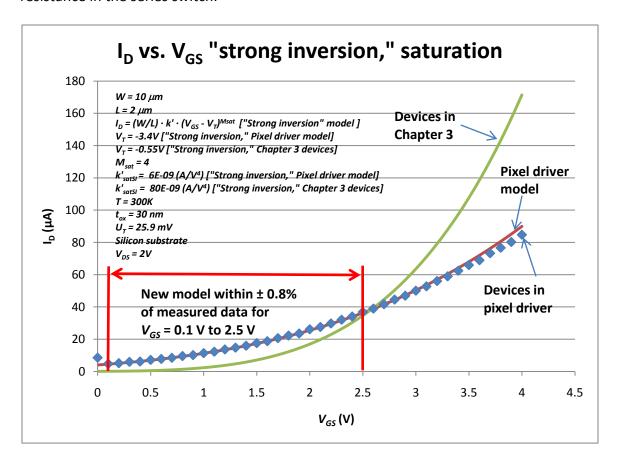

After completion of the  $V_T$  and  $k'_{satSI}$  extraction in Figure 4.1, a comparison is created in Figure 4.2 that shows the accuracy of the updated model parameters. Also, the deviation from the previous model is plotted to display the  $V_T$  shift that occurred. As observed, the extraction of  $V_T = -3.4$  V and  $k'_{satSI} = 6 \times 10^{-9}$  A/V<sup>4</sup> for the pixel driver run gives considerably different modeling compared to  $V_T = -0.55$  V and  $k'_{satSI} = 80 \times 10^{-9}$  A/V<sup>4</sup> extracted for a previous run in Figure 3.1. Such a large shift in those two parameters could be a result of damage done to the pixel driver transistors at some time after leaving AFRL.

From the new and complete model of the single ZnO thin-film FET in Figure 4.2, analysis of the pixel driver circuit allows for a closer approximation of the series on resistance in the series switch.

Figure 4.2. Analysis of the deviation from Chapter 3 model parameters and updated model parameters for fabricated ZnO thin-film FET pixel driver.

# 4.2 Applications of ZnO Thin-Film FET Pixel Drivers

The liquid crystal display (LCD) is a mainstay in both portable and large electronics. This leads to numerous branches of research looking for more efficient and effective ways to increase contrast ratios, pixel brightness, and longevity of displays. These displays are located in certain items such as LCD televisions (TVs) and portable displays for smart phones. Due to the latest advances in light emitting diode (LED)

technology, a new LED known as an organic LED (OLED) is a very popular choice for many manufacturers of displays. However, because of the nature of the OLED, its pixel brightness is directly controlled by the amount of current that is passed through it [20]. This requires a pixel driver transistor that has both the capability to deliver the required current and not block the light being emitted by the display. Currently, amorphous silicon driver circuits are used to provide the current to drive OLED displays. Since amorphous silicon transistors are not transparent, they need to be made small with high voltages to enable the correct amount of current drive [5].

A natural solution for the need of high current and high transparency is the ZnO thin-film FET. The ZnO thin-film FET has high mobility, high transparency in the visible wavelength of light, and most importantly, is very compatible with inexpensive plastic substrates [12]. With the transparent nature of the ZnO thin-film FET, it is possible to use a larger FET than with amorphous silicon transistors to provide the same amount of current drive [5]. This allows for lower voltage rails, which leads to less total power consumption.

# **4.3 Circuit Description**

Two ZnO thin-film FET pixel driver configurations are selected and fabricated. For the purposes of this dissertation, they are named the single-transistor and selectable pixel driver.

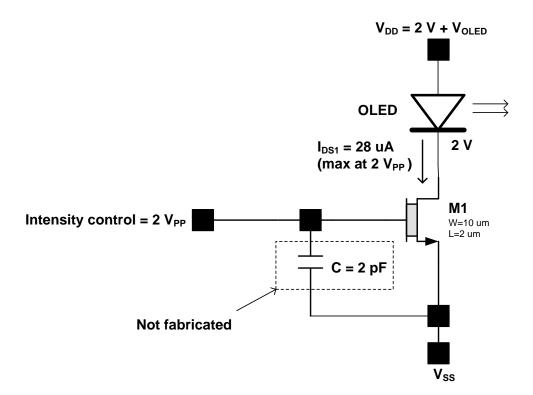

The simplest of the two circuit configurations is the single-transistor pixel driver with schematic shown in Figure 4.3. As the name states, the single-transistor pixel driver contains only one ZnO thin-film FET and drives the OLED without additional circuitry.

This is the simplest solution and has the advantage of increased contrast ratio because of the smaller size from fewer transistors in the driver circuit allowing for smaller pixels. It also will have a higher yield than a circuit with more transistors [20].

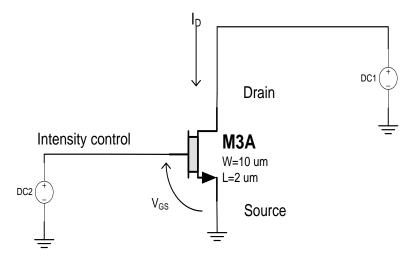

Figure 4.3. Single-transistor ZnO thin-film FET pixel driver schematic.

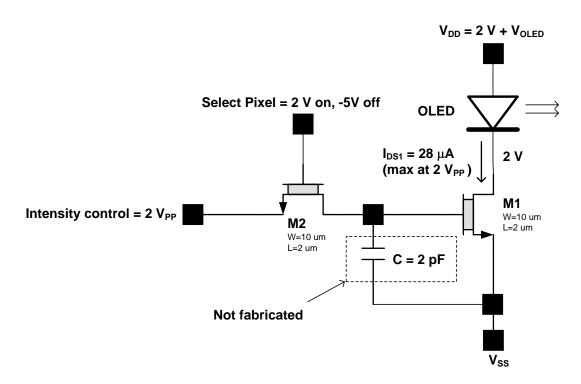

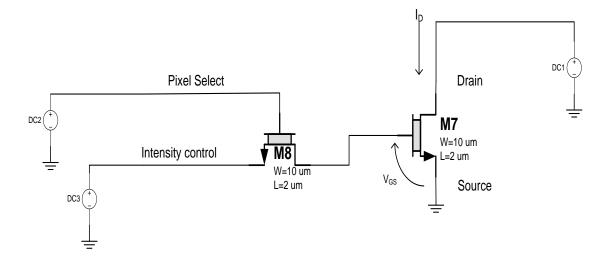

Slightly more complex is the selectable pixel driver shown in Figure 4.4. The selectable pixel driver has an additional series switch that allows the selection of the pixel driver for such applications as a multiplexed control line scheme as presented in [21].

Figure 4.4. Selectable ZnO thin-film FET pixel driver schematic.

For both the single-transistor and selectable pixel driver, a capacitor is used in the end application to hold a charge on the gate of the driver transistor in order to hold the control voltage, (the intensity voltage shown in Figures 4.3 and 4.4) during the frame delay [22].

# 4.4 Analysis and Design

The design of the single-transistor pixel driver circuit is presented first. The selectable pixel driver is then presented, building upon the single pixel driver design. Using (3.2) to find the drain current, a device size of 10  $\mu$ m wide by 2  $\mu$ m long is selected to provide a total gate area of 20  $\mu$ m<sup>2</sup>. As of this writing, the smallest operational ZnO pixel driver transistor gate area is 100  $\mu$ m<sup>2</sup> [13]. Once the size is selected, proper voltage biasing is required to ensure appropriate current capability to drive the OLED. In this

design,  $V_{DS}$  = 2 V and  $V_{GS}$  = 2V are used to provide 28  $\mu$ A to the OLED by using the modeling equations of Chapter 3, with the model parameters extracted in Figure 4.1. The 28  $\mu$ A value came from the need to supply current to a 20  $\mu$ m x 20  $\mu$ m OLED pixel. Since the average current necessary to produce a bright display is approximately 10 mA/cm² [20], a steady current of 0.04  $\mu$ A is required. If it is assumed that there are 400 address lines and only one line is active at any one given time, the current needed is 16  $\mu$ A (400 · 0.04  $\mu$ A), to make a pixel shine brightly during the entire duty cycle. Margin is added due to the infancy of this process in case the mobility is less than originally expected. Figure 4.5 gives a schematic diagram of the single transistor pixel driver with bias and sizing details.

Figure 4.5. Single-transistor ZnO thin-film FET pixel driver designed for a 20  $\mu m$  x 20  $\mu m$  OLED pixel.

From the single-pixel design, the selectable pixel driver adds the series ZnO thinfilm FET switch that is used for a matrix-style display to select the pixel from a multiplexed controller. The selectable pixel driver schematic is shown in Figure 4.6.

Figure 4.6. Selectable ZnO thin-film FET pixel driver designed for a 20  $\mu$ m x 20  $\mu$ m OLED pixel.

In Figure 4.6, the current flow seen through device M2 is assumed to be very small (only M1 gate leakage and capacitor leakage). Therefore the circuits of Figure 4.5 and 4.6 for both circuits perform identically because of identical gate voltage passing to the gate of M1 for both circuits. All calculations take into account that the actual supply voltage will need to be higher than 2 V above the voltage drop across the OLED. For display purposes, the gate capacitor is in the schematic at 2 pF, but it is not fabricated in the prototypes evaluated.

# 4.5 Design Simulations

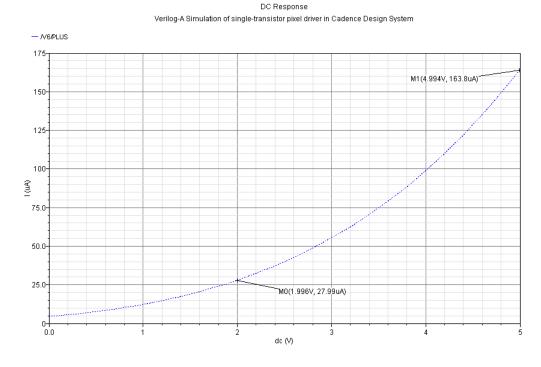

Preparing for design simulations, the modeling from Chapter 3 with the modeling parameters of Figure 4.1 are used for both the single-transistor and selectable pixel driver circuits. For each circuit, both a spreadsheet mathematical model and a verilog-A model are created and used to guide the design efforts. The verilog-A model found in Appendix A, is simulated in the Cadence design suite.

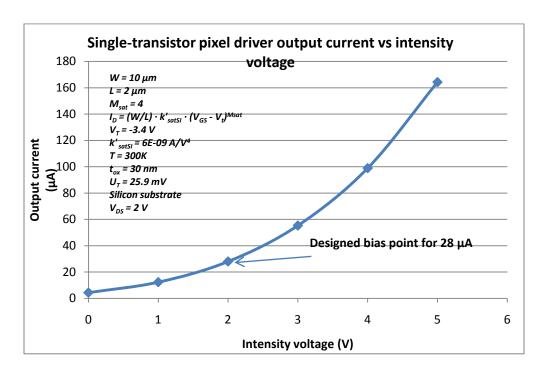

For each of the circuits, (3.2) is used with  $k'_{satSl} = 6\text{E-}09 \text{ A/V}^4$  and a threshold voltage  $V_T = -3.4 \text{ V}$  to complete the model variables. As mentioned, the sizing of M1 is  $W = 10 \text{ }\mu\text{m}$  and  $L = 2 \text{ }\mu\text{m}$  as also shown in Figure 4.1.

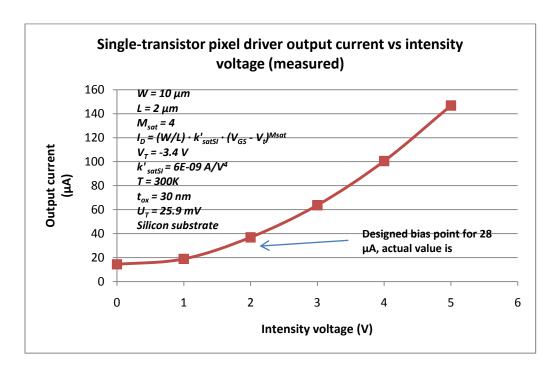

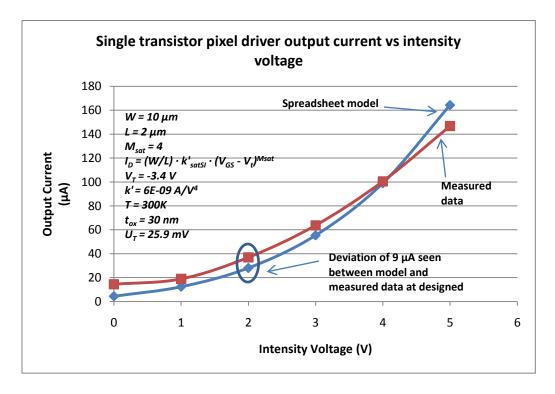

Figures 4.7 and 4.8 show the simulated drive current performance from a spreadsheet mathematical model and a verilog-A model, respectively, for the single-transistor pixel driver. In Figures 4.7 and 4.8, the ZnO thin-film FET is capable of delivering much more current than the required 28  $\mu$ A. For both the spreadsheet and verilog-A model, greater than 160  $\mu$ A is achievable for an intensity voltage of 5 V if required by a specific OLED.

Figure 4.7. Spreadsheet drive current model data for single-transistor ZnO thin-film FET pixel driver design.

Figure 4.8. Verilog-A drive current model data for single-transistor ZnO thin-film FET pixel driver design.

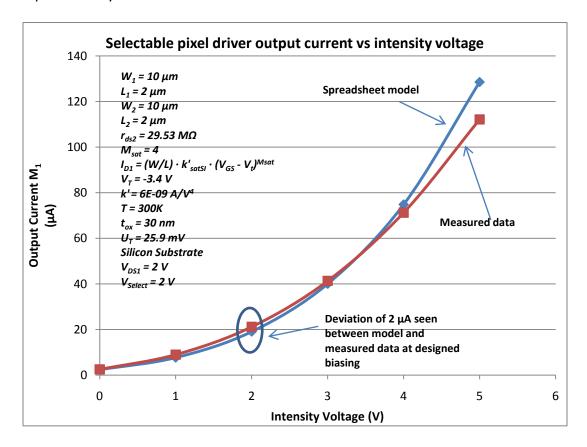

Figures 4.9 and 4.10 show the spreadsheet and verilog-A drive current model data for the selectable pixel driver circuit design. This model includes the unexpected loss observed with the series select switch (M2) used in a matrix display control configuration. The drain-source (switch) resistance is calculated from the non-saturation drain current given in Figure 3.5 and the operating  $V_{GS}$  of 0.4 V for M2 from measured data. A voltage drop across M2 is proof of gate leakage in M1, which may support the assumption of damage in the pixel driver transistors. The switch resistance is

$$r_{ds} = \frac{1}{k'_{nonsat} \cdot \left(\frac{W}{L}\right) \cdot (V_{GS} - V_T)^{m_{nonsat}}}$$

$$= \frac{1}{\left(1.08 E - 07 \left(\frac{A}{V^{2.3}}\right)\right) \cdot \left(\frac{10 \mu m}{2 \mu m}\right) \cdot (0.4 V - 0.1 V)^{2.3}} = 29.53 M\Omega$$

Figure 4.9. Spreadsheet drive current model data for selectable ZnO thin-film FET pixel driver design.

In the spreadsheet model used for Figure 4.9, the observed series switch loss must be included for accuracy. From the single-transistor pixel driver, the output current drops from 28 µA to 19 µA since the intensity voltage is dropped across the series switch. As a result, with the highest intensity voltage of 5V, the selectable pixel driver gives a current output just below 130 µA, which is 30 µA below the single-pixel driver circuit in Figure 4.7. According to the verilog-A simulation results shown in Figure 4.10, at an intensity voltage of 5 V, the switch loss is actually higher resulting in 86 μA, which is far below that of the spreadsheet model across the M2 switch. Experimental measurements showed a voltage drop across the M2 switch indicating current into the gate of M1. This performance is not completely understood and is modeled with a simple resistive divider for the verilog-A model and a 0.4 V drop in the spreadsheet model. The verilog-A model is adjusted with the resistive divider to model measured performance at the designed biasing. If the verilog-A simulations are done with only a series switch, then the performance is identical to the single-transistor verilog-A simulation. No gate leakage is expected since no gate leakage modeling is included in the verilog-A model. As previously mentioned, this measurement of gate leakage may be the result of damage to the device.

Figure 4.10. Verilog-A drive current model data for selectable ZnO thin-film FET pixel driver design.

# 4.6 Experimental Evaluation

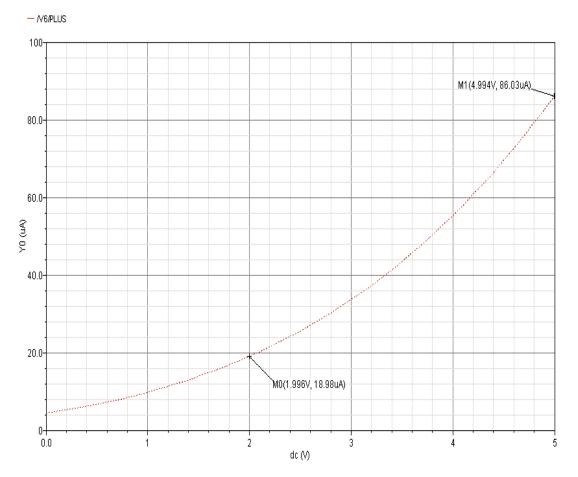

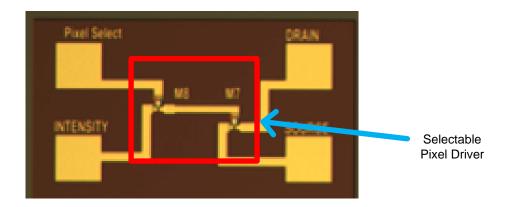

Photomicrographs of the final fabricated pixel driver circuits are shown in Figures 4.11 and 4.12. Figure 4.11 shows the single-transistor pixel driver, and Figure 4.12 shows the selectable pixel driver. Both were fabricated at the Air Force Research Laboratory (AFRL).

Figure 4.11. Photomicrograph of fabricated single-transistor ZnO thin-film FET pixel driver circuit.

Figure 4.12. Photomicrograph of fabricated selectable ZnO thin-film FET pixel driver circuit.

Testing of each circuit consisted of essentially an identical setup. The only difference being the additional power supply required to drive the pixel select input on the selectable pixel driver circuit. Each test setup is shown in Figures 4.13 and 4.14 for the single transistor pixel driver and selectable pixel driver, respectively.

Figure 4.13. Single-transistor ZnO thin-film FET pixel driver test circuit.

Figure 4.14. Selectable ZnO thin-film FET pixel driver test circuit.

Figures 4.15 and 4.16 show the measured drive current for the ZnO thin-film FET pixel driver circuits.

Figure 4.15. Measured data for single-transistor ZnO thin-film FET pixel driver design.

As seen in Figure 4.15, the actual current delivered at the designed operating bias point is 37  $\mu$ A compared to 28  $\mu$ A predicted by the modeling in Figure 4.7.

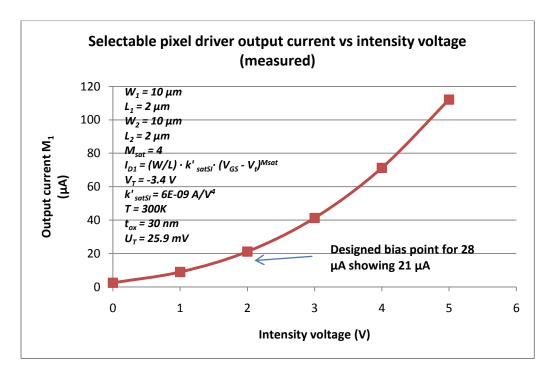

Figure 4.16. Measured data for selectable ZnO thin-film FET pixel driver design.

As with the drive current in Figure 4.15, the measured drive current in Figure 4.16 deviates from the modeled values, but this time in the opposite direction with a lower than expected measured output current of 21  $\mu$ A compared to 28  $\mu$ A predicted by the modeling. The measured device current at 21  $\mu$ A compared to 37  $\mu$ A for the single-transistor design suggests significant voltage drop across the M2 switch.

## 4.7 Comparison of Modeled and Measured Results

In this section, both measured and modeled performance of the single-transistor pixel driver and the selectable pixel driver are presented. Figure 4.17 compares the measured and modeled current of the single-transistor pixel driver. In Figure 4.17 the modeled current clearly follows the same shape and trend as the measured current, but the measured current is above the modeled current for intensity voltages below 4 V.

Figure 4.17. Measured and modeled drive current for the single-transistor ZnO thin-film FET pixel driver circuit.

Figure 4.18 compares the measured and modeled current of the selectable pixel driver. Here, the increase in measured current compared to modeled current is partially compensated by switch losses mentioned earlier.

Figure 4.18. Measured and modeled drive current for the selectable ZnO thin-film FET pixel driver circuit.

# 4.8 Summary and Conclusions

The pixel driver circuit designs are not novel in nature, but do display improved current density over previously published work. Their performance is compared to previously published results in Table 4.1.

| Table 4.1. Comparison of current densit publications. | y (I <sub>D</sub> /\ | <i>N</i> ) be | tweer          | n this   | work           | and previous    |

|-------------------------------------------------------|----------------------|---------------|----------------|----------|----------------|-----------------|

|                                                       | W                    | L             | V <sub>D</sub> | $V_{GS}$ | I <sub>D</sub> | Current Density |

|                                                       | (µm)                 | (µm)          | (V)            | (V)      | (μΑ)           | (μA/μm)         |

|                                                  | W    | L    | $V_D$ | $V_{GS}$ | I <sub>D</sub> | Current Density |

|--------------------------------------------------|------|------|-------|----------|----------------|-----------------|

|                                                  | (µm) | (µm) | (V)   | (V)      | (μΑ)           | (μA/μm)         |

| Single transistor pixel driver "this work"       |      | 2    | 2     | 2        | 37             | 3.7             |

| Selectable pixel driver "this work"              |      | 2    | 2     | 2        | 21             | 2.1             |

| D. Redinger, et. al. [5]                         |      | 10   | 5     | ??       | 5              | 0.005           |

| T. Hirao, et. al. [13]                           |      | 10   | 10    | 40       | 129            | 12.9            |

| Single transistor pixel driver (max) "this work" |      | 2    | 2     | 5        | 145            | 14.5            |

Note that the pixel drivers presented here achieve comparable current density as reported in [13], but at  $V_{GS}$  = 5 V compared to  $V_{GS}$  = 40 V in [13]. One point that requires emphasis is that the measured pixel driver circuits were measured with a much smaller  $k'_{satSI}$  (13.3 times smaller) than their predecessors measured at the AFRL in Chapter 3. However, the  $V_T$  is also shifted to a -3.4 V from a 0.5 V expectation during design. The parameter changes could translate into even higher current density if fabricated as designed. The change in current density is shown in

Current density change =

$$\left(\frac{V_{GS(pixel)} - V_{T(pixel)}}{V_{GS(AFRL)} - V_{T(AFRL)}}\right)^4 \cdot \left(\frac{k'_{satSI(pixel)}}{k'_{satSI(AFRL)}}\right)$$

$$= \left(\frac{5 V - (-3.4 V)}{5 V - 0.5}\right)^4 \cdot \left(\frac{6 \times 10^{-9} \, A/V^4}{80 \times 10^{-9} \, A/V^4}\right) = 9\% \, \text{change}$$

(4.2)

which results in an expected 9% increase in current density if fabricated as designed. Because of the measured M1 gate leakage, threshold voltage shift, and  $k'_{satSI}$  shift, a second fabrication is planned. The second fabrication will further investigate the current density of the ZnO thin film FET pixel driver circuits.

In conclusion, two separate pixel driver circuits using ZnO thin-film FETs were designed, fabricated, and evaluated show an appropriate application for the technology. The ZnO thin-film FET is shown to provide an appropriate amount of current for an OLED or other display pixel for use in TV displays and portable hand-held device displays. In the future, with more stable processes, ZnO thin-film FETs should be replacements for the amorphous silicon thin-film transistors as display drivers for the information and entertainment display markets.

### CHAPTER 5: DESIGN OF A ZNO THIN-FILM FET ANALOG AMPLIFIER

In this chapter, an analog amplifier is designed to demonstrate the amplification capabilities of an all-NFET amplifier circuit made with ZnO thin-film FETs. This design is calculated based upon the modeling work completed in Chapter 3. The capacitive modeling work is used to simulate frequency response of the ZnO thin-film FET analog amplifier. The initial amplifier design was done by advisor, Dr. David Binkley.

### **5.1 Circuit Description and Transistor Parameters**

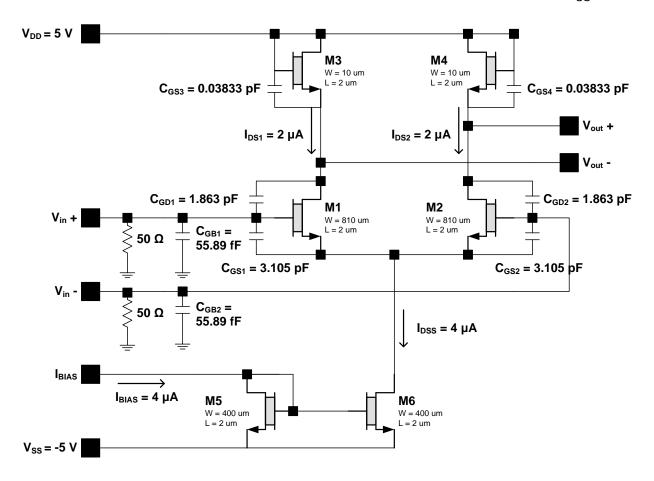

This section describes the analog amplifier architecture and gives some insight on the design process. Figure 5.1 shows the all-NFET analog amplifier design used for this research. The two active load transistors, M3 and M4, are wired with a diode connection in order to maintain saturation operation, where  $V_{DS} = V_{GS} > V_{DS,sat}$ . The differential pair, M1 and M2, is biased to maintain a certain level of transconductance for a designed small-signal gain. The current mirror, M5 and M6, is set for a 1 to 1 ratio, for easier fabrication and measurement. Also, with a 1 to 1 ratio in the current source,  $I_{BJAS} = I_{DSS}$ , and  $I_{DSS} = I_{DS1} + I_{DS2}$ .

The entire circuit is designed for fully differential operation and dual rail voltages,  $V_{DD} = -V_{SS}$  for less biasing circuitry on the input gates of the differential pair. The ground or 0 V bias voltage on the input differential pair allows for easy measurements.