# PRODUCTIVELY SCALING HARDWARE DESIGNS OVER INCREASING RESOURCES USING A SYSTEMATIC DESIGN ANALYSIS APPROACH

by

# Andrew Gregory Schmidt

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2011

| Approved by:          |

|-----------------------|

| Dr. Ronald R. Sass    |

| Dr. James M. Conrad   |

| Dr. Bharat Joshi      |

| Dr. Ryan Adams        |

| Dr. Shannon Schlueter |

© 2011 Andrew Gregory Schmidt ALL RIGHTS RESERVED

## ABSTRACT

ANDREW GREGORY SCHMIDT. Productively scaling hardware designs over increasing resources using a systematic design analysis approach.

(Under the direction of DR. RONALD R. SASS)

As processor development shifts from strict single core frequency scaling to heterogeneous resource scaling two important considerations require evaluation. First, how to design systems with an increasing amount of heterogeneous resources, and second, how to maintain a designer's productivity as the number of possible configurations grows. Therefore, it is necessary to determine what useful information can be gathered from existing designs to help predict or identify a design's potential scalability, as well as, identifying which routine tasks can be automated to improve a designer's productivity. Moreover, once this information is collected, how can this information be conveyed to the designer such that it can be used to increase overall productivity when implementing the design over increasing amounts of resources?

This research looks at various approaches to analyze designs and attempts to distribute an application efficiently across a heterogeneous cluster of computing resources through the use of a Systematic Design Analysis flow and an assortment of productivity tools. These tools provide the designer with projections on the amount of resources needed to scale an existing design to a specified performance, as well as, projecting the performance based on a specified amount of resources. This is accomplished through the combination of static HDL profiling, component synthesis resource utilization, and runtime performance monitoring. For evaluation, four case studies are presented to demonstrate the proposed flow's scalability on a small scale cluster of FPGAs. The results are highly favorable, providing orders of magnitude speedup with minimal intervention from the designer.

# ACKNOWLEDGMENTS

I would like to thank everyone who has knowingly (or unknowingly) given me advice, support, encouragement, hope, laughter, and caffeine. Throughout it all I have been blessed with inspiring professors, brilliant peers, amazing friends, and a wonderfully loving family. I hope that someday I might be able to express my deepest gratitude for all that you have shared with me.

To the army of graduate students in the RCS lab (Will, Scott, Robin, Shanyuan, Siddhartha, Ashwin, Yamuna, Bin, Rahul, Shweta, and countless others) it has been a real pleasure to work with you, learn from you, and spend countless late nights together, waiting for systems to synthesize.

To my committee, I am grateful for the many hours you have taken to help advise me. From the words of encouragement while passing in the hallway to the detailed discussions regarding my research and my future plans, you have helped me stay focused, positive, and moving forward.

Certainly, none of this would have been possible without my advisor. Ron, even with a Cambrian Explosion of synonyms for the qualities you possess, I could not thank you enough or express my appreciation for all that you have done for me. I am honored that you are my advisor and I am thrilled to call you my friend.

Of course having such a supportive family helps too. Greg, Bonnie, Matt, Rachel, Chuck, Linda, and Tyler, family does not get much better than this! Without you all I would not have gotten started.

Hilary, you made this feel easy. Without you this would not have mattered.

# TABLE OF CONTENTS

| LIST O | F TAB   | BLES                                       | 2  |

|--------|---------|--------------------------------------------|----|

| LIST O | F FIGU  | URES                                       | xi |

| LIST O | F ABB   | BREVIATIONS                                | XV |

| CHAPT  | ΓER 1:  | INTRODUCTION                               | 1  |

| 1.1    | Field   | Programmable Gate Arrays                   | 4  |

| 1.2    | Produ   | activity Tools                             | (  |

| 1.3    | Thesis  | s Statement                                | 8  |

| CHAPT  | ΓER 2:  | BACKGROUND                                 | 10 |

| 2.1    | Field-  | Programmable Gate Array                    | 10 |

|        | 2.1.1   | Function Generators                        | 11 |

|        | 2.1.2   | Storage Elements                           | 13 |

|        | 2.1.3   | Logic Cells                                | 13 |

|        | 2.1.4   | Logic Blocks                               | 15 |

|        | 2.1.5   | Special-Purpose Function Blocks            | 17 |

| 2.2    | Hardy   | vare Description Languages                 | 25 |

|        | 2.2.1   | VHDL                                       | 26 |

|        | 2.2.2   | Verilog                                    | 27 |

| 2.3    | Xilinx  | Integrated Software Environment            | 28 |

|        | 2.3.1   | Xilinx Synthesis Tool                      | 28 |

|        | 2.3.2   | Netlist Builder                            | 32 |

|        | 2.3.3   | Map                                        | 34 |

|        | 2.3.4   | Place and Route (PAR)                      | 35 |

|        | 2.3.5   | Configuration Bitstream Generation         | 36 |

| 2.4    | Recon   | figurable Computing Cluster                | 37 |

| 2.5    | Spirit' | 's Integrated On-Chip and Off-Chip Network | 36 |

|       |                            |                                          | Vl  |  |

|-------|----------------------------|------------------------------------------|-----|--|

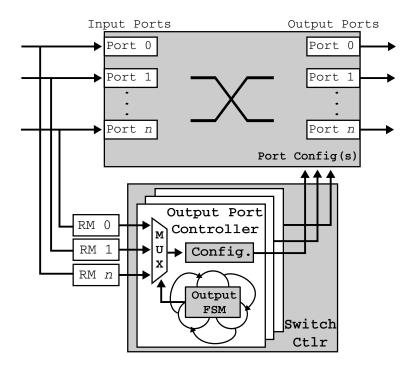

|       | 2.5.1                      | AIREN Router                             | 41  |  |

|       | 2.5.2                      | AIREN Interface                          | 42  |  |

|       | 2.5.3                      | AIREN Routing Module                     | 43  |  |

|       | 2.5.4                      | AIREN Switch Controller                  | 44  |  |

|       | 2.5.5                      | On-Chip/Off-Chip Network Integration     | 45  |  |

|       | 2.5.6                      | AIREN Resource Utilization               | 46  |  |

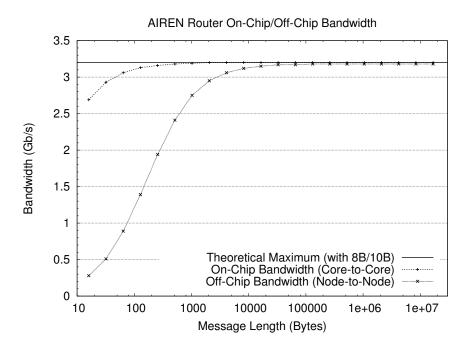

|       | 2.5.7                      | AIREN Performance                        | 47  |  |

| CHAPT | TER 3:                     | RELATED WORK                             | 51  |  |

| 3.1   | High I                     | Performance Reconfigurable Computing     | 51  |  |

| 3.2   | Existin                    | ng Methods for Scaling Designs           | 55  |  |

| 3.3   | Produ                      | ctivity Tools                            | 57  |  |

| 3.4   | Perfor                     | mance Monitoring                         | 59  |  |

| CHAPT | CHAPTER 4: DESIGN          |                                          | 60  |  |

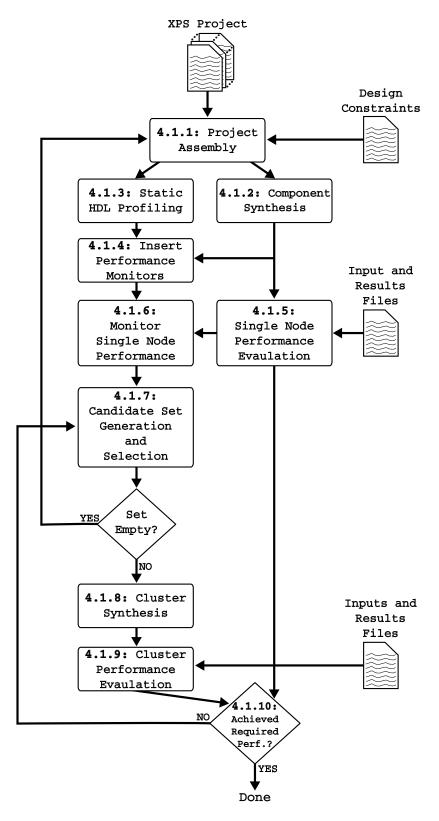

| 4.1   | Systematic Design Analysis |                                          | 61  |  |

|       | 4.1.1                      | Project Assembly                         | 61  |  |

|       | 4.1.2                      | Component Synthesis                      | 66  |  |

|       | 4.1.3                      | Static HDL Profiling                     | 70  |  |

|       | 4.1.4                      | Insertion of Performance Monitors        | 74  |  |

|       | 4.1.5                      | Single Node Performance Evaluation       | 79  |  |

|       | 4.1.6                      | Monitor Single Node Performance          | 80  |  |

|       | 4.1.7                      | Candidate Set Generation and Selection   | 84  |  |

|       | 4.1.8                      | Cluster Synthesis                        | 94  |  |

|       | 4.1.9                      | Cluster Performance Evaluation           | 95  |  |

|       | 4.1.10                     | Performance Analysis                     | 97  |  |

| 4.2   | Tool I                     | Development                              | 98  |  |

|       | 4.2.1                      | Generate Systems Tool                    | 98  |  |

|       | 4.2.2                      | Performance Monitor Recommendataion Tool | 100 |  |

|       |        |                                        | vi  |

|-------|--------|----------------------------------------|-----|

|       | 4.2.3  | PLB Replicate PCORE Tool               | 101 |

| 4.3   | HDL :  | Profiling                              | 103 |

|       | 4.3.1  | Memory Interfaces                      | 103 |

|       | 4.3.2  | Network Interfaces                     | 104 |

|       | 4.3.3  | Latency Sensitivity                    | 104 |

|       | 4.3.4  | Resource Utilization                   | 105 |

| 4.4   | Perfor | rmance Monitor Infrastructure          | 105 |

|       | 4.4.1  | Overview                               | 105 |

|       | 4.4.2  | Networks in Monitoring Infrastructure  | 106 |

|       | 4.4.3  | System Monitor Hub                     | 108 |

|       | 4.4.4  | Context Interface                      | 109 |

|       | 4.4.5  | Performance Monitor Hub                | 110 |

|       | 4.4.6  | Performance Monitor Cores              | 111 |

| СНАРТ | TER 5: | EVALUATION METHODOLOGY                 | 118 |

| 5.1   | Evalua | ation Infrastructure                   | 119 |

|       | 5.1.1  | Xilinx ML410                           | 119 |

|       | 5.1.2  | Xilinx ML510                           | 119 |

|       | 5.1.3  | Xilinx XUPV5                           | 120 |

| 5.2   | System | matic Design Analysis Flow Evaluation  | 120 |

|       | 5.2.1  | Project Assembly                       | 122 |

|       | 5.2.2  | Component Synthesis                    | 122 |

|       | 5.2.3  | Single Node Performance Evaluation     | 123 |

|       | 5.2.4  | Static HDL Profiling                   | 123 |

|       | 5.2.5  | Insertion of Performance Monitors      | 123 |

|       | 5.2.6  | Monitor Single Node Performance        | 124 |

|       | 5.2.7  | Candidate Set Generation and Selection | 124 |

|       | 5.2.8  | Cluster Synthesis                      | 125 |

|       |          |                                        |     | viii |

|-------|----------|----------------------------------------|-----|------|

|       | 5.2.9    | Cluster Performance Evaluation         |     | 125  |

|       | 5.2.10   | Performance Analysis                   |     | 125  |

| 5.3   | Evalua   | ation with Applications                |     | 126  |

| CHAPT | ΓER 6: . | ANALYSIS                               |     | 128  |

| 6.1   | Case S   | Study: Matrix-Matrix Multiplication    |     | 128  |

|       | 6.1.1    | Design                                 |     | 129  |

|       | 6.1.2    | Implementation                         |     | 134  |

|       | 6.1.3    | Results and Analysis                   |     | 138  |

|       | 6.1.4    | Observations and Summary               |     | 143  |

| 6.2   | Case S   | Study: Basic Local Alignment Search To | ool | 145  |

|       | 6.2.1    | Design                                 |     | 147  |

|       | 6.2.2    | Implementation                         |     | 154  |

|       | 6.2.3    | Results and Analysis                   |     | 162  |

|       | 6.2.4    | Observations and Summary               |     | 171  |

| 6.3   | Case S   | Study: Smith/Waterman Algorithm        |     | 171  |

|       | 6.3.1    | Design                                 |     | 173  |

|       | 6.3.2    | Implementation                         |     | 175  |

|       | 6.3.3    | Results and Analysis                   |     | 183  |

|       | 6.3.4    | Observations and Summary               |     | 188  |

| 6.4   | Case S   | Study: Collatz Conjecture              |     | 190  |

|       | 6.4.1    | Design                                 |     | 192  |

|       | 6.4.2    | Implementation                         |     | 194  |

|       | 6.4.3    | Results and Analysis                   |     | 201  |

|       | 6.4.4    | Observations and Summary               |     | 209  |

| 6.5   | System   | natic Design Analysis Flow Evaluation  |     | 211  |

| 6.6   | Functi   | onal Analysis                          |     | 216  |

|       | 6.6.1    | Matrix-Matrix Multiplication           |     | 218  |

|                       |                                   | ix  |

|-----------------------|-----------------------------------|-----|

| 6.6.2                 | Basic Local Alignment Search Tool | 219 |

| 6.6.3                 | Smith/Waterman Algorithm          | 219 |

| 6.6.4                 | Collatz Conjecture                | 220 |

| CHAPTER 7: CONCLUSION |                                   | 221 |

| REFERENCES            |                                   | 224 |

# LIST OF TABLES

| TABLE 2.1: | AIREN resource utilization (V4FX60)                                  | 47  |

|------------|----------------------------------------------------------------------|-----|

| TABLE 2.2: | largest 32-bit full crossbar switch possible in $15\%$ of the device | 47  |

| TABLE 2.3: | hardware send/receive latency through one hop                        | 48  |

| TABLE 2.4: | node-to-node latency with AIREN router                               | 49  |

| TABLE 4.1: | sample system utilization output from Parse Report tool              | 69  |

| TABLE 4.2: | sample output in table form of FSM Profiler                          | 83  |

| TABLE 4.3: | system monitor request commands                                      | 109 |

| TABLE 4.4: | resource utilization of CIF                                          | 109 |

| TABLE 4.5: | system and performance monitor hubs resources                        | 111 |

| TABLE 5.1: | Xilinx ML410 development board resources                             | 120 |

| TABLE 5.2: | Xilinx ML510 development board resources                             | 121 |

| TABLE 5.3: | Xilinx XUPV5 development board resources                             | 121 |

| TABLE 6.1: | resource utilization of MMM hardware core (V4FX60)                   | 135 |

| TABLE 6.2: | performance of original MMM core with programmable $\mathrm{I/O}$    | 139 |

| TABLE 6.3: | performance of bus based MMM core with DMA                           | 140 |

| TABLE 6.4: | performance using Cannon's algorithm                                 | 142 |

| TABLE 6.5: | summary of Matrix-Matrix Multiplication case study                   | 144 |

| TABLE 6.6: | original BLAST hardware resource utilization (V4FX60)                | 156 |

| TABLE 6.7: | databases used in experiments                                        | 164 |

| TABLE 6.8: | query (1) 248 (2) 4,292 and (3) 14,216 bytes number of hits          | 164 |

| TABLE 6.9: | tree topology speedup comparisons                                    | 167 |

| TABLE 6.10 | : summary of BLAST case study                                        | 172 |

| TABLE 6.11 | : performance monitor results for PLB SLV IPIF                       | 179 |

| TABLE 6.12 | : databases used in evaluation of Smith/Waterman core                | 183 |

| TABLE 6.13 | : resource utilization of Smith/Waterman configurations (V4FX60)     | 186 |

|                                                                | xi  |

|----------------------------------------------------------------|-----|

| TABLE 6.14: summary of Smith/Waterman case study               | 191 |

| TABLE 6.15: Collatz Core resource utilization (V4FX60)         | 195 |

| TABLE 6.16: PLB bus and bridge resource utilization comparsion | 204 |

| TABLE 6.17: summary of Collatz Conjecture case study           | 212 |

| TABLE 6.18: Project Assembly stage                             | 214 |

| TABLE 6.19: Component Synthesis stage                          | 214 |

| TABLE 6.20: Single Node Performance Evaluation stage           | 214 |

| TABLE 6.21: Static HDL Profiling stage                         | 215 |

| TABLE 6.22: Insertion of Performance Monitors stage            | 215 |

| TABLE 6.23: Monitor Single Node Performance stage              | 216 |

| TABLE 6.24: Candidate Set Generation and Selection stage       | 216 |

| TABLE 6.25: Cluster Synthesis stage                            | 216 |

| TABLE 6.26: Cluster Performance Evaluation stage               | 217 |

| TABLE 6.27: Performance Analysis stage                         | 217 |

|                                                                |     |

# LIST OF FIGURES

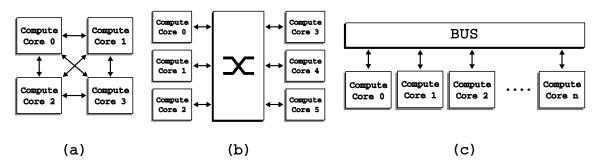

| FIGURE 1.1:  | compute core connectivity example                      | 2  |

|--------------|--------------------------------------------------------|----|

| FIGURE 1.2:  | compute core memory interface example                  | 3  |

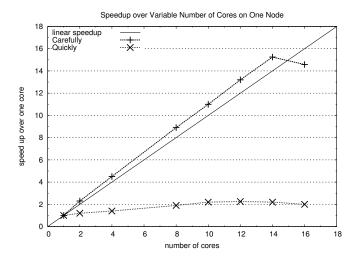

| FIGURE 1.3:  | sample speedup performance comparison of two designs   | 5  |

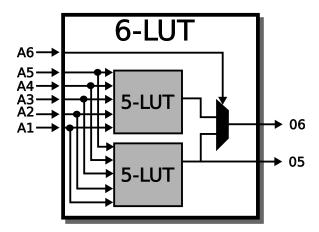

| FIGURE 2.1:  | Virtex 5's six input LUT block diagram                 | 12 |

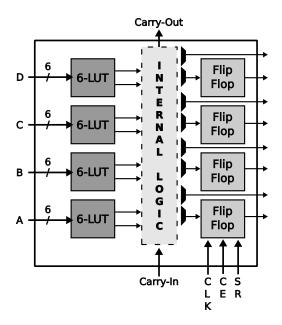

| FIGURE 2.2:  | Virtex 5's slice block diagram                         | 15 |

| FIGURE 2.3:  | Virtex 5's CLB block diagram                           | 16 |

| FIGURE 2.4:  | high-level view of a Platform FPGA                     | 18 |

| FIGURE 2.5:  | Virtex 5's PowerPC 440 block diagram                   | 19 |

| FIGURE 2.6:  | Virtex 5's IOB block diagram                           | 22 |

| FIGURE 2.7:  | Virtex 5's clock regions block diagram                 | 24 |

| FIGURE 2.8:  | sample synthesis script for XST                        | 29 |

| FIGURE 2.9:  | sample XST synthesis final report                      | 30 |

| FIGURE 2.10: | sample XST synthesis device summary report             | 31 |

| FIGURE 2.11: | sample XST synthesis timing report                     | 31 |

| FIGURE 2.12: | Xilinx synthesis flow                                  | 32 |

| FIGURE 2.13: | Xilinx implementation flow                             | 36 |

| FIGURE 2.14: | Spirit cluster block diagram                           | 39 |

| FIGURE 2.15: | 64 node Spirit cluster at UNC Charlotte                | 40 |

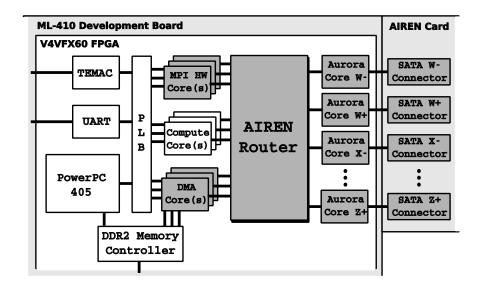

| FIGURE 2.16: | typical base system configuration                      | 40 |

| FIGURE 2.17: | AIREN router block diagram                             | 41 |

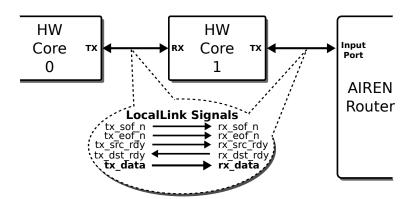

| FIGURE 2.18: | Xilinx LocalLink standard block diagram                | 43 |

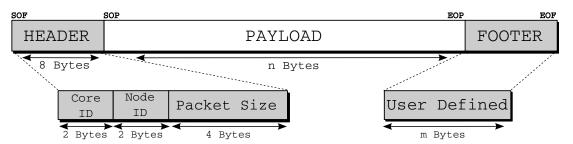

| FIGURE 2.19: | AIREN packet structure                                 | 44 |

| FIGURE 2.20: | AIREN network card                                     | 46 |

| FIGURE 2.21: | AIREN's measured bandwidth with hardware based routing | 49 |

| FIGURE 4.1:  | systematic design analysis tool flow                   | 62 |

|              |                                                              | xiii |

|--------------|--------------------------------------------------------------|------|

| FIGURE 4.2:  | file hierarchy created by Generate Systems tool              | 64   |

| FIGURE 4.3:  | sample output of Parse Report tool                           | 69   |

| FIGURE 4.4:  | VHDL Parser Python data structure declarations               | 71   |

| FIGURE 4.5:  | sample output of VHDL Parser tool                            | 72   |

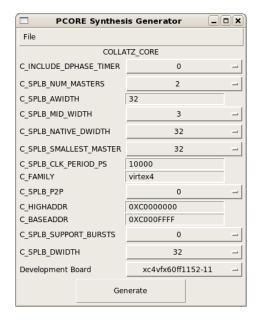

| FIGURE 4.6:  | Parse PCORE Synthesis Generator GUI                          | 74   |

| FIGURE 4.7:  | sample output of Performance Monitor Recommendation tool     | 76   |

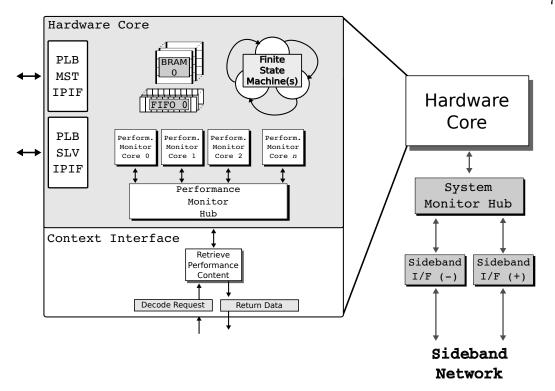

| FIGURE 4.8:  | block diagram of inserted performance monitor infrastructure | 77   |

| FIGURE 4.9:  | example of VHDL instance for FSM Profiler Monitor            | 78   |

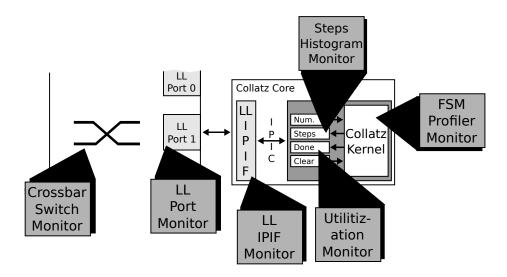

| FIGURE 4.10: | example of performance monitors inserted in Collatz Core     | 79   |

| FIGURE 4.11: | generated perf_core C struct                                 | 82   |

| FIGURE 4.12: | generated PLB slave IPIF C struct                            | 83   |

| FIGURE 4.13: | generated C FSM profiler C struct                            | 83   |

| FIGURE 4.14: | sample output of PLB slave IPIF monitor                      | 84   |

| FIGURE 4.15: | sample of MHS created by Bus Master to DMA tool              | 92   |

| FIGURE 4.16: | central DMA controller block diagram                         | 93   |

| FIGURE 4.17: | sample commands used during Cluster Evaluation stage         | 96   |

| FIGURE 4.18: | code snippet for Genreate Systems tool                       | 99   |

| FIGURE 4.19: | code snippet for Performance Monitor Recommend tool          | 101  |

| FIGURE 4.20: | code snippet of the PLB Replicate PCORE tool                 | 102  |

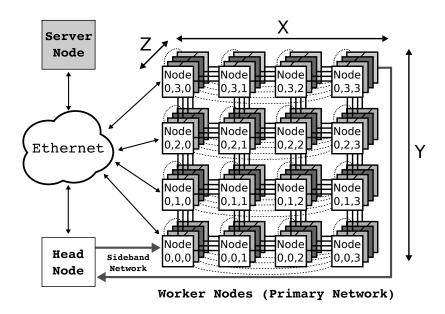

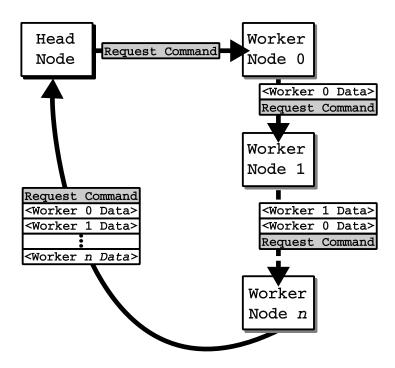

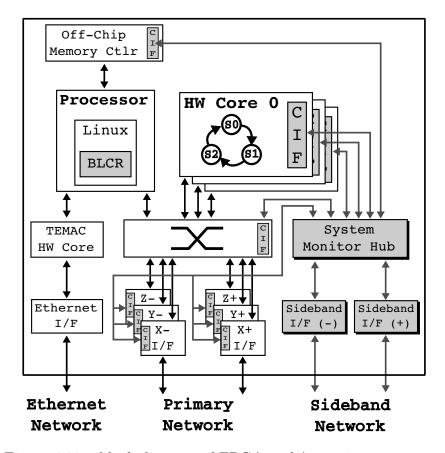

| FIGURE 4.21: | nodes and networks in cluster                                | 106  |

| FIGURE 4.22: | dataflow diagram on monitor's sideband ring network          | 107  |

| FIGURE 4.23: | block diagram of FPGA node's monitoring system               | 108  |

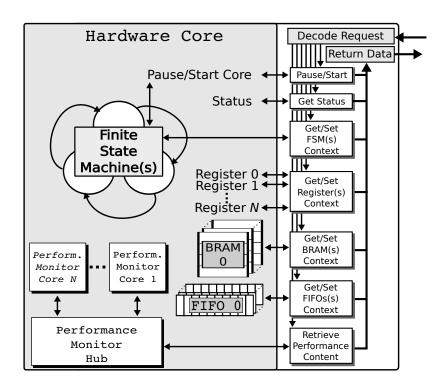

| FIGURE 4.24: | block diagram of hardware core and its CIF                   | 110  |

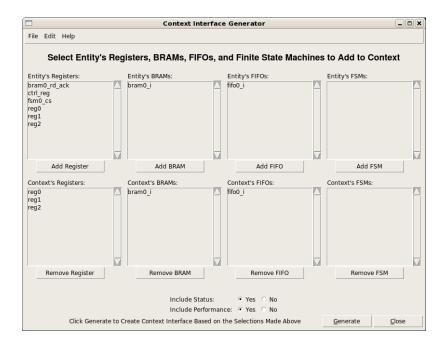

| FIGURE 4.25: | Context Interface Generator GUI                              | 111  |

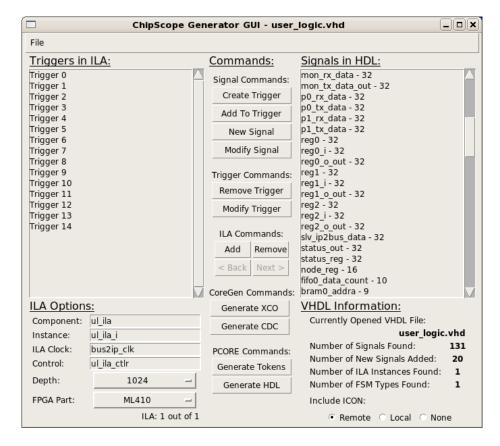

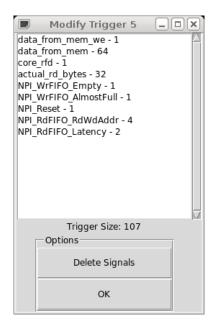

| FIGURE 4.26: | custom ChipScope ILA insertion GUI                           | 113  |

| FIGURE 4.27: | custom ChipScope modify trigger GUI                          | 114  |

| FIGURE 6.1:  | matrix-matrix multiplication                                 | 129  |

|              |                                                          | xiv |

|--------------|----------------------------------------------------------|-----|

| FIGURE 6.2:  | matrix-matrix multiplication in C                        | 129 |

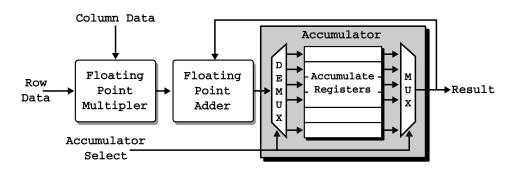

| FIGURE 6.3:  | single precision multiply accumulate unit                | 130 |

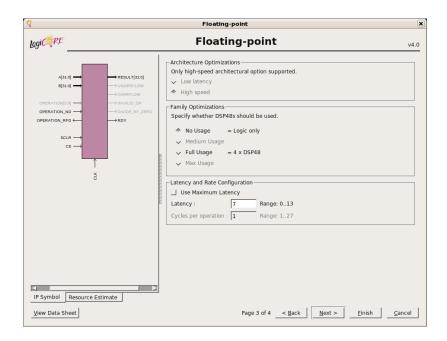

| FIGURE 6.4:  | sample SP FP adder Xilinx CoreGen MMM parameters         | 131 |

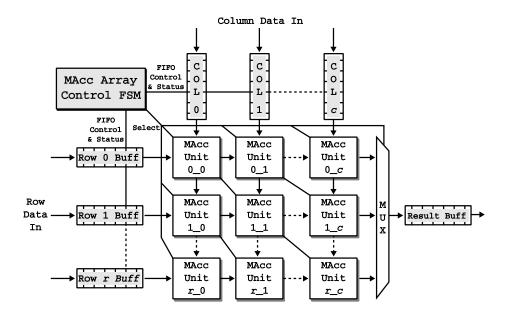

| FIGURE 6.5:  | a variable sized array of MAcc units                     | 132 |

| FIGURE 6.6:  | VHDL code snippet of MAcc Array                          | 132 |

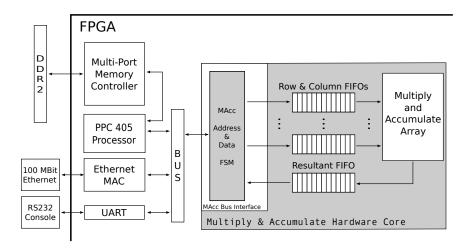

| FIGURE 6.7:  | block diagram of MMM core's programmable I/O system      | 133 |

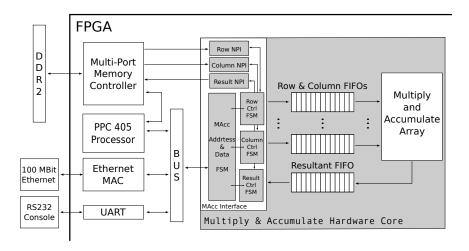

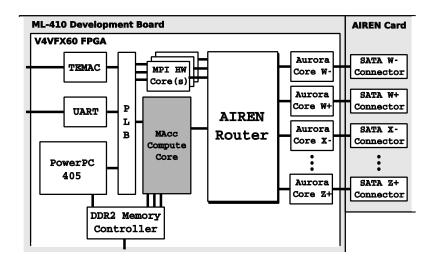

| FIGURE 6.8:  | MAcc array fast Ethernet candidate configuration         | 137 |

| FIGURE 6.9:  | MAcc array AIREN candidate configuration                 | 138 |

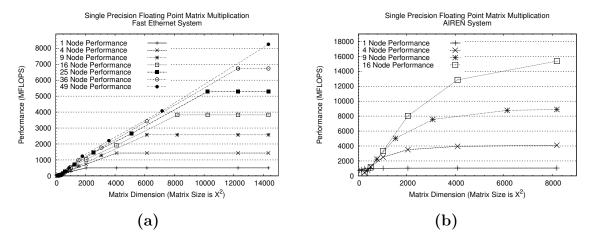

| FIGURE 6.10: | MMM performance of network configurations                | 141 |

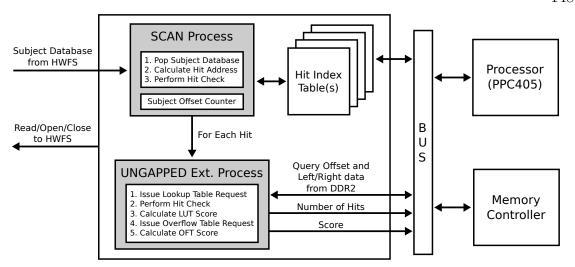

| FIGURE 6.11: | functional overview of the BLAST core                    | 148 |

| FIGURE 6.12: | dataflow of tree topology                                | 150 |

| FIGURE 6.13: | tree topology's head node                                | 150 |

| FIGURE 6.14: | tree topology's disk node                                | 151 |

| FIGURE 6.15: | tree topology's BLAST intermediate node                  | 152 |

| FIGURE 6.16: | tree topology's BLAST leaf node                          | 153 |

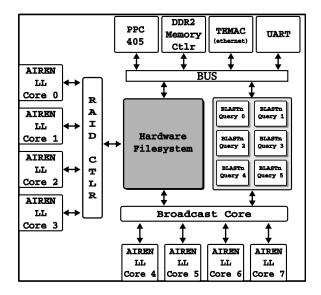

| FIGURE 6.17: | torus topology implemented on Spirit cluster             | 159 |

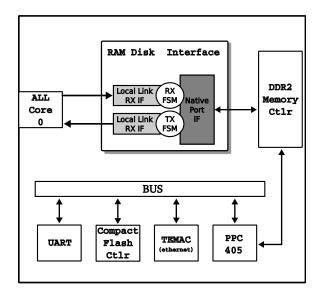

| FIGURE 6.18: | torus topology's head node                               | 160 |

| FIGURE 6.19: | torus topology's disk node                               | 161 |

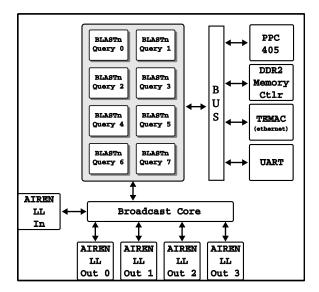

| FIGURE 6.20: | torus topology's BLAST node                              | 162 |

| FIGURE 6.21: | dataflow of torus topology configuration                 | 163 |

| FIGURE 6.22: | tree topology speedup comparisons                        | 166 |

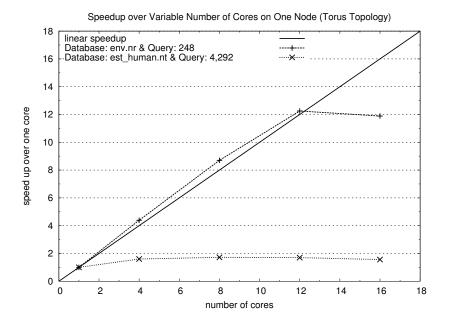

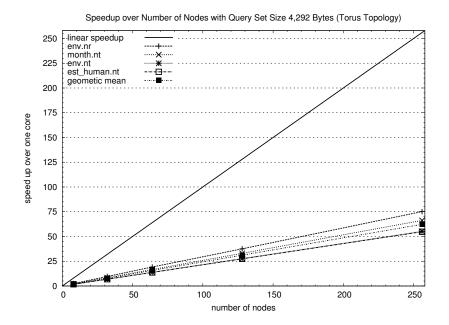

| FIGURE 6.23: | torus topology speedup comparisons                       | 168 |

| FIGURE 6.24: | torus topology with eight BLAST cores                    | 169 |

| FIGURE 6.25: | torus topology with eight BLAST cores speedup comparison | 170 |

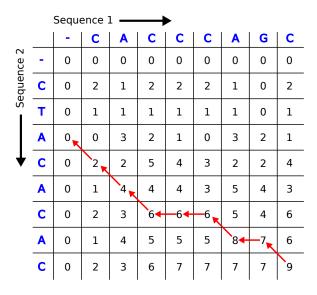

| FIGURE 6.26: | example of Smith/Watern alignment                        | 172 |

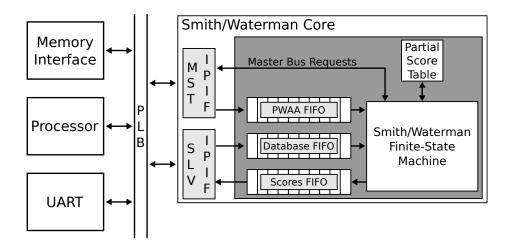

| FIGURE 6.27: | Smith/Waterman core top-level entity block diagram       | 173 |

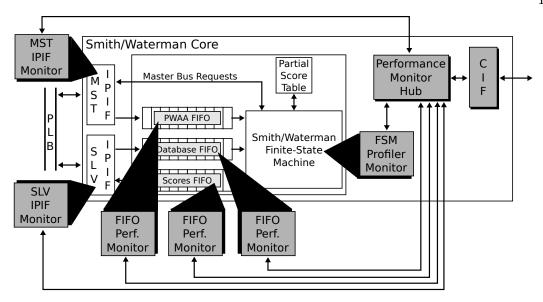

| FIGURE 6.28: | Smith/Waterman core's performance monitors               | 177 |

|              |                                                          |     |

|              |                                                            | XV  |

|--------------|------------------------------------------------------------|-----|

| FIGURE 6.29: | modification made to original dropgsw2.c                   | 179 |

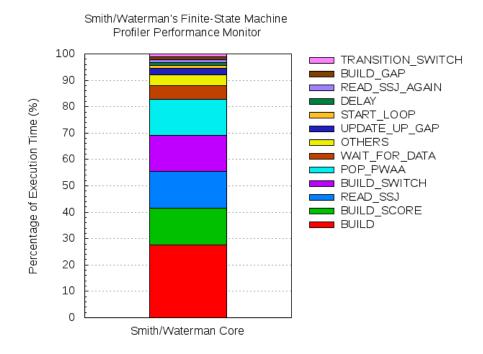

| FIGURE 6.30: | Smith/Waterman core's FSM profiler monitor results         | 182 |

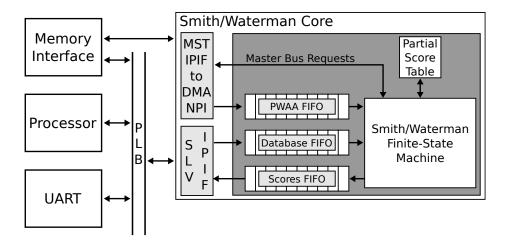

| FIGURE 6.31: | Smith/Waterman core's DMA interface                        | 183 |

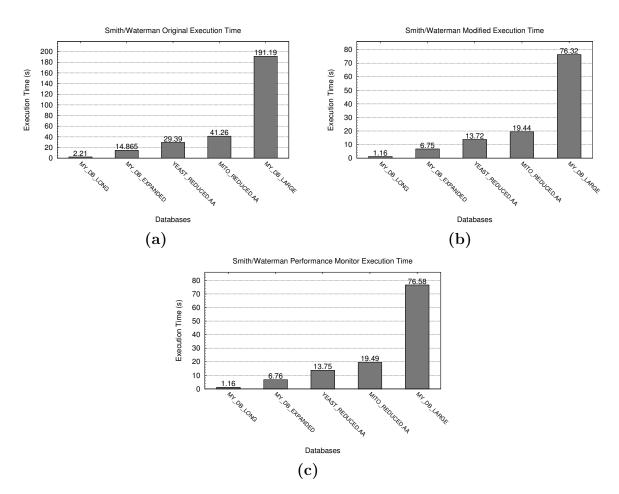

| FIGURE 6.32: | Smith/Waterman core's execution times                      | 185 |

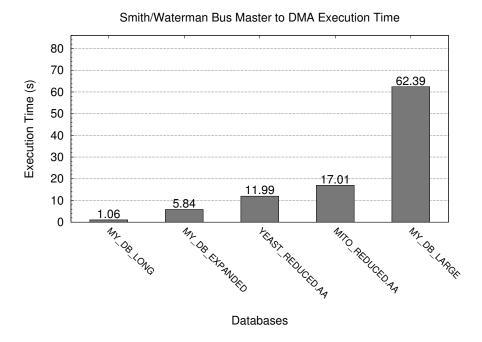

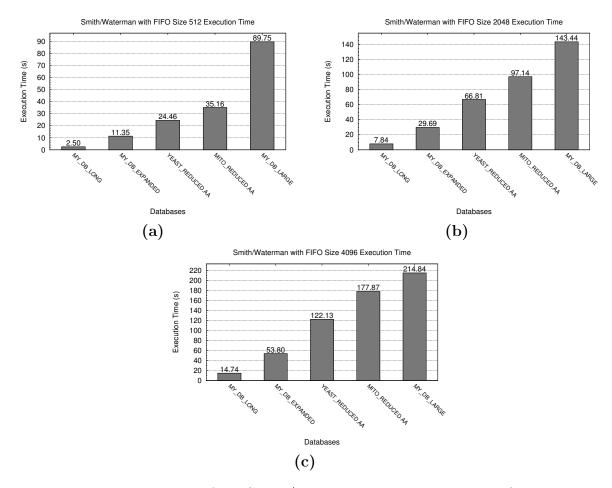

| FIGURE 6.33: | Smith/Waterman's DMA interface execution time              | 187 |

| FIGURE 6.34: | Smith/Waterman's FIFO modification execution times         | 188 |

| FIGURE 6.35: | FSM error identified by performance monitors               | 189 |

| FIGURE 6.36: | Collatz Conjecture with $n=3$                              | 191 |

| FIGURE 6.37: | Collatz Conjecture in C                                    | 192 |

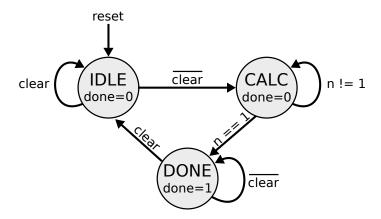

| FIGURE 6.38: | Collatz Conjecture FSM                                     | 193 |

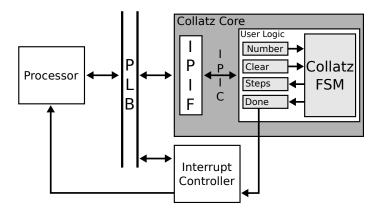

| FIGURE 6.39: | Collatz with PLB slave IPIF                                | 193 |

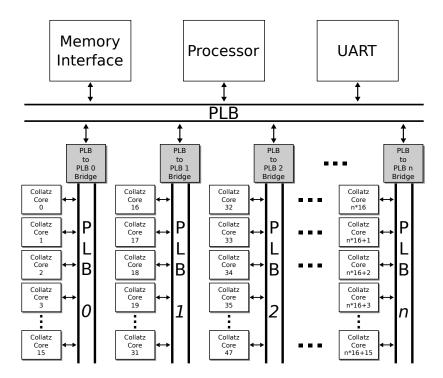

| FIGURE 6.40: | Collatz scaled across PLBs and bridges                     | 198 |

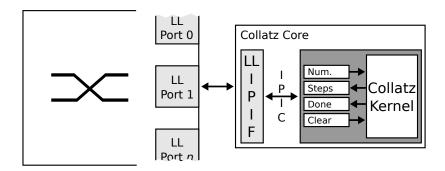

| FIGURE 6.41: | Collatz core with interface to the crossbar switch         | 199 |

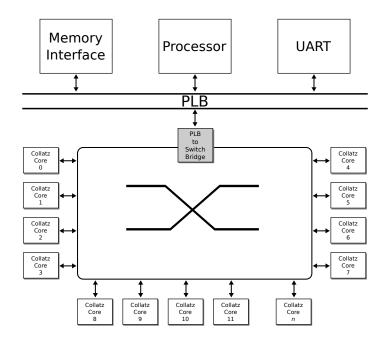

| FIGURE 6.42: | Collatz core scaled across crossbar switch                 | 200 |

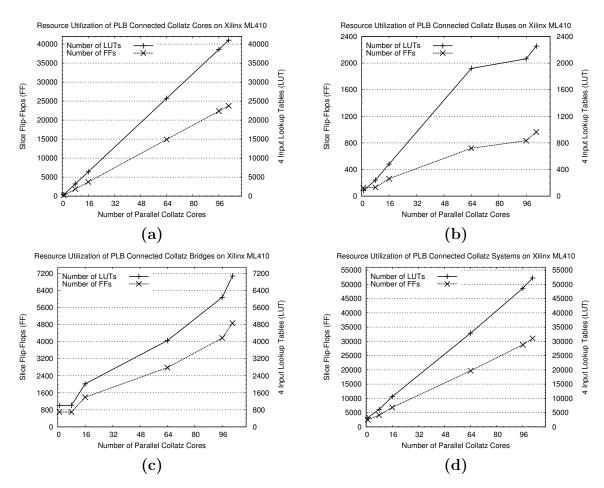

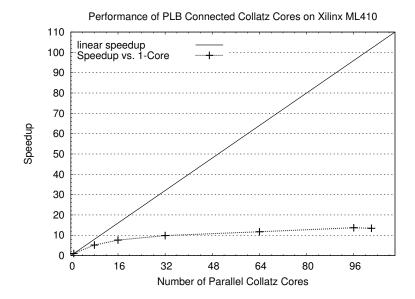

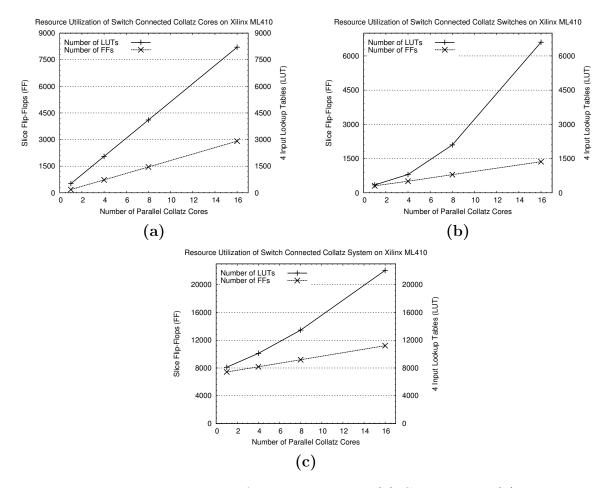

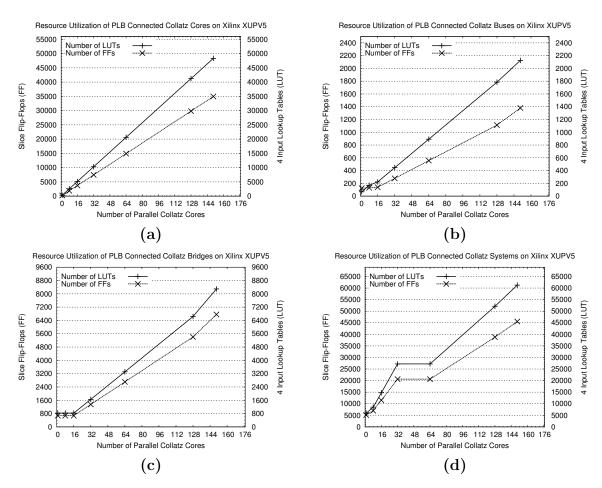

| FIGURE 6.43: | Collatz core's PLB system resource utilization on ML410    | 202 |

| FIGURE 6.44: | Collatz core's PLB system speedup on ML410                 | 203 |

| FIGURE 6.45: | Collatz core's crossbar switch system utilization on ML410 | 205 |

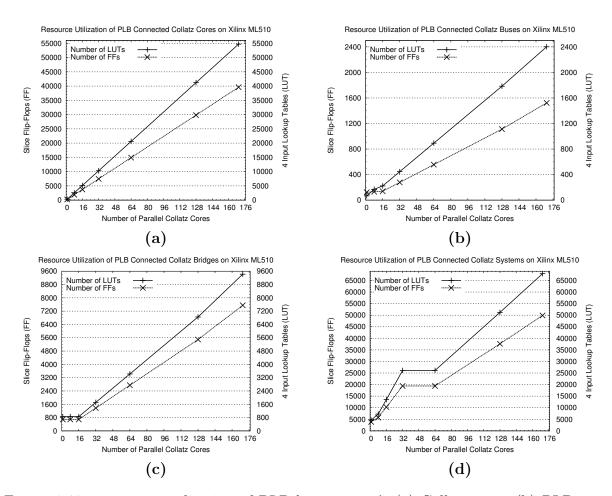

| FIGURE 6.46: | Collatz core's PLB system resource utilization on ML510    | 207 |

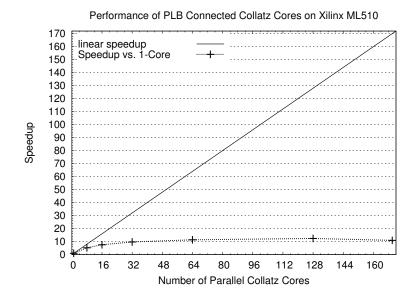

| FIGURE 6.47: | Collatz core's PLB system speedup on ML510                 | 208 |

| FIGURE 6.48: | Collatz core's PLB system resource utilization on XUPV5    | 210 |

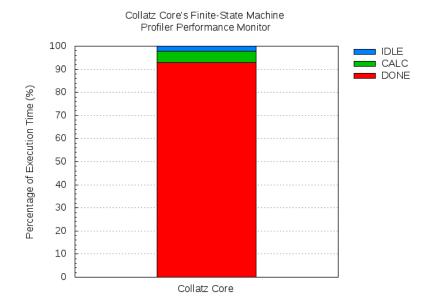

| FIGURE 6.49: | Collatz core's FSM profiler monitor results                | 211 |

212

219

FIGURE 6.50: Collatz core's histogram of steps

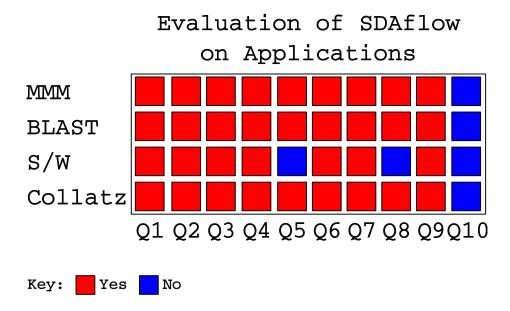

FIGURE 6.51: overall results of systematic design analysis flow

## LIST OF ABBREVIATIONS

AIREN Architecture Independent Reconfigurable Network

ALL AIREN Data Link Layer

BBD Black Box Description

BLAS Basic Linear Algebra Subprograms

BLAST Basic Local Alignment Sequence Tool

BRAM Block Random Access Memory

BSB Base System Builder

CIF Context Interface

CIP Create and Import Peripheral

DCI Digitally Controlled Impedance

DCM Digital Clock Mangers

DRAM Dynamic Random Access Memory

DRC Design Rule Check

DSP Digital Signal Processing

EOF End of Frame

FF Flip-Flops

FPGA Field Programmable Gate Array

FSC FPGA Session Control

FSM Finite State Machine

GUI Graphical User Interface

HDL Hardware Description Language

HPC High Performance Computing

HWFS Hardware Filesystem

ILA Integrated Logic Analyzer

IPIC Intellectual Property Interconnect

IPIF Intellectual Property Interface

ISE Integrated Software Environment

LUT Lookup Table

MAcc Multiply and Accumulate

MHS Microprocessor Hardware Specification

MMM Matrix-Matrix Multiplication

MMU Memory Management Unit

MPD Microprocessor Description

NCD Native Circuit Description

NFS Network Filesystem

NGD Native Generic Database

NPI Native Port Interface

PAO Peripheral Analysis Order

PAR Place and Route

PLB Processor Local Bus

PSoC Programmable System-on-Chip

RAID Redundant Array of Independent Disks

RCC Reconfigurable Computing Cluster

RSH Remote Shell

SDAflow Systematic Design Analysis Flow

SGEMM Single Precision General Matrix-Matrix Multiplication

SRAM Static Random Access Memory

SOF Start of Frame

SRP Synthesis Report

XCO Xilinx CoreGen

XMP Xilinx Microprocessor Project

XST Xilinx Synthesis Tool

# CHAPTER 1: INTRODUCTION

For decades programmers have relied upon frequency scaling to run the same computer applications faster with each generation of new processor. Unfortunately, this trend of ever faster clock frequencies has, for the most part, peaked and have begun to level off at around 2-3 GHz [1]. This is in part due to the increased power consumption and heat dissipation. As a result, industry has shifted away from strict single processor core frequency scaling in favor of resource scaling — increasing the number of compute (processor) cores on the chip with each generation [2].

While initially these chips consisted of homogeneous (dual core processors, quad core, etc.) processing elements, newer chips are being constructed with an assortment of processor cores, memory controllers, graphics controllers, discrete processing elements, and others [3, 4, 5, 6]. These heterogeneous chips with specialized compute cores could potentially offer significant performance improvements by offloading computation that is not well suited for a single sequential processor.

However, it remains unclear how to best assemble these compute cores on a single chip. Take a simple example of how to connect compute cores on a single chip. For a relatively small number of compute cores it is possible, in some cases, to connect them all together in a fully connected direct network (complete graph), as seen in Figure 1.1(a). As the number of compute cores increase, the interconnection resources increase (at the rate of c = n(n-1)/2, where n represents the number of nodes and c represents the number of connections). As the number of nodes increase, the amount of communication resources using the fully connected network becomes too costly and the propagation delay becomes too great. As a result, an alternative interconnect is required, such as a crossbar switch shown in Figure 1.1(b). The crossbar switch still

Figure 1.1: block diagram of different ways to connect compute cores: (a) direct connect, (b) crossbar switch, and (c) a shared bus

allows every core to communicate with every other core, but not all at the same time in (the number of interconnects depends on the implementation). A third configuration of these compute cores could be a shared bus, Figure 1.1(c), which limits the amount of parallel communication between cores, but minimizes the amount of interconnection resources.

Moreover, as the number of different types of compute cores increase, so does the complexity associated with best placing them on a chip. This placement can greatly effect the performance of a system, especially in the area of High Performance Computing (HPC). Here, every last bit of processing potential is eked out by programmers in order to maximize performance and surpass computing barriers such as the recently broken PetaFLOP barrier.

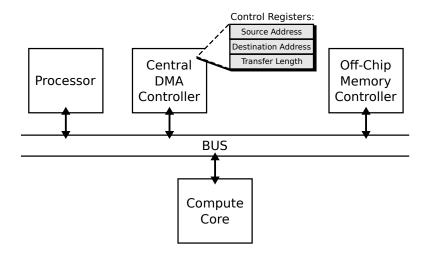

As another example, consider a design that includes a single compute core as an application accelerator. The designer can optimize the core to best utilize all of the available resources to yield the greatest performance. However, this is not always as simple as it sounds. When just considering access to off-chip memory, the designer must consider the bandwidth and latency requirements in order to determine whether the core should rely on the processor to initiate the data transfer (shown in Figure 1.2(a)), or if the core should initiate the data transfer. If the core is to initiate the transfer, should it be connected to a shared bus as a bus master, (Figure 1.2(b)), or should it be directly connected to the memory controller (Figure 1.2(c))?

Figure 1.2: block diagram of (a) one compute core connected to a shared bus and acting as a slave, receiving data from the processor which is directly connected to the memory controller, (b) one compute core connected to a shared bus and acting as a bus master, and (c) one compute core directly connected to the memory controller

These issues are easy to visualize, but efficient and practical design decisions have to be addressed. One important issue is how to partition on-chip resources. In a general purpose processor there is a trade-off between the size of the caches and number of processor cores. While it may be a difficult decision, with the advancements in fabrication, multi-processor core designs are not drastically sacrificing cache sizes. On the other hand, in more heterogeneous designs the trade-off becomes an even more concerning problem as it is difficult to compare the significance of one resource over another. Making a trade-off between adding an additional memory controller compared to particular a discrete processing element is application specific, and the designer of the chip has to make a decision that may result impact sales.

Another issue is with respect to a design where more resources have become available (whether due to using more chips, migrating to a larger chip, or because the core only initially consumed a portion of the available resources). Now the designer has to go through an even more complex problem to try and scale the number of cores. Often the simple solution is to replicate n number of these cores, using all of the resources available. Yet, without careful consideration a thoughtful design may actually degrade system performance. This is the old adage, "more isn't always better."

There may be little effect on the performance by changing how a single core is

connected, to say off-chip memory; however, when adding more cores, the contention for the processor, shared bus, or the memory controller itself can degrade the overall performance. The processor may be able to sustain a single or even a few compute cores, but at some point the processor may be overwhelmed trying to service too many cores. This is also true with bus contention [7]. As the number of cores that are connected to the same shared bus increase, each must wait for its turn to access the bus. This increases the latency between issuing requests and receiving data. Finally, even if there were enough resources to connect these cores directly to the memory controller, it becomes the bottleneck trying to service an increasing number of parallel requests to memory.

Figure 1.3 shows two examples of the performance gained by scaling a system from a single cores to 16 cores. The first configuration was quickly assembled and resulted in a poorly implemented design with performance that does provide a speedup, but only does so at a very modest  $2.25 \times$  speedup. Now compared to the second configuration, a carefully thought out design, the speedup is significantly improved and actually tracks slightly better than linear speedup. While not every design may scale so fortuitously, the implementation can play a vital role in how the system scales. Furthermore, both designs peak prior to fully utilizing the available resources at 16 cores. This again illustrates the point that even if it is possible to put more cores in the design, it may not provide an increase in performance.

# 1.1 Field Programmable Gate Arrays

The work presented here focuses on the use of multiple Field Programmable Gate Arrays (FPGAs), where resources are more diverse and the scaling potential is even more evident. FPGAs now have the ability to assemble a programmable system-on-chip (PSoC) that includes processors, memory controllers, system buses and on-chip peripherals. And with the programmable logic resources increasing with every generation [8], still tracking Moore's law (the number of transistors will double ap-

Figure 1.3: sample speedup performance comparison of two designs

proximately every two years [9]), it is possible to experiment with the scalability and connectivity of designs (please see Chapter 2 for a more detailed background on FPGAs).

FPGAs enable this research to investigate real applications running in hardware with actual data sets as opposed to a simulated analysis. What this means is that the entire system is part of the evaluation. Often times simulation can limit the scope due to increased evaluation times that are necessary for a sequential processor to model the behavior of a parallel system. Simulation also must predict performance of non-deterministic components such as access to off-chip memory. Experimenting with FPGAs provides tangible results of fully running systems with complex hardware and software configurations. Moreover, running these experiments is crucial to understanding the systems behavior because static analysis of the performance might not be accurate when an application's data sets can play a significant role in the overall performance. That is to say, run under one set of inputs the application may demonstrate tremendous speedups, yet under another it may perform dismally.

The main focus of this research looks at various approaches to analyze and attempts to distribute an application efficiently across a heterogeneous cluster of computing resources. The process will also provide the designer with projections on the amount of resources needed to scale an existing design to a specified performance, as well as, projecting the performance based on a specified amount of resources. More specifically, this work will investigate the feasibility to productively scale existing hardware designs to a large number of FPGA resources in an all-FPGA cluster.

# 1.2 Productivity Tools

To aid in the development of a system, a series of development tools are presented that operate in collaboration with the existing synthesize and analysis tools that designers are accustom to using. Chapter 2 and Chapter 3 provide a more detailed description of these existing tools, whereas Chapter 4 discusses the specific tools developed as part of this work. This section briefly highlights the type of tools that have been developed as part of this work to help improve a designer's overall productivity.

Traditionally a designer relies upon the exiting tools to assemble designs, but often must make significant modifications to the design manually. During the development stage a designer may need to known the resource utilization of a component in the design. To identify the utilization the designer must manually create a project, synthesize the design, and read the synthesis report. While tools and graphical user interfaces (GUIs), such as Xilinx ISE [10], exist to help, the designer is still tasked with not only the complete assembly of the project, but also the analysis of the synthesis results to intelligently create efficiently performing systems. What is needed are tools that can quickly assemble these project autonomously, perform routine tasks such as synthesis, parse and analyze results, and present the designer with recommendations on how to scale the design and/or connect the design for increased performance.

Scaling a design can also mean migrating a design from one device to another. A designer does not have the luxury of simply resynthesizing/recompiling the design to take advantage of the increase in resources that have been so favorable for software

developers during the hey days of processor frequency scaling. This is due to the fact that during synthesis the HDL source is used to generate the logic configuration for the specific device. Without changing the design, even if the new device has twice the amount of resources, the HDL specification will still produce the same design. Instead the system must be redesigned. Even in the trivial case of scaling the number of components to utilize the now larger device requires significant design effort. To assist the designer, migration tools can be used to port a design to the new device along with replication tools to utilize the increase in available resources.

Often times a system does not perform better by simply increasing the number of components operating in parallel, perhaps due to other bottlenecks present in the system such as buses or accessing memory. As a result, the designer may spend a significant amount of effort augmenting a design to combat the bottleneck. Instead, tools to parse the existing design to identify the interfaces between the components in the design could be used to then assemble alternative configurations utilizing different types of interconnections.

Regardless of the scalability or the performance due to how a system is configured, a designer often evaluates the performance of individual components in a system. For example, a designer may wish to determine the utilization of a particular resource. Doing so requires the designer to manually create and insert specific monitors and add them to their design. Moreover, the designer must also provide a mechanism to retrieve the data from these monitors, often at the expense of other resources (e.g. ChipScope [11, 11]) or runtime performance when the processor must stop its calculations to retrieve and store the data for the designer. Therefore it would be advantageous for a tool or set of tools to exist to not only identify what should be monitored in a system, but to insert the necessary infrastructure to enable the monitoring to be minimally invasive.

These types of tools can help improve a designer's productivity by reducing the

amount of unnecessary or often redundant work that comes from hardware design. The goal of these tools is not to fully replace the designer, but instead to allow the designer to focus on the development of the critical components of the system. Furthermore, these tools can improve the lifetime of the developed system by enabling the system to migrate to newer devices without significant effort by the original designer. The rest of this work is aimed at not only the development of such tools, but the evaluation of their effectiveness to improve the productivity during a system's design.

#### 1.3 Thesis Statement

As we shift from frequency scaling to resource scaling we need to consider how to not only design for such systems, but to maintain a designer's productivity by minimizing the design search space as the number of possible configurations grows. We need to determine what routine tasks can be automated to further improve a designer's productivity. We need to understand what useful information can be gathered from existing designs to help predict or identify scalability and performance potential of future designs. We must also address how can this information be conveyed to the designer such that it can be used to increase overall productivity when implementing future designs on an increasing amount of resources.

Furthermore, with so many configuration choices, there needs to be a means to compare each configuration. But how or what should be compared? Should the comparison focus on computation rate, throughput, resource utilization or some other metric? And even if such a metric for comparison exists, how can the performance be describe such that a designer can quickly understand how to efficiently (and productively) utilize the system?

Thus, the ultimate question we are trying to address is: can the knowledge of an experienced hardware designer be codified into a design flow and a set of tools? If so, this will make system designers more productive.

In this work we propose to answer all of these questions through a Systematic Design Analysis flow (SDAflow) that includes the use of static hardware profiling, timing and resource profiling in concert with runtime performance monitoring to create a model of performance and a set of tools for spatial scaling that will aim to increase designer productivity.

The remainder of this dissertation is organized as follows. Chapter 2 presents the necessary background information the reader should be familiar with in order to understand the dissertation work. This is followed by Chapter 3 which covers related work found in both academia and industry. Next, Chapter 4 covers the design and implementation of the Systematic Design Analysis flow (SDAflow) along with the productivity tools created for this work. In Chapter 5 the experimental setup and evaluation methodology for the design flow and tools is presented. Chapter 6 follows with four case studies used to evaluate the Systematic Design Analysis flow and the effectiveness of the productivity tools. Chapter 7 concludes with a brief summary of the research.

# CHAPTER 2: BACKGROUND

This chapter begins with an overview of Field-Programmable Gate Arrays (FP-GAs) and the components that can be found on modern FPGAs in Section 2.1. For those more familiar with FPGAs reading this section may not be necessary, but it does provide a good overview and review for the less initiated. Section 2.2 briefly covers hardware descriptions languages (HDLs). It is not necessary to be proficient with a specific HDL, but it might prove useful to be familiar with the terms and the capabilities of HDLs as some of the design and analysis includes discussions and code examples.

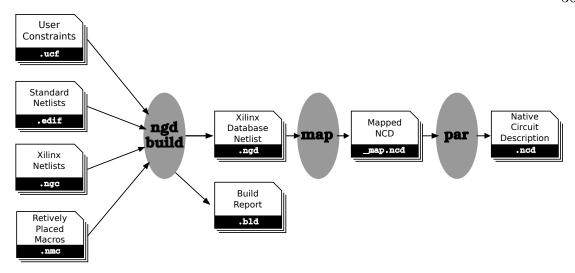

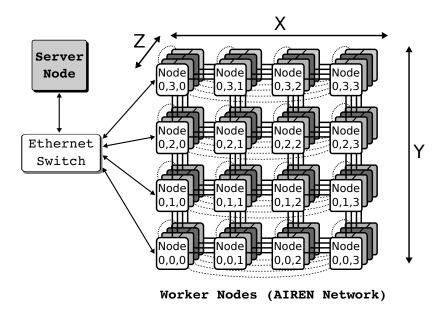

In Section 2.3 the Xilinx tool chain is presented. This tool chain is used extensively throughout this work and it may be useful to refer back to this section in later chapters. The basic tool flow is covered with a description of each basic step from synthesizing a hardware description language design to the generation a FPGA configuration file. In Section 2.4 the Reconfigurable Computing Cluster (RCC) project currently under evaluation at the University of North Carolina at Charlotte is presented. A significant portion of the research discussed here will be accomplished with hardware and software that are part of the RCC project. Finally, in Section 2.5, the custom high-speed network that is used as part of the RCC project is discussed in thorough detail. The detail is presented in this chapter as background to help explain the capabilities of this custom network and how its integration into the FPGA cluster enables research to study scalability of designs beyond a single node in the cluster.

# 2.1 Field-Programmable Gate Array

A modern FPGA consists of a 2-D array of programmable logic blocks, fixedfunction blocks, and routing resources implemented in the CMOS technology. Along the perimeter of the FPGA there are special logic blocks that are connected to external package I/O pins. Logic blocks consist of multiple logic cells, while logic cells contain function generators and storage elements. These general terms will be discussed in more detail throughout this section.

# 2.1.1 Function Generators

FPGA devices use *function generators* to implement Boolean logic functionality rather than physical gates. For example, to implement the Boolean function:

$$f(x, y, z) = xy + z'$$

using a 3-input function generator, first create the eight row Boolean truth table for this function. For each input the truth table represents what the Boolean function's output will be. If each of the function's output bits were stored into individual static memory (such as SRAM) cells and connected as inputs to an 8x1 multiplexer (MUX), the three inputs (x,y,z) would be the select lines for the MUX. The result is commonly what is known as a *look-up table* (LUT).

It is also important to understand that unlike a digital circuit implemented within logic gates, the propagation delay from a single LUT is fixed. This means, regardless of the complexity of the Boolean circuit, if it fits within a single LUT, the propagation delay remains the same. This is also true for circuits spanning multiple LUTs, but instead, the delay depends on the number of LUTs and additional circuitry necessary to implement the larger function.

To generalize, the basic n-input function generator consists of a  $2^n$ -to-1 multiplexer (MUX) and  $2^n$  SRAM (static random access memory) cells. By convention, a 3-LUT is a 3-input function generator. The 3-input structure is mentioned for demonstration purposes, although 4-LUT and 6-LUTs are more common in today's components, such as the Xilinx Virtex 4 and 5 FPGAs.

Figure 2.1: Virtex 5's six input LUT is built from two five input LUTs with the sixth input controlling a MUX between the two LUTs

To implement a function with more inputs than would fit in a single LUT, multiple LUTs are used. The function can be decomposed into sub-functions of a subset of the inputs, each sub-function is assigned to one LUT, and all of the LUTs are combined (via routing resources) to form the whole function. There are also some dedicated routing resources to connect neighboring LUTs with minimal delay to support low propagation delays.

In practice, using HDL to describe the digital circuit and then using synthesis tools to map the textual description to an equivalent look-up function is more common than the designer defining the LUTs logic itself. What is important as far as the designer is concerned is how to represent a circuit to efficiently utilize the available resources. The 6-LUT on the Virtex 5 can either be used as a single 6-LUT or as two 5-LUTs as long as both 5-LUTs share the same inputs. A designer can take advantage of this when building digital circuits by not including the unnecessary inputs which the synthesis tools may infer to a larger LUT. Figure 2.1 represents the block diagram of a 6-LUT. In the event that all 6 inputs are used for the LUT, the bottom output 05 is not used.

An important observation is that SRAM cells are volatile, if power is removed the value is lost. As a result, we need to learn how to set the SRAM cell's value. This process, called configuring (or programming), could be handled by creating an address decoder and sequentially writing the desired values into each cell. However, the number of SRAM cells in a modern FPGA is enormous and random access is rarely required. Instead, the configuration data is streamed in bit-by-bit. The SRAM cells are chained together such that, in program mode, the data out line of one SRAM cell is connected to the data in line of another SRAM cell. If there are n cells, then the configuration is shifted into place after n cycles. Some FPGA devices also support wider, byte-by-byte, transfers as well to support parallel transfers for faster programming.

# 2.1.2 Storage Elements

While the function generators provide the fundamental building block for combinational circuits, there are additional components within the FPGA to provide a wealth of functionality. As is common with other programmable logic devices, the D-type flip-flops are incorporated in the FPGA. The flip-flops can be used in a variety of ways, the simplest being data storage. Typically, the output of the function generator is connected to the flip-flop's input. Also, the flip-flop can be configured as a latch, operating on the clock's positive or negative level. When designing with FPGAs, it is suggested to configure the storage elements to be D flip-flops instead of latches. A latch being level-sensitive to the clock (or enable) increases the difficulty to route clock signals within a specific timing requirement. For designs with tight timing constraints, such as operating custom circuits at a high operating frequency that span large portions of the FPGA, D flip-flops are more likely to meet the timing constraints.

# 2.1.3 Logic Cells

By combining a function generator and a storage element the result is commonly what is referred to as a *logic cell*. Logic cells are really the low-level building block upon which FPGA designs are built. Both combinational and sequential logic can

be built from within a logic cell or a collection of logic cells. Many FPGA vendors will compare the capacity of an FPGA based on the number of logic cells (along with other resources as well). In fact, when comparing designs, it is no longer relevant to describe an FPGA circuit in terms of "number of equivalent gates (or transistors)". This is because a single LUT can represent very modest equations which would only require a few transistors to implement, or very complex circuit such as a RAM which would require many hundreds of transistors. While the process of mapping larger circuits for logic cells has not been described yet, it is possible to identify based on the number of logic cells how big or small a design is and whether or not it will fit within a given FPGA chip.

The Xilinx Virtex 5 combines four of these logic cells to create a *slice*, as is shown in a simple block diagram in Figure 2.2. With four 6-LUTs and D flip-flops contained within close proximity, it is possible to use these components to design more complex circuits. In addition to Boolean logic, a slice can be used for arithmetic and RAMs/ROMs. Some slices are connected in such a way that they can be used for data storage as distributed RAMs or shift registers. This is accomplished by combining multiple LUTs in the slice. The distributed RAM can be configured as single, dual and in some cases quad ports providing independent read and write access to the RAM. The depth of the RAMs vary based on the number of ports, but can range from 32 to 256 1-bit elements. The distributed RAMs data width can be increased beyond 1-bit; however, there will be a trade off between the width and depth and resource usage. For example, a 64x8 (64 8-bit elements) RAM is implemented in nine LUTs (1-LUT per 64x1 RAM and an additional LUT for logic). However, a 64x32 extends beyond an efficient use of the configurable resources and is moved into what will be discussed shortly, Block RAM (BRAM).

In addition to logic and memory, slices can be used as shift registers. A shift register is capable of delaying an input x number of clock cycles. Using a single LUT,

Figure 2.2: Virtex 5's logic slice block diagram with four 6-LUTs and four flip-flop/latch storage elements

data can be delayed up to 32 clock cycles. Cascading all four LUTs in one slice the delay can increase to 128 clock cycles. This is useful for small buffers that would traditionally be implemented within a more valuable resource such as a Block RAM.

With all of these possible uses, a D flip-flop can be added to provide a synchronous read operation. With the additional D flip-flop, a read will be subject to an additional latency of one clock cycle. This may or may not impact a design, but for designs with high timing constraints, adding the synchronous operation can relax the constraint.

# 2.1.4 Logic Blocks

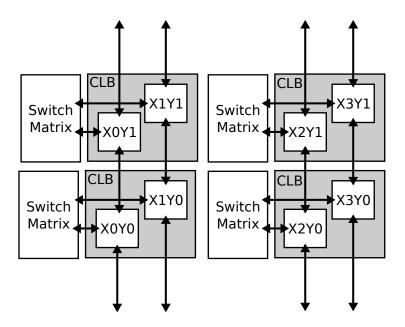

While logic cells could be considered the basic building blocks for FPGA designs, in actuality it is more common to group several logic cells (slices) into a block and add special-purpose circuitry, such as an adder/subtractor carry chain, into what is known as a *logic block*. This allows a group of logic cells that are geographically close to have quick communication paths, reducing propagation delays and improving design implementations. For example, the Xilinx Virtex 5 families put four logic cells in a *slice*. Two slices, and carry-logic form a *Configurable Logic Block* or CLB.

Figure 2.3: Virtex 5 CLB block diagram of the interconnection between each slice in the CLBs and their connection to the switch matrix

Figure 2.3 depicts the basic structure and interconnection of the CLBs, slices and switch matrices for the Virtex 5.

Abstractly speaking, the logic blocks are what someone would see if they were to "look into" an FPGA. The exact number of logic cells and other circuitry found within a logic block is vendor specific; however, we are now able to realize even larger digital circuits within the FPGA fabric.

Logic blocks are connected by a routing network to provide support for more complex circuits in the FPGA fabric. The routing network consists of switch boxes. A switch box, is used to route between the inputs/outputs of a logic block to the general on-chip routing network. The switch box is also responsible for passing signals from wire segment to wire segment. The wire segments can be short (span a couple of logic blocks) or long (run the length of the chip). Since circuits often span multiple logic blocks, the carry chain allows direct connectivity between neighboring logic blocks, bypassing the routing networking for potentially faster implemented circuits.

Competing vendors and devices often have different routing networks, different

special-purpose circuitry, and different size function generators. So it is difficult to come up with an exact relationship for comparison. The comparison is further complicated since it also depends on the actual circuit that is being implemented.

# 2.1.5 Special-Purpose Function Blocks

So far the focus has been on the internals of the FPGA's configurable (or programmable) logic. A large portion of the FPGA consists of logic blocks and the routing logic to connect the programmable logic. However, as semiconductor technology advanced and more transistors became available, FPGA vendors recognized that they could embed more than just configurable logic to each device.

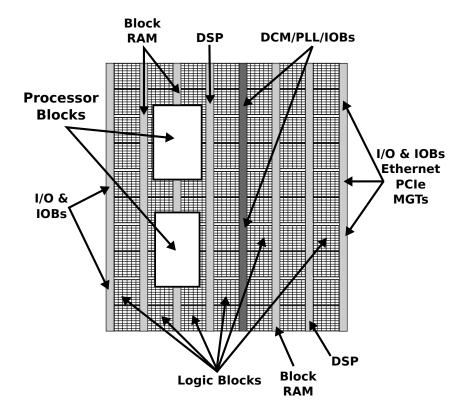

Platform FPGAs combine the programmable logic with additional resources that are embedded into the fabric of the FPGA. A good question to ask at this point is "why embedded specific resources into the FPGA fabric?" To answer this question consider FPGA designs compared to ASIC designs. An equivalent ASIC design is commonly considered to use fewer resources and consume less power than an FPGA implementation. However, ASIC designs are not only often found to be prohibitively expensive, the resources are fixed at fabrication. Therefore FPGA vendors have found a compromise with including some ASIC components among the configurable logic.

The block diagram of a Platform FPGA, seen in Figure 2.4, shows the arrangement of these special-purpose function blocks placed throughout the FPGA. Which function blocks are included and their specific placement is determined by the physical device, this illustration is meant to help better understand the general construct of modern FPGAs. The logic blocks still occupy a majority of the FPGA fabric in order to support a variety of complex digital designs; however, the move to support special-purpose blocks provides the designer with an ASIC implementation of the block as well as removes the need to create a custom design for the block. For example, a processor block could occupy a significant portion of the FPGA if implemented in the logic resources.

Figure 2.4: high-level view of a Platform FPGA

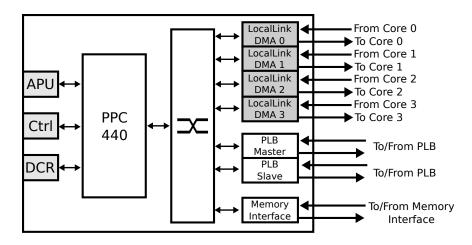

# 2.1.5.1 Processors

Arguably one of the more significant additions to the FPGA fabric is a processor embedded within the FPGA fabric. For many designs requiring a processor, often choosing an FPGA device with an embedded processor (such as the FX series part for the Xilinx Virtex 5) can greatly simplify the design process while reducing resource usage and power consumption. The IBM PowerPC 405 and 440 processors are examples of two processors included in the Xilinx Virtex 4 and 5 FX FPGAs respectively. The PowerPC 440's block diagram is shown in Figure 2.5.

These are conventional RISC processors which implement the PowerPC instruction set. Both the PowerPC 405 and 440 come with some embedded system extensions, but do not implement floating-point function units in hardware. Each come with level 1 instruction and data cache and a memory management unit (MMU) with translation look-aside buffer to support virtual memory. A variety of interfaces exist

Figure 2.5: PowerPC 440 processor block diagram showing the available interfaces between processor and the FPGA fabric

to connect the processors to the FPGA programmable logic to allow interaction with custom hardware cores.

Not all FPGAs come with a processor embedded into the FPGA fabric. For these devices the processor must be implemented within the FPGA fabric as a soft processor core. These range from small, simple purpose processors such as the Xilinx PicoBlaze which can be useful for implementing more complex state machines in Assembly rather than a hardware description language. A MicroBlaze is the bigger brother of the PicoBlaze, occupying approximately 1,500 slices (an order of magnitude more than the PicoBlaze) but can support a full running operating system such as Linux. Still more complex processors can be included, the Sun UltraSparc for example has been implemented on an FPGA; however, it consumes a significant amount of resources.

#### 2.1.5.2 Block RAM

Many designs require the use of some amount of on-chip memory. Using logic cells it is possible to build variable sized memory elements; however, as the amount of memory needed increases, these resources are quickly consumed. The solution, to provide a fixed amount of on-chip memory embedded into the FPGA fabric called  $Block\ RAM$  (BRAM). The amount of memory depends on the device; for example,

the Xilinx Virtex 5 XC5VFX130T (on the ML-510 development board) contains 298 36 Kb BRAMs, for a total storage capacity of 10,728 Kb. Local on-chip storage such as RAMs and ROMs or buffers can be constructed from BRAMs. BRAMs can be combined together to form larger (both in terms of data width and depth) BRAMs. BRAMs are also dual-ported, allowing for independent reads and writes from each port, including independent clocks. This is especially useful as a simple clock crossing device, allowing one component to produce (write) data at a different frequency as another component consuming (reading) the data.

One common uses of BRAMs in FPGA designs is for FIFOs. FIFOs, or simply data queues, are primitives the designer can take advantage of, rather than building their own out of BRAM logic, reducing design and debugging time. Recently, FPGAs have started to include FIFOs as separate components within the FPGA fabric. The Virtex 5 and 6 are two such devices, although the physical limitations on the functionality may rule out their use in a design.

## 2.1.5.3 Digital Signal Processing Blocks

To allow more complex designs which may consist of either digital signal processing or just some assortment of multiplication, addition and subtraction, *Digital Signal Processing Blocks* (DSP) have been added to many FPGA devices. As with the Block RAM, it is possible to implement these components within the configurable logic, yet it is more efficient in terms of area, performance, and power consumption to embed multiple of these components within the FPGA fabric. At a high level, the DSP blocks of a multiplier, accumulator, adder, and bitwise logical operations (such as AND, OR, NOT, NAND, etc.) It is possible to combine DSP blocks to perform larger operations such as single and double precision floating point addition, subtraction, multiplication, division and square-root. The number of DSP blocks is device dependent; however, they are typically located near the BRAMs which is useful when implementing processing requiring input and/or output buffers.

In the Virtex 5, the DSP slices are known as DSP48E (48-bit DSP element) slices. The DSP slices include a 25x18 two's complement multiplier, 48-bit accumulator (for multiply accumulate operations), an adder/subtractor for pipelined operations and bitwise logical operations. Embedding this functionality into the slice provides a significant savings in FPGA resources since implementing the equivalent resources in LUTs is quite expensive.

For applications needing filters, such as comb and finite impulse response, to transforms, such as fast and discrete Fourier, to CORDIC (coordinate rotational digital computer) algorithm, the DSP slices are used when available. The Virtex 5 FX130T on the ML-510 contains 320 DSP slices. Compared to the 20,480 regular slices, this seems like disproportionate amount, yet not all designs require the use of DSP slices. For designs requiring a higher percentage of DSP slices, the Xilinx SX series FPGAs include more DSP resources. There are tools, one of which we will introduce shortly, which help the designer quickly implement customized DSP components. They are also useful for resource and performance approximation.

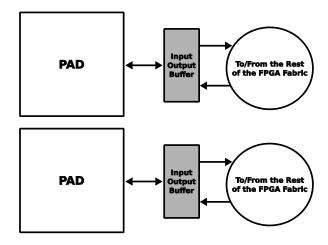

# 2.1.5.4 Select I/O

Interfacing off the FPGA is another important issue when designing for embedded systems. In most cases there will be a need to interface with some physical device(s). Depending on the number of I/O pins required, some devices are better suited than others, but they are all built around *Input/Output Blocks* (IOB).

Now, let's augment the logic block array with IOBs that are on the perimeter of the chip. These IOBs connect the logic block array and routing resources to the external pins on the device. Each IOB can be used to implement various single-end signaling standards, such as LVCMOS(2.5 V) and LVTTL (3.3 V) and PCI (3.3 V). IOBs can also support double data rate signaling used by commodity static and dynamic random access memory. The IOBs can be paired with adjacent IOBs for differential signaling, such as LVDS.

Figure 2.6: Xilinx Select IOB tile, for connections between FPGA fabric and the pad on the FPGA device

From Figure 2.6 each I/O tile spans two pads (which connect to physical pins). Each Pad connects to a single IOB which connects to the input and output logic. Xilinx uses the term Select I/O to refer to configurable inputs and outputs which support a variety of standard interfaces (LVCMOS, SSTL, LVDS, etc.) Select I/O also take advantage of Digitally Controlled Impedance (DCI) to eliminate adding resistors close to the device pins which are needed to avoid signal degradation. DCI can adjust the input or output impedance to match the driving or receiving trace impedance. Some advantages include the reduction in the number parts which simplifies the PCB routing effort. It also provides a way to correct for variations in manufacturing, temperatures, and voltages.

## 2.1.5.5 Multi-Gigabit Transceivers

Over the last twenty years, digital I/O standards have varied between serial and parallel interfaces. Serial interfaces time-multiplex the bits of a data word over a fewer conductors while parallel interfaces signal all the bits simultaneously. While the parallel approach has the apparent advantage of being faster (data are being transmitted in parallel), this is not always the case in the presence of noise. Many recent interfaces — including various switched Ethernet standards, Universal Serial

Bus [12, 13], SerialATA [14], FireWire [15], InfiniBand [16] — are now using low-voltage differential pairs of conductors. These standards use serial transmission and change the way data is signaled to make the communication less sensitive to electromagnetic noise.

High Speed Serial Transceivers are devices that serialize and deserialize parallel data over a serial channel. On the serial side, they are capable of baud rates from 100 Mb/s to 11.0 Gb/s which means that they can be configured to support a number of different standards, including Fiber Channel, 10G Fiber Channel, Gigabit Ethernet, and InfiniBand. As with other the aforementioned FPGA blocks, the transceivers can be configured to work together. For example, two transceivers can be used to effectively double the bandwidth. This is called channel bonding (multi-lane and trunking are common synonyms).

In the Virtex 5 series FPGAs two types of transceivers exist, RocketIO GTX and GTP. GTX transceivers are capable of a higher bandwidth whereas the GTP transceivers are lower bandwidth and require less power. The number of transceivers vary from part to part. For example, the Virtex 5 FX130T includes 20 GTX transceivers. As with the DSP slices and SX series FPGAs, there are applications which require a higher percentage of transceivers to configurable logic. The TX (also known as TXT or HX) series FPGAs include these additional transceivers. Both the GTX and GTP transceivers are bi-directional, providing independent transmit and receive at the same time.

Xilinx includes a customizable GTX/GTP wizard to expedite adding the transceiver logic to a design or specific component. In short, it is possible to specify the data width (parallel data), frequency and channel bonding needed by the design. Design considerations are needed for systems with tight timing or resource constraints; however, a lot of the headache typically associated with high-speed integration can be eliminated.

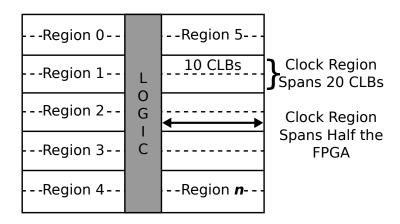

Figure 2.7: clock regions on an FPGA span 20 CLBs vertically and half of the FPGA horizontally, the number of clock regions varies by chip

# 2.1.5.6 Digital Clock Manager

In FPGA designs it is common to operate different cores at different frequencies. In traditional designs, any clocks needed would have to be generated off-chip and connected as an input to the system. With FPGA designs it is possible to generate a wide range of clock rates from a single (or a few) clock source(s). While it is easier to design systems with only a few different clock rates, having the flexibility to incorporate clock rates after board fabrication is compelling to designers. However, there are limitations on the number of clocks that can be generated and routed to various parts of the FPGA. A number of clock regions exist on the FPGA (varying from 8 to 24 based on the Virtex 5 FPGAs) which support up to 10 clocks domains. The FPGA is split in half and on each half a clock region spans twenty CLB. The Virtex 5 FX130T has 20 clock regions. Figure 2.7 is simple example of the clock regions on the FPGA.

To help the designer use and manage these clocks, Xilinx uses digital clock managers (DCM). Generally speaking, a DCM takes an input clock and can generate a customizable output clock. By specifying the multiply and divider values the frequency-synthesis output clock clkfx can generate a custom clock. Given an input clock clkin the equation:

$$clkfx = M/D * clkin$$

is used to generate the output clock. However, the DCM provides more than just generating different clock rates. A DCM is also capable of phase shifting the input clock by 90, 128, and 270 degrees. The DCM also provides a 2× the input clock rate and can phase shift this input clock by 180 degrees. It is easy to see without going into more detail that DCMs are a useful tool to generate the necessary clock(s) in FPGA designs. In short, meeting timing when designing with FPGAs can be a difficult task unless design considerations for timing and clocks are included from the beginning of the design process.

## 2.2 Hardware Description Languages

Now that the internals of an FPGA have been presented, the next step is to discuss how to "configure" them. This can be accomplished through the use of a hardware description language as a high-level language to describe the circuit to be implemented on the FPGA. The origins of hardware description languages were rooted in the need to document the behavior of hardware. Over time, it was recognized that the descriptions could be used to simulate hardware circuits on a general-purpose processor. This process of translating an HDL source into a form suitable for a general-purpose processor to mimic the hardware described is called simulation. Simulation has proved to be an extremely useful tool for developing hardware and verifying the functionality before physically manufacturing the hardware. It was only later that people began to synthesize hardware, automatically generating the logic configuration for the specified device from the hardware description language.

Unfortunately, while simulation provided a rich set of constructs to help the designer test and analyze the design, many of these constructs extend beyond what is physically implementable within hardware (on the FPGA) or synthesize inefficiently into the FPGA resources. As a result only a subset of hardware description languages can be used to synthesize designs to hardware. The objective of this section

is to present two of the more popular hardware description languages, VHDL and Verilog, along with a brief overview of some high-level languages to produce digital circuits.

#### 2.2.1 VHDL

VHDL, which stands for VHSIC<sup>1</sup> Hardware Description Language, to describe digital circuits. In simulation, the VHDL source files are analyzed and a description of the behavior is expressed in the form of a netlist. A *netlist* is a computer representation of the a collection of logic units and how they are to be connected. The logic units are typically AND/OR/NOT gates or some set of primitives that makes sense for the target (4-LUTs, for example). The behavior of the circuit is exercised by providing a sequence of inputs. The inputs, call *test vectors*, can be created manually or by writing a program/script that generates them. The component that is generating test vectors and driving the device under test is typically called a *test bench*.

In VHDL, there are two major styles or forms of writing hardware descriptions. Both styles are valid VHDL codes; however they model hardware differently. This impacts synthesis, simulation, and, in some cases, designer productivity. These forms are:

**Structural/Dataflow** Circuits are described in terms of logic units and signals.

Dataflow is a type of structural descriptions that has syntactic support to make it easier to express Boolean logic.

**Behavioral** Circuits are described in an imperative (procedural) language to describe how the outputs are related to the inputs as a process.

A third style exists as a mix between both structural and behavioral styles. For programmers familiar with sequential processors, the behavioral form of VHDL seems natural. In this style, the process being described is evaluated by 'executing the program' in the process block. For this reason, often complex hardware can be expressed

<sup>&</sup>lt;sup>1</sup>Very high speed integrated circuit

succinctly and quickly — increasing productivity. It also has the benefit that simulations of certain hardware designs are much faster because the process block can be directly executed. However, as the design becomes more complex, it is possible to write behavioral descriptions that cannot be synthesized. Converting behavioral designs into netlists of logic units is called *High-Level Synthesis* referring to the fact that behavioral VHDL is more abstract (or higher) than structural style.

In contrast, since the structural/dataflow style describes logic units with known implementations, these VHDL codes almost always synthesize. Also, assembling large systems (such as Platform FPGAs) requires structural style at the top-level since it is combining large function units (processors, peripherals, etc.) It is also worth noting that some structural codes do not synthesize well. An example of this is using a large RAM in a hardware design. A RAM is not difficult to describe structurally because of its simple, repetitive design. However, in simulation this tends to produce a large data structure and that needs to be traversed every time a signal changes. In contrast, a behavioral model of RAM simulates quickly because it matches the processor's architecture well.

## 2.2.2 Verilog

Another common hardware description language is Verilog. Verilog has many similarities to VHDL as both were originally intended describe hardware circuit designs. Verilog is considered to be less verbose than VHDL, often making it easier to use, especially for designers more familiar with an imperative coding style like C++ or Java. As with VHDL, Verilog became more than just a textual representation of a circuit. Designers used Verilog to simulate circuits which eventually led to a subset of the language supporting hardware synthesis.

In Verilog, there are three major styles or forms of writing hardware descriptions. Both styles are valid VHDL codes; however they model hardware differently. This impacts synthesis, simulation, and, in some cases, designer productivity. These forms are:

Gate Level Modeling Circuits are described in terms of logic units.

Structural Circuits are described in terms of modules.

**Behavioral** Circuits are described in an imperative (procedural) language to describe how the outputs are related to the inputs.

## 2.3 Xilinx Integrated Software Environment

The Integrated Software Environment (ISE) contains a suite of commands that can turn FPGA designs described in hardware description languages and netlists into bitstream configuration files. To gain a better understanding of the tool flow it is necessary to cover the underlying commands [17] that are called by the ISE GUI.

## 2.3.1 Xilinx Synthesis Tool

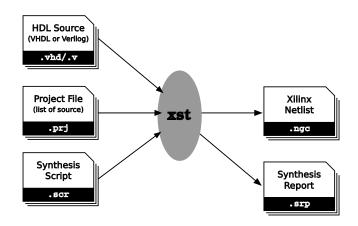

At the core of the ISE tool chain is the Xilinx Synthesis Tool [18] (XST). XST is used to synthesize hardware description languages into a netlist. XST is not the only synthesis tool available; however, as it is available within the ISE tool chain, it is the most obvious synthesis tool to use.

To help understand how XST works, let's begin by synthesizing a simple VHDL version of a 1-bit full adder. In addition to the VHDL file, two files are needed to run XST in commandline mode. These two files are the project file and the synthesis script file. The project file specifies all of the HDL in the project to be synthesized. It is commonly named with the extension .prj. In the full adder example, only one VHDL file exists so the project file simply contains:

#### vhdl work fadder.vhd

The three columns denote the HDL type, library name and VHDL filename. The work library is the default library to use.

```

run

-ifn fadder.prj

-ofn fadder.ngc

-ofmt NGC

-top fadder

-opt_mode Speed

-opt_level 1

-iobuf NO

-p xc5vfx130t-ff1738

```

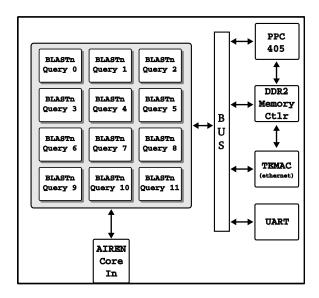

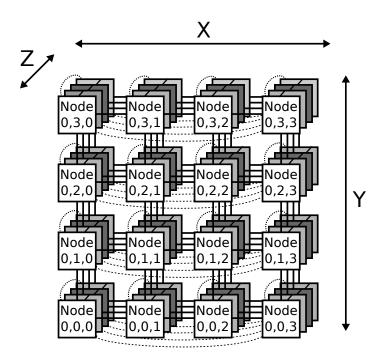

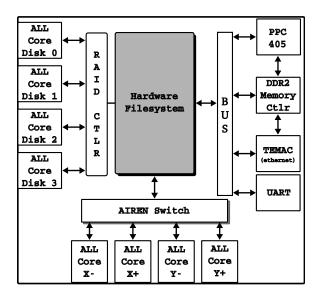

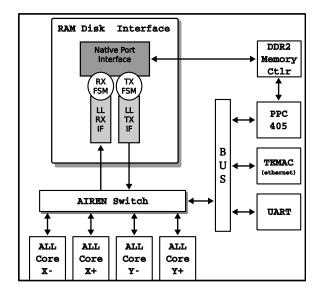

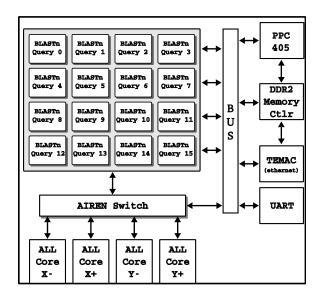

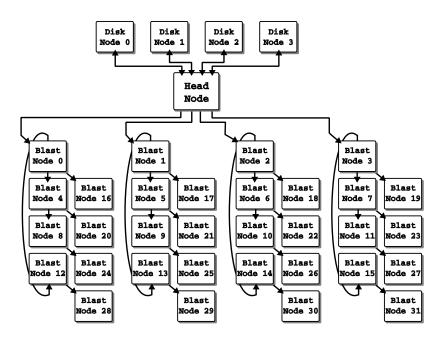

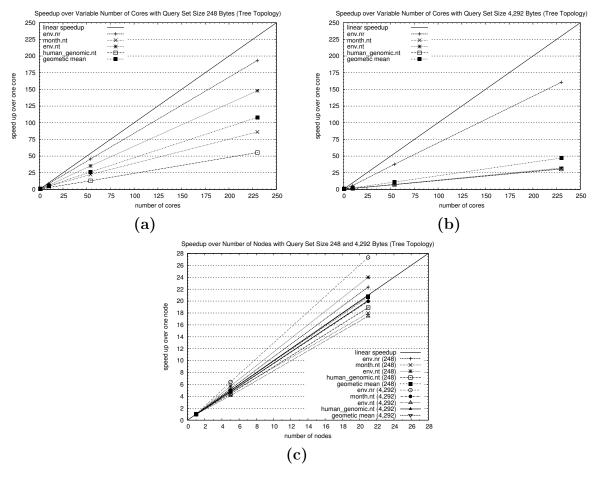

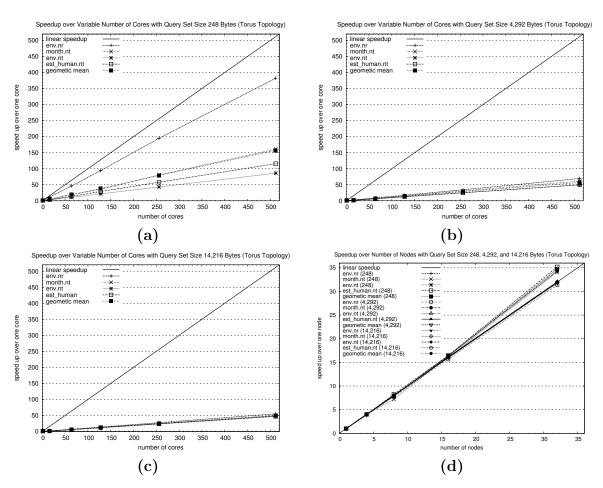

Figure 2.8: sample synthesis script for XST