## A SECURE SOC PLATFORM FOR SECURITY ASSESSMENTS IN FPGAS

by

# Geraldine Shirley Nicholas

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2023

| Approved by:          |

|-----------------------|

| Dr. Fareena Saqib     |

| Dr. Ahmed Arafa       |

| Dr. Arindam Mukherjee |

| Dr. Gabor Hetyei      |

©2023 Geraldine Shirley Nicholas ALL RIGHTS RESERVED

### ABSTRACT

GERALDINE SHIRLEY NICHOLAS. A SECURE SOC PLATFORM FOR SECURITY ASSESSMENTS IN FPGAS. (Under the direction of DR. FAREENA SAQIB)

With the rapid increase in connected devices and SoC design architecture being used in diverse platforms, they become potential targets to gain unauthorized access for data and privacy invasion. Therefore, heterogeneous SoC architecture raises security concerns in addition to the benefits they offer with improved throughput. They are susceptible to side-channel attacks where secure information is extracted through communication channels. Crypto algorithms implemented for secure authentication tend to leak sensitive information jeopardizing system security. Memory corruption vulnerabilities, code injection, buffer overflow attacks and other software-based attacks through untrusted channels tend to control the flow of the application with malicious data. Though traditional defense mechanisms have been implemented they are all still vulnerable to side-channel attacks.

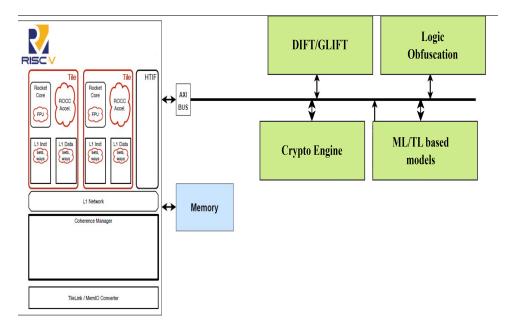

Secure measures to protect the interfaces and data propagation through different channels are critical and building a resilient model consists of the on-chip security factors. In this work, a platform based SoC model is implemented to meet the security objectives using the RISC-V architecture in which an information flow tracking module tracks the flow of data for the system's integrity along with crypto engines and a secure boot mechanism for secure device authentication providing encrypted data transfers. For bitstream resilient SoC models the work extends a logic obfuscation module with runtime security leading to a secure assessment framework. This work explores the microarchitectural vulnerabilities with Machine Learning models and proposes a Transfer Learning technique based counterfeit detection scheme for supply chain vulnerability.

## **DEDICATION**

This dissertation is dedicated to God and my family, for without their love and support, none of this would be made possible. To my father who has always believed in me and has encouraged me to further myself. To my mother, for the love and care to keep me going. To my brother, who has always taught me to work hard for the things I aspire to achieve. This work is also dedicated to my husband Binesh Kumar, who has been a constant source of support and encouragement during the challenges of graduate school and life. He has also been an inspiration throughout this journey of mine and therefore plays a crucial part in my success.

## ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere gratitude to my advisor Dr. Fareena Saqib, for the continuous support and encouragement throughout my research. For her patience, motivation, valuable comments, suggestions, and immense knowledge to make the research meaningful.

Also, I would like to thank and acknowledge my committee members: Dr. Arindam Mukherjee, Dr. Ahmed Arafa and Dr. Gabor Hetyei for providing encouraging and constructive feedback in developing my research.

Finally, I would like to thank all my friends who contributed to the research: Chaitanya Mukund Bhure, Dhruvakumar Aklekar and Vineet Chadalavada.

# TABLE OF CONTENTS

| LIST OF | TABLE    | S                             | xi  |

|---------|----------|-------------------------------|-----|

| LIST OF | FIGUR    | ES                            | xii |

| LIST OF | ABBRE    | EVIATIONS                     | XV  |

| СНАРТ   | ER 1: IN | TRODUCTION                    | 1   |

| 1.1.    | Motivati | ion                           | 1   |

| 1.2.    | Contribu | utions                        | 2   |

| 1.3.    | Organiza | ation                         | 3   |

| СНАРТ   | ER 2: BA | ACKGROUND STUDY               | 5   |

| 2.1.    | System-o | on-Chip Security              | 5   |

|         | 2.1.1.   | Hardware security             | 7   |

|         | 2.1.2.   | System or platform security   | 7   |

|         | 2.1.3.   | Cloud security                | 8   |

| 2.2.    | Key Fac  | tors of SoC Platform Security | 8   |

|         | 2.2.1.   | Root of Trust                 | 8   |

|         | 2.2.2.   | Secure boot                   | 9   |

|         | 2.2.3.   | Execution Level Security      | 10  |

| 2.3.    | Access C | Control Mechanism             | 11  |

| 2.4.    | Informat | tion Flow Tracking            | 11  |

|         | 2.4.1.   | Coarse Grained IFT Models     | 12  |

|         | 2.4.2.   | Fine Grained IFT Models       | 14  |

| 2.5.    | Trusted  | Execution Environment         | 15  |

|                                                                                                                                                                                                                                                                                                                                                 |                                  |           |                                                                                 | vii |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------|---------------------------------------------------------------------------------|-----|

|                                                                                                                                                                                                                                                                                                                                                 | 2.6.                             | Logic Ob  | ofuscation                                                                      | 16  |

|                                                                                                                                                                                                                                                                                                                                                 | 2.7.                             | Security  | Models                                                                          | 17  |

|                                                                                                                                                                                                                                                                                                                                                 |                                  | 2.7.1.    | ARM Trustzone                                                                   | 17  |

|                                                                                                                                                                                                                                                                                                                                                 |                                  | 2.7.2.    | Intel SGX                                                                       | 18  |

|                                                                                                                                                                                                                                                                                                                                                 |                                  | 2.7.3.    | RISC-V                                                                          | 20  |

| СН                                                                                                                                                                                                                                                                                                                                              |                                  |           | CURITY-AWARE DESIGN FLOW FOR BITSTREAM                                          | 23  |

|                                                                                                                                                                                                                                                                                                                                                 | 3.1.                             | Introduc  | tion                                                                            | 23  |

|                                                                                                                                                                                                                                                                                                                                                 | 3.2.                             |           | nodel for Boot Process and Runtime Security of a Reigurable Device in the Field | 24  |

|                                                                                                                                                                                                                                                                                                                                                 |                                  | 3.2.1.    | Boot-Time bitstream modification                                                | 24  |

|                                                                                                                                                                                                                                                                                                                                                 |                                  | 3.2.2.    | Runtime attacks                                                                 | 24  |

|                                                                                                                                                                                                                                                                                                                                                 | 3.3.                             | Secure D  | esign Flow                                                                      | 25  |

|                                                                                                                                                                                                                                                                                                                                                 |                                  | 3.3.1.    | Secure Boot Mechanism                                                           | 25  |

|                                                                                                                                                                                                                                                                                                                                                 |                                  | 3.3.2.    | Obfuscation Framework                                                           | 27  |

|                                                                                                                                                                                                                                                                                                                                                 |                                  | 3.3.3.    | Secure IP Using ARM TrustZone                                                   | 28  |

| 2.7.2. Intel SGX 2.7.3. RISC-V  CHAPTER 3: SECURITY-AWARE DESIGN FLOW FOR SECURITY  3.1. Introduction  3.2. Threat model for Boot Process and Runtime Secconfigurable Device in the Field  3.2.1. Boot-Time bitstream modification  3.2.2. Runtime attacks  3.3. Secure Design Flow  3.3.1. Secure Boot Mechanism  3.3.2. Obfuscation Framework | ntation and Experimental Results | 29        |                                                                                 |     |

|                                                                                                                                                                                                                                                                                                                                                 | 3.5.                             | Security  | Analysis                                                                        | 34  |

|                                                                                                                                                                                                                                                                                                                                                 | 3.6.                             | Conclusio | on                                                                              | 35  |

| СН                                                                                                                                                                                                                                                                                                                                              |                                  |           |                                                                                 | 36  |

|                                                                                                                                                                                                                                                                                                                                                 | 4.1.                             | Introduc  | tion                                                                            | 36  |

|                                                                                                                                                                                                                                                                                                                                                 | 4.2.                             | Threat n  | nodel                                                                           | 37  |

|                                                                                                                                                                                                                                                                                                                                                 | 4.3.                             | Advance   | d Encryption Standard                                                           | 37  |

|         |           |                                                  | viii |

|---------|-----------|--------------------------------------------------|------|

| 4.4. D  | Design In | nplementation and Experimental Results           | 38   |

| 4       | 1.4.1.    | AES Algorithm Implementation using Chisel        | 39   |

| 4       | 1.4.2.    | Hardware based AES Accelerator                   | 43   |

| 4.5. S  | Security  | Analysis                                         | 47   |

| 4.6. C  | Conclusio | on                                               | 47   |

|         |           | ARSE-GRAINED HARDWARE-BASED INFORMA-<br>TRACKING | 48   |

| 5.1. In | ntroduct  | cion                                             | 48   |

| 5.2. T  | Threat m  | nodel                                            | 49   |

| 5       | 5.2.1.    | Buffer Overflow Attacks                          | 49   |

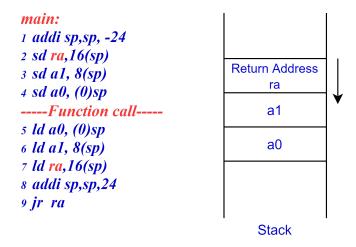

| 5       | 5.2.2.    | Return Address Attacks                           | 50   |

| 5.3. R  | RISC-V    | Architectural Design Approach                    | 51   |

| 5       | 5.3.1.    | RISC-V Core                                      | 52   |

| 5       | 5.3.2.    | Tag Mechanism                                    | 53   |

| 5       | 5.3.3.    | Security Policies                                | 54   |

| 5.4. C  | Compiler  | -Specific Simulation Model                       | 55   |

| 5.5. E  | Experime  | ental Results                                    | 56   |

| 5       | 5.5.1.    | Architectural Model                              | 56   |

| 5       | 5.5.2.    | Simulation Model                                 | 58   |

| 5.6. S  | Security  | Analysis                                         | 59   |

| 5.7. C  | Conclusio | on                                               | 60   |

|                                                                                                             | ix |

|-------------------------------------------------------------------------------------------------------------|----|

| CHAPTER 6: MULTI GRANULAR LEVEL BASED INFORMATION FLOW TRACKING                                             | 61 |

| 6.1. Introduction                                                                                           | 61 |

| 6.2. Threat model                                                                                           | 61 |

| 6.2.1. Data Level Leakage                                                                                   | 62 |

| 6.3. RISC-V Architectural Design Approach                                                                   | 63 |

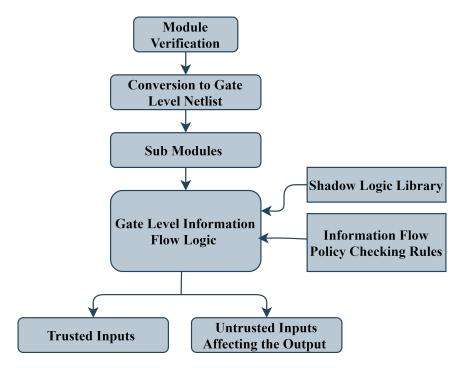

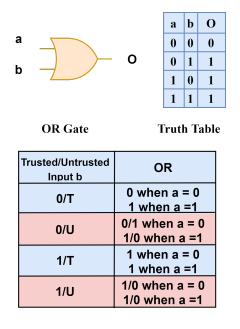

| 6.3.1. Shadow Logic for tainted gates                                                                       | 64 |

| 6.4. Information Flow Policy Checking                                                                       | 65 |

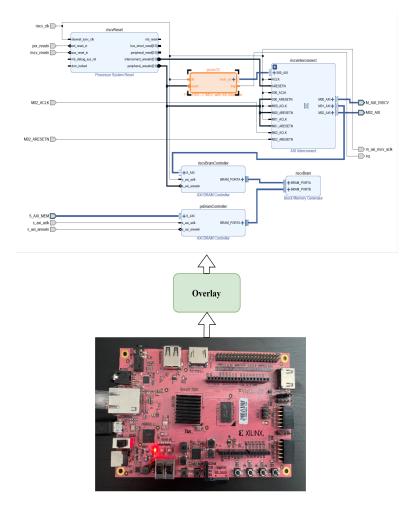

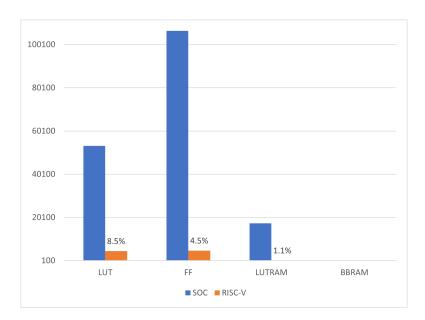

| 6.5. Experimental Results                                                                                   | 67 |

| 6.5.1. Netlist and submodules                                                                               | 67 |

| 6.6. Security Analysis                                                                                      | 70 |

| 6.7. Conclusion                                                                                             | 71 |

| CHAPTER 7: MICRO-ARCHITECTURAL VULNERABILITIES WITH MACHINE LEARNING MODELS AND TRANSFER LEARNING TECHNIQUE | 72 |

| 7.1. Introduction                                                                                           | 72 |

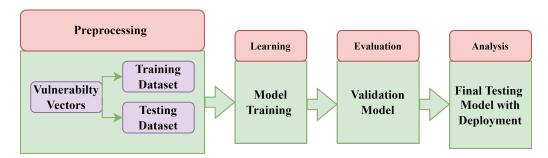

| 7.2. Machine Learning Models                                                                                | 73 |

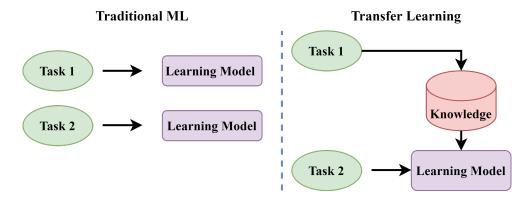

| 7.3. Transfer Learning                                                                                      | 75 |

| 7.4. Hardware Security Vulnerabilities                                                                      | 76 |

| 7.5. IC Counterfeit Detection Mechanism                                                                     | 77 |

| 7.5.1. Image Augmentation with Preprocessing Layers                                                         | 77 |

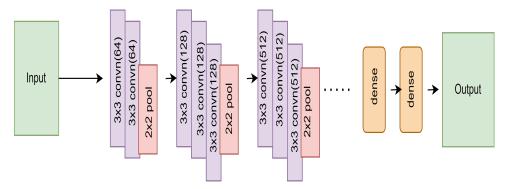

| 7.5.2. Pre-trained Convolution Models                                                                       | 78 |

| 7.6. Experimental Results                                                                                   | 79 |

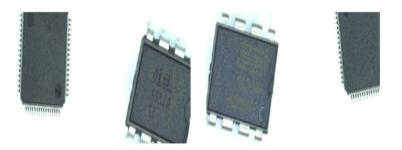

| 7.6.1. Training Data                                                                                        | 79 |

|                                       | X  |  |

|---------------------------------------|----|--|

| 7.6.2. Testing Data                   | 80 |  |

| 7.7. Security Analysis                | 82 |  |

| 7.8. Conclusion                       | 83 |  |

| CHAPTER 8: CONCLUSION AND FUTURE WORK | 84 |  |

| REFERENCES                            | 86 |  |

|   | •   |

|---|-----|

| v | 1   |

| Λ | . 1 |

# LIST OF TABLES

| TABLE 2.1: RISC-V compatible countermeasures                                                  | 22 |

|-----------------------------------------------------------------------------------------------|----|

| TABLE 3.1: Fault impact summary for the ISCAS- $85/89$ benchmarks                             | 32 |

| TABLE 3.2: Average Hamming Distance (50%) for the benchmark circuits with different key sizes | 32 |

| TABLE 4.1: Resource Utilization of the AES core                                               | 45 |

| TABLE 5.1: Resource Utilization of IFT Module                                                 | 57 |

| TABLE 6.1: Execution Time Of ISCAS 85,89 And EPFL Benchmarks                                  | 70 |

| TABLE 6.2: Resource Utilization of Proposed RISC-V IP                                         | 70 |

| TABLE 7.1: Classification Report                                                              | 82 |

# LIST OF FIGURES

| FIGURE 2.1: Security Challenges in a Connected Network                                                         | 6  |

|----------------------------------------------------------------------------------------------------------------|----|

| FIGURE 2.2: Key factors affecting the SoC Platform Security                                                    | 10 |

| FIGURE 2.3: Tag bits assigned to untrusted sources by the IFT module                                           | 13 |

| FIGURE 2.4: Gate level IFT with shadow logic                                                                   | 15 |

| FIGURE 2.5: Logic-locked circuit with two new key gates added in C17 circuit                                   | 16 |

| FIGURE 2.6: ARM TrustZone implementation                                                                       | 18 |

| FIGURE 2.7: SGX Model                                                                                          | 19 |

| FIGURE 2.8: Freedom E31 core with RISC-V ISA Specification                                                     | 21 |

| FIGURE 3.1: Secure boot authentication and key exchange process                                                | 26 |

| FIGURE 3.2: Key Gate Insertion Framework                                                                       | 28 |

| FIGURE 3.3: AXI communication signals                                                                          | 29 |

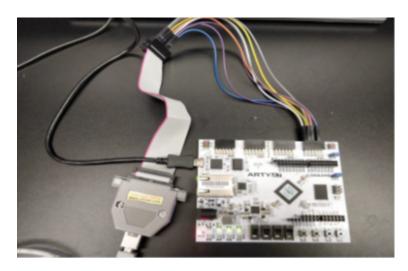

| FIGURE 3.4: Hardware setup                                                                                     | 30 |

| FIGURE 3.5: System block with secure IPs                                                                       | 31 |

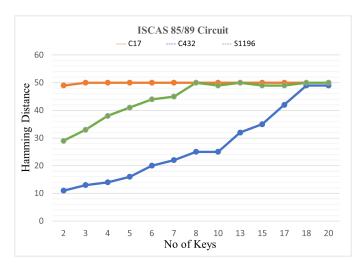

| FIGURE 3.6: Hamming distance between the outputs of designs on applying the correct key and a random wrong key | 33 |

| FIGURE 3.7: Design using AXI GPIO Ports for Secure IP                                                          | 34 |

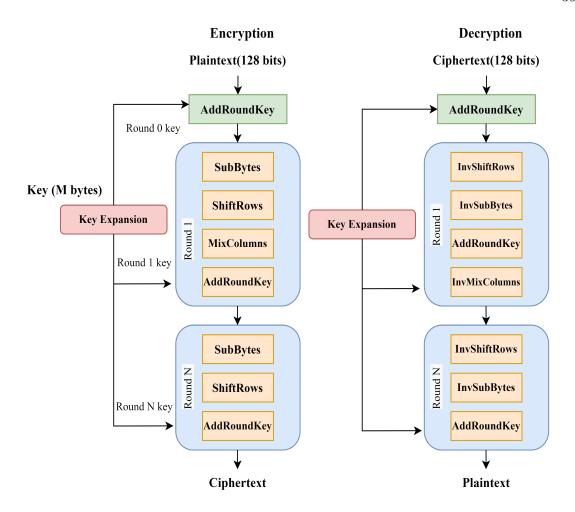

| FIGURE 4.1: Overall structure of AES with 128- bit encryption key                                              | 39 |

| FIGURE 4.2: AES algorithm block diagram                                                                        | 40 |

| FIGURE 4.3: Pseudo code of the encryption algorithm                                                            | 41 |

| FIGURE 4.4: Hardware setup with JTAG Debugger                                                                  | 42 |

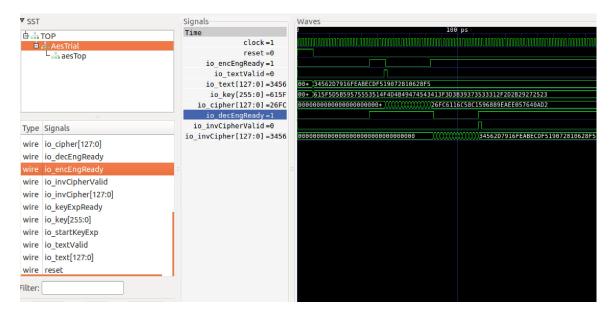

| FIGURE 4.5: Simulation Results                                                                                 | 43 |

|                                                                                                                     | xiii |

|---------------------------------------------------------------------------------------------------------------------|------|

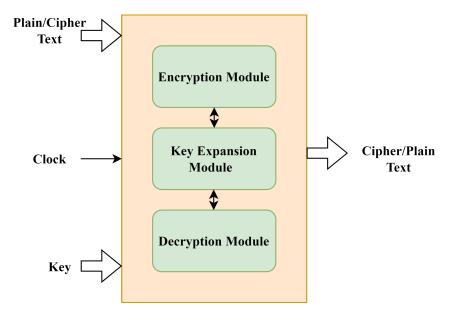

| FIGURE 4.6: AES Engine                                                                                              | 43   |

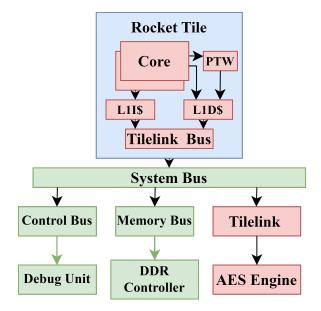

| FIGURE 4.7: AES block diagram with the RISC-V core                                                                  | 44   |

| FIGURE 4.8: AES Algorithm instantiated with the RISC-V core                                                         | 44   |

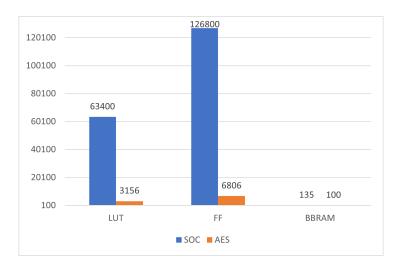

| FIGURE 4.9: Relative resource utilization of RISC-V                                                                 | 45   |

| FIGURE 4.10: Relative resource utilization of AES                                                                   | 46   |

| FIGURE 4.11: Hello world application running on the modified RISC-V core.                                           | 46   |

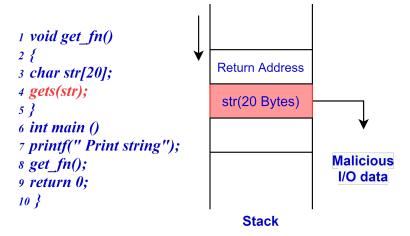

| FIGURE 5.1: Buffer Overflow Attack                                                                                  | 50   |

| FIGURE 5.2: Return Address Attack                                                                                   | 51   |

| FIGURE 5.3: IFT design with RISC-V core                                                                             | 54   |

| FIGURE 5.4: Field Format to add new instructions in RISC-V                                                          | 55   |

| FIGURE 5.5: Pseudo code for Tag Module with Tag Cache                                                               | 57   |

| FIGURE 5.6: Buffer overflow attack in RISC-V Architecture without IFT module                                        | 59   |

| FIGURE 5.7: IFT module implemented eliminating the attack by exception                                              | 59   |

| FIGURE 6.1: Trojan insertion in Gate Level Circuit                                                                  | 63   |

| FIGURE 6.2: RISC-V core Tag mechanism and Gate Level IFT                                                            | 64   |

| FIGURE 6.3: Gate Level IFT Model Flow                                                                               | 66   |

| FIGURE 6.4: OR Gate Shadow Logic Truth Table                                                                        | 66   |

| FIGURE 6.5: PYNQ flow with the RISC-V IP and AXI Interface designed for the PYNQ board using Overlay                | 68   |

| FIGURE 6.6: Gate Level IFT detecting the untrusted gate (NAND) for the submodule Priority Encoder B in c432 circuit | 69   |

| FIGURE 6.7: Relative Resource Utilization                                                                           | 71   |

|                                                                       | xiv |

|-----------------------------------------------------------------------|-----|

| FIGURE 7.1: ML workflow applied for hardware vulnerability analysis   | 73  |

| FIGURE 7.2: Traditional Machine Learning and Transfer Learning Model  | 76  |

| FIGURE 7.3: VGG-16 Architecture                                       | 78  |

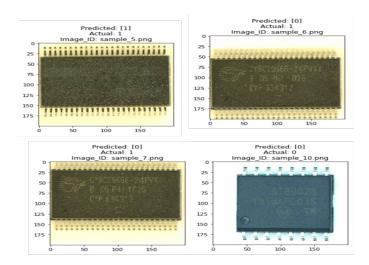

| FIGURE 7.4: Validated Images using Image Augmentation                 | 80  |

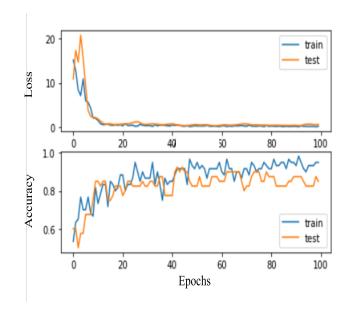

| FIGURE 7.5: Accuracy and Loss Plot for VGG-16 model                   | 80  |

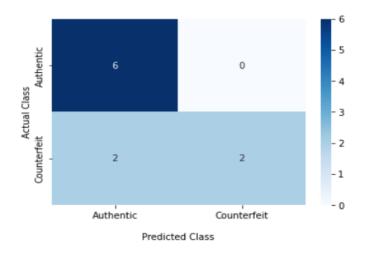

| FIGURE 7.6: Confusion matrix for the VGG-16 model                     | 81  |

| FIGURE 7.7: True class and predicted authentic and counterfeit images | 82  |

| FIGURE 8.1: Design components implemented for the SoC Secure Model    | 85  |

## LIST OF ABBREVIATIONS

AES Advanced Encryption Standard

AMD Advanced Micro Devices

API Application Program Interface

ARM Advanced RISC Machine

ASIC Application-Specific Integrated Circuits

AXI Application Extensible Interface

BBRAM Battery Backup Random Access Memory

CEP Common Evaluation Platform

CHISEL Constructing Hardware in a Scala Embedded Language

CNN Convolutional Neural Network

CRAS Cryptographic Return Address Stack

CSR Control and Status Register

DIFT Dynamic Information Flow Tracking

DSLR Digital Single-Lens Reflex

EDA Electronic Design Automation

EMF Electro Magnetic Field

FIFO First In First Out

FIRRTL Flexible Intermediate Representation for RTL

FPGA Field Programmable Gate Array

FSBL First Stage Boot Loader

GLIFT Gate Level Information Flow Tracking

GNU GNU Not Unix

GPIO General Purpose Input Output

HDFI Hardware Assisted Data-Flow Isolation

HDL Hardware Description Language

HELPPUF Hardware Embedded Delay PUF

IC Integrated Chip

ICAP Internal Configuration Access Port

IFT Information Flow Tracking

IoT Internet of Things

ISA Instruction Set Architecture

JTAG Joint Test Action Group

LRN Local Response Normalization

LUT LookUp Table

MIT Mixed-mode Information Flow Tracking

ML Machine Learning

OS Operating System

PCAP Processor Configuration Access Port

PL Programmable Logic

PRM Processor Reserved Memory

PS Processing System

PSA Platform Security Architectures

PUF Physical Unclonable Function

RISC-V Reduced Instruction Set Architecture

RSA Rivest Shamir Adleman

RTL Register Transfer Level

SAT Boolean Satisfiability

SCA Side Channel Analysis

SFLL Secure Function Logic Locking

SGX Software Guard Extensions

SoC System-on-a-Chip

SVM Support Vector Machine

TEE Trusted Execution Environment

TPM Trusted Platform Module

TZASC TrustZone Address Space Controller

TZMA TrustZone Memory Adapter

VGG Visual Geometry Group

#### CHAPTER 1: INTRODUCTION

#### 1.1 Motivation

Modern heterogeneous computing systems, which incorporate IoT devices and networks, have the potential to deliver high-speed, optimized performance with enhanced capabilities. However, due to the increased number of components required to achieve such results, these systems are susceptible to various security threats. When an active device is connected to a network, it becomes vulnerable to firmware and hardware attacks, where the former involves exploiting vulnerabilities in different system components to gain control over the entire system, and the latter requires safeguarding the System-on-Chip (SoC) design against unauthorized access and data leakage [1]. The development of frameworks for protecting hardware security attacks is primarily dependent on the Intellectual Property (IP) and system architecture.

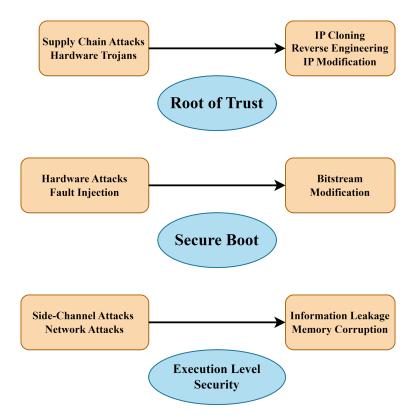

To develop a secure SoC platform, it is crucial to identify the security vulnerabilities of the system, especially in platforms with different levels of abstraction. The key factors for ensuring the security of an SoC platform are the Root of Trust [2], Secure Boot, and Execution Level Security. The Root of Trust employs a set of modules with diverse security features to monitor system functionality and provide secure authentication for each component in the system. Secure Boot establishes the integrity of the firmware and builds trust between the system and firmware before the execution of an application through authentication and validation. Execution Level Security provides access control and information flow tracking from various channels, along with a Trusted Execution Environment (TEE) to isolate security-critical components in the system.

Protecting interfaces and data propagation across various channels is critical, and

building a resilient model requires on-chip security measures. Although traditional architectures provide a secure environment to some extent, they fail to ensure different levels of security within a system. Thus, a platform based SoC model can serve as a foundation for evaluation tools and techniques to achieve security objectives. To build a robust side-channel analysis framework, RISC-V architecture is utilized due to its ability to provide a platform for the custom implementation of security extensions compared to other traditional architectures. Additionally, RISC-V is an open-source Instruction Set Architecture (ISA) which further adds to its benefits. This research focuses on addressing the significant threats in an SoC design architectural platform and presenting novel security enhancements using RISC-V architecture.

#### 1.2 Contributions

This research has the following contributions towards major challenges in an SoC Design and Architectural Platform.

- Identifies security threats and presents threat models that affect an SoC Design and Architectural Platform. Existing work and their shortcoming are also discussed.

- Proposes a novel device authentication scheme for runtime bitstream security.

This framework employs logic-locking mechanism and extents its applications of secure boot process for FPGAs along with ARM TrustZone for secure configuration.

- Design of an extensible hardware cryptographic accelerator compatible with the RISC-V model in which an AES cryptographic engine with encryption function is used during critical data transfers.

- Proposes a RISC-V design of a coarse-grained hardware-based Information Flow

Tracking framework with a tagged mechanism at the architectural level which

detects security violations at runtime. This model uses a one-bit tag to track the data flow from untrusted channels with a separate tag cache module for minimal overhead.

- Proposes a RISC-V design of a fine-grained Gate level-based Information Flow Tracking framework for security critical datapath using optimized shadow logic for leakage model. This scheme focuses on a specific security critical module and the datapath of the module to be executed to overcome the performance and area overhead from existing schemes. Translation from the instruction level to the data level is based on the module instantiation with security-critical data.

- Presents microarchitectural vulnerabilities in the SoC design along with different machine learning models for SoC security validation and verification. This work proposes a transfer learning based counterfeit detection scheme for supply chain vulnerability.

#### 1.3 Organization

This document is organized as follows:

Chapter 2 describes the background information on the topics involved in this research along with the overview of the existing works related to SoC Design Security and Architectural Platforms.

Chapter 3 presents a security-aware design flow scheme with secure boot features and logic locking applications for bitstream security with ARM TrustZone enabled isolation.

Chapter 4 details the contribution of the proposed extensible hardware cryptographic accelerator for the RISC-V model.

Chapter 5 proposes the coarse-grained hardware-based Information Flow Tracking framework with the performance analysis.

Chapter 6 proposes the fine-grained gate-level-based Information Flow Tracking framework with optimized shadow logic for security critical data modules.

Chapter 7 extends the research to microarchitectural vulnerabilities with Machine Learning Models and Transfer Learning Technique based counterfeit detection model. Lastly, the conclusions of the research are presented in Chapter 8.

#### CHAPTER 2: BACKGROUND STUDY

## 2.1 System-on-Chip Security

Due to its utilization in cyber-physical systems, embedded computing systems, and the Internet of Things (IoT), security has become a critical component of SoC design. With the SoC market projected to exceed 207 billion dollars by the end of 2023, the model faces new vulnerabilities and increased cyberattacks, posing reliability issues [3]. As computing devices are employed in various applications, they are susceptible to a vast amount of sensitive data and critical information that must be safeguarded against malicious access. The analysis and evaluation of resilient mechanisms against different attack models are significant aspects of SoC design. Four major types of attack scenarios must be considered when examining reference models for security and challenges in the SoC Design and Architectural Platform:

- Insertion of Malware/Unwanted Application gaining access: By using system software privilege levels, an adversary can insert a hidden functionality that tracks critical data and information or triggers disruptive outcomes in a connected network. In addition, malicious modification to the circuit can be done by bypassing the security fence of the system.

- Side-channel attacks: One of the most common methods of security exploitation involves obtaining information on crypto engines through communication channels within a system. This method enables an adversary to reverse engineer system functions by monitoring power consumption or electromagnetic fields associated with the hardware to gain access to the network. Additionally, memory access patterns and timing information at run time are targeted to

exploit vulnerabilities in the system.

- Supply Chain Attacks: The globalized Integrated Chip (IC) supply chain has the potential to be vulnerable to malicious design modifications or IP theft through reverse engineering [6]. On the other hand, in software supply chain attacks, the focus is on an unsecured network or infrastructure, which can be targeted by malicious code to compromise build tools.

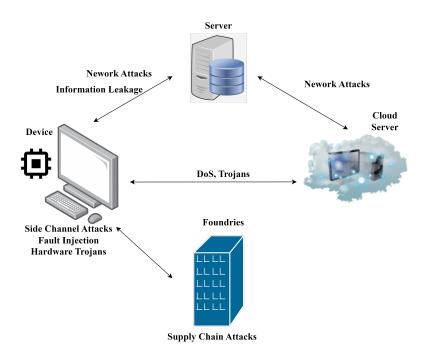

- Network Attacks: Denial of Service in a distributed network results in bridging through the system and gaining access to it. This type of attack can cause significant disruption to the availability of the system and the services it provides. Figure 2.1 illustrates the different security challenges in a connected network.

Figure 2.1: Security Challenges in a Connected Network

To ensure a secure architecture, it's essential to protect the application from untrusted sources and various vulnerabilities that may compromise the system's security. These threats include malicious IPs in hardware, vulnerable firmware, and

side-channel vulnerabilities through different communication channels. Secured SoC models must implement robust security policies to prevent unauthorized access to the devices, including authentication, confidentiality, integrity, and access control to the system. There are three different groups in which security assurance can be classified, owing to the complex roots of security assurance.

## 2.1.1 Hardware security

Hardware platforms and ICs utilized in diverse applications are susceptible to threats that may arise throughout different phases of the component's lifecycle. Hardware security pertains to the security concerns resulting from underlying hardware and architectural vulnerabilities that affect the design, implementation, and validation of security operations in such models. Malicious alterations of ICs, IP piracy, reverse engineering, and unauthorized access to privileged resources via debugging channels are some common hardware attacks. Current approaches predominantly prioritize safeguarding against hardware supply chain attacks, which include Hardware Trojan attacks, counterfeit IPs, and implementation-dependent vulnerabilities in cryptographic modules leading to the exposure of sensitive information [5].

## 2.1.2 System or platform security

The platform security architecture refers to vulnerabilities that may arise from functional and performance aspects of the system, which malicious third parties may exploit during runtime. These include the leakage of security-critical data and side-channel attacks that can alter the system's behavior. Protecting sensitive information stored in hardware from untrusted software and networks is critical, and this is achieved through various levels of isolation. Access control and information flow policies with validation are implemented to ensure a robust and secure system [6]. Authentication and security controls serve as methods of protecting information and mitigating unauthorized access.

## 2.1.3 Cloud security

Providing resource sharing and on-demand services, cloud computing offers a distributed work environment with extensive functionality and data storage. While advantageous over traditional systems, there are privacy and security concerns that allow adversaries to gain unauthorized control over stored data. Cloud security involves vulnerabilities and security issues that arise from communication channels in a client-server model, where critical data is transmitted through the network cloud [7]. Cloud-based attacks include data breaches, denial of service, and corruption of collected data integrity through backdoor channels leading to remote access. To develop a secure platform for an SoC with various abstraction levels, it is essential to identify the system's security vulnerabilities. The key factors of SoC Platform Security are as follows.

## 2.2 Key Factors of SoC Platform Security

#### 2.2.1 Root of Trust

The Root of Trust is a crucial system component that ensures data integrity and verifies the functionality and design of the system. It can be either hardware or software-based, with hardware Root of Trust being the most secure option, as it establishes a high level of trust by verifying its own integrity. The most secure hardware Root of Trust is a stand-alone security module or one that is implemented within a processor or System on Chip, ensuring isolation of resources, keys, and security assets, along with a side channel resistant model and multiple layers of defense mechanisms [8]. The Trusted Platform Module (TPM) [9] is an example of a tamper-evident hardware module that provides Root of Trust measurement, remote attestation, and cryptographic functions for the protection of both keys and sensitive data. The Physical Unclonable Function (PUF) [10] based security is another hardware Root of Trust that enables unique IDs with true random number generation and secure key stor-

age, with an anti-tampering design. To establish a trusted supply chain platform, methodological approaches such as PUF technology and obfuscation techniques for SoC design can be employed to support Root of Trust features [11].

### 2.2.2 Secure boot

The programmable logic in SoC FPGAs supports both hardwired microprocessors and soft-IP-based ones. These devices are programmed through bitstreams, and an attack on the bitstream can jeopardize the entire system operation while it is deployed in the field. FPGA bitstream reverse engineering is a major concern since reverse engineering and other fault injection-based attacks can manipulate the cryptographic components, compromising the system's confidentiality and data integrity. To address this problem, various solutions such as authentication of bitstreams and encryption models have been proposed [12]. For instance, Xilinx provides a secure boot mechanism with authenticated bitstreams to safeguard against such vulnerabilities [13]. Additionally, secure root of trust architecture with TPM drivers and over-the-air updates is implemented to detect malicious modifications in configuration files [14]. Multilayered secure boot is another approach that updates the LookUp Table (LUT) frames using remote attestation and PUF-based mutual authentication during runtime [15]. Self-authentication secure boot mechanism uses PUF-based authentication to protect the secure boot process, and any modification made to unencrypted bitstreams results in key regeneration failure of the PUF [16]. For securing open-source architectures, a lightweight RISC-V-based secure boot framework with PUF and different encryption standards with secure remote key attestation is implemented [17]. Figure 2.2 shows the key factors that impact SoC Platform Security.

Figure 2.2: Key factors affecting the SoC Platform Security

## 2.2.3 Execution Level Security

To protect system assets from unauthorized access, SoC security is essential. The execution level security measures the access control mechanisms, information flow control, and isolation of the programs that are necessary to protect confidential information stored in the computing system. The access to the assets can be dependent on the state of execution, and hence, run time vulnerabilities need to be considered while implementing security measures. System-level policy classes for risk assessment are focused on execution level security. Information leakage models are secured by memory protection using programmable hardware monitors [18]. During the design phase, static techniques such as binary code checks [19] and verification tools [20] for program validation are implemented. Hardware-based techniques detect memory-based vulnerabilities like buffer overflow and format strings during runtime [21]. Hardware-based technologies have better processing speed and smaller resource

overhead, making them more efficient than software-based methods [22].

#### 2.3 Access Control Mechanism

Communication between devices connected to a network for data transfer can expose them to untrusted nodes that can exploit software vulnerabilities, making them susceptible to attacks at the application level as well as the firmware level. Therefore, it is necessary to provide attestation of the firmware to ensure that the device proves that it is attested with a trusted remote entity [23]. In addition, authentication is a process that verifies the identity of the user to access the system, while authorization is an access control mechanism that determines access rights based on the security operations performed on the system. To ensure authorized access and bitstream protection for reconfigurable devices, an authentication and encryption mechanism with access control functionality is required. Access control involves a set of class policies to access hardware and software components during execution [24]. Secured communication channels with multi-level security using PUFs for remote key updates provide access management and bitstream verification [25], thereby safeguarding the data and the system from malicious modifications.

#### 2.4 Information Flow Tracking

Heterogeneous System on Chips and IoT devices connected to communication channels face the risk of information leakage and code injection due to their vulnerability to untrusted systems. Information Flow Tracking (IFT) technique is a promising analysis technique for security applications that enables the detection of information leakage and malicious data in real-time. Different IFT approaches, based on static verification during the design phase or dynamic checking at runtime, have been implemented. The precision of the IFT logic and the granularity of the building blocks determine the levels of abstraction. IFT implementations include both hardware and software-based approaches and depend on the explicit and implicit flow of data to

design conditional behaviors for the model. In this section, existing IFT implementations based on precision granularity models will be discussed.

## 2.4.1 Coarse Grained IFT Models

At the architectural level, Information Flow Tracking implementations offer a security mechanism for metadata propagation and security policies by providing a coarse-grained precision logic with a dedicated tag mechanism. These implementations can either be hardware-based, depending on the architectural features and datapath of the ISA model, or coarse-grained models that track control-sensitive information along with program variables and independent labels. The access and information flow with tags can be achieved through a dedicated co-processor or a modified ISA with tag modules. Buffer overflow attacks and memory corruption can be prevented by identifying malicious data, and IFT models protect the system from these attacks [26][27].

Several IFT models have been developed to improve security. For instance, Flexi-Taint [28] is an IFT model that supports an accelerator with tainted security policies and extends the processor's datapath for tag propagation. Dynamic Information Flow Tracking (DIFT) [29] is a hardware-based approach that uses an ARM coprocessor to track and debug traces using static analysis. Hardware Assisted Data-Flow Isolation (HDFI) [30] and HyperFlow [31] are hardware-based RISC-V implementations that use a tagged mechanism and security policies for information flow control. Exploitable Buffer Overflow Detection by Information Flow Tracking (BOFT) [32] is an automated framework that integrates formal verification with IFT and leverages symbolic execution to provide explicit and implicit IFT with extensive instrumentation for taint propagation.

Mixed-mode Information Flow Tracking (MIT) [33] provides byte granularity by using taint semantics at compile time that are dependent on runtime logs, thus decoupling the tracking logic from program execution. FineDIFT [34] is a hardware-based

mechanism that generates data flow graphs of a running process with a coprocessor to provide flexibility, but the metadata storage requirements result in several limitations of software instrumentation. Kejun Chen et all summarizes the current DIFT solutions referring to the over tainting problem leading to high false positive rates [35]. These issues can be addressed by adopting parallel tag propagation schemes and customizing security policies in IFT models.

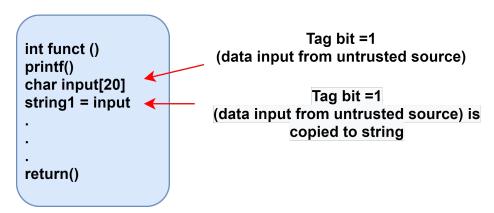

Indirect Flow Propagation System (MITOS) [36] uses an analytical algorithm for indirect flow propagation with an arbitrary number of tag types for flexibility. However, a tag-based model results in architectural overhead as the memory is modified to incorporate tag bits, or if complex lattice structures are built to secure the data. An efficient model should limit hardware design overheads and provide IFT capabilities in hardware design. In such models, the tagging mechanism assigns a tag bit to untrusted data and tracks the propagation of the data using the tag bits. For example, incoming data from an untrusted source (input) is assigned a tag bit, and the IFT module tracks the data using the tag bits value to indicate if the data is spurious or safe. All incoming data is assigned a tag bit with the value 1 indicating that it is unsafe, and 0 for trusted data. If the data is copied to string1, it is identified as an untrusted source, and the IFT module tracks the data. Figure 2.3 shows an illustration of this process.

Figure 2.3: Tag bits assigned to untrusted sources by the IFT module

## 2.4.2 Fine Grained IFT Models

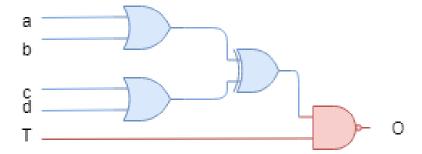

The implementation of IFT also includes fine-grained models with data labels associated only with data flow, instead of focusing on control flow transfers. A gate level IFT model is a fine-grained model associated with Boolean gates, where the information flow appears at the gate level netlist, providing better precision logic. GLIFT [37] is a shadow logic-based technique that adds logic to all the gates, resulting in design complexity and overhead. Several techniques have been implemented using data flow logic [38] as the backbone, including optimized labelling and enhanced encoding techniques [39] [40] [41], which help reduce complexity but affect the precision logic of the system. The asset based GLIFT [42] model provides structural checking with security properties.

Gate level-based leakage detection [43] detects the leaky path with parser and logic modules for formal verification but results in intense computation complexity for large designs. The multi-bit label tracking model [44] quantitatively detects the information leakage with area constraints, where the multi-bit labels are directly proportional to the number of gates in the circuit. A unified model for gate level propagation [45] generates synthesizable propagation logic to be used in EDA tools where the attribute labels at different levels of precision are addressed for faults with the flexibility to be used in different emulation platforms.

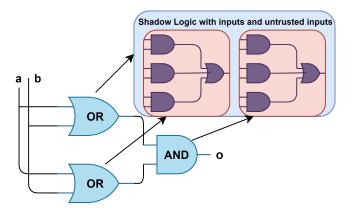

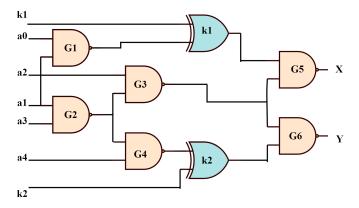

A gate level based IFT model consists of gates and shadow logic for all the gates, as shown in Figure 2.4 A separate shadow logic is implemented for each gate, (a and b are the inputs with an output o) where the shadow consists of the inputs along with untrusted inputs that affect the output. This scheme results in additional area overhead. Therefore, approaches that reduce the complexity of the gate level model and enable tracking of data critical modules, such as crypto engines and security accelerators, rather than tracking the whole module, enhance the overall system overhead.

Figure 2.4: Gate level IFT with shadow logic

## 2.5 Trusted Execution Environment

The Trusted Execution Environment is an execution environment that provides security features through isolation of software and data [46]. TEE based on ARM TrustZone technology provides a mechanism to isolate security-critical components in a system [47], while Intel SGX enclave is used in modern processors to protect privilege levels by authorized functions [48]. Other architectures used for security-critical applications include AMD Platform Secure Processor, AMD Memory Encryption Technologies, Intel Management Engine (ME), Open Portable TEE, and various Platform Security Architectures (PSA).

In the ARM TrustZone technology, the software is partitioned into two worlds to prevent software attacks, where the secure world protects critical data and the non-secure world executes the normal operating system [49]. The secure monitor call acts as a bridge between the two worlds. Once the system boots, the processor enters the secure world of the TEE, and once all privileged operations are completed, it switches back to the normal world and yields control to the bootloader [50]. Data routed to a specific world is controlled by system operational modes and device configuration. TEE provides secure trusted services, such as authentication and remote attestation, to protect application integrity. TEE-enabled authentication from a remote device can mitigate phishing attacks [51]. TrustZone architecture uses identity authentica-

tion to provide run-time authentication and data protection mechanisms to verify private data and ensure data access security using Application Program Interface (API) calls [52]. The Programmable Logic (PL) master dynamically configures data using the Application Extensible Interface (AXI) interconnect signals, and a secure authentication scheme can be achieved using the secure slave key transaction with the master [53].

## 2.6 Logic Obfuscation

Logic obfuscation is a technique that enhances the security of a design by inserting key gates to the original design, thus locking the netlist. This makes the functionality of the design hidden and only allows the correct key combination to unlock the design functionality. By inserting key gates, the locked design produces corrupted outputs if an adversary tries to access or modify the design. Figure 2.5 illustrates a modified logic locked equivalent circuit for the c17 circuit, with key gate insertion. An input sequence of 10011 with the correct key combination of K0 and K1=11 produces the corresponding outputs X and Y as 01. However, if the key combination is wrong (e.g., 00), the output of the circuit is modified, and the design becomes erroneous. Nonetheless, attacks such as the Boolean satisfiability attack can eliminate the wrong key combinations using the distinguished inputs, effectively breaking the logic-locking techniques.

Figure 2.5: Logic-locked circuit with two new key gates added in C17 circuit

To prevent such attacks, SAT resilient techniques such as SARLock and TT-Lock make the attack iterations grow exponentially with increasing key size [54][55], whereas Anti-SAT provides tuning flexibility for the key gate configurations [56]. Furthermore, schemes such as SFLL remove a functional logic block and restore the original logic using Hamming distance [57], while fault-based logic encryption leverages EDA tools to insert key gates with fault impact metrics [58]. These techniques are useful for intellectual property protection and can also be extended to applications of secure boot.

## 2.7 Security Models

Most of the traditional architectures have limited capability to implement security features necessary to secure devices from different types of attacks. The main reason for this is the lack of flexibility as the developers of proprietary architectures do not offer security enhancements due to the associated performance tradeoffs. RISC-V architecture, on the other hand, provides this flexibility to customize the design of a system with reconfigurability and system security. The following section describes the security models, features and vulnerabilities in the existing traditional architectures and provides a RISC-V compatible countermeasures by taking into consideration the possible threats in the SoC design and Architecture Platform.

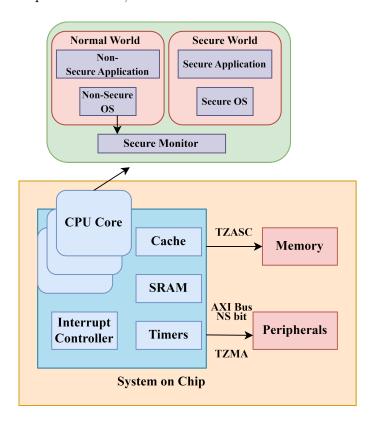

#### 2.7.1 ARM Trustzone

The hardware-assisted TrustZone feature in the ARM-centric processing system provides a secure implementation, while the FPGA fabric holds the programmable logic and uses the AXI bus to communicate with the processing system. The intellectual property cores are partitioned into secure and non-secure worlds, providing isolation. The ARM TrustZone includes the TrustZone Memory Adapter (TZMA) and TrustZone Address Space Controller (TZASC), which establish partitions between memory and peripheral units for both worlds. However, modern designs with large

stacks of libraries and optimized functions are vulnerable to cache-based side-channel attacks. Key extraction from secure crypto engines is possible by compromising the non-secure world Operating System (OS) or by tracking power or Electro Magnetic Field (EMF) signals during key exchanges [59]. The ARM TrustZone is susceptible to hardware attacks such as malicious modification of secure IP, denial of service, resource denial, and port attacks [60]. While configuring the NS bit along the AXI bus is simple and effective, managing the structure in a multi-core environment is challenging. Incorporating additional security enforcements for optional memory controllers outside the Cortex-M TrustZone Architecture is necessary. Figure 2.6 illustrates the ARM TrustZone implementation, which includes various units and cores.

Figure 2.6: ARM TrustZone implementation

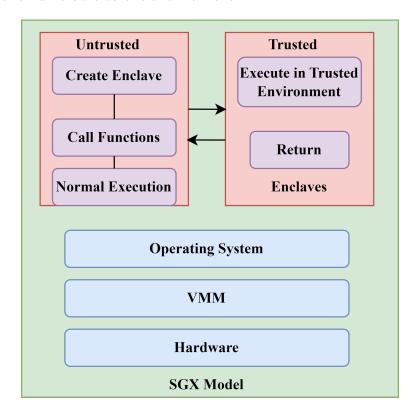

#### 2.7.2 Intel SGX

Intel SGX allows for the protection of application address mappings and provides enclave memory access semantics [61]. The enclaves are secure regions of memory that are protected from any access or modification. These enclaves are encrypted and decrypted on the fly, providing hardware-isolated trusted environments. Figure 2.7 shows the basic operation performed in the SGX model. In this model, an untrusted application invokes a trusted function inside the enclave, which cannot be accessed by any other application. This model achieves confidentiality of the code with isolation and protects against integrity violations from software attacks. The Processor Reserved Memory (PRM) holds the enclave page cache and is protected from any non-enclave memory accesses. However, the downside of this model is that the enclave gains full access to the entire address space of the untrusted application, which makes it vulnerable to enclave malware.

Figure 2.7: SGX Model

Furthermore, the enclave is vulnerable to cache based side-channel attacks, and software based side-channel attacks have been targeted on co-located SGX enclaves to extract Rivest Shamir Adleman (RSA) private keys [62]. Although most modern

Intel processors feature Hyperthreading, SGX does not prevent it, allowing malicious software to execute system threads. Additionally, the Intel-specific architectural and microarchitectural model with SGX's security features is not publicly available, which limits the ability to develop a trust model by customizing TEEs without proprietary rights. Bridging the support for more than one hardware-enforced isolated domain is not possible with the traditional architectures.

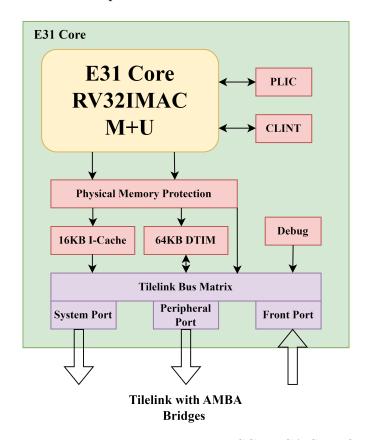

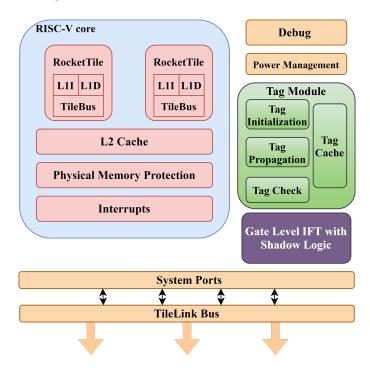

### 2.7.3 RISC-V

RISC-V is an open-source architecture that provides a highly flexible and customizable platform for implementing different levels of security in a system. Unlike SoC with 3PIP proprietary architecture, RISC-V's extensible ISA with minimal instruction set allows for the implementation of a customized processor that can support several security applications. For instance, the Common Evaluation Platform (CEF) can be used to identify the security properties of a RISC-V system [63]. The RISC-V security committee has proposed an abstraction-augmented aISA that extends a bridge between hardware and software beyond the traditional ISA for control [64]. RISC-V Multizone Security by Hex Five provides a hardware-enforced software defined separation with multiple TEEs [65]. With the benefits of RISC-V being open-source, especially in the security context, different modules can be implemented to secure the system from different kinds of attacks [66]. The physical memory protection provided by this architecture is used for authenticating the execution of trusted nodes. Integration of hardware cryptographic accelerators, key management, and security extensions are made simple using available open-source frameworks. Multi-threaded enclaves with memory-mapped resource protection are achieved by different RISC-V security implementations modules.

Additionally, RISC-V supports various extensions like Multiplication(M), Atomic (A), Single precision (F) and Double precision (D) floating point, which are collected into (G) extension that provides a general-purpose scalar instruction set. As RISC-V

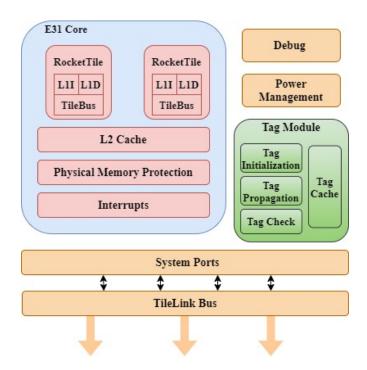

based systems continue to grow rapidly and new security vulnerabilities emerge, it is important to add some security features to RISC-V processors. Figure 2.8 illustrates the block diagram of Freedom E31 core with RISC-V ISA Specification, which supports 32, 64, and 128-bits instruction widths and four different instruction formats: R-type, I-type, S-type, and U-type. The processor is written in Chisel HDL (based on Scala language). The flexibility of the RISC-V architecture also supports RISC-V extensions to support the IFT model, which provides a strong timing sensitive security behavior that is otherwise not possible with traditional ISAs.

Figure 2.8: Freedom E31 core with RISC-V ISA Specification

Some of the existing information flow tracking models on RISC-V are tag based bare metal and PULPino based model to protect the system from memory attacks [67]. Liu et al [68] enforced a hardware extension of RISC-V SoC with static analysis to generate control flow graphs. Samuel et al [69] present an augmented tag isolation mechanism

to improve the dynamic reuse of untrusted memory across security boundaries by sharing execution stacks with real-time constraints. Isadora [70] framework uses a minimal testbench to run an automated trace generator for information tracking limiting access to the full RISC-V toolchain. Table 2.7.3 provides RISC-V compatible countermeasures by taking into consideration the possible threats in the Trusted Execution Environment, and the SOC design and Architecture Platform.

Table 2.1: RISC-V compatible countermeasures

| Threat Models                | RISC-V compatible countermeasure models             |  |  |  |  |

|------------------------------|-----------------------------------------------------|--|--|--|--|

| Cache-Timing Attacks         | Transparent Hardware-Protection Layers with         |  |  |  |  |

|                              | memory access leakage protection [71][85]           |  |  |  |  |

| Side-Channel Attacks         | Core hardened resilient models with hardware        |  |  |  |  |

|                              | Accelerators and virtual TEEs [71]                  |  |  |  |  |

| Denial of Service and Memory | Information flow tracking models tracking the flow  |  |  |  |  |

| Attacks                      | of the data to protect memory corruption and        |  |  |  |  |

|                              | mitigate DoS attacks by attestation models [86][87] |  |  |  |  |

| Malware Insertion            | Secure boot for SoCs along with data tracking       |  |  |  |  |

|                              | models [71]                                         |  |  |  |  |

| Supply Chain Attacks         | Logic Obfuscation with SAT attack resilient model   |  |  |  |  |

|                              | for the SoC platform[71][102]                       |  |  |  |  |

# CHAPTER 3: SECURITY-AWARE DESIGN FLOW FOR BITSTREAM SECURITY

### 3.1 Introduction

Reconfigurable devices offer flexibility in dynamic reconfiguration features, but they are susceptible to bitstream modifications that can compromise the security of the device. An attacker can tamper with or insert hardware trojans into the bitstream during boot time or runtime if they have physical access to the configuration bitstream. To protect the bitstream during boot time, a secure boot with authentication can be implemented, which provides a root of trust. However, this can be bypassed by tampering with the device boot process using the Processor Configuration Access Port (PCAP) or Internal Configuration Access Port (ICAP) ports. Existing solutions like PUF modules [15] [16] [72], over-the-air updates, and TPM-based key management systems provide bitstream protection and authentication, but they may not be enough to prevent malicious modifications in configuration files [73][74].

Though these models provide bitstream security during boot time the PL can be replaced to perform different operations by replacing it with malicious bitstreams. To protect the application bitstream during runtime, various designs for trust techniques have been developed [75][76][77]. For instance, logic locking schemes are used to secure gate level IPs from bitstream reverse engineering, while ARM TrustZone provides isolation to secure critical applications by enforcing secure transactions during device authentication. This chapter presents the threat model for boot process and run time security and proposes a multi-layered security framework to mitigate malicious code modification during boot-up and runtime.

# 3.2 Threat model for Boot Process and Runtime Security of a Reconfigurable Device in the Field

Considering a reconfigurable device in the field in a client-server model that communicates with the server with critical data transactions. Authorized access control must be provided for secure communication between the client and the server module. Thus, the section represents the threat model during boot-up process and the runtime vulnerabilities.

### 3.2.1 Boot-Time bitstream modification

An adversary can redirect the normal execution flow of code to an unauthorized piece of code by hijacking the boot process. The Processing System (PS) controls the PL bitstream during boot up where modifications to the bitstream can be made via field configuration or other communication ports. Hardware trojans present in the system can be triggered to replace the PL logic to perform different tasks. In bitstream spoofing with relay and replay attacks, an adversary acts as an authenticated client to replace the original bitstream with a malicious one. Unauthorized memory access through hardware cores leaks critical data which can break the boot process on FPGA SoCs [78]. Authentication keys stored in the memory can be easily accessed through malicious hardware cores leading to system compromise by modifying the boot loader.

#### 3.2.2 Runtime attacks

At runtime once the bitstream has been loaded an attacker may target dynamic reconfigurable partitions or may want to target certain portions of the configuration. Bitstreams must be encrypted to prevent IP theft and cloning and authenticated to eliminate tampering and trojan insertion. Extraction of the bitstream encryption keys leads to several runtime attacks such as:

• Side-channel bitstream key extraction: Extraction of the keys through different communication channels.

- Architectural model attacks: Hardware cores targeting the configuration files to bypass authentication.

- Bitstream Tampering: Manipulation of critical functions and targeting prconfiguration files to modify the bitstream.

# 3.3 Secure Design Flow

This work focuses on bitstream security to mitigate malicious code modification during the boot-up process and runtime. It provides a multi featured secure design where when the device powers on, a secure boot authentication is done using the PUF mechanism which generates a unique challenge-response pair in a client-server environment. Once the authentication is done a logic-locked mechanism based bitstream obfuscation is done to the application bitstream and programmed in the PL which provides secure IP isolation using the ARM TrustZone configurations. In addition, to eliminate tampering attacks, the key to unlock the logic-locked bitstream is securely stored in the TPM and through secure communication, it is used to unlock the bitstream.

#### 3.3.1 Secure Boot Mechanism

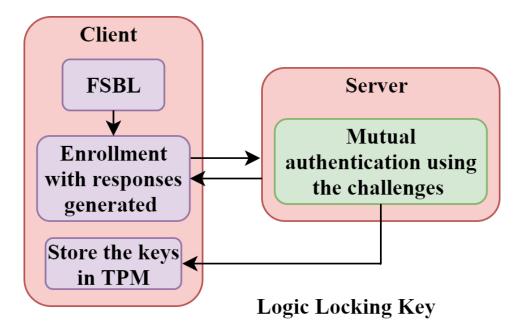

During the boot process, the initial stage provides authentication for the bitstream with a unique key response generated by the PUF, followed by applying a logic-locking mechanism to the application logic. The PUF generates the per-device unique responses using input challenges, and during the enrollment phase, the verifier and the prover generate challenge-response pairs which are encrypted using AES core to prevent unauthorized access.

The client enrolls with the server in a trusted environment to receive the authentication bitstream, which is loaded during the boot process. The Hardware Embedded Delay PUF (HELPPUF) [79], which is based on path delay variation, generates the challenge-response pairs for authentication. The server sends the input challenges to

the client, and the responses gathered in the server produce a unique key for authentication. The first stage bootloader loads the authentication bitstream on the PL fabric, and the PUF generates a response using the unique challenge and response pairs provided by the TPM.

In the reconstruction phase, authentication is done using the unique per-device key, and the PUF response is processed to generate a secret key for decrypting the encrypted application bitstream. The First Stage Boot Loader (FSBL) overwrites the authentication bitstream with the application bitstream, establishing secure communication between a client-server model. Custom device drivers are used to enable communication with TPM during the secure boot process to provide secure extensions for key storage [15], and TPM securely stores the keys generated during runtime to mitigate malicious intrusion. The overall key exchange mechanism for authentication is depicted in Figure 3.1.

Figure 3.1: Secure boot authentication and key exchange process

# 3.3.2 Obfuscation Framework

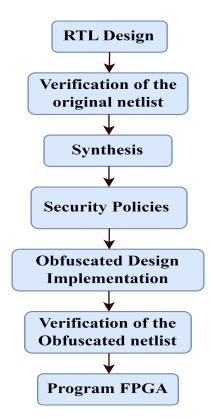

The secure boot flow is integrated with a logic-locking automation framework, allowing key gates to be inserted at either the Register Transfer Level (RTL) or netlist level. To safeguard gate level IP, the key gates are inserted into the gate-level netlist using the insertion scheme illustrated in Figure 3.2. The flow is generated and implemented with Synopsys tools and Vivado via the automated framework, which ensures IP reuse security by integrating key gates into the design process. Utilizing solely the RTL code increases the vulnerability of the design to reverse engineering by potential adversaries. The framework is designed to switch the implementation method based on the input file type, with the ABC tool [80] being used to convert input files to Verilog. The generated test bench utilizes the input Hardware Description Language (HDL) to produce a set of vectors to verify the design.

During synthesis, the Synopsys tool transforms the RTL into a gate-level netlist. Two encryption-based logic locking schemes, SARLock and fault-based encryption, are included in the experiment to enhance resistance against SAT attacks. SARLock exponentially increases the key size to generate computational complexity, guaranteeing that a single key produces a fault for any input pattern. Fault-based encryption integrates a fault impact metric [81] to determine the highest fault impact and maximize the effectiveness of each gate inserted in the design. The key produced by logic locking is stored on the server, and any attempts to tamper with the bitstream result in a corrupted or incorrect output, rendering it impossible to clone the IP. During runtime, without the correct key provided from the server, the original application's functionality remains unknown and challenging to break. After successful device authentication, the correct key is sent from the server and stored in the device TPM.

Figure 3.2: Key Gate Insertion Framework

## 3.3.3 Secure IP Using ARM TrustZone

The ARM TrustZone configuration provides accessibility of MIO ports through the secure world. Key storage for the TPM is integrated with the FPGA via the SPI interface and the TPM driver library. To establish secure communication at the FSBL for secure boot, transfer functions are implemented. Using AXI interconnects, PS configures registers to design a secure IP in the PL, with the AXI interconnect providing the IP security status parameter. After secure boot authentication, the ARM TrustZone loads the logic-locked bitstream on the secure IP of the PL. If an unauthorized master attempts to access the secure IP, the secure IP raises an error signal, with NS bits on the AXI bus indicating the security transaction status.

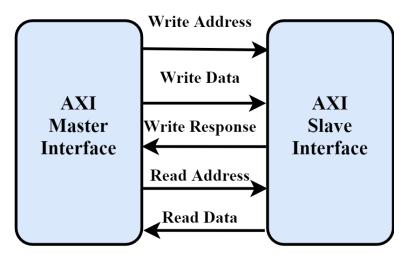

The AXI bus comprises five communication signals, as depicted in Figure 3.3, to establish communication between a master and a slave. ARPROT and AWPROT signals are used to determine whether read/write access is granted to secure and non-

secure IPs. Depending on the NS bits, the slave checks for security violations, and transactions are completed with read or write signals. To monitor the master-slave interface's AXI-transactions, a core wrapper is implemented. The wrapper ensures that only authorized transactions are permitted, and any configuration modification raises an exception. Secure transactions take place in the secure IP of the PL using ARM TrustZone. After device authentication, the key to unlock the bitstream stored in the TPM is securely sent to the secure IP.

Figure 3.3: AXI communication signals

## 3.4 Implementation and Experimental Results

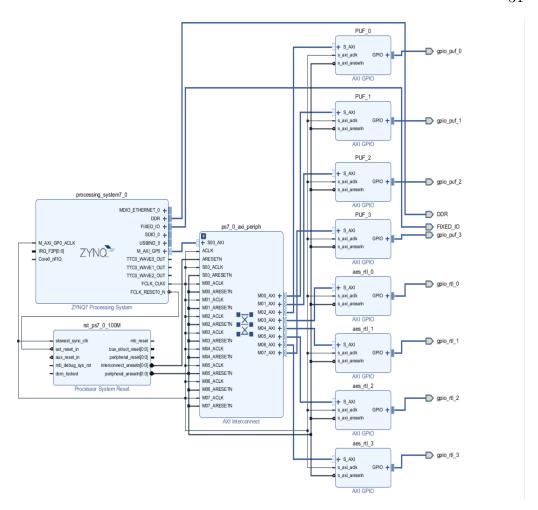

The hardware setup for the proposed framework on the Xilinx Zedboard FPGA, equipped with Zynq-7000 XC7Z020-CLG484, incorporates the ARM Cortex A9 processor and TPM SLB9670 module, as shown in Figure 3.4. To generate unique key pairs, the HELPPUF component is integrated into the existing hardware functions [79], and the device-unique encryption key is generated by the PUF. This 128-bit encryption key is then utilized by the AES cryptographic core for bitstream encryption and validation. The system block with PUF IP and AES IP are added as secure slave registers with a custom configured system wrapper, and each General-Purpose Input Output (GPIO) port is 32-bit wide. Once device authentication is completed,

the authentication bitstream is programmed into the PL and verified with the PUF generated keys before the logic-locked application bitstream is sent from the server to the device.

Figure 3.4: Hardware setup

The obfuscated automated framework with SARLock and Fault-based encryption is tested using circuits from benchmarks including the ISCAS-85/89 suite [82]. For fault-based encryption, the circuits are analyzed using the ABC tool [80] to generate bench and Verilog files, and the fault impact is calculated using the stuck-at fault analysis. By using the fault impact provided [83] in which using the stuck-at fault analysis the Fault impact = (#test patterns detecting sa0) x (#output bits affected by sa0) x (#test patterns detecting sa1) x (#output bits affected by sa1) is calculated. Key gates are inserted for the highest calculated fault impact, which protects the IP from reverse engineering. This design offers flexibility to control corrupt outputs and maximize design complexity for the attacker by targeting 50% Hamming distance with a smaller number of key gates, significantly reducing the area overhead. Figure 3.5 shows the system block with PUF IP and AES IP added as secure slave registers with a custom configured system wrapper.

Figure 3.5: System block with secure IPs

Table 3.1 shows the fault impact summary for the ISCAS- 85/89 benchmarks with different sets of test patterns. This shows the fault coverage along with the faults detected at different gates to compute the fault impact for logic encryption. Based on the fault impact factor Table 3.2 shows the average Hamming distance calculated for the benchmarks with a range of key sizes between correct and incorrect outputs to obtain a 50% Hamming distance with a smaller number of keys to preserve the complexity of the locked design. Figure 3.6 shows the Hamming distance between the outputs of designs on applying the correct key and a random wrong key. The whole framework is automated along with functional verification for the generated netlist using input test vectors. The key generated during logic obfuscation is stored on the

server and upon mutual authentication, it is sent to the secure IP and stored on the TPM. The secure IP and AXI interconnect implemented by using the TEE is used to eliminate non-secure transactions and other AXI attacks. By using an isolation design flow, the isolated secure IP block will have separate resources and ports for transactions.

Table 3.1: Fault impact summary for the ISCAS- 85/89 benchmarks