# DISSERTATION - LEVERAGING LLVM IR FOR DESIGN SPACE EXPLORATION AND MODELING OF APPLICATION AND DOMAIN-SPECIFIC HARDWARE

by

# Samuel Rogers

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2022

| App     | proved by:     |

|---------|----------------|

| Dr.     | Hamed Tabkhi   |

| Dr.     | Arun Ravindran |

| <br>Dr. | Andrew Willis  |

| <br>Dr. | Tsing-Hua Her  |

©2022 Samuel Rogers ALL RIGHTS RESERVED

#### Abstract

SAMUEL ROGERS. Dissertation - Leveraging LLVM IR for Design Space Exploration and Modeling of Application and Domain-Specific Hardware. (Under the direction of DR. HAMED TABKHI)

The limitations of transistor scaling and the rise of power-constrained compute environments have driven a new renaissance in hardware design through hardware acceleration. Application and domain-specific hardware accelerators offer fantastic efficiencies over traditional, general-purpose processors and are seeing extensive use in applications ranging from embedded platforms to high-performance cloud computing clusters.

Developing new hardware accelerators comes at a great cost in terms of both time and engineering effort. It is greatly outpaced by rapidly evolving algorithmic developments, particularly in emergent domains like AI and deep learning. Hardware developers need new, more agile tools to aid in both simulation and integration of hardware accelerators in modern systems.

To aid in the integration and optimization of application-specific memories for hardware accelerators this work presents two automated solutions based on the Low Level Virtual Machine (LLVM) compiler infrastructure. These solutions explore static data access characteristics of applications to guide hardware designers in optimizing memory hierarchy prior to hardware synthesis. They are also compatible with existing synthesis tool-chains to enable some automated memory optimizations when synthesizing accelerator designs.

This work also introduces a new design space exploration tool for application and domain-specific accelerators in the form of the gem5-SALAM simulator. This simulator provides high fidelity modeling of accelerator power and performance within a full system simulation. It also significantly reduces the amount of time and effort needed to explore the system design space for accelerators versus traditional hardware design flows.

Lastly the work presented as part of gem5-SALAM's revision introduces a new set of simulation abstractions for redefining how simulation models are written for event-driven simulators. These abstractions address the fundamental design challenge of decoupling simulated functionality from timing and concurrency constraints, while maintaining full compatibility and interoperability with

the popular open-source simulation framework gem 5.  $\,$

#### ACKNOWLEDGEMENTS

I would like to acknowledge and thank my advisor and mentor Dr. Hamed Tabkhi for the support he has given me in my research. Not only has he provided guidance and insight within the fields of computer architecture and academic research, he has also provided valuable guidance and mentoring that has helped me better balance my work and home life.

I would also like to thank the members of the TeCSAR lab for their support in my research. In particular I would like to acknowledge Arnab Purkayastha and Suhas Shiddhibhavi, with whom I developed the OpenCL analysis research. Their expertise and work on the OpenCL synthesis to FPGA component of the research enabled me to focus my efforts on algorithmic analysis.

I would also like to acknowledge and thank Joshua Slycord for his efforts in datapath modeling in the gem5-SALAM project. With his work we have been able to develop a truly amazing tool and publish it in a highly esteemed journal and conference. My thanks also go out to the newest member of the SALAM team, Zephaniah Spencer, with whom I look forward to continue working.

I would also like to thank Dr. Arrvindh Shriraman and his students at Simon Fraiser University for their collaboration and guidance for gem5-SALAM's development. Insights from their hardware research and usage of gem5-SALAM in classroom instruction helped to identify necessary improvements for gem5-SALAM.

Sincere thanks go out to my doctoral committee, Dr. Andrew Willis and Dr. Arun Ranvindran for their help and guidance both in and out of the classroom. I greatly value and appreciate the time you have taken to help me in my PhD. work, and in the guidance for post-graduate life. My thanks also goes out to Dr. Tsing-Hua Her for her participation in my doctoral committee as the external graduate faculty member.

Finally, I would like to acknowledge and thank my loving wife, Jenna Rogers, for her constant support throughout every part of life both in and out of school.

# TABLE OF CONTENTS

| ES                                                  | viii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RES                                                 | ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EVIATIONS                                           | xiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NTRODUCTION                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| are Design Tools and Design Space Exploration       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| outions                                             | Ş                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Outline                                             | <u>4</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ACKGROUND AND RELATED WORK                          | Ę                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| w-Level Virtual Machine (LLVM) Tool Chain           | Ę                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| and Exploration of Hardware Accelerators            | Ę                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| y Optimization Challenges for Hardware Accelerators | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| L Synthesis and Memory Optimization on FPGAs        | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LOCALITY AWARE MEMORY ASSIGNMENT AND                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Memory Access Analysis                              | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pointer Identification                              | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pointer Behavior Analysis                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Memory Access Pattern (MAP) File                    | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| e-Level Memory Assignment                           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Locality Measurement                                | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Memory Assignment                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| tion                                                | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Performance and Power Comparison                    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                     | EVIATIONS  STRODUCTION  The Design Tools and Design Space Exploration  Dutions  Outline  ACKGROUND AND RELATED WORK  We-Level Virtual Machine (LLVM) Tool Chain  and Exploration of Hardware Accelerators  The Optimization Challenges for Hardware Accelerators  L Synthesis and Memory Optimization on FPGAs  COCALITY AWARE MEMORY ASSIGNMENT AND  Memory Access Analysis  Pointer Identification  Pointer Behavior Analysis  Memory Access Pattern (MAP) File  The Optimization Pointer Memory Assignment  Locality Measurement  Memory Assignment  Lion |

|       |            |                                                        | vii |

|-------|------------|--------------------------------------------------------|-----|

|       | 3.3.2.     | Memory Allocation                                      | 23  |

|       | 3.3.3.     | Algorithm Effects on Optimal Memory Allocation         | 24  |

|       |            | VM-BASED MEMORY DECOUPLING FOR OPENCL<br>TION ON FPGAS | 26  |

| 4.1.  | . The FP   | GA Memory Wall and Optimization                        | 26  |

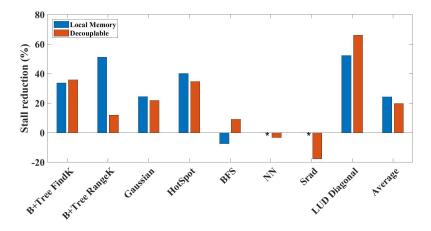

| 4.2.  | . Automa   | ted LLVM-Based Memory Decoupling                       | 29  |

|       | 4.2.1.     | Algorithmic Implementation                             | 31  |

| 4.3   | . Evaluati | ion                                                    | 32  |

|       | 4.3.1.     | Performance Evaluation                                 | 33  |

|       | 4.3.2.     | Resource Utilization Overheads                         | 36  |

|       | 4.3.3.     | Power Efficiency                                       | 36  |

| СНАРТ | ER 5: GI   | EM5-SALAM                                              | 39  |

| 5.1.  | . SALAM    | Infrastructure                                         | 40  |

|       | 5.1.1.     | Static Graph Elaboration                               | 40  |

|       | 5.1.2.     | Dynamic LLVM Runtime Engine                            | 42  |

|       | 5.1.3.     | Metrics Estimation                                     | 43  |

|       | 5.1.4.     | gem5 Integration and Scalable Full System Simulation   | 45  |

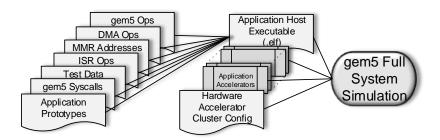

|       | 5.1.5.     | Simulation Setup and Configuration                     | 49  |

| 5.2.  | . Simulati | ion Results and Validation                             | 51  |

|       | 5.2.1.     | Metrics Validation                                     | 51  |

|       | 5.2.2.     | System Validation on FPGAs                             | 53  |

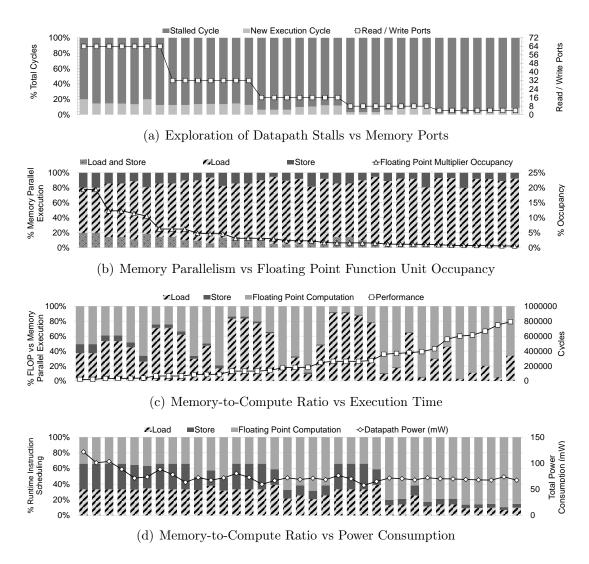

|       | 5.2.3.     | Design Space Exploration                               | 54  |

|       | 5.2.4.     | Multi Accelerator Design Space Exploration             | 57  |

|           |            |                                                            | viii |

|-----------|------------|------------------------------------------------------------|------|

|           |            | PANDING SIMULATION DESIGN ABSTRACTIONS<br>5-SALAMv2        | 60   |

| 6.1.      | Abstract   | ting Timing and Concurrency in Simulation                  | 62   |

|           | 6.1.1.     | Event-driven simulation and gem5's timing model            | 62   |

|           | 6.1.2.     | Modeling Hardware Timing and Concurrency in gem5-<br>SALAM | 64   |

| 6.2.      | gem5-SA    | ALAMv2 Specification                                       | 70   |

|           | 6.2.1.     | System Setup and Initialization                            | 70   |

|           | 6.2.2.     | LLVM Runtime Engine                                        | 79   |

|           | 6.2.3.     | gem5 Integration and Scalable Full System Simulation       | 81   |

| 6.3.      | Simulation | on Results and Metrics Validation                          | 85   |

|           | 6.3.1.     | Timing, Power, and Area Validation                         | 85   |

|           | 6.3.2.     | FPGA System Validation                                     | 87   |

|           | 6.3.3.     | Simulation Timing Comparison                               | 88   |

| 6.4.      | Design S   | Space Exploration                                          | 89   |

|           | 6.4.1.     | Case Study: LeNet-5                                        | 89   |

|           | 6.4.2.     | MobileNetV2 Exploration                                    | 95   |

| СНАРТ     | ER 7: CC   | ONCLUSION                                                  | 100  |

| Bibliogra | aphy       |                                                            | 104  |

|                                                                                                                                     | ix |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| LIST OF TABLES                                                                                                                      |    |

| TABLE 2.1: Aladdin Datapath vs Data-dependent Execution                                                                             | 7  |

| TABLE 2.2: Aladdin datapath vs. memory design                                                                                       | 8  |

| TABLE 4.1: System characteristics used for study.                                                                                   | 33 |

| TABLE 4.2: Kernel global variable data information per application                                                                  | 33 |

| TABLE 4.3: Baseline profiling information for each application                                                                      | 33 |

| TABLE 5.1: System validation results                                                                                                | 51 |

| TABLE 6.1: Comparison of some of the shortcomings present gem5-SALAMv1 and how we have improved upon those aspects in gem5-SALAMv2. | 61 |

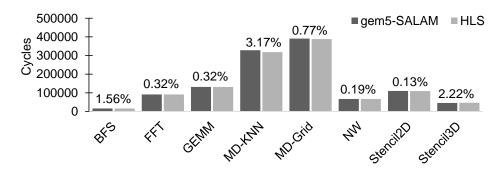

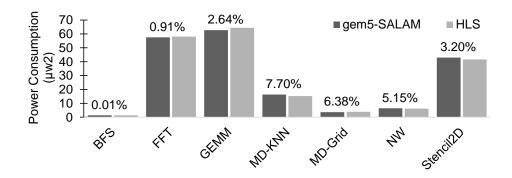

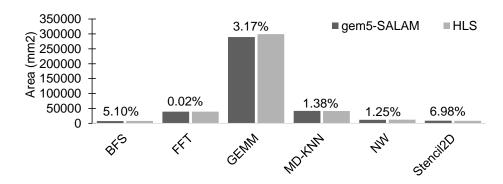

| TABLE 6.2: gem5-SALAM vs HLS power, area, and performance comparison.                                                               | 85 |

| TABLE 6.3: gem5-SALAM vs HLS power, area, and performance error percentages.                                                        | 86 |

| TABLE 6.4: FPGA vs gem5-SALAM system validation comparison.                                                                         | 87 |

| TABLE 6.5: FPGA vs gem5-SALAM system validation comparison results.                                                                 | 87 |

| TABLE 6.6: gem5-SALAM simulation timing values and comparison.                                                                      | 88 |

| TABLE 6.7: MobileNetV2 96x96 Sim time and latency                                                                                   | 98 |

| TABLE 6.8: "MobileNetV2 Network Complexity for 96x96 Input"                                                                         | 98 |

| TABLE 6.9: Runtime Comparison of MobileNetV2 on SALAMv1 and SALAMv2                                                                 | 99 |

## LIST OF FIGURES

| FIGURE 2.1: MD-KNN Exploration                                                          | 12 |

|-----------------------------------------------------------------------------------------|----|

| FIGURE 3.1: Memory Allocation Tool Chain                                                | 15 |

| FIGURE 3.2: Pointer Identification (Stage 1)                                            | 16 |

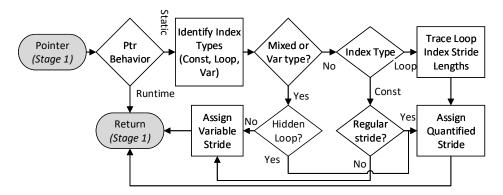

| FIGURE 3.3: Pointer Behavioral Analysis (Stage 2)                                       | 17 |

| FIGURE 3.4: Stride Measurement (Stage 3)                                                | 17 |

| FIGURE 3.5: Memory Access Pattern-file $(MAP\text{-}file)$                              | 18 |

| FIGURE 3.6: Memory Allocation Graph                                                     | 20 |

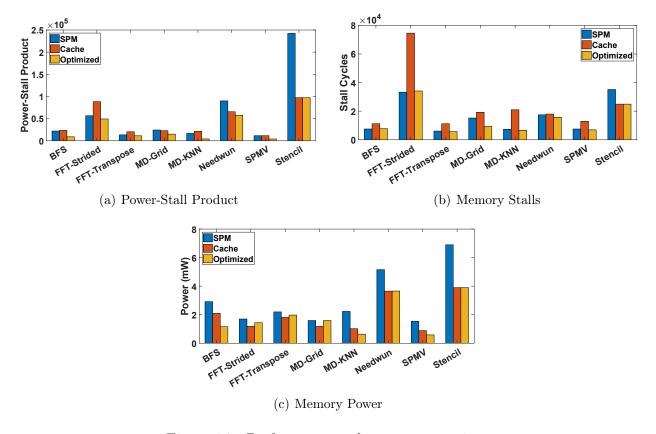

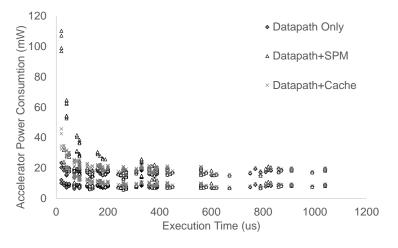

| FIGURE 3.7: Performance and power comparison                                            | 22 |

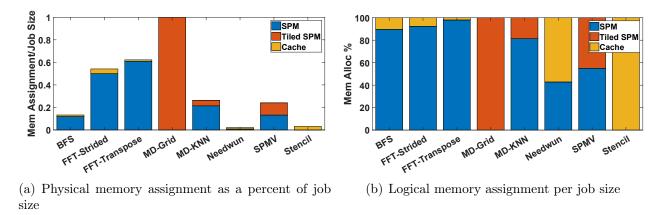

| ${\bf FIGURE~3.8: Memory~type~distribution~for~optimized~memory~assignment}$            | 24 |

| FIGURE 3.9: Memory Access Graphs for Alternate MD Realizations                          | 25 |

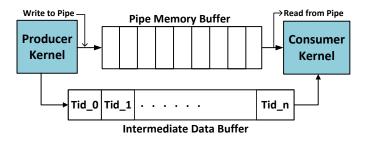

| FIGURE 4.1: OpenCL Pipe semantic                                                        | 27 |

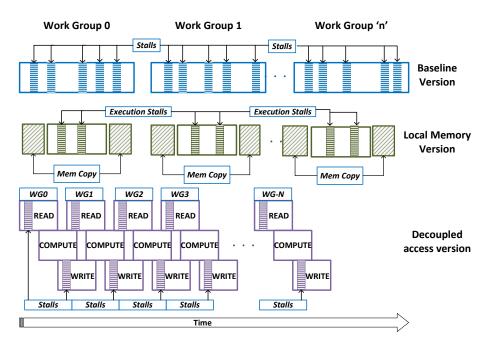

| FIGURE 4.2: Execution pattern comparison                                                | 28 |

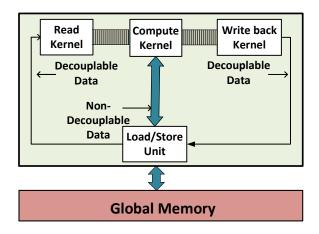

| FIGURE 4.3: Memory decoupling with pipes                                                | 29 |

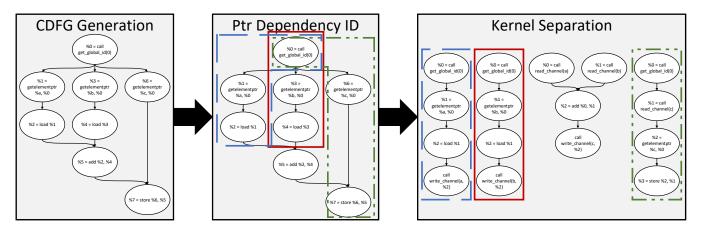

| FIGURE 4.4: Automated Kernel Memory Access Decomposition                                | 31 |

| FIGURE 4.5: Conceptual realization of the decoupled access incorporated into OpenCL HLS | 32 |

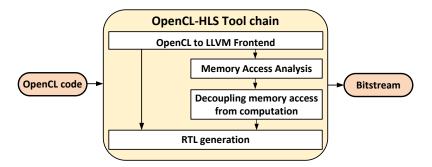

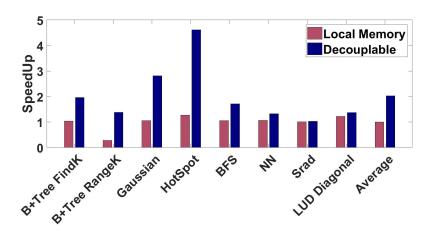

| FIGURE 4.6: Performance improvement over the baseline                                   | 34 |

| FIGURE 4.7: Memory stalls reduction over the baseline                                   | 35 |

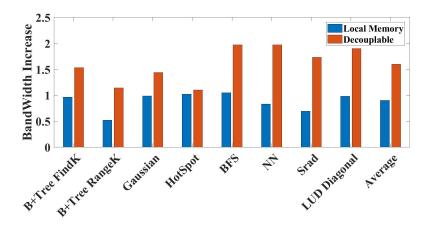

| FIGURE 4.8: Memory bandwidth improvement over the baseline                              | 35 |

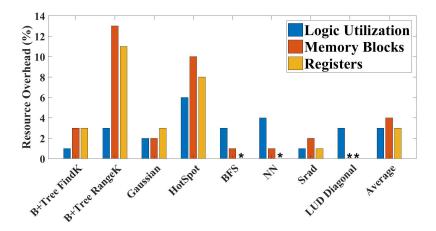

| FIGURE 4.9: Decoupling resource utilization overhead over the baseline                  | 36 |

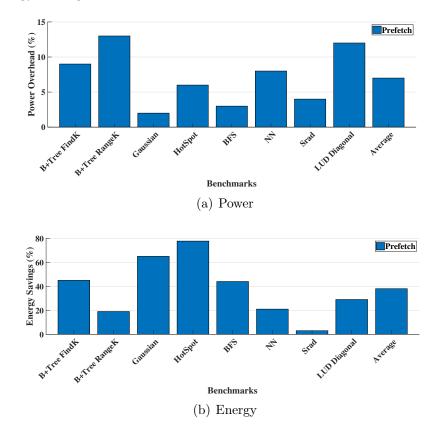

| FIGURE 4.10: Power overhead and energy saving over the baseline                         | 37 |

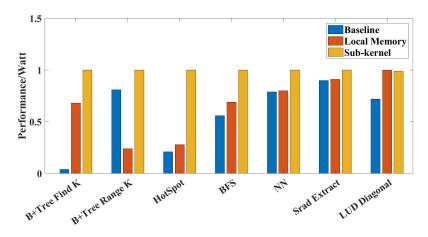

| FIGURE 4.11: Normalized Performance/Watt                                                | 38 |

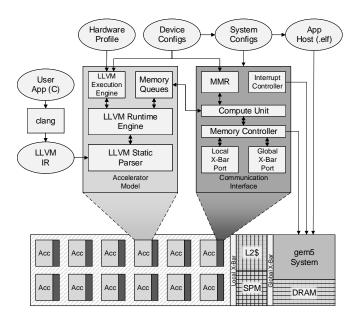

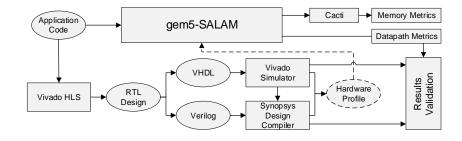

| FIGURE 5.1: gem5-SALAM Full-System Architecture                                         | 39 |

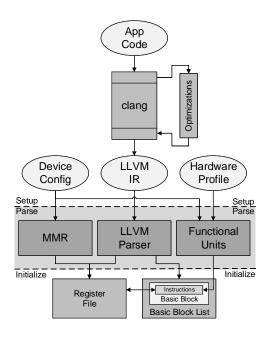

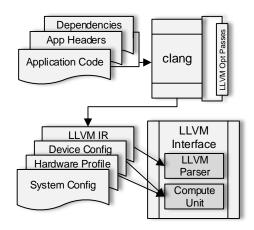

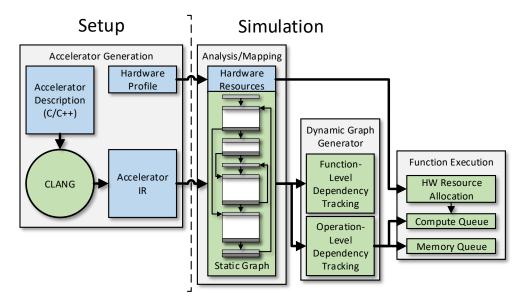

| FIGURE 5.2: Accelerator Model Generation                                                | 41 |

|                                                                                                                                                                                                                                                                                    | xi |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

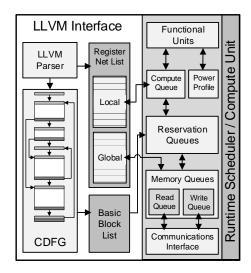

| FIGURE 5.3: LLVM Runtime Engine Simulation Model                                                                                                                                                                                                                                   | 43 |

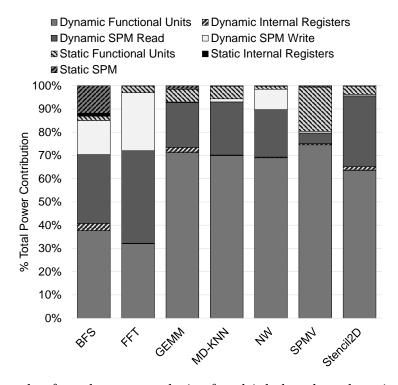

| FIGURE 5.4: Example of total power analysis of multiple benchmarks using private SPM.                                                                                                                                                                                              | 44 |

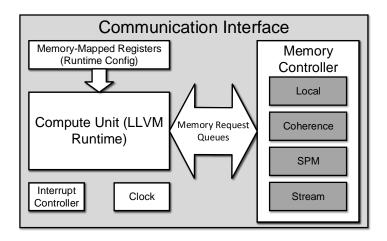

| FIGURE 5.5: Communications Interface                                                                                                                                                                                                                                               | 46 |

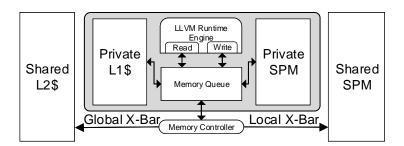

| FIGURE 5.6: Accelerator Memory Model                                                                                                                                                                                                                                               | 47 |

| FIGURE 5.7: Single Accelerator Configuration                                                                                                                                                                                                                                       | 50 |

| FIGURE 5.8: Accelerator Cluster Configuration                                                                                                                                                                                                                                      | 50 |

| FIGURE 5.9: Validation Flow                                                                                                                                                                                                                                                        | 52 |

| FIGURE 5.10: Performance Validation                                                                                                                                                                                                                                                | 52 |

| FIGURE 5.11: Power Validation                                                                                                                                                                                                                                                      | 53 |

| FIGURE 5.12: Area Validation                                                                                                                                                                                                                                                       | 53 |

| FIGURE 5.13: GEMM Design Space Pareto Curve                                                                                                                                                                                                                                        | 54 |

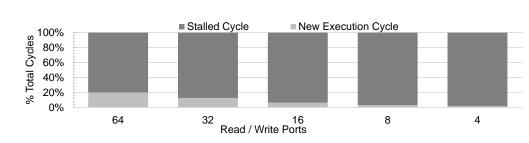

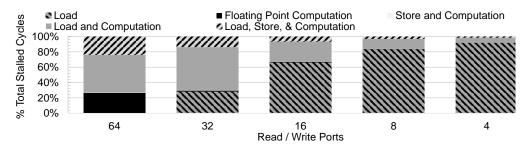

| FIGURE 5.14: GEMM Stalls Breakdown                                                                                                                                                                                                                                                 | 56 |

| FIGURE 5.15: GEMM Memory and Compute Design Space Exploration                                                                                                                                                                                                                      | 57 |

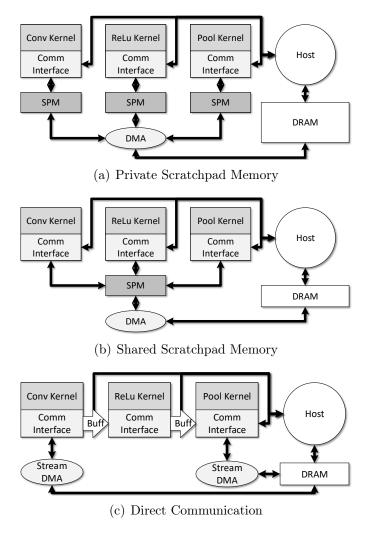

| FIGURE 5.16: Producer-Consumer Accelerator Scenarios                                                                                                                                                                                                                               | 58 |

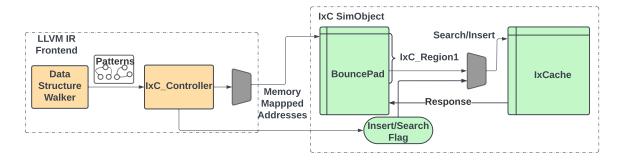

| FIGURE 6.1: Index Cache Implementation                                                                                                                                                                                                                                             | 69 |

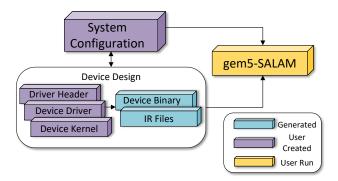

| FIGURE 6.2: Overview of the gem5-SALAMv1 user design methodology. There was significant effort and knowledge of gem5 specific programming semantics required in comparison to gem5-SALAMv2 from the user.                                                                          | 71 |

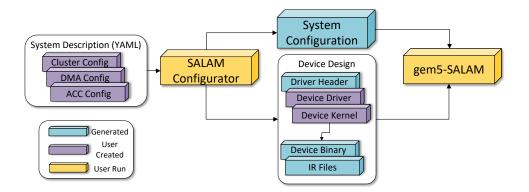

| FIGURE 6.3: Overview of the gem5-SALAMv2 device configuration. By automating the system and header configuration we have removed the need for experience in programming gem5 and dramatically simplified the design process while simultaneously allowing far more complex models. | 72 |

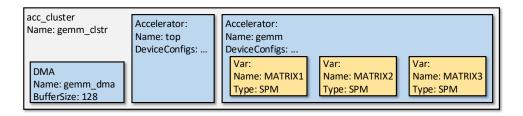

| FIGURE 6.4: Example of the gem5-SALAMv2 device configuration for a accelerator cluster running a general matrix multiplication application.                                                                                                                                        | 73 |

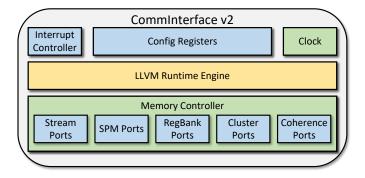

| FIGURE 6.5: Overview of the LLVM runtime model present in gem5-SALAMv2. The automated configuration tools invoked during setup provide the constructs needed for elaboration to generate the static graph. This is then dynamically mapped to the allocated resources to perform a cycle accurate simulation of the application.                                               | 78 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 6.6: Overview of the communications interface in gem5-SALAMv2. This new unified interface handles all communications between gem5-SALAMv2 clusters, accelerators, memory objects, and the gem5 ecosystem.                                                                                                                                                               | 80 |

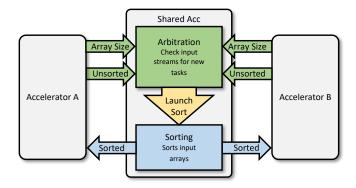

| FIGURE 6.7: Shared accelerator resource scenario detailing the ability of gem5-SALAMv2 to have data driven accelerators.                                                                                                                                                                                                                                                       | 84 |

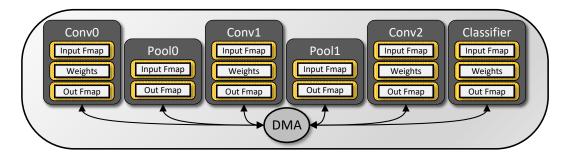

| FIGURE 6.8: Design A - All accelerators in this architecture are shown connecting to a single DMA for all memory transfers.                                                                                                                                                                                                                                                    | 92 |

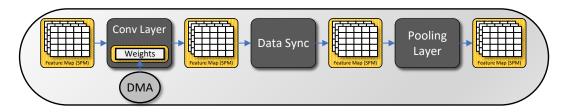

| FIGURE 6.9: Design B Functional Unit - With the increased complexity of Design B, only a single network functional unit is shown that demonstrates how the Convolution, Data Sync, and Pooling layers are connected internally.                                                                                                                                                | 92 |

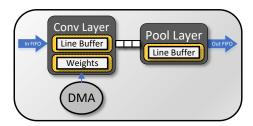

| FIGURE 6.10: Design C Functional Unit - With the integration of data management into the convolution accelerator, there is now only a Convolution and Pooling layer at a functional unit level. The Convolution accelerator stores data from the input FIFO to the Line Buffer SPM to be utilized for the operation, all accelerators are interconnected with streaming FIFOs. | 93 |

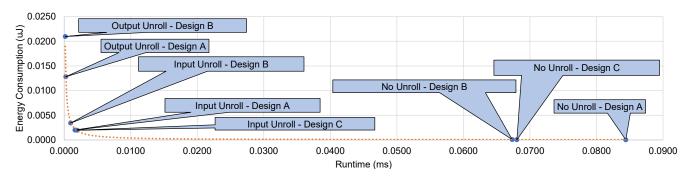

| FIGURE 6.11: Total Data-Path Computational Energy Consumption VS<br>Runtime Plot for LeNet-5 Test Configurations                                                                                                                                                                                                                                                               | 94 |

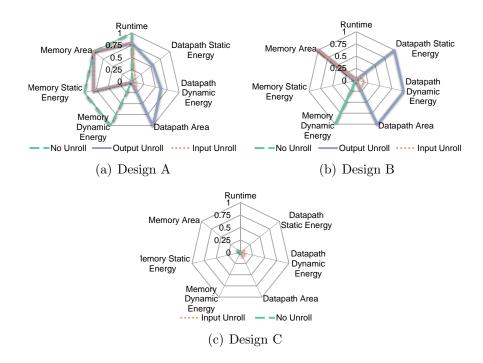

| FIGURE 6.12: LeNet-5 Power, Area, and Performance Values - These values were normalized by dividing all results by the max value obtained in any of the three architectures for each category. This technique preserves the ratio of the results between architectures on a scale from 0-to-1.                                                                                 | 95 |

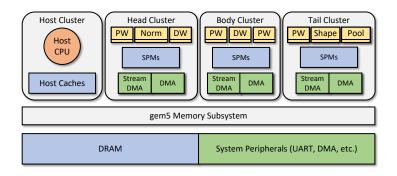

| FIGURE 6.13: MobileNetV2 System Architecture - System architecture details for the MobileNetV2 design. The Head, Body, and Tail clusters are represented here, and show how the design interfaces with the gem5 system.                                                                                                                                                        | 96 |

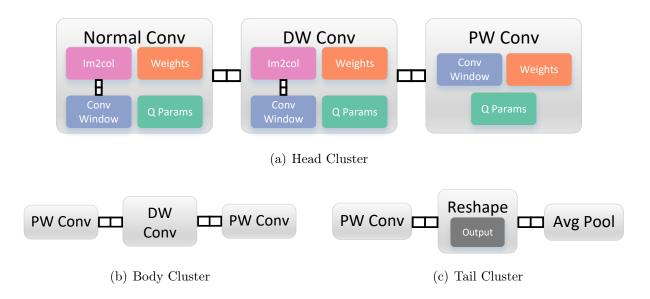

FIGURE 6.14: MobileNetV2 Cluster Architecture - Individual cluster configurations for the Head, Body, and Tail. The Head (a), shows a detailed overview of the Normal, Depthwise, and Pointwise convolutional functional units (FUs). The Body (b) and Tail (c), use a summarized version of each of these FUs to demonstrate how they are configured at the cluster level.

#### LIST OF ABBREVIATIONS

API Application Programming Interface.

CDFG Control and Dataflow Graph

CPU Central Processing Unit.

DMA Direct Memory Access

DNN Deep Neural Network

DSE Design Space Exploration

FPGA Field Programmable Gate Array.

GPU Graphical Processing Unit.

HDL Hardware Description Language

HLS High-level synthesis.

IR Intermediate Representation

ISA Instruction Set Architecture.

LLVM Low Level Virtual Machine.

OpenCL Open Compute Language.

RTL Register Transistor Logic.

SDK Software Development Kit.

SoC System on Chip

SPM Scratchpad Memory

#### CHAPTER 1: INTRODUCTION

With transistor technology reaching the fundamental limits of Dennard scaling and Amdahl's law, hardware designers are searching for innovative new means for driving device performance and power efficiency. Ironically many recent advances in compute technologies have in fact been reversions from general purpose processors to application-specific designs that can leverage the dark silicon on modern systems on chips (SoCs) with highly optimized and power-efficient datapaths. The fundamental limitation has thus become the costs of developing, testing, and integrating new hardware in a domain where algorithmic advances rapidly eclipse the capabilities of new hardware. To amortize some of the expenses associated with the development of hardware accelerators, we have also seen the development of domain-specific accelerators. These types of devices trade some of the efficiency of fully application-specific accelerators for limited programmability to support a small subset of applications, or domain. The most recognizable example of domain-specific accelerators is the integrated graphics processors found in many modern CPUs.

One domain that has been a particularly significant driver in domain-specific processor design has been deep learning. Deep learning applications are characterized by massively parallel computation along with equally impressive amounts of data movement. Deep learning became popular after general-purpose GPUs provided a platform with the necessary scale to handle the data-intensive training regimens characteristic of neural networks. However, the hardware requirements of modern deep neural networks (DNNs) rapidly outpaced that capacity of general-purpose GPUs. This lead to the rise of domain-specific accelerators for deep learning such as Google's Tensor Processing Unit (TPU) [1] and NVIDIA's tensor cores and open-source NVDLA accelerator. These accelerators leverage large systolic processing arrays to exploit the compute parallelism present in DNNs while supporting flexibility in data movement as data demands shift from input feature limited to network parameter limited. Unfortunately the deep learning application domain has evolved significantly to leverage smaller, sparser networks that swap computation for data-dependent control and hand-

crafted data movement between network blocks. The lower parallelism and increasing runtime control leads to lower occupancy of systolic resources and makes systolic processors like the TPU or NVDLA increasingly inefficient for modern neural networks.

An alternate approach to domain-specific acceleration is to construct a domain-level processor using a series of application-specific processors alongside a flexible interconnect and interfaces. This approach was advocated for in [2], and more recently realized in markets with Xilinx's Versal ACAP [3]. These designs offer the promise of increased flexibility over traditional systolic arrays for emergent deep learning applications, while still offering the efficiency and performance benefits of domain-specific processing.

## 1.1 Hardware Design Tools and Design Space Exploration

The field of hardware design automation and design space exploration is quite rich with solutions for synthesis, coverage testing, and layout. The process of taking a new design from Register-Transfer Logic (RTL) simulation to chip tapeout has never been easier, with industrial-quality tool chains becoming more and more available to end users. Tool chains like AMD/Xilinx's Vitis Unified Software Platform even bring high performance High Level Synthesis (HLS) tools to developers that are more comfortable with software development than hardware development. Alternatively, expanding support for high-level language constructs in high-level hardware description languages like SystemC, SystemVerilog, and Chisel[4] provide opportunities to develop hardware with a higher degree of abstraction.

Despite robust tool support for post-RTL development, the tool space for pre-RTL design and early design space exploration is much weaker. This space is far more dominated by academic interests that leverage simulation and analytical models for evaluating the potential benefits of new architecture ideas prior to the large time and money investment of extensive RTL development. Software-based simulation solutions offer important opportunities to explore key design considerations around hardware structure and integration long before a firm architecture has been established. Full-system simulations, like those offered by gem5[5], enable designers to evaluate architecture ideas and identify integration challenges ranging from memory interfaces and I/O, to driver support in modern operating systems. Importantly these simulations retain their value even into RTL develop-

ment due to their greater capacity for rapid design space exploration. While simulation solutions are fantastic for modeling classical CPU and GPU-based systems, their support for more fundamental hardware design is severely lacking. Numerous efforts have been made to integrate custom hardware accelerators and other heterogeneous compute elements to simulation, including [6, 7, 8, 9, 10, 11]. Unfortunately these solutions are generally highly tailored to a particular integration challenge and ultimately fail to provide a generalized solution to integrating new custom hardware models into gem5 and other simulators.

A side effect of the lack of support for custom hardware solutions in early design space exploration tools is the increased challenge for exploring memory optimization of such devices. Even the industrial tool chains for RTL development largely lock users into predefined intellectual properties built on top of standards like AXI, AXI-Stream, and AXI-Lite. Meanwhile most pre-RTL solutions focus more on datapath modeling or their own customized solutions for data tiling[9, 8]. As a result there is a lack of tools for both optimizing and exploring unique memory solutions prior to extensive RTL development.

#### 1.2 Contributions

Given the rapidly evolving nature of both hardware and algorithmic design for deep learning applications it is important to have robust tools for hardware-software co-design. Given the heavy data-dependence of DNNs it is just as important to optimize device memory and system integration as it is to optimize computation. There is a need for tools that can both analyze the design constraints of emergent AI applications and rapidly prototype designs in order to explore system level impacts of design optimizations. To this end my work seeks to make three key contributions:

- Automate memory access analysis for memory optimization of hardware accelerators including variable-level memory assignment and allocation[12], and automated hardware prefetching on FPGAs[13].

- Produce an innovative pre-RTL simulation tool for design space exploration of custom hardware accelerators[14, 15].

- Introduce new simulation design abstractions that bring hardware-level insights into event

driven simulator design.

## 1.3 Report Outline

The remainder of this report is organized as follows. Chapter 2 covers relevant background knowledge and covers other works that relate to the optimization and design-space exploration of hardware accelerators. Chapter 3 and Chapter 4 highlight implementation of the my first contribution through two associated works in hardware accelerator memory optimization. Chapter 5 describes my second contribution by introducing and detailing the design-space exploration tool gem5-SALAM. Chapter 6 takes a deeper dive into the challenges of event-driven simulation, and how gem5-SALAMv2 seeks to fundamentally address these challenges with new design abstractions. Additionally chapter 6 describes the process of redesigning the original gem5-SALAM from the ground up to provide a robust simulation framework for modern compute architectures. Chapter 7 contains concluding remarks from this report.

#### CHAPTER 2: BACKGROUND AND RELATED WORK

## 2.1 The Low-Level Virtual Machine (LLVM) Tool Chain

The translation of human readable code in high level programming abstractions to optimized machine code is a complicated and ever-growing task. In the past every new combination of source language and target architecture required a customized compiler solution. This lead to numerous redundancies since the vast majority of code optimizations are completely independent of source language semantics and target architecture structures. Seeing an opportunity to unify and improve code compilation and optimization, researchers developed the Low-Level Virtual Machine (LLVM) infrastructure [16]. LLVM is a modular code optimization infrastructure built around a unique intermediate representation (IR). This IR provides a level of abstraction similar to that found in many machine instruction sets, while maintaining high level control and data flow semantics normally associated with high-level languages. By providing this level of abstraction, LLVM is able to efficiently optimize code in a way that is independent of both source language and target hardware architecture. LLVM also provides a convenient abstraction for algorithmic analysis that makes it popular in non-traditional compilation tasks such as high-level synthesis (HLS) tools. Since its inception LLVM has gained enormous support from both academia and industry, featuring extensively in numerous proprietary tool chains as well as serving as the foundation for new programming languages like Julia.

## 2.2 Design and Exploration of Hardware Accelerators

One of the biggest challenges for designing and integrating new accelerators into modern SoCs is simulating and exploring design parameters. Often accelerators are initially designed and tested in isolation, which can lead to over-tuning of design parameters based on idealized assumptions about data availability and other system overheads. While synthesis and RTL simulations of accelerators in isolation may be reasonably quick, full-system RTL simulation of an SoC can often take days or longer. As a result, electronic design automation (EDA) companies, like Synopsys, have developed

proprietary tools like Platform Architect that abstract many system-level elements and provide cycle-accurate performance estimations of SoC designs incorporating accelerators through SystemC and transaction-level models (TLM).

As hardware design has shifted from classical RTL design flows to more software developerfriendly approaches the LLVM compiler [16], and its IR, has become a key component of many

design flows. Popular HLS tools like Vivado and LegUp [17] internally use a modified clang tool

flow for translating hard descriptions written in C to popular RTL targets such as Verilog, VHDL,

and SystemC. With growing interests in deep learning acceleration the LeFlow project [18] was

developed to integrate TensorFlow's XLA compiler with LegUp and enable the synthesis of deep

learning accelerators on FPGAs. In addition to synthesis tools, LLVM has also been employed for

pre-RTL design space exploration. The RIP framework [19] leverages LLVM for the identification

and modeling of "hot loops" in an application in order to design accelerators for those portions

of code. Similarly, Needle [20] and the work described in [21] leverage LLVM for detecting hot

portions of code and automatically generating accelerators for DySER-styled [22] architectures. For

exploring the design and system-level impacts of loosely-coupled hardware accelerators Lumos+

[23] and LogCa [24] tools can be used. These approaches employ analytical modeling for estimating

the power, performance, and area requirements of hardware accelerators in highly heterogeneous

accelerator-rich systems.

For researchers that do not have access to proprietary EDA tools, the gem5 system simulation[5] and its derivatives have become a popular solution. gem5 is an open-source, industry-backed system simulator based on a joint C++/Python programming abstraction. This provides cycle-accurate system performance estimation at an abstraction that is more accessible to developers who are looking for alternatives to proprietary and RTL-based development tools. Furthermore, its open-source C++/Python API enables the extension of its capabilities. While the base API of gem5 supports a wide variety of models for system elements such as memory, CPUs, GPUs, and busses, it lacks modeling for application-specific hardware accelerators. To address this shortcoming, researchers have sought ways to integrate application-specific accelerator modeling into gem5.

gem5-Aladdin [7] integrates the Aladdin [6] pre-RTL simulator into gem5. The base Aladdin simulator relies on instrumenting LLVM IR [16], associated with C descriptions of hardware accelerator

functionality, in order to generate a runtime trace of executed LLVM instructions. This runtime trace is then loaded into the simulation engine, where it is further optimized and instrumented with timing information before being passed to an event-driven simulation engine. While Aladdin demonstrates impressive accuracy for a pre-RTL simulation model, its reliance on runtime traces can lead to unreliable results for irregular applications. This is the result of its approach of reverse engineering a datapath based on the parallelism of the dynamic instruction trace. In applications where execution semantics and parallelism vary depending on input data, Aladdin will generate different datapaths for the same kernel source code, as the input data changes. Table 2.1 demonstrates this behavior for the Sparse Matrix-Vector Multiplication (SPMV) built around the Compact Row Storage (CRS) data format. In the source code we added a one bit-shift operation that would activate if the input value fell within an arbitrary range we defined, then included this value in one dataset but not the other to demonstrate this shortcoming. As illustrated in Table 2.1, the number of floating-point adders in the datapaths change between two runs with the same kernel code but different input data sets. Additionally, since the value that triggered the shift condition was not in the data set for the first run of the application, Aladdin did not model the shift operation as part of the datapath.

The system integration of Aladdin into gem5-Aladdin introduces new limitations. Here, adjustments to system parameters such as cache line size and accelerator cache size, which can impact data availability, have the effect of changing Aladdin's datapath and power estimation for even regular applications. This characteristic is demonstrated in Table 2.2. In this scenario, a sweep of the highly regular GEMM application is run over varying cache sizes. As the sizes of the caches are varied, the number of allocated functional units also changes. Since Aladdin is reverse-engineering the datapath, changes in lookup times and cache hits/misses affect the availability of data and subsequently, the simulated datapath. Table 2.2 also shows that switching over to a multi-ported

Table 2.1: Aladdin Datapath vs Data-dependent Execution

| Accelerator | Dataset | Functional Units |      |             |

|-------------|---------|------------------|------|-------------|

| Accelerator |         | FMUL             | FADD | Int Shifter |

| SPMV-CRS    | 1       | 8                | 4    | 0           |

| SI WIV-CIG  | 2       | 8                | 8    | 1           |

Table 2.2: Aladdin datapath vs. memory design

| Accelerator | Memory |      | Functional Units |      |

|-------------|--------|------|------------------|------|

|             | Type   | Size | FMUL             | FADD |

|             | Cache  | 256B | 665              | 879  |

| GEMM        |        | 512B | 679              | 903  |

| N-Cubed     |        | 1kB  | 696              | 928  |

| (Fully      |        | 2kB  | 712              | 948  |

| unrolled)   |        | 4kB  | 639              | 843  |

|             |        | 8kB  | 650              | 864  |

|             |        | 16kB | 468              | 624  |

| SPM         |        | 194  | 258              |      |

ScratchPad Memory (SPM) has a significant impact on the datapath that Aladdin simulates. While a hardware developer would certainly want to co-optimize both datapath and memory hierarchy, gem5-Aladdin does not provide developers with the means of decoupling the generated datapath from the impacts of the memory hierarchy. Developers should have the capacity to independently sweep design parameters for both datapath and memory<sup>1</sup>.

Another limitation of gem5-Aladdin stems from the way it has integrated into gem5's system infrastructure. The gem5-Aladdin project exposes the Aladdin simulator to gem5's system infrastructure by creating a gem5 object wrapper. However, Aladdin's wrapper is only partially integrated into gem5. The gem5-Aladdin's partial integration inhibits system-level exploration and prototyping of common accelerator-rich scenarios in modern SoCs. The gem5 component of gem5-Aladdin merely serves accounting for memory latency in the performance estimates of individual accelerators. As an example, to transfer data between the accelerator's private SPM and dynamic RAM (DRAM), direct memory access (DMA) operations must be exposed directly to the accelerator source code, so that they can appear in the runtime trace. The consequence is that accelerators and their private SPMs lack the standard communication ports necessary for intercommunication between devices in the system. Another example is that MMRs and other traditional interfaces are not included in the accelerator wrapper in gem5-Aladdin. The host CPU instead communicates with accelerators via a software bypass integrated into gem5's Syscall Emulation (SE) simulation framework. Furthermore,

<sup>&</sup>lt;sup>1</sup>Both the runtime data tests and the memory hierarchy tests were conducted using the latest build of gem5-Aladdin as of April 2020.

these interfaces cannot merely be added to the Aladdin wrapper without violating design assumptions that are imperative to Aladdin's integration into gem5. Doing so would require a complete redesign of the Aladdin wrapper, custom system elements (i.e., DMAs, SPMs, etc.), device drivers, and user programming experience.

The other gem5 extension, PARADE[8], simulates multi-accelerator architectures based on AR-CMP [25]. This simulator offers a full-system simulation with a full Linux kernel in gem5. Accelerators are designed via a scarcely-documented and proprietary custom data-flow language while power and timing information are extracted from HLS. Since PARADE relies on static estimates of power and timing from HLS, it is unable to accurately model accelerators where power and timing can vary based on input data. PARADE also enforces a fairly rigid system architecture, limiting the scope of design space exploration to the model proposed in ARCMP[25]. Rather than being able to communicate directly with accelerators within PARADE's framework, system elements instead send all requests to PARADE's Global Accelerator Manager (GAM) which facilitates all communication within the PARADE framework, as well as across the boundary between gem5 and PARADE. Furthermore, there is no means by which a user can control or modify the internal timing and data flow within PARADE's framework. This includes the order of execution of cascaded accelerators that operate in a producer-consumer fashion, and can result in the out-of-order operation of accelerators. Similar to gem5-Aladdin, any designs that don't precisely match the original design specification of ARCMP[25] and its GAM, require an extensive redesign of PARADE's system elements, scheduler, and even the dataflow language used for describing accelerators.

Another recent tool that also leverages LLVM for parsing and instrumentation is the MosaicSim tool [9], which offers a lightweight simulation of heterogeneous systems comprised of CPUs and accelerators. MosaicSim roughly models hardware accelerators as simple in-order or out-of-order compute cores, providing configuration options like instruction issue width, re-order buffer size, and load-store queue (LSQ) size. While this can provide rough approximations for the compute performance of an accelerated segment of an LLVM IR compute graph, it lacks many of the fine-grained controls needed to model or profile an application-specific datapath. For instance, users lack the capacity to model hardware constraints such as functional unit re-use or even adjust the timing/power/energy costs of individual elements of the compute datapath. The tool does also

support integration of RTL models generated by HLS tools, however these RTL models are not integrated into the same tiled memory model of the more abstract models. MosaicSim relies on pre-generated execution traces for the modeling of accelerators. In MosaicSim this includes both a trace of load/stores ops, as well as a control-flow trace to track the progression of basic blocks. Reliance on execution traces imposes several major restrictions on modeling in MosaicSim. Trace sizes, generation times, and read times introduce significant overheads for simulation. For very large and long-running applications, traces may exceed several GB in size. Additionally, for applications where the load/store and control flow behaviors are dictated by input data, users need to generate new traces for each new set of input data.

For researchers who are more comfortable with SystemC development, gem5 now supports the direct integration of SystemC models [11]. SystemC support in gem5 was achieved by translating transactions within the TLM2.0 IEEE1666 standard to gem5's internal memory transaction model. This offers the most opportunities for design space exploration and simulation, however as an HDL-based option, it will also require a higher degree of design effort than the other options.

## 2.3 Memory Optimization Challenges for Hardware Accelerators

The optimization of memory hierarchies has been studied extensively in general-purpose CPUs. Many innovative solutions have been developed for memory-path optimization (cache vs. scratchpad memory) on embedded CPUs [26, 27, 28, 29] and extensive work gone toward optimizing hybrid memory structures for domain specific CPUs. Such optimizations have shown to lead to significant improvements (20% or more) in both raw performance and overall power consumption within a specific domain [27, 29].

At the same time, while a large amount of effort has been focused on the design and exploration of application-specific datapaths, the exploration of application-specific memory hierarchies has not been explored in depth. For the purpose of simplifying accelerator design, and regularizing data access times in accelerators, hardware architecture generally rely of scratchpad memories and streaming interfaces for data access. The general approach isn't all that different than preloading regularly accessed data in the shared memory of GPUs for improved access times. With this approach large data structures with predictable access patterns can be divided into smaller tiles,

and the costs of off-chip memory access can be hidden by overlapping the execution on one data tile with the movement of subsequent tiles to the scratchpad in a process called *double buffering*. Double buffering provides fantastic efficiencies in hardware design by amortizing off-chip memory access costs, regularizing data access latencies, and limiting the amount of expensive on-chip memory resources that must be allocated to support accessing large data structures[30]. Unfortunately this approach cannot be used on structures with sparse or irregular data access, as seen in sparse matrix operations and my graph traversal algorithms. In these cases the entire structure must be allocated and transferred to the scratchpad memory, regardless of how much of the structure is actually used by the accelerator.

Faced with the limitations of scratchpad and streaming memories for irregular data access in applications, some hardware designers have begun to look into using caching methods employed by modern CPUs and GPUs in their accelerator designs[7]. Caches trade the highly regular access times of scratchpad memories for a smaller memory footprint. By exploiting spatial and temporal locality in data access, caches are able to mitigate off-chip memory accesses while storing a limited subset of the application data. Unfortunately miss penalties for data not present in the cache are high, and the initial access of data in off-chip memory cannot be amortized in the same way that streaming and scratchpad-based memory access can be. This makes caches sub-optimal for accessing highly regular data structures.

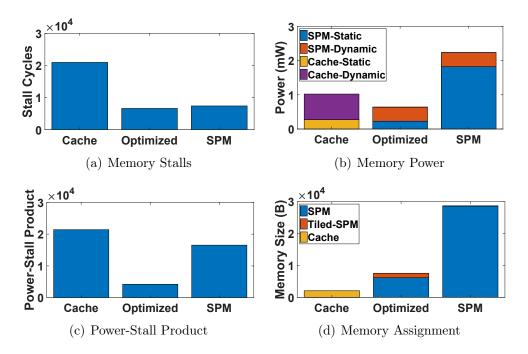

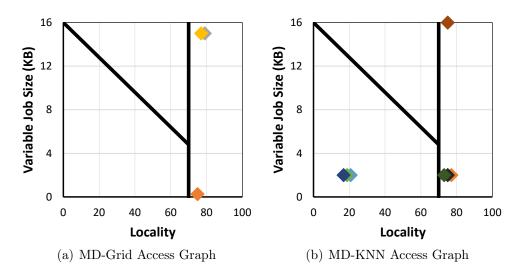

In the same way that optimization of an accelerator datapath is highly application-specific, design and optimization of an accelerator memory hierarchy should also consider algorithm-intrinsic characteristics. Fig. 2.1 shows a comparison of different memory configurations for a K-Nearest Neighbors application from the MachSuite [31] benchmark suite over a series of parameters included datapath stalls, power consumption, and allocated memory size. Additionally a new metric, called the power-stall product, is introduced to capture the co-optimization of memory by minimizing power consumption and memory stalls exposed to the datapath. A lower power-stall product is better in this evaluation. The particular K-Nearest Neighbors application explored in Fig. 2.1 consists of three input arrays with runtime data-dependent memory access, one input array with nicely strided data access, and three output arrays with strided data access. Allocating all of these arrays to a scratchpad would require approximately 28KB of on-chip memory. Given the nicely strided

Figure 2.1: MD-KNN Exploration

data access pattern and large size of four of the seven arrays in the application, a tiled or streaming memory can reduce the required memory allocation by more than three times vs. the monolithic scratchpad memory approach. Execution stalls can also be reduced since the data movement of the streaming and tiled data can be overlapped with computation.

It should be noted that optimizing purely for on-chip memory size would suggest that a cache is the optimal allocation. A sweep of the cache design space for this application found that there was no performance benefit of increasing cache size beyond 2KB. This is because caches are able to exploit data locality to capture the working set of an application without needing to store all of an applications data at once. This benefit becomes more pronounced as data size and sparsity increase, making it ideal for applications with runtime-dependent control over large data structures. The downside to caching is the cost of cold start misses the first time data is loaded to cache, as well as the potential need to re-fetch data that is replaced in the cache. Since caches move data at a smaller granularity than the direct memory access (DMA) engines used in scratchpad memory-based approaches, they are less able to amortize the timing and energy costs of mass data transfer from off-chip memory. This results in lower power-stall product efficiency per byte of memory allocated for caches vs. scratchpads. Despite this lower efficiency, the monolithic cache approach achieves

nearly the same level of power-stall product efficiency as a monolithic SPM design, and in some applications the optimal allocation will lean in favor of caching. The challenge then is to identify when data should be cached vs. streamed or bulk transferred to SPMs.

## 2.4 OpenCL Synthesis and Memory Optimization on FPGAs

Availability of OpenCL synthesis for FPGA development opens up many interesting research areas for developers and users of HLS tools alike. Many works study the efficiency of common massively-parallel workloads on FPGAs devices[32, 33, 34, 35, 36, 37, 38, 39, 40]. This includes the work of Purkayastha et al.[35], which introduced a generic taxonomy to classify and maximize parallelism potential on Intel FPGAs. These approaches primarily focus on application-specific performance optimization techniques [33, 34], or making performance comparisons between FPGAs and GPUs [32, 35].

There is also an interest in using OpenCL pipe semantic for efficient inter-kernel communication across multiple OpenCL kernels [41, 42, 43, 44]. The pipe semantic has been leveraged as part of both the Alterra and Xilinx HLS[45] solutions for synthesizing efficient data movement hardware between design units. However, the above implementation all focus on more traditional producer-consumer buffers between compute kernels that mirrors the well-established AXI-stream semantic.

These design principles are largely explored in the context of multi-threaded, multi-kernel work-loads within the reconfigurable computing community [46, 47, 48, 49, 50, 51, 52, 53, 54]. These works generally focus on context switching and partial reconfiguration to support multiple applications on the same hardware. Some work has been done to study multi-threading on singular applications with a higher emphasis on threading performance [55, 56]. Unfortunately multi-threading support is still quite limited in HLS-based design flows that treat OpenCL threads like traditional hardware loops.

The idea of decoupling memory access from compute is well established within the architecture community[57]. Usually works have focused on general-purpose architectures (e.g., CPUs, GPUs, array processors) or application-specific accelerators with a fixed hardware [58, 59, 60]. Works like Domain-Specific Design Space Exploration[39] and Function-Level Processor[40] attempt to extend these concepts to the scope of domain processors. While these works briefly explore the

compute/memory decoupling concept within the scope of broader compute decoupling across the domain, they do not offer any specific solution for memory and compute decoupling.

One possible solution to the decoupling problem is through pre-fetching[61, 62]. Pre-fetching leverages an understanding of data access features within an application in order to load the necessary data prior to its usage. Pre-fetching can either be implemented in hardware such as is the case in [63, 64, 65] or in software as seen in [66, 67, 68]. Some efforts have been made to develop joint hardware/software implementations for pre-fetching[69], particularly with respect to address-based cache pre-fetching and optimization[70, 71].

#### CHAPTER 3: LOCALITY AWARE MEMORY ASSIGNMENT AND TILING

The first contribution of this research is to aid in and automate the analysis of hardware accelerator memories based on the algorithm-intrinsic characteristics of the accelerated application, presented as Locality Aware Memory Assignment and Tiling in the Design Automation Conference 2018[12].

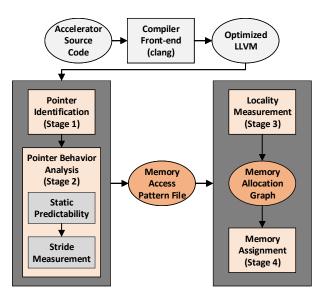

Figure 3.1: Memory Allocation Tool Chain

Rather than sweeping over the entire design space of memory hierarchies for an accelerator I have developed an approach and tool, shown in Fig. 3.1, that examines the algorithm-intrinsic characteristics of memory access in an application, and guides hardware developers in designing a locality-aware memory assignment and tiling design. This process can be broken into two main phases: (1) static memory access analysis and (2) variable-level memory assignment.

## 3.1 Static Memory Access Analysis

The static memory analysis is performed at the abstraction provided by the LLVM intermediate representation (IR) where memory access strides can be examined on a per-variable basis. As shown in Fig. 3.1, a user starts by compiling the accelerated application to the LLVM IR using the corresponding LLVM frontend compiler (clang for C/C++ applications). This LLVM is then

parsed in two phases: (1) Pointer Identification and (2) Pointer Behavior Analysis.

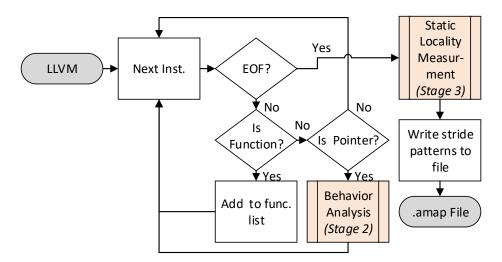

## 3.1.1 Pointer Identification

The first pass over the IR focuses on identifying the addressing of memory pointers. Pointers are organized by function call and are classified as local or global with respect to the function in which they are called. This parse works at the function granularity in order to limit analysis of the memory accesses to static behaviors that can be understand at compile-time. The general flow of this parse is shown in Fig. 3.2.

Figure 3.2: Pointer Identification (Stage 1)

Whenever a new memory access is found, corresponding addressing instruction is added to the pointers access list in the tool, and the pointer's access behavior is updated by the Pointer Behavior Analysis stage. Once the entire file has been parsed, access strides are calculated for all pointers found in the file. The tool then dumps the complete memory access pattern information to a file for further analysis in the second part of the approach.

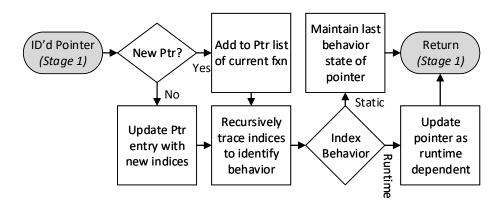

#### 3.1.2 Pointer Behavior Analysis

The purpose of the pointer behavior analysis phase, shown in Fig. 3.3 is to classify the static predictability of a memory access, and determine the stride of accesses without runtime dependencies. Runtime-dependent accesses are characterized by array indices that are dependent on input data in some form. This includes, but is not limited to, cases such as determining an array index from a value stored in another array, or traversing a graph from a user-defined starting point. From

the perspective of the analysis tool, it is simply looking through the critical path leading up to the memory access for any computation that is dependent on a variable that is declared outside of the function's scope. Memory accesses without external dependencies are considered predictable, even if they are addressed by another variable that is itself predictable.

Figure 3.3: Pointer Behavioral Analysis (Stage 2)

A benefit of the LLVM IR is that it maintains application control and dataflow characteristics of high-level programming languages, while providing a low-level abstraction closer to a machine's instruction set architecture (ISA). The explicit data and control flow present in the IR allows for a quick recursive trace of the critical path of a memory access.

When all accesses to particular pointer in a file have been identified, the tool is then able to determine the variable's access stride via the process shown in Fig. 3.4.

Figure 3.4: Stride Measurement (Stage 3)

Stride measurement is skipped entirely for pointers with runtime-dependent characteristics. For all other pointers, the tool further classifies the pointer indexes as *constant*, *loop*, or *variable*. Constant indexes are characterized by explicit integer offsets or accesses to the base pointer, which

corresponds to the C expression array[0] or \*array. Loop indices correspond to incrementing/decrementing counters commonly used in loops. Indices which are the result of some other computation are considered variable. When nested loops are found in a program, there may be instances in which a loop index takes on the form of a variable index. An example of this would be when a multidimensional array is indexed like a 1D array (ex: A[i\*rowlength+j]). To capture these cases the classifier performs a trace back on the array index instruction to search for such expressions.

After determining the index type for each access on a pointer, the stride of the accesses can then be computed. The stride of a loop indexed variable can be determined by examining the corresponding increment/decrement operation. For constant indices the tool calculates the stride between successive accesses. If the stride is constant, or within a limited range, the average stride is assigned and the variable is marked as strided. In the case of irregular strides the pointer is marked as variable an extrema are noted. Stride calculations are not performed for pointers with mixed or variable type indices, but extrema are noted if available.

## 3.1.3 Memory Access Pattern (MAP) File

The Memory Access Pattern (MAP) file generated by the tool provides designers with an overview of memory access in an application, which can be used to guide designers in memory hierarchy design. As a secondary benefit, it provides a quick point of reference to guide the designer through the original LLVM IR file if they want to investigate memory access further by hand.

Figure 3.5: Memory Access Pattern-file (MAP-file)

The structure of the MAP file is shown in Fig. 3.5. In addition to the pointer-specific parameters described above, the MAP file also includes information about calling functions, including parameter lists. This can be used to understand the linkage of variables that might be passed between function

calls, to better understand application-level characteristics. For each pointer that is considered global within a function's scope, its type, corresponding IR instruction, and indices are listed. The stride for the pointer is listed if it could be calculated. Otherwise the classification of the stride is provided.

## 3.2 Variable-Level Memory Assignment

After the the memory access analysis tool has generated the application's memory access pattern file, the approach proceeds to the assignment and allocation of memory. Variables assigned to scratchpad memories or tiled scratchpad memories are assigned to their own unique memory elements. Due to limitations in evaluation tools, cached variables are all assigned to the same cache. Prior to memory assignment, however, the spatial and temporal locality of each variable must be determined.

### 3.2.1 Locality Measurement

The locality measurement phase of the approach is responsible for determining the inherent static locality of each variable based on the access patterns found in the MAP file. The spatial locality of a variable is determined by the length of its stride. The formulation for spatial locality formulated by Weinburg et al. [72] is shown in Eq. 3.1. For the purposes of this calculation, the absolute value of the stride is used for any negative-valued strides. In the case that the stride of a variable could not be determined, manual verification of stride is employed.

$$L_{spatial} = \sum_{stride=1}^{\infty} \frac{P(stride)}{stride}$$

(3.1)

The temporal locality of a variable is determined by Eq. 3.2, based on the work in Weinburg et al. [72]. Since the Weinburg et al. locality analysis relies on runtime values that are not available in this approach, the distance metric is instead replaced by counting the number of memory accesses to particular variable before a non-loop index is repeated.

$$L_{temporal} = \sum_{i=0}^{log_2(N)} \frac{(dist_{2^{(i+1)}} - dist_{2^i}) * (log_2(N) - i)}{log_2(N)}$$

(3.2)

The overall locality of a variable is finally determined by a weighted sum of spatial and temporal locality, as shown in Eq. 3.3. For this formulation spatial locality is given a higher weight than temporal locality due to its greater significance in accelerated applications.

$$L_{total} = \left(w_s * L_{spatial} + w_t * L_{temporal}\right) * 100 \tag{3.3}$$

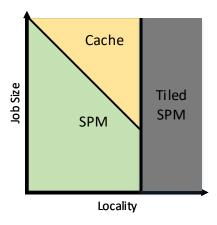

Tiled scratchpad memories are designed to exploit spatial locality, but are limited by temporal locality that may require re-fetching of older data tiles. Caches benefit significantly from both spatial and temporal locality due to the corresponding reduction in cache misses. Traditional scratchpads do not receive any benefit from data locality due to the fact that the entirety of the application data needs to be preloaded into the scratchpad prior to running the accelerator.

#### 3.2.2 Memory Assignment