# ULTRA LOW POWER TECHNIQUES FOR MACHINE LEARNING ON THE EDGE

by

#### Md Munir Hasan

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2022

| Approved by:        |

|---------------------|

| Dr. Jeremy Holleman |

| Dr. Andrew Willis   |

| Dr. Hamed Tabkhi    |

| Dr. A. Suzanne Boyd |

# ©2022 Md Munir Hasan ALL RIGHTS RESERVED

#### ABSTRACT

MD MUNIR HASAN. Ultra Low Power Techniques for Machine Learning on the Edge. (Under the direction of DR. JEREMY HOLLEMAN)

Deep learning has become an integral part of machine learning. It has radically transformed our lives in healthcare, automotive systems, human computer interaction etc. Although, deep learning requires a tremendous amount of compute power and resources, the success of deep learning in solving complex tasks has generated a serious interest in deploying deep learning models in edge sensors and IoT devices. However, that goal presents serious challenges. Typical deep learning models require very powerful hardware with large memories and high power consumption. However, sensor systems and IoT devices at the edge are heavily resource constrained. They have a limited amount of compute power and on-board memory. That is why many efforts are being actively pursued to optimize the deep learning models so that they fit into the limited resources of edge devices.

In this dissertation, I explore different techniques for achieving ultra low power hardware for enabling machine learning at the edge. There have been numerous advances in circuit design techniques such as subthreshold analog computing, in memory computation, etc., for very low power applications. Emerging devices and circuits to integrate those devices into low power applications have shown promising results for custom hardware based edge devices. In this study, I explore neuromorphic techniques that lower the power consumption of the computation hardware without significantly degrading the performance. I draw inspiration from biology to design low power circuits, specifically spiking neurons of the biological nervous system. I explore biologically relevant neurons, circuits and

learning rules to minimize computation and power consumption for machine learning at the edge device and sensors.

I have proposed a modification to a sparse coding algorithm that decreases the number of circuits for hardware implementation. I have proposed an analog spiking neuron design which can display a variety of spiking behaviors. The circuit is compact, low power, uses low supply voltage and has high power efficiency, which improves the state of the art. Analog circuits suffer from the problem of leakage current, which makes the design of synaptic circuits difficult. I have proposed a leakage current mitigation technique in a synaptic circuit array and provide simulation experiments to show its efficacy. Spiking neural network is still an emerging branch of machine learning. Hence, there are a lack of necessary tools for simulation. Although there are many hardware neuron circuits, there are no spiking neural network simulators that can account for the hardware non-idealities in the simulation. When it comes to the performance of robust circuits and systems with predictable outcomes through simulation, the inclusion of hardware non-idealities is a must. Given the complexity of spiking neural network hardware, it is not an easy task. I propose phase-plane method for easily extracting hardware non-idealities and using them in the existing simulator to simulate spiking neural networks. The proposed method is computationally inexpensive and easily integrates with spiking network simulators. I compare the spice simulation and phase-plane simulation of spiking neural networks to show that phase-plane can indeed account for hardware non-idealities.

#### ACKNOWLEDGEMENTS

I would like to thank my supervisor Dr. Jeremy Holleman for his continuous support and advice. I am grateful to him for his guidance in this work. I would like to thank the Graduate Assistant Support Plan (GASP) for financial support in my graduate studies. I would also like to thank the committee members Dr. Andrew Willis, Dr. Hamed Tabkhi and Dr. A. Suzanne Boyd for their time and constructive discussion in shaping this dissertation.

$This \ work \ is \ dedicated \ to \ my \ loving \ parents.$

### Table of Contents

| List | of Ta | bles                                                 | xi  |

|------|-------|------------------------------------------------------|-----|

| List | of F  | gures                                                | xii |

| Glos | sary  | х                                                    | vii |

| Chap | oter  | : Introduction                                       | 1   |

| 1.   | 1 N   | otivation                                            | 2   |

| 1.   | 2 P   | oposed Contributions                                 | 4   |

| 1.   | 3 R   | eprint Permissions of Previously Published Materials | 5   |

| Chap | oter  | : Fundamentals of Neuromorphic Engineering           | 6   |

| 2.   | 1 B   | ological Spiking Neuron                              | 7   |

|      | 2.    | .1 Neuron Operation                                  | 7   |

| 2.   | 2 S   | iking Neuron Models                                  | 11  |

|      | 2.    | 2.1 One dimensional Leaky Integrate and Fire Model   | 12  |

|      | 2.    | 2.2 Two or More Dimensional Model                    | 14  |

| 2.   | 3 Ir  | formation Encoding                                   | 14  |

|      | 2.    | 8.1 Neuron Based Encoding                            | 15  |

|      | 2.    | 3.2 Population Based Encoding                        | 16  |

| 2.   | 4 L   | arning in Spiking Models                             | 16  |

| 2.   | 5 D   | scussion                                             | 19  |

| Chap | ter 3: Memory Efficient Sparse Coding                 | 20 |

|------|-------------------------------------------------------|----|

| 3.   | Introduction                                          | 20 |

| 3.5  | Sparse Coding Algorithm                               | 21 |

|      | 3.2.1 Network Design                                  | 21 |

|      | 3.2.2 Learning Rules                                  | 23 |

|      | 3.2.3 Learned RFs                                     | 25 |

| 3.3  | Sparsity of Activities                                | 26 |

| 3.4  | Reconstruction Accuracy                               | 28 |

| 3.   | Quality of RFs and Reconstruction                     | 28 |

| 3.0  | Computation and Hardware Complexity                   | 31 |

| 3.   | Conclusion                                            | 31 |

| Chap | ter 4: Compact Ultra Low Power Spiking Neuron Circuit | 33 |

| 4.   | Introduction                                          | 33 |

| 4.5  | Neuron Circuit                                        | 34 |

| 4.3  | Circuit operation                                     | 34 |

| 4.   | Spike patterns                                        | 37 |

| 4    | Power Consumption                                     | 39 |

| 4.0  | Comparison                                            | 40 |

| 4.   | Effect of device mismatch                             | 42 |

| 4.8  | Conclusion                                            | 43 |

| Chap | ter 5: Synapse Circuit and Leakage Compensation       | 45 |

| 5.   | Introduction                                          | 45 |

| 5.2  | Method                                                | 47 |

|      | 5.2.1 Initial Synapse Circuit                         | 47 |

|      | 5.2.2 Leakage Current Compensating Circuit            | 49 |

| 5.3  | Experiment, Results and Discussion                    | 51 |

|      | 5.3.1 Experimental Setup                              | 51 |

|         | 5.3.2   | Results                                           | 53  |

|---------|---------|---------------------------------------------------|-----|

|         | 5.3.3   | Discussion                                        | 53  |

| 5.4     | Chip    | Implementation                                    | 54  |

| 5.5     | Concl   | usion                                             | 56  |

| Chapte  | er 6:   | Hardware Model Based Simulation of Spiking Neural |     |

| Netwo   | rk      |                                                   | 58  |

| 6.1     | Introd  | duction                                           | 58  |

| 6.2     | Overv   | view of Phase Plane Analysis                      | 59  |

|         | 6.2.1   | Phase Plane                                       | 59  |

|         | 6.2.2   | Solving ODE Using Phase Plane                     | 61  |

| 6.3     | Silicon | n Circuit Using Phase Plane                       | 66  |

|         | 6.3.1   | Neuron Circuit                                    | 66  |

|         | 6.3.2   | Mathematical Description                          | 68  |

|         | 6.3.3   | Solving Circuit ODE Using Phase Plane             | 69  |

|         | 6.3.4   | Meshgrid Size and Memory Access Time              | 73  |

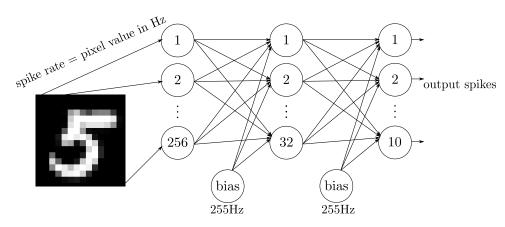

| 6.4     | Neura   | al Network Simulation                             | 73  |

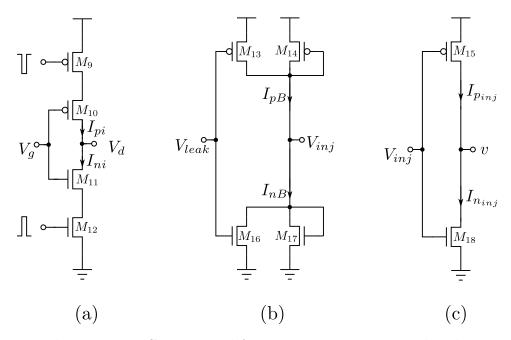

|         | 6.4.1   | Synapse Circuit                                   | 73  |

|         | 6.4.2   | Synapse Model Extraction                          | 75  |

|         | 6.4.3   | Network Simulation for classification             | 78  |

| 6.5     | Concl   | usion                                             | 81  |

| Chapte  | er 7:   | Conclusion                                        | 83  |

| Bibliog | graphy  | 7                                                 | 86  |

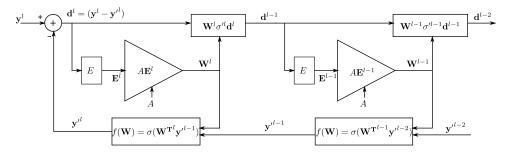

| Appen   | dix A   | : Supervised Learning as Negative Feedback        | 99  |

| A.1     | Introd  | duction                                           | 96  |

| A.2     | Theor   | retical Background                                | 100 |

| ۸ و     | Moth    | o.d                                               | 100 |

|       | A.3.1  | System Setup                                         | 102 |

|-------|--------|------------------------------------------------------|-----|

|       | A.3.2  | Stability Criteria                                   | 103 |

| A.4   | Applic | eation in Machine Learning                           | 105 |

|       | A.4.1  | Regression                                           | 105 |

|       | A.4.2  | Single Layer Classifier                              | 105 |

|       | A.4.3  | Deep Network                                         | 106 |

| A.5   | Compa  | arison with Gradient Descent                         | 107 |

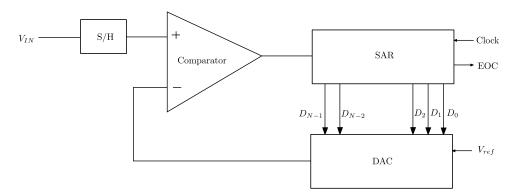

| A.6   | Analog | g to Digital Converter as Supervised Learning System | 109 |

| Appen | dix B: | Codes Used in Simulation                             | 111 |

| B.1   | Meshg  | rid Generation                                       | 111 |

| B 2   | Spikin | g Neural Network Simulation                          | 133 |

### List of Tables

| 3.1 | Classification Accuracy                              | 30 |

|-----|------------------------------------------------------|----|

|     | Transistor size, capacitor and supply voltage values |    |

|     | Synapse Packing Size in a Single Chip                |    |

| 6.1 | Speed Comparison for a 50ms of Network Simulation    | 80 |

## List of Figures

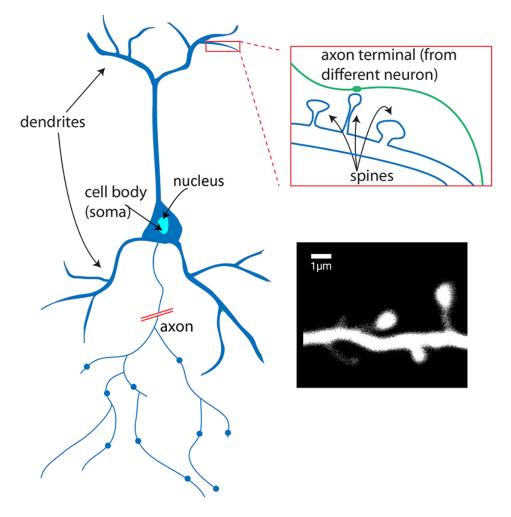

| 2.1 | General structure of a biological neuron. Bottom-right image:                          |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | microscopic image of a dendrite from which spines branch off.                          |    |

|     | (Image courtesy: Queensland Brain Institute, Alan Woodruff; De                         |    |

|     | Roo et. al. [1] / CC BY-SA 3.0 via Commons)                                            | 8  |

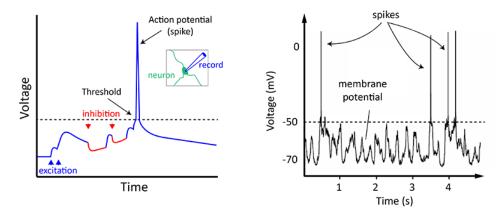

| 2.2 | Generation of action potential in a biological neuron. Left: quali-                    |    |

|     | tative depiction of action potential generation. Right: membrane                       |    |

|     | voltage trace recorded from an actual neuron in a mouse's cortex.                      |    |

|     | (Image courtesy: Queensland Brain Institute)                                           | 9  |

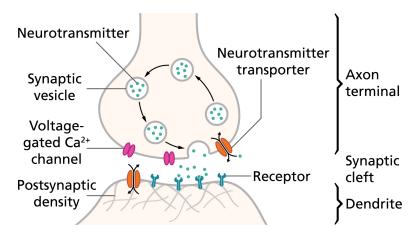

| 2.3 | Spike, causes neurotransmitters to be released across the synaptic                     |    |

|     | cleft, causing an electrical signal in the postsynaptic neuron.                        |    |

|     | (Image courtesy: Queensland Brain Institute)                                           | 10 |

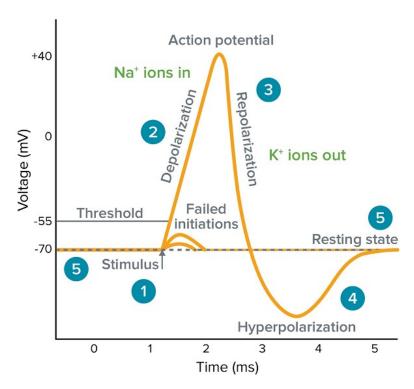

| 2.4 | Shape of an action potential. (Image courtesy: molecular devices)                      | 11 |

| 2.5 | Modeling the neuron cell membrane by electrical circuit                                | 12 |

| 3.1 | (a) Feed-forward, feedback and pixel connection (b) Integrate and                      |    |

|     | fire neuron model                                                                      | 22 |

| 3.2 | 190 randomly selected RFs out of 512 RFs learned using the rules                       |    |

|     | in Eq. 3.6. Each of the RF is $16 \times 16$ size. Simulation settings:                |    |

|     | $\tau = 1$ unit, $\theta = 2$ . Learning rate used in learning these RFs:              |    |

|     | $\alpha = 0.1,  \beta = 0.01.  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots$ | 23 |

| 3.3 | Sparsity histogram: sparsity is indicated by a $16 \times 16$ image patch   |    |

|-----|-----------------------------------------------------------------------------|----|

|     | being represented by small number of active neurons most of the             |    |

|     | time an image patch is presented to the network                             | 26 |

| 3.4 | Reconstruction error comparison                                             | 27 |

| 3.5 | Sparsity and reconstruction rms error tuning by tuning the values           |    |

|     | of inhibitory connection strength                                           | 29 |

| 3.6 | Reconstruction images and rms error for one of the images from              |    |

|     | flower datadset. $W$ matrix is unaltered for reconstruction                 | 30 |

| 4.1 | Proposed neuron circuit (a) Input block, (b) $M_{1-3}$ for thresholding     |    |

|     | and spike generation, (c) $M_{4-5}$ for axon, (d) $M_{6-8}$ for reset and   |    |

|     | spike width, refractory control, (e) $M_{9-11}$ for adaptation and          |    |

|     | bursting control                                                            | 35 |

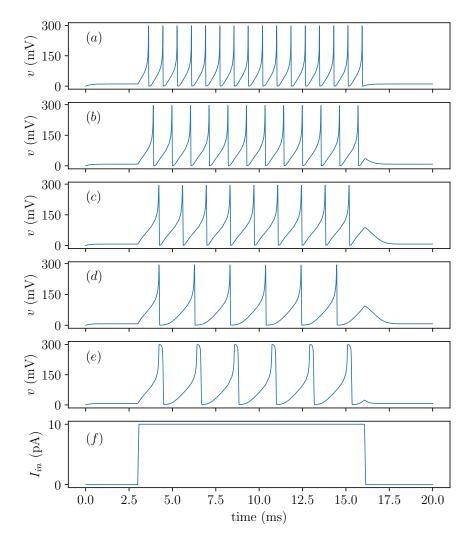

| 4.2 | Different spiking patterns from the Neuron. For all cases $V_{dd} =$        |    |

|     | $300mV$ , $V_{th} = 50mV$ , $V_k = 30mV$ (a) RS: $V_w = 80mV$ , $V_r =$     |    |

|     | $120mV$ , $V_{au} = 280mV$ , $V_{ad} = 3mV$ , (b) RS-FA: $V_w = 80mV$ ,     |    |

|     | $V_r = 120mV, V_{au} = 120mV, V_{ad} = 3mV, (c) \text{ CH: } V_w = 70mV,$   |    |

|     | $V_r = 145mV$ , $V_{au} = 120mV$ , $V_{ad} = 50mV$ , (d) IB: $V_w = 80mV$ , |    |

|     | $V_r = 130mV, V_{au} = 120mV, V_{ad} = 3mV,$ (e) FS: $V_w = 80mV,$          |    |

|     | $V_r=135mV,V_{au}=280mV,V_{ad}=3mV,({\rm f})$ input current $I_{in}$        | 38 |

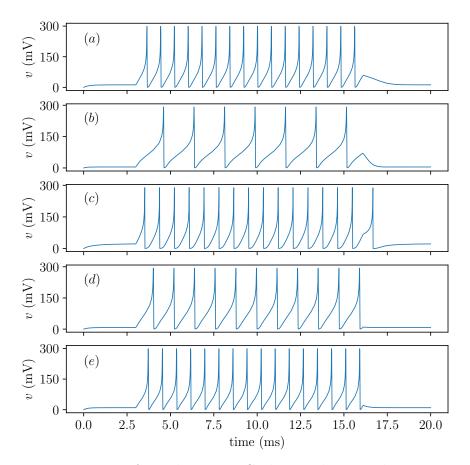

| 4.3 | Spiking pattern when spiking threshold, refractory period and               |    |

|     | spike width changes (a) $V_{th} = 30mV$ , $V_w = 80mV$ , $V_r = 80mV$ ,     |    |

|     | (b) $V_{th} = 50mV$ , $V_w = 80mV$ , $V_r = 80mV$ , (c) $V_{th} = 70mV$ ,   |    |

|     | $V_w = 80mV, V_r = 80mV, (d) V_{th} = 70mV, V_w = 80mV,$                    |    |

|     | $V_r = 30mV$ , (e) $V_{th} = 70mV$ , $V_w = 170mV$ , $V_r = 30mV$ , (f)     |    |

|     | Input current $I_{in}$                                                      | 40 |

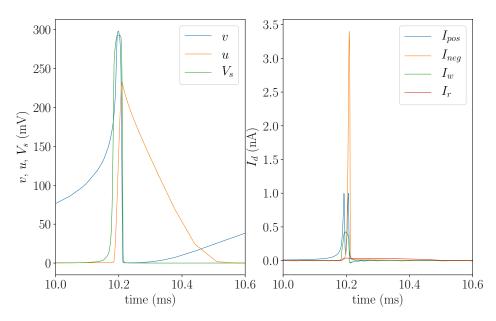

| 4.4 | Close up view of voltage and drain current spike traces. Current            |    |

|     | spikes at the time of membrane voltage spike                                | 41 |

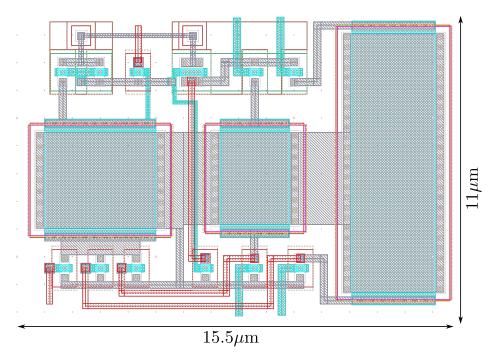

| 4.5 | Layout of the proposed neuron circuit. Most of the area is taken                     |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | by the capacitors                                                                    | 43 |

| 4.6 | Few runs from the Monte Carlo sampling simulation. Due to device                     |    |

|     | mismatch frequency of spike is affected                                              | 44 |

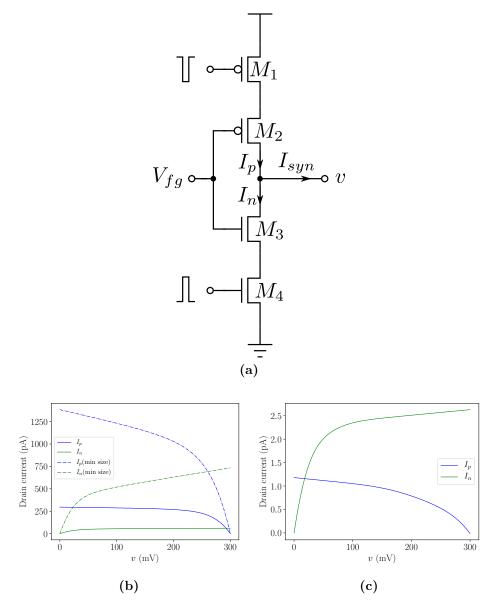

| 5.1 | Synapse circuit and currents. All the transistors are of size                        |    |

|     | $260 \text{nm} \times 260 \text{nm}$ . (a) synaptic current from a single synapse is |    |

|     | $I_{syn} = I_p - I_n$ , (b) active synapse current at $V_{fg} = 100 \text{mV}$ for   |    |

|     | both the proposed design and a synapse using minimum-sized                           |    |

|     | transistors, (c) inactive synapse current at $V_{fg}$ =100mV. Even                   |    |

|     | though the synapse is inactive there is substantial current that acts                |    |

|     | as inhibitory current. This current scales up as more synapses are                   |    |

|     | added                                                                                | 48 |

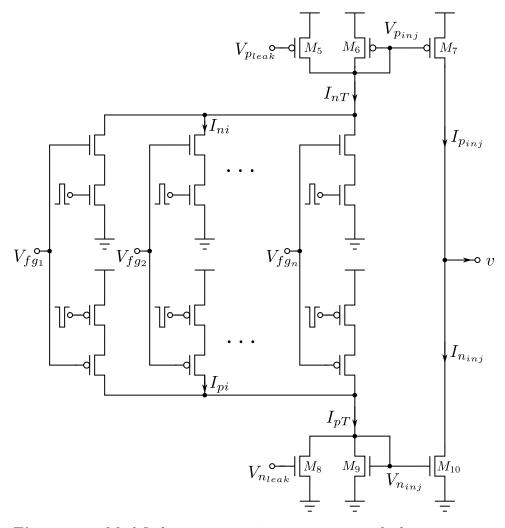

| 5.2 | Modified synapse circuit to compensate leakage currents                              | 50 |

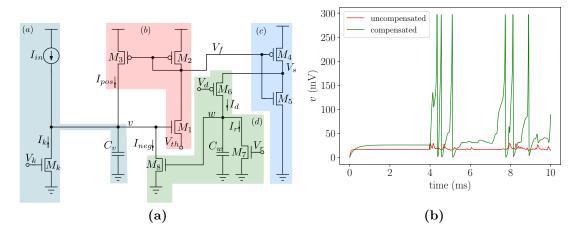

| 5.3 | (a) The neuron circuit used in the experiment, (b) comparison of                     |    |

|     | neuron membrane potential with leakage compensated synapses                          |    |

|     | vs uncompensated synapses. With uncompensated synapses, the                          |    |

|     | membrane potential barely increased by a pre-synaptic spike.                         |    |

|     | Weights and inputs are same in both compensated and uncom-                           |    |

|     | pensated cases                                                                       | 52 |

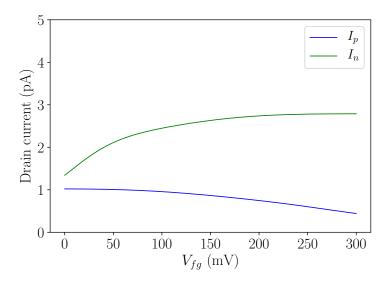

| 5.4 | Inactive synapse leakage current dependence on $V_{fg}$ . The currents               |    |

|     | are shown for $v=150\text{mV}$ as $V_{fg}$ is varied                                 | 54 |

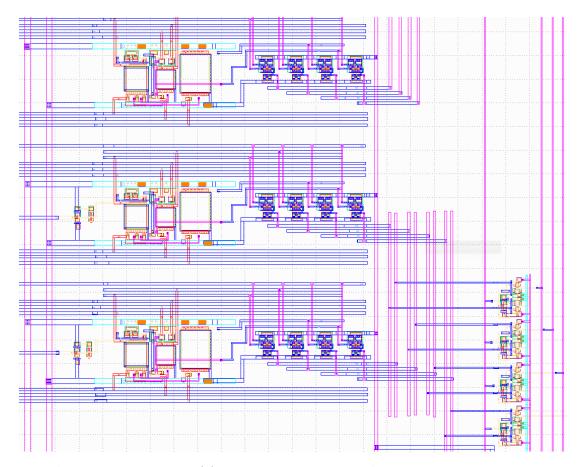

| 5.5 | Layout of frew neuron circuits with measurement circuitry                            | 55 |

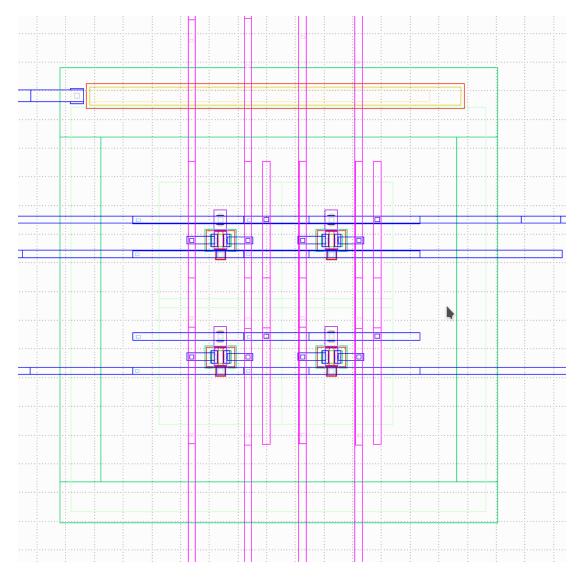

| 5.6 | A $4 \times 4$ sonos cell array                                                      | 56 |

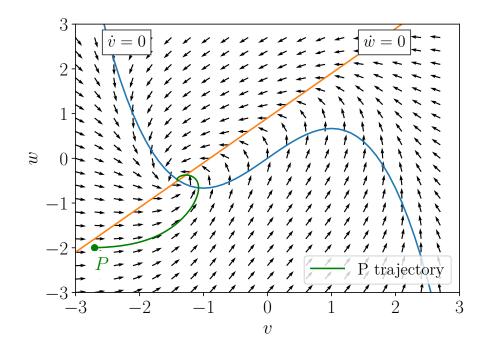

| 6.1 | Phase plane and nullclines of FHN model for $\epsilon = 1.25, a = 0.9,$              |    |

|     | b=1,I=0. Velocities are scaled to unit value. The trajectory of                      |    |

|     | point $P$ moves in the direction of arrows                                           | 61 |

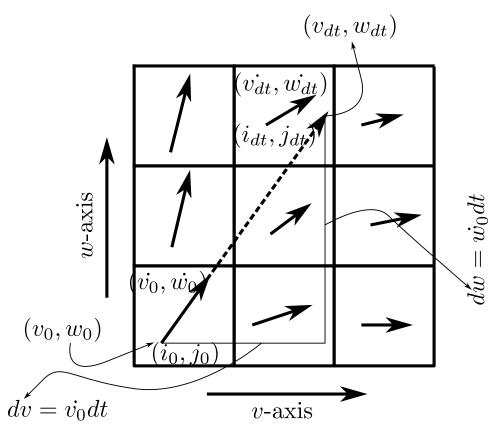

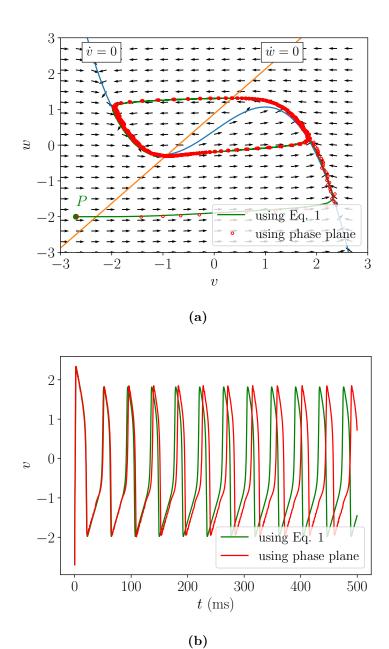

| 6.2  | ODE solving using phase plane meshgrid. Dotted line shows jump                                     |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | of initial point over time step $dt$                                                               | 62 |

| 6.3  | (a) Trajectory of point $P=(-2.7,-2.0)$ and (b) time domain                                        |    |

|      | solution obtained by solving ODE using phase plane and Eq. 6.1.                                    |    |

|      | FHN model parameters: $\epsilon = 0.08, a = 0.7, b = 0.8, I = 2.$                                  |    |

|      | Meshgrid step size is 0.1 on both axis                                                             | 63 |

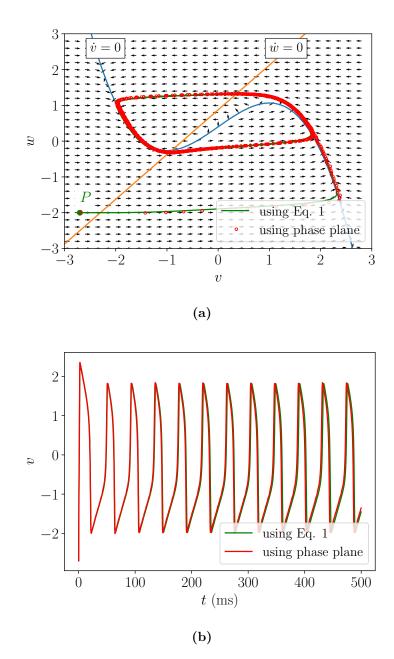

| 6.4  | (a) Trajectory of a point $P=(-2.7,-2.0)$ and (b) time domain                                      |    |

|      | solution obtained by solving ODE using phase plane and Eq. 6.1.                                    |    |

|      | FHN model parameters: $\epsilon = 0.08, \ a = 0.7, \ b = 0.8, \ I = 2.$                            |    |

|      | Meshgrid step size is 0.05 on both axis                                                            | 64 |

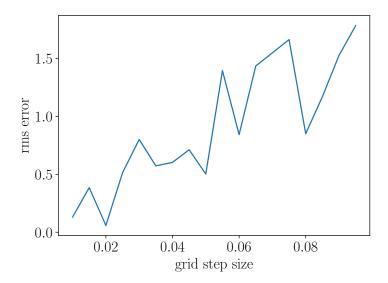

| 6.5  | root mean squared error variation of phase plane solution with the                                 |    |

|      | solution from equations as meshgrid step size varies                                               | 65 |

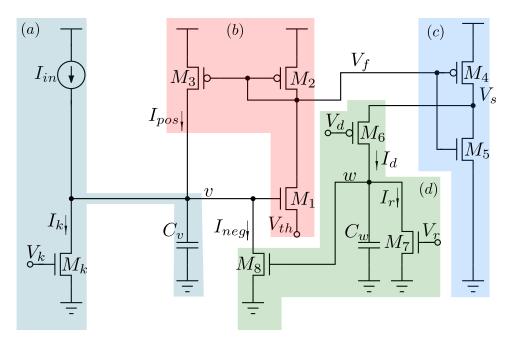

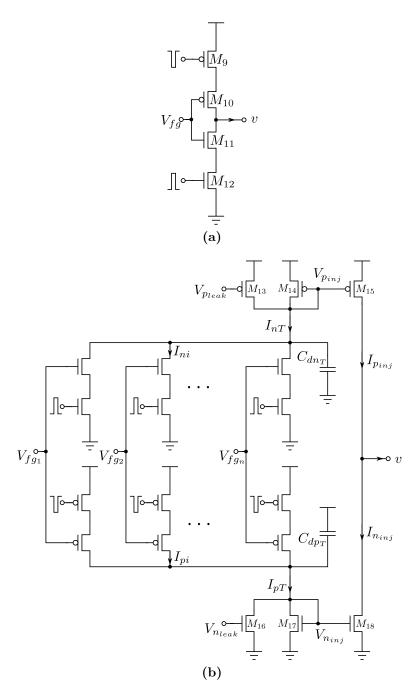

| 6.6  | Silicon neuron circuit [2]. For $M_{1-3,5-8}$ W/L = 260nm/260nm, For                               |    |

|      | $M_4 \text{ W/L} = 800 \text{nm} / 260 \text{nm}, C_v = 50 \text{fF}, C_u = 30 \text{fF}$          | 67 |

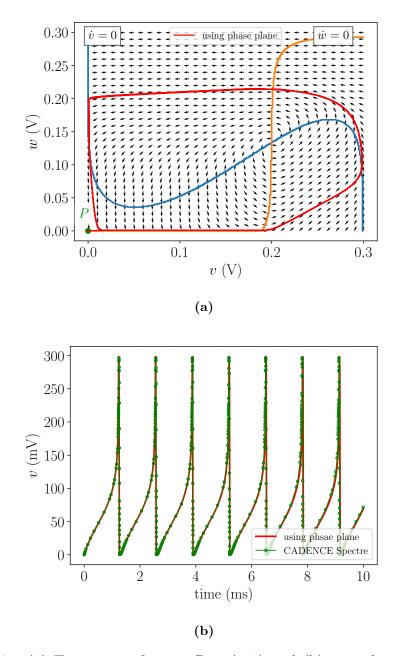

| 6.7  | (a) Trajectory of point $P=(0,0)$ and (b) time domain solution                                     |    |

|      | obtained by solving ODE using phase plane for $I_{in}=6\mathrm{pA}$ and time                       |    |

|      | domain membrane voltage trace. Voltage settings: $V_{dd} = 300 \text{mV}$ ,                        |    |

|      | $V_k = 10 \text{mV}, V_{th} = 50 \text{mV}, V_d = 80 \text{mV}, V_r = 100 \text{mV}$ and capacitor |    |

|      | values: $C_v = 50 \text{fF}, C_w = 30 \text{fF}, C_p = 5 \text{fF}$                                | 70 |

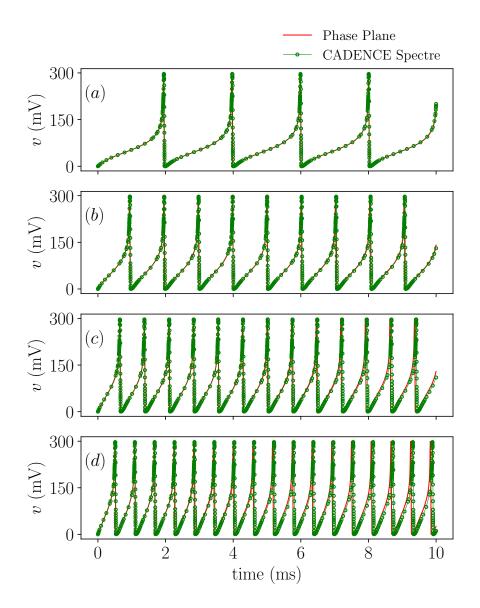

| 6.8  | Phase plane solution and Cadence spectre solution for (a) $I_{in} =$                               |    |

|      | 4pA, (b) $I_{in} = 8pA$ , (c) $I_{in} = 12pA$ , (d) $I_{in} = 16pA$                                | 71 |

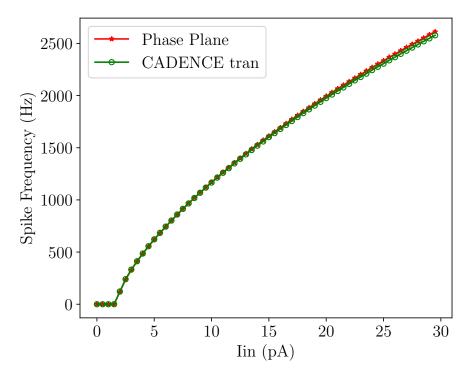

| 6.9  | Frequency vs input current curve of the neuron circuit                                             | 72 |

| 6.10 | (a) Synapse circuit (b) Synapse bundle circuit to eliminate leakage                                |    |

|      | current. Every transistor has size $W/L = 260 nm/260 nm$                                           | 74 |

| 6.11 | Circuits used for generating synapse meshgrids                                                     | 76 |

| 6.12 | Neural network topology                                                                            | 77 |

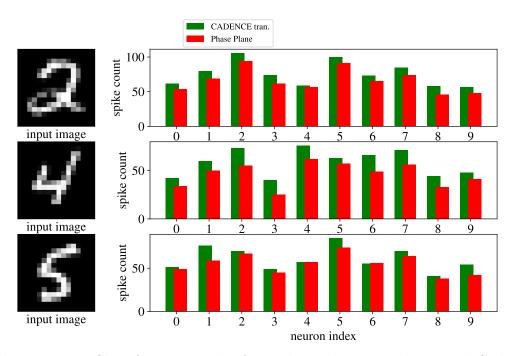

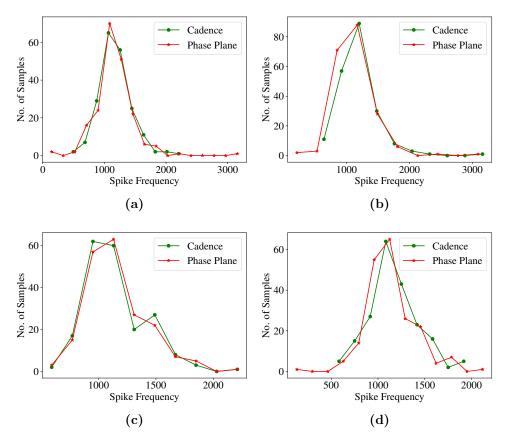

| 6.13 | Classification results from phase plane simulation and Cadence           |

|------|--------------------------------------------------------------------------|

|      | spectre transient simulation of the network. Three examples are          |

|      | shown. Spike counts at the network output are closely reproduced         |

|      | in the phase plane simulation. Variation of the spike count at the       |

|      | network output are also reproduced                                       |

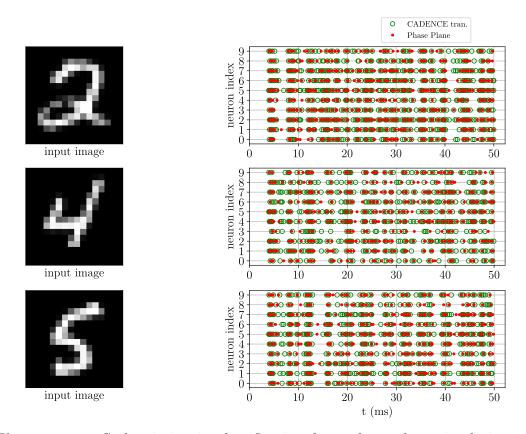

| 6.14 | Spike timing in classification from phase plane simulation and           |

|      | Cadence spectre transient simulation of the network. Three               |

|      | examples are shown. Spike timing and spike clusters are closely          |

|      | reproduced                                                               |

| 6.15 | Comparison of Monte-Carlo simulation on neuron spiking fre-              |

|      | quency. Histogram results are obtained by applying process               |

|      | variation to devices as: (a) Including all devices (b) Excluding         |

|      | $M_8$ (c) Excluding $M_6$ (d) Excluding $M_7$                            |

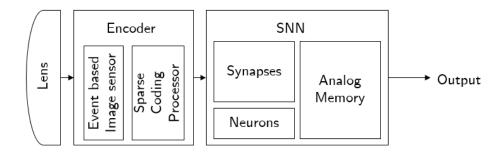

| 7.1  | A neuromorphic image sensor processing pipeline 83                       |

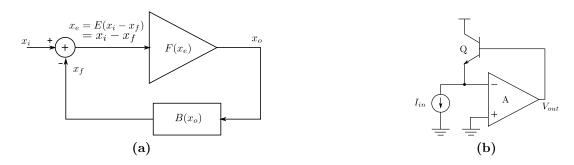

| A.1  | (a) A generic negative feedback system (b) An Operational                |

|      | amplifier with an exponential element in the feedback path               |

|      | realizes a logarithmic input-output function. The transistor Q has       |

|      | exponential voltage to current relationship. The feedback system         |

|      | implements inverse of the exponential i.e. logarithmic function 100      |

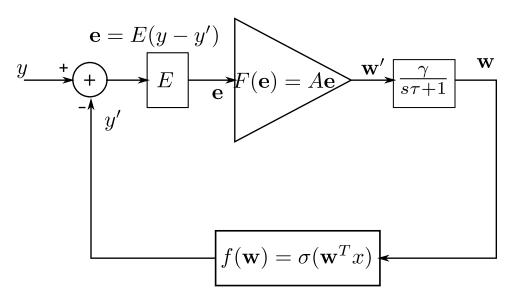

| A.2  | A negative feedback system as optimizer for machine learning system. 102 |

| A.3  | Backpropagating the difference vector to previous layers 106             |

| A.4  | SAR ADC as supervised learning system                                    |

#### Glossary

ANN Artificial Neural Network

CNN Convolutional Neural Network

MPW Multi Project Wafer. This is a way to share a silicon wafer

for different designs. It allows individuals to submit their chip

designs for fabrication without having to buy the whole wafer.

PDK Process Development Kit. This is a collection of silicon

foundry model files which is provided by the fabrication

foundry. The PDK contains the models required for circuit

simulation. It also contains the design rules for layout.

RF Receptive Field

Skywater The name of the PDK that Google is using for open source

chip fabrication

SNN Spiking Neural Network

#### Chapter 1

#### Introduction

When it comes to designing low power, compact devices and systems, biological systems offer exciting inspiration that the engineering community can benefit from. Using biologically relevant devices, algorithms and models to solve machine learning tasks is commonly known as neuromorphic engineering. Neuromorphic computing has recently emerged as a promising alternative to von Neumann systems. In von Neumann systems, memory and computation are separate. A central processing unit is responsible for controlling the memory and computation. This architecture is based on a central clock, which executes instructions in a serial manner. As Moore's law is expected to come to an end, von Neumann-based computing systems will eventually not be able to meet the computational demand in the future. Tremendous amounts of data are being generated every day, which needs to be processed using artificially intelligent machines. Processing such vast amount data also means a greater demand on the power consuption and computing power.

On the other hand, analog computing techniques offer better power efficiency [3] compared to digital computing techniques. As a result, many neuromorphic systems [4, 5, 6] are based on analog computation techniques. On top of that, neuromorphic systems are highly parallel in nature. They also colocate memory and processing, which has the promise of overcoming the von

Neumann bottleneck [7]. A large amount of power is required to move data in and out of memory than it takes for actual computation, which is known as the von Neumann bottleneck. Instead of separating memory from computation, memory can be placed close to the computation in order to minimize data movement. This memory colocation is inspired by biology. As a result, neuromorphic engineering has become a common name in the field of machine learning.

Traditional artificial neural networks (ANN) use neurons that operate on continuous values. On the other hand, operations in neuromophic computing systems use spiking neurons where computation is based on spike events. Spiking neural networks (SNN) have emerged as a promising candidate for the next generation of neural networks [8]. Neurons in ANNs are rate-code-based models where continuous valued inputs are weighted and summed, after which a nonlinear function is applied to produce neuron output. However, in SNNs, spike events are integrated over time and an output event spike is generated when the integrated value crosses a threshold. A spiking neuron in an SNN is biologically plausible. Moreover, because of the neurons' event based nature, it is more energy efficient. There are also significant differences between the learning methods of ANNs and SNNs. Most SNNs are trained with biologically plausible learning rules such as Hebbian learning [9], spike timing dependent plasticity (STDP) learning rule [10] etc. whereas ANNs are trained using backpropagation rule [11].

#### 1.1 Motivation

Recently, machine learning on the edge has become a very popular and practical concept [12]. There are several reasons for this popularity.

• Machine learning at the edge enables processing the data in real time. For offline processing, the data needs to be collected and then sent to the cloud

servers or data processing stations. Directly processing data at the place of data collection removes a significant overhead and processing time. Critical technologies such as autonomous vehicles and medical devices can greatly benefit from real time machine learning at the edge.

• Sending data from sensor devices to cloud servers potentially presents a security risk. Cloud servers store sensitive personal user information, which is subject to adversarial attacks. By performing machine learning locally at the edge, the data storage and hence any security risk are eliminated.

There are several design considerations for machine learning on edge devices. The computing power and memory resources of the edge device are extremely limited. A typical edge sensor, for example an environmental sound detector or cough detector for biomedical data acquisition, has to operate on very limited power. These kinds of devices are typically run by coin cell batteries. If the power cost of computation is high, then the battery would run out very quickly. Furthermore, a wearable biomedical sensor has to be very compact in size. This puts a limit on the computing devices, battery size, and also the memory constraints available on board the device. Thus, edge machine learning in application specific integrated circuits (ASIC) is a very challenging task. SNN offers many desirable properties which edge machine learning can benefit from. SNNs are inherently event based systems which can provide energy efficient and robust decision making. Using the properties of biologically motivated spiking neural networks, I can develop machine learning systems that are capable of operating under strict energy and memory constraints.

#### 1.2 Proposed Contributions

To meet the challenges of machine learning on the edge, I study and explore the following domains.

- Develop memory efficient approximate computing algorithms: Sparse coding is a biologically inspired unsupervised learning algorithm that potentially explains the sparse activity of the biological brain. As an engineering approach to reduce power consumption, sparse coding is gaining more and more interest. Moreover, it can be used as a feature discovery layer [13] of a convolutional neural network (CNN). Recently, a spiking version of sparse coding called SAILNet [14] has been proposed. SAILNet is particularly attractive because the learning rules are biologically plausible. Hence, a sparse coding algorithm such as SAILNet might become an important preprocessing step in spike based information processing systems. A memory-efficient version of the SAILNet algorithm is required for deployment in edge devices. I propose a modification [15] to the algorithm which reduces the memory footprint of the coding algorithm.

- Design compact ultra low power neuron circuit for neuromorphic systems: In order to pave the way for energy efficient intelligent edge devices based on spiking neurons, ultra low power SNN components are needed. The neuron is one key component in an SNN. For the neuron circuit an ultra low power, compact analog spiking neuron [16] in 130nm CMOS technology is presented in chapter 4.

- Mitigation of Leakage current in Synaptic Array: Analog circuits suffer from the problem of leakage current. For synaptic circuits, this leakage current presents a problem in the steady state response of the neuron. A technique for mitigating the leakage current and synaptic circuit array

design is presented [17] in chapter 5. The synaptic array is designed using 130nm CMOS technology.

• Develop simulation techniques to account for hardware nonidealities: For custom analog circuit based SNN implementation, it is necessary to perform spice simulation in order to verify the expected functionality and effect of hardware non idealities. Simulation of SNNs is time consuming. Simulating an SNN in a spice simulator is even more time consuming. Even a smallsized SNN (e.g. two layer fully connected network with 100 and 10 neurons) takes 8 hours of simulation time in Cadence spectre. As a result, it makes more sense to simulate the network in an SNN simulator, adjust the network parameters and then do the final spice simulation. However, existing SNN simulators cannot take into account hardware non idealities. Analog circuits are subject to noise and device mismatch. For custom analog circuit implementation, it is necessary to incorporate device hardware nonidealities into the machine learning model so that the model can mimic performance when they are deployed in real hardware. In chapter 6, I propose a method [18] to simulate SNN that can take into account hardware non idealities and provide very close simulation output as the spice based simulator.

#### 1.3 Reprint Permissions of Previously Published Materials

This dissertation contains materials from articles that I published previously. Reprint permission has been obtained from the corresponding publishers for the copyrighted materials. Proper copyright notices have been given in the references as directed by the publishers in entries [15, 16, 17, 18].

#### Chapter 2

#### Fundamentals of Neuromorphic Engineering

The concept of brain-inspired machines has existed since the beginning of computer engineering. Both von Neumann [19] and Turing [20] discussed machines and the brain in the 1950's. However, Dr. Carver Mead was the first scientist who recognized the similarity between the silicon electronic circuits and the biological nervous system [21]. He coined the term neuromorphic computing in 1990. The physics of the operation of a biological neuron makes use of the exponential function of the Boltzmann distribution. The Boltzmann distribution is also utilized in the operation of a silicon transistor. The nervous system operates under various constraints, such as limited energy, the presence of noise etc. Silicon electronic systems also operate under such constraints. Dr. Mead argued that it should be possible to emulate the architecture of nervous system and computational principles in silicon electronic circuits and achieve robust information processing power similar to the biological nervous system.

If we compare the processing power of a biological nervous system with digital computing systems, we see that biological systems are more efficient by many orders of magnitude. It is estimated that a human brain performs synaptic computations on the order of  $3.6 \times 10^{15}$  operations per second [3] while consuming only 12W of power. This is such an extreme computational efficiency that no

supercomputer will be able to match. Below I provide an overview of biological computing components and their neuromorphic models.

#### 2.1 Biological Spiking Neuron

A typical neuron cell is shown in Fig. 2.1. The cell is functionally divided into three sections. The dendrites, the cell body and the axon. The axon acts as the output signal branch of the neuron. The dendrites act as the input signal branch of the neuron where axons from other neurons connect. The structure of the dendrites looks like tree branches with leaf-like structures called spines. The overall structure of the neuron resembles the structure of a tree with branches, roots and trunk. When a neuron wants to talk to other neuron it forms a connection between axon of one neuron to the dendrite of other neuron. The connection between an axon and a dendrite is called a synapse. The synapse mostly forms between an axonal branch and the dendritic spine. Sometimes a synapse can form between an axon and the cell body as well.

#### 2.1.1 Neuron Operation

Neurons are essentially electrical devices. When communicating to other neurons, the neuron sends a voltage spike called an action potential as an output down the axon. The membrane potential of a neuron is always stated with respect to the outside. At steady state the inside of the cell is more negative than the outside. Typically, the membrane potential inside the cell is -70mV with respect to the outside at steady state. This is called the resting potential. When the neuron receives an input action potential at the dendrite, the membrane potential can either become more negative (polarize) or more positive (depolarize) than the resting potential. If the membrane potential becomes depolarized, the input

**Figure 2.1:** General structure of a biological neuron. Bottom-right image: microscopic image of a dendrite from which spines branch off. (Image courtesy: Queensland Brain Institute, Alan Woodruff; De Roo et. al. [1] / CC BY-SA 3.0 via Commons)

action potential is said to be excitatory. Likewise, if the membrane potential becomes polarized, the input action potential is said to be inhibitory. How much the membrane potential will polarize or depolarize depends on the strength of the synapse. As the input action potential comes in, the membrane potential changes. When the membrane potential reaches a threshold voltage, typically around -50mV, the membrane potential abruptly increases to a value around

**Figure 2.2:** Generation of action potential in a biological neuron. Left: qualitative depiction of action potential generation. Right: membrane voltage trace recorded from an actual neuron in a mouse's cortex. (Image courtesy: Queensland Brain Institute)

+20mV and then immediately falls down below threshold as shown in Fig. 2.2. This pulse of membrane potential is called an action potential which travels down the axon. The action potential is also simply referred to as *spike*. The spike typically has an amplitude of 100mV and a duration of 1ms. A chain of action potentials from a neuron is called spike train. Spikes are the fundamental units of communication between neurons.

The description above presents a qualitative description of how neurons work. In reality, the operation of neuron involves complex interaction of charge-carrying ions  $(Na^+, K^+, Cl^-, Ca^+)$  and neurotransmitters (dopamin, glutamate, acetylcholin etc.). Fig. 2.3 shows a typical structure of a synapse. The neuron sending the signal is called a presynaptic neuron, and the neuron receiving the signal is called a postsynaptic neuron. When the spike reaches the presynaptic terminal, it causes voltage-gated ion channels to open, releasing the neurotransmitter in the synaptic cleft. The transmitters then bind to the receptors on the dendrite of the postsynaptic neuron. Depending on the type of neurotransmitter, the receptors cause positive or negative ion currents to flow

**Figure 2.3:** Spike, causes neurotransmitters to be released across the synaptic cleft, causing an electrical signal in the postsynaptic neuron. (Image courtesy: Queensland Brain Institute)

across the cell membrane. This ion current is accumulated on the membrane, which causes the membrane potential to increase or decrease.

When the membrane potential reaches the spiking threshold, a rush of  $Na^+$  influx current causes a rapid increase of the membrane potential as shown in Fig. 2.4. Then immediately  $Na^+$  influx current stops and K+ current flows out of the cell, thereby repolarizing the cell. This rapid rise and subsequent fall is called a spike. When a neuron generates a spike, it cannot be stopped by any inhibitory inputs. If the input current is insufficient to depolarize the membrane potential to the threshold voltage, no spike will fire. After generating a spike, the membrane potential goes below the resting potential to a voltage called the reset potential. This phase is called hyperpolarization. From the reset potential, the membrane potential reaches the resting potential again. It is very difficult to make the neuron generate another spike in the time period between the hyperpolarization and the resting state. This period is called the refractory period of the neuron.

Figure 2.4: Shape of an action potential. (Image courtesy: molecular devices)

#### 2.2 Spiking Neuron Models

The first mathematical model for a neuron was provided by Hodgekin and Huxley [22] in 1952 which eventually led to the Nobel Prize in 1963. The neuron model accounted for the detailed dynamics of ion channels. This is very useful from the neuroscientific point of view but, at the same time, computationally expensive, which does not provide any insight into the computational power of a neuron. As a result, a simplified model of the neuron is needed, which captures the behavior of the neuron without the detailed dynamics of the ion channels. For engineering and computational purposes, the neural dynamics can be conceived as an input current charging a capacitor combined with a mechanism that triggers action potential above a critical voltage. Below, I describe two dominant classes of neuron models in the literature.

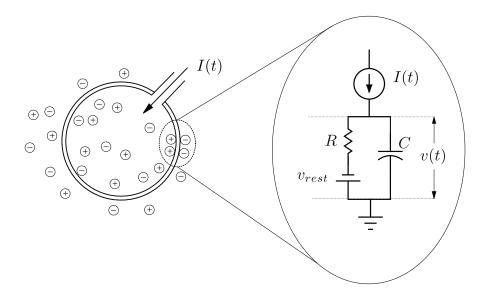

Figure 2.5: Modeling the neuron cell membrane by electrical circuit.

#### 2.2.1 One dimensional Leaky Integrate and Fire Model

Neuron models where action potentials are described as events are called Integrate-and-Fire models. The shape of an action potential is not important because information is contained in the presence or absence of a spike. Integrate-and-fire models have two separate components that are both necessary to define their dynamics: first, an equation that describes the evolution of the membrane potential; and second, a mechanism to generate spikes. Fig. 2.5 shows the electrical equivalent circuit of the neuron cell membrane. The cell membrane acts like a capacitor C which can accumulate charge. The resistor R provides a path to leak the current out of the cell, which accounts for the imperfect insulator of the cell membrane. The voltage source  $v_{rest}$  allows the circuit to settle at resting voltage at steady steady state. The membrane potential is represented by v(t). The input current I(t) is split between the resistive current  $I_R$  and capacitive current  $I_C$  branches. The mathematical description is shown in (2.1).

$$I(t) = I_R + I_C \tag{2.1a}$$

$$I(t) = \frac{v(t) - v_{rest}}{R} + C\frac{dv(t)}{dt}$$

(2.1b)

$$\tau_m \frac{v(t)}{dt} = -(v(t) - v_{rest}) + RI(t)$$

(2.1c)

Here,  $\tau_m = RC$  is the time constant of the differential equation. From the mathematical analysis of the electrical circuit, it can be seen that the neuron membrane potential can essentially be described as a linear differential equation. From the electrical engineering point of view, the model equation is a leaky integrator. In addition, a criterion is required to generate the spike. Whenever, the membrane potential v(t) reaches or exceeds a given threshold  $\theta$ , a spike is generated as a Dirac delta function as output of the neuron. The membrane potential is subsequently reset to a reset potential  $v_r$ . Whenever a spike is generated as output, the neuron is said to have fired a spike. The firing time is labeled as  $t^{(f)}$ . The firing mechanism is formally expressed as (2.2).

$$t^{(f)}: v(t) > \theta \tag{2.2a}$$

$$\lim_{\delta \to 0; \delta > 0} v(t^{(f)} + \delta) = v_r \tag{2.2b}$$

After a neuron has fired a spike, the dynamics again follows (2.1). When a neuron i fires multiple times, the spikes can be labeled as  $t_i^{(f)}$  where  $f = 1, 2, \cdots$  denote the label of spikes. The spike trains can be expressed as a sum of Dirac delta functions as in (2.3).

$$S_i(t) = \sum_f \delta(t - t_i^{(f)}) \tag{2.3}$$

#### 2.2.2 Two or More Dimensional Model

There is another form of neuron model which integrates the mechanism of upward stroke of spike generation into the model itself. One example of this type of model is Izhikevich [23] model. In this type of model, the dynamics of the membrane potential is tailored with functions to generate the spike. In addition to the membrane potential, another variable is used called the recovery variable or slow variable in order to balance the disturbance in the membrane potential caused by the spike. The membrane potential is also termed as fast variable. The two-dimensional model consisting of the fast and a slow variable is given by (2.4).

$$\frac{dv}{dt} = \frac{1}{C} \{ k(v - v_r)(v - v_t) - u + I \}$$

(2.4a)

$$\frac{du}{dt} = a\{b(v - v_r) - u\} \tag{2.4b}$$

$$(v, u) \leftarrow (c, u + d)$$

if  $v \ge v_{peak}$  (2.4c)

Here, C is membrane capacitance,  $k, v_r, v_t, a, b, c, d, v_{peak}$  are modeling parameters, I is input current. When the membrane potential reaches a predefined peak potential  $v_{peak}$  the time is recorded as firing time  $t^{(f)}$  and the dynamics is reset by setting the membrane potential v to a reset potential v and the recovery variable v to v

#### 2.3 Information Encoding

The actual mechanism of how information is encoded by a spiking neuron and how computation is performed is still unknown. Experimental evidence points to different forms of encoding mechanisms. In general, the hypothesis of information encoding can be broadly categorized as *neuron based* and *population*

based encoding. There is support for both kinds of hypothesis. However, the universally accepted method of neural encoding is a subject of debate. There are different coding mechanisms in these broad categories. A discussion of these mechanisms is necessary from a neuromorphic perspective. Depending on the hardware, algorithm, and application, one method of encoding may be preferable over the other.

#### 2.3.1 Neuron Based Encoding

In this encoding mechanism, each neuron is believed to encode a numerical value or a representation in its spike. This idea of a single neuron representing a single piece of information is hypothesized from the notion of grandmother cell [24]. The idea is that there is a single neuron that becomes active when a person sees their grandmother. In other words, a single neuron encapsulates the representation of the person's grandmother. This way different neurons in the nervous system represent different ideas or concepts. The strength of the ideas or concepts could be represented by spike rates or spike timings.

#### **Rate Coding**

Rate coding hypothesis assumes that the information is represented by the firing rate or the number of spikes over a period of time of a neuron [25]. An example of a rate code based neuron is the motor neuron in the peripheral nervous system. A muscle's contraction is controlled by the number of spikes coming onto the muscle in a short time window. The greater the number of spikes, the greater the contraction. In this regard, the spike rate can be thought of as representing numerical values.

#### **Temporal Coding**

In a given time window, a neuron can emit some spikes in quick succession and be silent, whereas another neuron can emit the same number of spikes in that window. In both cases, the spike rate is the same, but the neuron has all of the spikes bunched together near the start of the window. In this case, the spike timing is important. In temporal coding, the latency of the spike firing can encode information. An example of temporal code is the early auditory system, where spike timing is used to localize sound [26].

#### 2.3.2 Population Based Encoding

Both rate codes and temporal codes describes encoding by individual neurons. The information can be encoded by the collective activity of a group of neurons as well. In this case, the representation is distributed across the activity of a population of neurons. An example of this coding is in the touch sensitive receptors on our skin. The more pressure is applied the more number of neurons are activated. This process of engaging more neurons as needed is called recruitment. Another form of population coding is to have individual neurons in the population to represent a part of the input. This way all of the neurons in the population can represent the whole input space. An example of this is the direction sensitive cells in the visual cortex. In a given cluster of neurons each neuron is tuned to respond to a particular direction of movement. This kind of population coding is also known as sparse coding.

#### 2.4 Learning in Spiking Models

The proper learning model and algorithm for training spiking neural networks is a major open question in neuromorphic engineering. The learning algorithm varies considerably depending on the network, neuron and synapse types. There is also the issue of whether to implement the training or learning on-chip or off-chip. A more fundamental issue is the lack of efficient training algorithms. Deep learning has enjoyed the use of backpropagation [11] in training neural networks. It has largely been successful in training different kinds of networks, such as feedforward and recurrent networks. Backpropagation uses gradient descent in the cost function landscape to reach a minimum error. There are many established and optimized tools available today that implement backpropagation Naturally, it makes sense to utilize these existing tools to train efficiently. spiking neural networks as well. However, backpropagation has not been equally successful in the spiking neural network domain for several reasons. backpropagation requires a continuous or piece-wise continuous differentiable function in order to create a smooth cost function landscape for gradient descent to work. Spiking neuron activation function is fundamentally discontinuous and thus non-differentiable in nature. As a result, backpropagation is not directly applied in the spiking domain. Second, backpropagation is not biologically plausible. There seems to be no evidence of a backpropagation-like mechanism happening in the brain. Learning in the brain is based on local synaptic activities. However, learning in backpropagation is non-local, meaning it needs synaptic activity from all the neurons in a layer in order to adjust the synaptic weight. Backpropagation also suffers from a weight transport problem, which means that the backward network needs access to the forward weight in order to calculate the gradients. Although, research has shown that techniques such as feedback alignment [27] have the potential to make backpropagation work using random backward weights, it does not achieve competitive performance for large networks. Despite problems with backpropagation, it is still the best tool available for supervised training for spiking networks with some relaxation in the spiking activation function. Below I briefly describe the current methods available for supervised and unsupervised training algorithms for spiking neural networks.

#### Supervised Learning

Backpropagation is the dominant method of supervised training in spiking neural networks. There are two ways backpropagation is applied to spiking neural networks. The first method is weight transfer method. In this method, first a traditional artificial neural network is trained using backpropagation. Then the artificial neural network is converted to a spiking neural network by replacing the traditional artificial neurons with spiking neurons. This type of conversion does not achieve comparable classification accuracy as the original network. Some weight optimization is required in order to bridge the accuracy gap by balancing weights and thresholds [28]. However, it still fails to reach comparable accuracy.

The second method is to directly apply backpropagation with some relaxation in the spiking activation function. Since, the spiking activation is non-differentiable, a differentiable approximation is used for training. After training is complete, the actual non-differentiable activation is used for inference. This technique is known as surrogate gradient [29, 30]. This technique also fails to achieve comparable accuracy compared to the equivalent artificial neural network. It requires a long inference time window to accumulate enough spikes for decision making. Time-varying parameters such as batch normalization through time [31] can be utilized to decrease the inference time window and accuracy gap.

#### Unsupervised Learning

Unlike its supervised counterpart, the spiking neural network enjoys biologically plausible unsupervised learning techniques. One of the earliest methods is known as *Hopfield network*. This type of network can memorize patterns in the network

dynamics and can retrieve the pattern back in the presence of noise. This type of network is often used to describe associative memory in the brain. Another type of method is called Spike Timing Dependent Plasticity (STDP) or better known as *Hebbian Rule*. In this rule, synaptic weight is increased if the postsynaptic neuron fires immediately after the firing of presynaptic neurons, and synaptic weight is decreased if the opposite happens. In popular terminology, it is known as the neurons that fire together wire together. This type of simple rule is quite powerful in finding underlying patterns and clusters in data [32].

#### 2.5 Discussion

There is still a significant amount of work to be done within the field of learning algorithms and low-power hardware for neuromorphic systems. In order to fully realize the benefits of neuromorphic hardware, a fundamental change in approach and underlying assumptions is necessary for the training method and encoding system. Algorithms such as backpropagation and associated network models were developed with the von Neumann architecture in mind. The spike system is fundamentally different from the von Neumann system. Using surrogate backpropagation with rate coding or temporal coding only tries to imitate the working process of a traditional aritifial neural network. Rate coding encodes numerical values for the input and output of the spiking neuron. A surrogate gradient allows a differentiable activation function for backpropagation to work. None of these methods utilize the underlying spiking hardware and biological training method. As a result, at best, this imitation-based spiking system is only capable of achieving similar performance as the corresponding traditional artificial neural network while achieving increased power efficiency. From an engineering perspective, this power efficiency is very attractive in edge computing and edge machine learning.

# Chapter 3

# Memory Efficient Sparse Coding

### 3.1 Introduction

The need for low power and energy efficient intelligent circuit has led electronic circuit designers to draw inspiration from biology [21]. Advancements made by neuroscience have helped shape machine learning techniques such as artificial neural network [33] and reinforcement learning. After the seminal work by Olhausen [34] on sparse coding, several algorithms hav been proposed [35, 36, 14] which inspired a hardware implementation of sparse coding [37, 38]. SAILNet [14] provides an algorithm that have local learning which is biologically plausible. However, in SAILNet the neurons threshold voltage is a learnable parameter. Different neurons in the same layer have different threshold voltages which requires more memory hardware.

In this chapter, I show that SAILNet can be modified to have the same threshold voltage across all the neurons and the feedback matrix can be collapsed into a vector. The resulting network can still reproduce the receptive fields (RFs) of V1 simple cells of visual cortex. The modified algorithm shows more sparsity of neuronal activity and still reconstructs input that image with reliable accuracy. The rest of the paper is organized as follows. First, I present our modification to the algorithm. Second, I show how the modified algorithm sparsity compares with

the original one. Third, I show how well the learned receptive fields represents the input stimuli by comparing the classification accuracy of reconstructed images in a convolutional neural network. Throughout the paper the modified algorithm is referred to as new network for simplicity.

## 3.2 Sparse Coding Algorithm

Sparse coding is based on the idea that an image I(x, y) can be represented as a linear superposition [34] of some basis functions  $\phi(x, y)$  as in Eq. 3.1.

$$I(x,y) = \sum_{i} n_i \phi_i(x,y) \tag{3.1}$$

where  $n_i$  is the coefficients corresponding to the basis  $\phi_i(x,y)$ . The basis functions are not necessarily orthogonal to each other. The basis functions are also overcomplete which means that number of basis functions are more than the total number of elements in I(x,y). The goal of sparse coding is to find a set of  $n_i$  to represent I(x,y) such that most of the values of  $n_i$  are zero. Which means that the image is represented by the activities of a small set of bases from the whole set of basis functions. In matrix form Eq. 3.1 can be expressed as  $I = \Phi N$ , where  $\Phi = [\phi_1 \phi_2 \cdots \phi_m]$  and  $N = [n_1 n_2 \cdots n_m]^T$ . Each column of  $\Phi$  is the flattened out from  $\phi_i(x,y)$ .

## 3.2.1 Network Design

Each basis function is represented by a spiking neuron. The activities of a neuron (number of spikes in a given period) represents the coefficients of the basis that the neuron represents. For sparse activity only a few neurons need to show activity and most of the other neurons need to be inactive. Lateral inhibition is a way to achieve this whereby the most active neuron prevents the other neurons

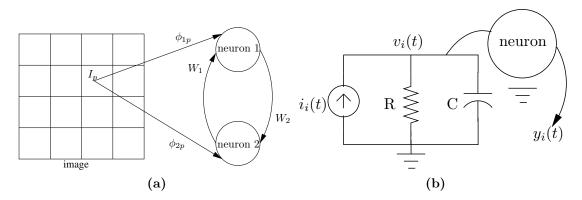

**Figure 3.1:** (a) Feed-forward, feedback and pixel connection (b) Integrate and fire neuron model.

from activating. Fig. 3.1 shows neuron connectivity. The input current for each neuron comprises of stimuli from pixel intensity values and activities of other neurons. The current in neuron i is as shown in Eq. 3.2.

$$i_i(t) = \frac{1}{R} (\sum_p \phi_{ip} I_p - W_i \sum_{i \neq j} y_j(t))$$

(3.2)

Here  $I_p$  is the image intensity value from pixel p, R is the membrane resistance.  $y_j(t)$  is neuron j output at time t.  $I_p$  and  $y_j$  act like voltages. If neuron j spikes at time t then  $y_j(t) = 1$ , else  $y_j(t) = 0$ .  $W_i$  is the lateral inhibitory connection strength between neuron i and other neurons. The  $i \neq j$  means the neuron does not inhibit itself. Unlike SAILNet or LCA where each neuron has M-1 inhibitory connections, here each neuron has one inhibitory connection that treats all incoming spikes from other neurons by same strength. The current changes the membrane potential  $v_i$  of neuron i according to the leaky integrate model given by the differential Eq. 3.3.

$$\tau \frac{dv_i(t)}{dt} = -v_i(t) + i_i(t)R \tag{3.3}$$

Here  $\tau=RC$  is the time constant, R is the membrane resistance, C is the membrane capacitance. When  $v_i$  reaches a certain threshold  $\theta$ , the neuron emits an action potential or spike. The output of each neuron is taken as number of spikes generated by the neuron,  $n_i = \sum_t y_i(t)$ , inside a fixed period of time following the stimulus presentation to the network. For simulation this period of time is taken as  $5\tau$  similar to [14]. For simulations in this chapter the network is taken as two times overcomplete. Input image size is chosen as  $16 \times 16 = 256$  pixels. Hence the number of neurons for two times overcomplete is  $2 \times 256 = 512$ .

**Figure 3.2:** 190 randomly selected RFs out of 512 RFs learned using the rules in Eq. 3.6. Each of the RF is  $16 \times 16$  size. Simulation settings:  $\tau = 1$  unit,  $\theta = 2$ . Learning rate used in learning these RFs:  $\alpha = 0.1$ ,  $\beta = 0.01$ .

## 3.2.2 Learning Rules

The learning rules are formed from the constrained optimization imposed on the network. First of all, the network activity must be able to reconstruct the input stimulus. From Eq. 3.1 the reconstructed pixel value is  $\bar{I}_p = \sum_i n_i \phi_{ip}$ . The mean squared error between the input and the reconstruction,  $\sum_p (I_p - \sum_i n_i \phi_{ip})^2$ ,

should be minimized. Secondly, the network activity has to be sparse i.e. only few neurons should produce spikes. If neuron i is active then other neurons should be ideally inactive if the input stimulus can be represented by only the activity of neuron i. Hence, the product  $n_i \sum_{i \neq j} n_j$  should be zero or close to zero. This also helps to ensure that the activity minimizes  $L_0$  norm. Using the Lagrange multiplier I can form the Lagrange function.

$$\mathcal{L} = \frac{1}{2} \sum_{p} (I_p - \sum_{i} n_i \phi_{ip})^2 - \sum_{i} W_i (n_i \sum_{i \neq j} n_j)$$

(3.4)

Here the inhibitory connection strength  $W_i$  for neuron i serves as the Lagrange multiplier. To minimize  $\mathcal{L}$  I perform gradient descent with respect to  $\phi_{ip}$  and  $W_i$ .

$$\Delta W_i = -\alpha \frac{\partial \mathcal{L}}{\partial W_i} = \alpha n_i \sum_{i \neq j} n_j$$

(3.5a)

$$\Delta \phi_{ip} = -\beta \frac{\partial \mathcal{L}}{\partial \phi_{ip}} = \beta n_i (I_p - \sum_j n_j \phi_{jp})$$

$$= \beta(n_i I_p - n_i^2 \phi_{ip} - n_i \sum_{i \neq j} n_j \phi_{jp})$$

(3.5b)

Here  $\alpha$  and  $\beta$  are learning rates. Learning rule from Eq. 3.5b is non local i.e. neuron i needs to know neuron activities from neuron j in the last term. But I notice that if network activity is sparse, only one neuron is active and others are inactive. So on average the  $n_i \sum_{i \neq j} n_j$  product should be zero. Hence, I can ignore the last term of Eq. 3.5b and thus the rule becomes local. The rule from Eq. 3.5a is local because  $W_i$  connects neuron i to other neurons and it needs activities  $n_i$  and  $\sum_{i \neq j} n_j$  which is local to  $W_i$ . The final learning rule as average

of batch process can summarized as follows.

$$\Delta W_i = \alpha \langle n_i \sum_{i \neq j} n_j \rangle$$

$$\Delta \phi_{ip} = \beta \langle (n_i I_p - n_i^2 \phi_{ip}) \rangle$$

$$= \beta (\langle n_i I_p \rangle - \langle n_i^2 \rangle \phi_{ip})$$

(3.6)

The  $\phi$  learning rule looks similar to SAILNet learning rule. But the assumptions made to arrive at these rules are different from those imposed in SAILNet. The threshold voltage is fixed for all the neurons here. For SAILNet the threshold voltage is also a learnable parameter.

## 3.2.3 Learned RFs

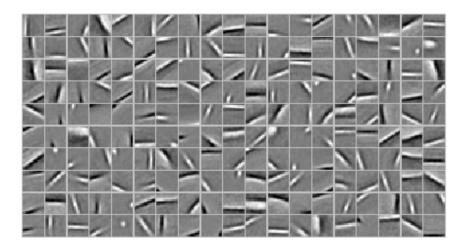

Training images to learn the basis functions/RFs are taken from natural image set of Olshausen and Field [34]. There are ten  $512 \times 512$  images of natural scenes available preprocessed by zero-phase lowpass filter described in [34]. W is set to zero and  $\Phi$  is set to random values before training as in [14]. Threshold voltage  $\theta$  is set to a value of 2. Batches of 100 images each of size  $16 \times 16$  with zero mean and unit standard deviation are selected randomly from the images in the database and presented to the network. Number of spikes generated from the neurons are counted over  $5\tau$  unit of time after the images are presented. With those spike counts W and  $\Phi$  are updated using the rules of Eq. 3.6. This process is repeated until a stable solution is reached. Fig. 3.2 shows some of the RFs obtained after training. The RFs are spatially localized, oriented and selective to structures like edges. These are the properties of RFs of mammalian primary visual cortex and looks similar to RFs recorded from V1 simple cells of macaque monkey [39].

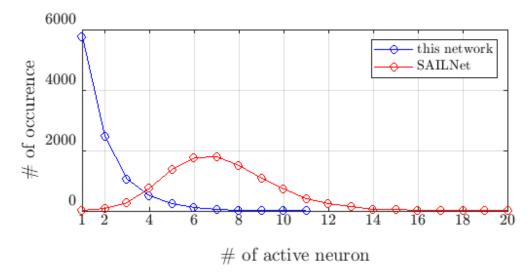

Figure 3.3: Sparsity histogram: sparsity is indicated by a  $16 \times 16$  image patch being represented by small number of active neurons most of the time an image patch is presented to the network.

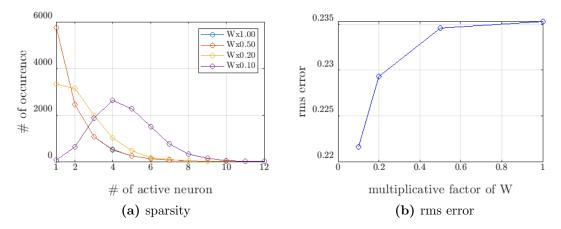

# 3.3 Sparsity of Activities

Here I compare the sparsity of the learned network with the sparsity of SAILNet. SAILNet was learned using the parameters provided in [14]. All ten images from the database are fed to both of the networks.  $16 \times 16$  image patches are taken from the database images and number of spikes are counted in a  $5\tau$  unit time window. Each image is  $512 \times 512$ , hence with  $16 \times 16$  image patches there are 1024 patches from one image and 10240 patches from all ten images. If I count the number of neurons with non-zero spike counts after each image patch presentation and plot them in a histogram I get a comparison of sparsity. Fig. 3.3 shows the result. The new network learning rules produced only one active neuron most of the time a  $16 \times 16$  image patch is presented. Out of 10240 image patches around 4800 patches, almost 47% of the time, a  $16 \times 16$  image patch is represented by only one neuron activity. Compared to that SAILNet produces seven active neurons most of the time a  $16 \times 16$  image patch is presented. The new network is clearly

Figure 3.4: Reconstruction error comparison.

more sparse than SAILNet. This is because of the learning rule of Eq. 3.5a which encourages one neuron to be active.

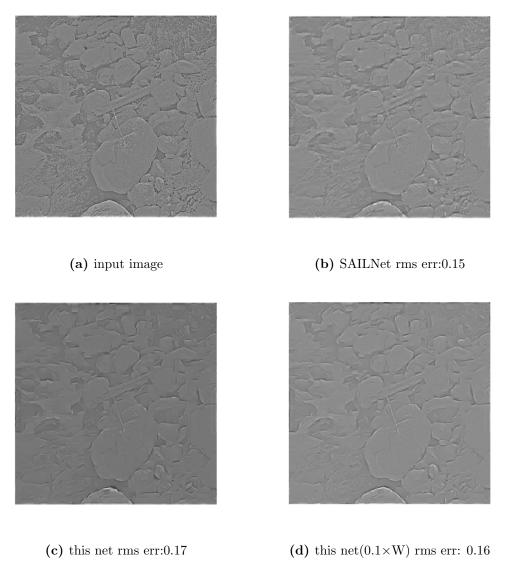

# 3.4 Reconstruction Accuracy

There is a trade off between sparsity of activity and accurate reconstruction. For accurate reconstruction of image from linear combination of basis functions, more than one basis functions are needed to reproduce fine details of input image. Since the new network has only one active neuron most of the time, the reconstruction error is slightly higher than SAILNet. Fig. 3.4 shows a reconstructed image along with rms errors for SAILNet and new network. The rms error is just slightly higher than that of SAILNet. This is expected because in new network sparsity is higher. If more accurate reconstruction is required, it can be achieved to some degree by tuning the value of W. If I reduce the inhibitory connection strengths, neurons will not have reduction of the membrane potential as much and more neurons will fire. Thus the network activity will get less sparse i.e. more than one neuron activity will represent the input stimulus most of the time. Fig. 3.4d shows such a reconstruction with inhibitory weights set to ten percent of learned inhibitory weights where network is less sparse and more details are visible. I am trading off activity sparsity for more accurate reconstruction. Fig. 3.5a shows how multiplying W with a factor less than one, changes sparsity for images in the dataset. As the inhibitory connection gets less stronger more neurons are active most of the time and the curve begins to look like SAILNet sparsity curve as in Fig. 3.3. As the sparsity is reduced by reducing values of W, the rms error also decreases as shown in Fig. 3.5b. These two figures clearly shows the trade off between sparsity and reconstruction accuracy.

### 3.5 Quality of RFs and Reconstruction

Although reconstruction error is slightly higher for the new network, to a human eye reconstructed images from SAILNet and new network looks similar as in

**Figure 3.5:** Sparsity and reconstruction rms error tuning by tuning the values of inhibitory connection strength.

Fig. 3.4. But would a computer vision program be able to tell if Fig. 3.4(b) and Fig. 3.4(c) are same and they are similar to Fig. 3.4(a)? To answer that question I devise an experiment. I feed reconstructed images to an image classifier and compare the classification error with the classification error of original images. If they are close then I can say that the reconstructed images have enough information for a computer be able to tell the difference. For this I train a [40] which has 17 classes convolutional neural network with flower dataset of flowers of each class with 80 images. This dataset is chosen because it is lightweight and has natural scene. Every image is resized to  $512 \times 512$  pixels. For convolutional neural network I choose ResNet-101 [33]. For training 80% and for testing 20% of the images from each class is used. Three testing image sets are made: first set with the original testing images, second set with the reconstructed images of the first set using SAILNet, third set with the reconstructed images of the first set using new algorithm. For reconstruction of the flowers, RFs learned in section 3.2.3 are used instead of learning them again on the flower database. The reason is that since those RFs are learned on natural images, they should be able to reproduce any other natural scenes. The flower images are color images but

**Table 3.1:** Classification Accuracy

| testing set               | accuracy |

|---------------------------|----------|

| original                  | 91.3%    |

| SAILNet reconstuction     | 86.2%    |

| new network reconstuction | 89.1%    |

the RFs are grayscale images. Hence, the reconstruction is done on R,G,B color channel separately. A reconstruction is shown in Fig. 3.6. Interestingly, the rms error for flower dataset turned out to be less than SAILNet while maintaining more sparsity. Using the three sets of testing images classification accuracy is measured. The result is shown in table 3.1. The classification accuracies for the reconstructed images are not too far from accuracy of original images. This proves that RFs can faithfully retain information for a convolutional neural network to be able classify. The classification accuracy of the new network turned out to be higher than SAILNet. I think this is because the details discarded by the new sparse coding network was helpful for the convolutional neural network for this dataset.

**Figure 3.6:** Reconstruction images and rms error for one of the images from flower datadset. W matrix is unaltered for reconstruction.

## 3.6 Computation and Hardware Complexity

Since a neuron does not inhibit itself, in SAILNet or LCA each neuron needs M-1feedback weights. For M neurons the feedback needs an  $M \times (M-1)$  vector matrix multiplier. With N elements in each input, feed-forward computation needs an  $N \times M$  vector matrix multiplier. In SAILNet there are also M threshold voltages. So total memory needed for SAILNet is  $NM + M(M-1) + M = NM + M^2$ . But in the modified algorithm each neuron has one feedback weight and it does not have different threshold for each neuron. Hence the memory requirement is NM+M. This is a huge savings in memory and associated circuits for hardware implementation. The vector matrix multiplication of  $M \times (M-1)$  elements is reduced to M multiplication which can save power as well. In [38] SAILNet was implemented in 65nm digital process. It takes significant fraction of the total power for data movement from memory. In [37] LCA was implemented using analog floating gate memory. It takes considerable amount of time to fix the floating gate voltages to appropriate values. Reducing number of feedback weights and removing neuron threshold as stored memory parameter can help both digital and analog implementation of sparse coding to reduce computation and speed up operation.

### 3.7 Conclusion

In this chapter, I present a modification of the sparse coding algorithm, SAILNet, that reduces the number of learnable parameters without significantly affecting the reconstruction error and still reproduce the RFs of V1. Our experiments show that the modified algorithm is more sparse but can reproduce the input signal with necessary information for it to be identified by a convolutional neural network. Although there is a trade off between sparsity and rms error,

this reduced memory algorithm can be useful for processes which can tolerate inaccuracies in data to a certain level.

# Chapter 4

# Compact Ultra Low Power Spiking Neuron Circuit

### 4.1 Introduction

Brain inspired neuromorphic systems use biologically plausible spiking neurons to model intelligent systems like silicon retina, cochlea and machine learning systems [41, 42, 43]. Simulation of large scale spiking neural networks in a traditional von-Neumann type digital system is not suitable because of the asynchronous nature of spiking neurons. Highly parallel nature of neuromorphic hardware makes them faster, which has led to their recently increasing popularity [44]. However, very large scale simulations of neural networks in hardware become power hungry. Hence, efforts went into designing biologically plausible spiking neuron circuits [45] with behaviors, such as adaptation and bursting while restricting power consumption of individual neurons.

While many designs implement a broad range of spiking behaviours [46], the circuits operate in strong inversion and consume high power. Other designs use subthreshold circuits [43], but they require many transistors. In this chapter I propose a leaky integrate and fire neuron that uses subthreshold device physics to implement neuron functionality, which allows us to reduce number of transistors. The circuit elements draw current only when the neuron is spiking and not at other times. The power consumption at spike time is very small. The neuron is

capable of showing complex behaviour like adaptation and bursting while using only a handful of transistors. I have used a 130nm silicon CMOS process for simulation in cadence spectre.

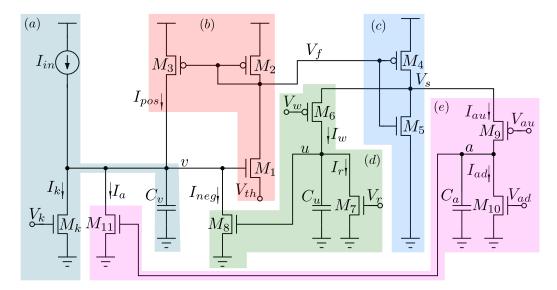

## 4.2 Neuron Circuit

The circuit is shown in Fig. 4.1. The circuit consists of five sub blocks. Block a with  $I_{in}$  and  $M_k$  serves as input excitation to the membrane capacitor  $C_v$ . Block b with  $M_{1-3}$  performs thresholding and spike generation. Block c with  $M_{4-5}$  acts as the axon which generates a voltage pulse at each spike. Block d with  $M_{6-8}$  controls spike width, refractory period and resets the neuron after a spike. Block e with  $M_{9-11}$  controls adaptation and bursting. The main firing and resetting dynamics are governed by (4.1) and (4.2)

$$C_v \frac{dv}{dt} = I_{in} - I_k + I_{pos} - I_{neg} - I_a \tag{4.1}$$

$$C_u \frac{du}{dt} = I_w - I_r \tag{4.2}$$

The neuron has 12 transistors that operate in the subthreshold regime. The body of all the nFETs are grounded, and the body of all the pFETs are connected to the positive supply. The circuit has multiple levels of control over the neuron operation. It can control spiking threshold, spike width, refractory period and adaptation period.

### 4.3 Circuit operation

The circuit operation is described below as a step by step process.

**Step 1:** Input current  $I_{in}$  acts as excitatory current to the neuron. The leak transistor  $M_k$  subtracts some current  $I_k$  from  $I_{in}$  using  $V_k$ . Hence, the total input

**Figure 4.1:** Proposed neuron circuit (a) Input block, (b)  $M_{1-3}$  for thresholding and spike generation, (c)  $M_{4-5}$  for axon, (d)  $M_{6-8}$  for reset and spike width, refractory control, (e)  $M_{9-11}$  for adaptation and bursting control.

current going into the membrane capacitor  $C_v$  is  $I_{in} - I_k$ . By controlling  $I_{in}$  and  $V_k$  input current to the neuron can be made excitatory or inhibitory. The net excitatory input current charges up the membrane capacitor  $C_v$ , and membrane voltage v increases.

Step 2: Membrane voltage v is applied to the gate of  $M_1$ . Once the gate voltage of  $M_1$  increases above the source voltage  $V_{th}$  which acts as spiking threshold,  $M_1$  starts to conduct current. This current is copied using  $M_{2-3}$  and fed back into membrane capacitor  $C_v$  thus implementing positive feedback current  $I_{pos}$ . The current through  $M_1$  can become very large if the top rail voltage is large. Here, the top rail voltage is low which limits the maximum current through  $M_1$  and consequently limits the power consumption for a spike. Since  $M_1$  is operating in the subthreshold regime, the current produced is exponentially related to the gate voltage. When v exceeds threshold  $V_{th}$ , this exponential positive feedback current raises v very quickly until v reaches the top voltage rail  $V_{dd}$ .

Step 3: As long as v is higher than  $V_{th}$ ,  $M_1$  conducts current and  $V_f$  drops below  $V_{dd}$ . The axon block is essentially an inverter. Hence,  $V_s$  goes up and reaches  $V_{dd}$ . The current through an inverter can be very high when both  $M_4$  and  $M_5$  are conducting. But in this case  $V_{dd}$  is low, which limits the current. As  $V_s$  goes up, capacitor  $C_u$  charges through  $M_6$  and increases voltage u. The speed of charging  $C_u$  can be controlled via  $V_w$ . Once u becomes high enough to produce a current though  $M_8$  such that  $I_{neg}$  overpowers  $I_{pos}$ ,  $C_v$  discharges, axon output  $V_s$  goes to ground and the neuron resets. Using  $V_r$  in  $M_7$ ,  $C_u$  can be discharged slowly so that voltage u can continue to produce high enough  $I_{neg}$  that the input current cannot charge  $C_v$ . This implements the refractory period. Once the refractory period is over the neuron starts the operation again if there is still any input current. By controlling the charging time of  $C_u$  using  $V_w$  the spike width can be controlled. Transistors attached to  $C_v$  implement the membrane resistance.

Spike frequency adaptation is accomplished by reducing the input current to membrane capacitor. With every spike axon output,  $V_s$  reaches  $V_{dd}$  which charges capacitor  $C_a$  slowly using  $M_9$ . The slight increase in voltage a causes  $M_{11}$  to conduct current  $I_a$  and leak some input current.  $V_{au}$  and  $V_{ad}$  controls the charging and discharging of  $C_a$ . By selecting proper values of the control voltages  $V_w$ ,  $V_r$ ,  $V_{au}$ ,  $V_{ad}$ , a wide range of spiking patterns can be achieved. The transistor sizing and capacitor values are given in Table 4.1. Individual transistors are very small in size except  $M_4$ , which is slightly larger than the others because it has to supply current to block d and e. The only large size capacitor is  $C_a$ , which controls adaptation and bursting.

**Table 4.1:** Transistor size, capacitor and supply voltage values

| $M_4~{ m W/L}$  | Other FET W/L   | $C_v$ | $C_u$ | $C_a$  | $V_{dd}$          |

|-----------------|-----------------|-------|-------|--------|-------------------|

| 800 nm / 260 nm | 260 nm / 260 nm | 50 fF | 30 fF | 100 fF | $300 \mathrm{mV}$ |

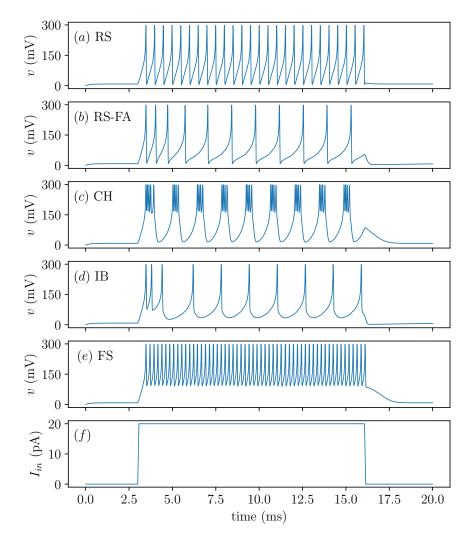

## 4.4 Spike patterns