# PV-BATTERY SERIES INTEGRATION FOR RESIDENTIAL SOLAR-PLUS-STORAGE SYSTEMS

by

# Namwon Kim

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2022

| Арр | proved by:       |

|-----|------------------|

| Dr. | Babak Parkhideh  |

| Dr. | Badrul Chowdhury |

| Dr. | Robert Cox       |

| Dr. | Maciej Noras     |

# ABSTRACT

NAMWON KIM. Pv-battery series integration for residential solar-plus-storage systems. (Under the direction of DR. BABAK PARKHIDEH)

Solar-plus-storage systems provide efficient energy yield and management, resilience, and more revenue to residential houses and buildings. In solar-plus-storage systems, power electronics converters are integral components to generate the maximum output power from a solar photovoltaic (PV) array, store the generated energy into a battery, and finally deliver and manage the power to an electric load or the electric grid. Many existing solar-plus-storage systems still use and combine legacy power electronics converter topologies initially designed for a solar PV generation system or a battery energy storage system (BESS) separately. These power converters are connected in parallel to an AC or DC point of common coupling: AC-parallel and DC-parallel integration methods. Another integration method of a solar-plus-storage system is connecting a high-voltage battery to the high-voltage DC bus in parallel in a solar PV generation system having two-stages power converter architecture: In-line integration method. These methods result in increased costs and size, lower energy yields due to the increased number of power electronics converters, and the requirement of high-voltage PV strings and batteries.

This research studies new PV-battery integration methods and PV-battery series optimizers—power electronics converters optimally designed for different residential solar-plus-storage systems. The two PV-battery integration methods are proposed: AC-series integration and DC-series integration. The proposed integration methods are based on the series connection of PV and battery modules. The AC-series integration method assists the residential panel-level series-connected solar PV inverters in reducing the intermittent PV output fluctuations with a low-voltage-profile battery energy storage inverter. The DC-series integration enables PV voltage support,

reducing the number of power converter stages, reducing the rated power of power converters, improving the system round-trip efficiency, and seamless source integration. Three PV-battery series optimizers are proposed for different solar-plus-storage applications. The proposed power converter topologies and controls are discussed in this dissertation. Off-line simulation, real-time controller hardware-in-the-loop simulation, and lab-scale experiment results are included and analyzed to demonstrate the operating and design principle and the control performance of the proposed system.

# DEDICATION

Dedicated to my wife, my parents, my brother, and my family.

# ACKNOWLEDGEMENTS

I would like to express my deepest appreciation and respect to my advisor, Dr. Babak Parkhideh, for his continuous support and advice on my Ph.D. research and all academic work that I have accomplished at the University of North Carolina at Charlotte (UNC Charlotte). I also would like to acknowledge my dissertation committees, Dr. Badrul Chowdhury, Dr. Robert Cox, and Dr. Maciej Noras, for their invaluable feedback, suggestions, and advice on my dissertation work.

I would like to acknowledge the Department of Electrical and Computer Engineering and the Energy Production and Infrastructure Center (EPIC) at UNC Charlotte for all education, teaching, and research opportunities that helped me build my knowledge and experience in many different aspects including Power Electronics. This background has allowed me to conduct and complete my Ph.D. research. I also would like to acknowledge the Graduate School and the International Student and Scholar Office at UNC Charlotte for all the academic support that helped me continue my Ph.D. research without interruptions, even during this challenging pandemic.

I would like to sincerely thank my lab mates and coworkers at UNC Charlotte—Dr. Mehrdad Biglarbegian, Mr. Chondon Roy, Dr. Hamidreza Jafarian, Dr. Iman Mazhari, Dr. Shahriar Nibir, Mr. Hossein Niakan, Mr. Ali Parsa Sirat, Mr. James Gafford, Dr. Daniel Evans, and Mr. Andrew LeClair—for their collaboration. I also would like to acknowledge our PowerAmerica team at UNC Charlotte and Dr. Madhu Chinthavali and his research team at ORNL for their support in the projects.

# TABLE OF CONTENTS

| LIST OF TABLE  | SS .                                                                        | >   |

|----------------|-----------------------------------------------------------------------------|-----|

| LIST OF FIGUR  | ES                                                                          | X   |

| LIST OF ABBRE  | EVIATIONS                                                                   | xiv |

| CHAPTER 1: IN  | TRODUCTION                                                                  | 1   |

| 1.1. Motivati  | ion                                                                         | 1   |

| 1.2. Literatu  | re Review                                                                   | Ş   |

| 1.3. Propose   | d Solutions                                                                 | 6   |

| 1.4. Organiza  | ation of Dissertation                                                       | 8   |

| OF AN AC-S     | CONTROL AND OPERATING RANGE ANALYSIS STACKED PV INVERTER ARCHITECTURE INTE- | 10  |

| 2.1. Introduc  | etion                                                                       | 10  |

| 2.2. PV-Batt   | tery AC-Stacked Inverter Architecture                                       | 12  |

| 2.2.1.         | Proposed PV-battery AC-stacked inverter architecture                        | 12  |

| 2.2.2.         | Interactive operation between inverter members                              | 14  |

| 2.3. Decentra  | alized Ramp-Rate Control Strategy                                           | 15  |

| 2.4. Results   | and Discussions                                                             | 18  |

| 2.4.1.         | Interactive operation between PV and ESS inverters                          | 19  |

| 2.4.2.         | Decentralized ramp-rate control                                             | 21  |

| 2.4.3.         | Operating range of the decentralized ramp-rate control                      | 23  |

| 2.5. Conclusi  | ion                                                                         | 25  |

| 2.6. Reference | ces                                                                         | 26  |

|          |            |                                                                                                             | viii |

|----------|------------|-------------------------------------------------------------------------------------------------------------|------|

| A SOL    | AR INV     | ATTERY SERIES INVERTER ARCHITECTURE:<br>ERTER FOR SEAMLESS BATTERY INTEGRA-<br>ARTIAL-POWER DC-DC OPTIMIZER | 31   |

| 3.1. Int | troductio  | n                                                                                                           | 31   |

| 3.2. PV  | V-Battery  | Integration Strategy and System Architecture                                                                | 34   |

| 3.2      | 2.1. P     | V-only mode                                                                                                 | 35   |

| 3.2      | 2.2. P     | V-battery mode                                                                                              | 37   |

| 3.2      | 2.3. B     | attery-only mode                                                                                            | 39   |

| 3.3. Pr  | roposed P  | Power Electronics Topology and Control Strategy                                                             | 40   |

| 3.3      | 3.1. P     | V-only mode                                                                                                 | 41   |

| 3.3      | 3.2. P     | V-battery mode                                                                                              | 42   |

| 3.3      | 3.3. Ba    | attery-only mode                                                                                            | 42   |

| 3.4. Re  | esults and | l Discussions                                                                                               | 43   |

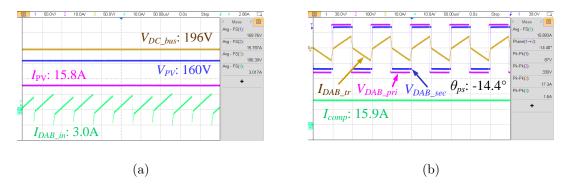

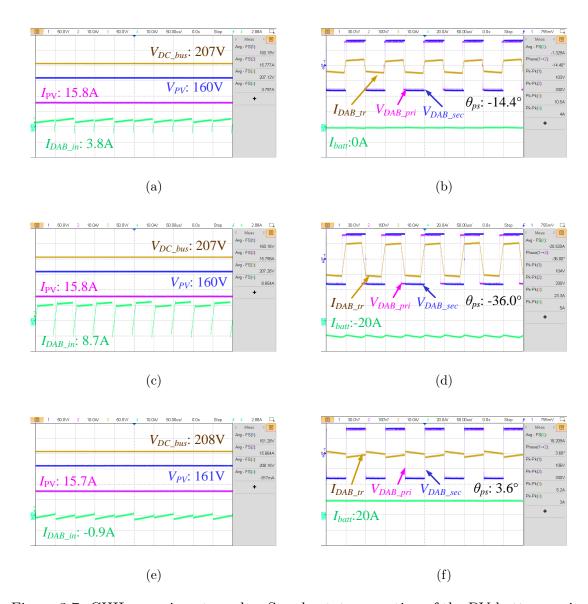

| 3.4      | 4.1. St    | seady-state operation                                                                                       | 45   |

| 3.4      | 4.2. Ti    | ransient operation                                                                                          | 48   |

| 3.5. Co  | onclusions | S                                                                                                           | 50   |

| 3.6. Re  | eferences  |                                                                                                             | 51   |

|          |            | ATTERY-SERIES DC-DC OPTIMIZER FOR REG-<br>MICROGRID APPLICATIONS                                            | 55   |

| 4.1. Int | troductio  | n                                                                                                           | 55   |

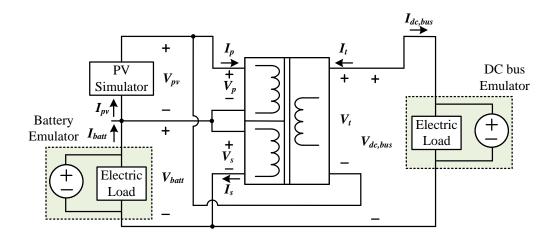

| 4.2. PV  | √-Battery  | y-Series DC-DC Optimizer                                                                                    | 59   |

| 4.2      | 2.1. D     | C-Series Integration for a Regulated DC Microgrid                                                           | 59   |

| 4.2      | 2.2. P     | V-Battery-Series DC-DC Optimizer                                                                            | 61   |

| 4.2      | 2.3. D     | C Analysis                                                                                                  | 64   |

|                                                                                                                                           | ix  |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

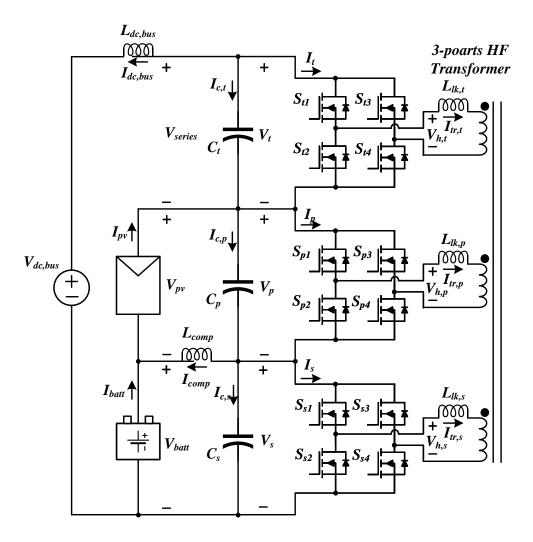

| 4.3. Converter Circuit and Design                                                                                                         | 67  |

| 4.3.1. HF Three-port Transformer                                                                                                          | 68  |

| 4.3.2. Filter Capacitors                                                                                                                  | 70  |

| 4.3.3. HF Ripple Attenuation Inductors                                                                                                    | 73  |

| 4.3.4. PV-Battery-Series Optimizer Design Parameters                                                                                      | 75  |

| 4.4. Closed-Loop Control and Simulation Results                                                                                           | 76  |

| 4.4.1. Closed-Loop Control                                                                                                                | 76  |

| 4.4.2. Simulation Results                                                                                                                 | 78  |

| 4.5. Experimental Results                                                                                                                 | 81  |

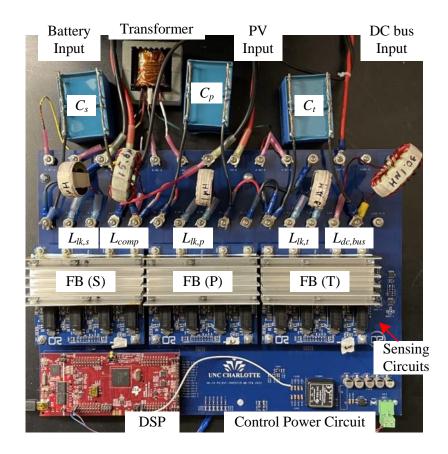

| 4.5.1. Hardware Prototype and Experimental Setup                                                                                          | 81  |

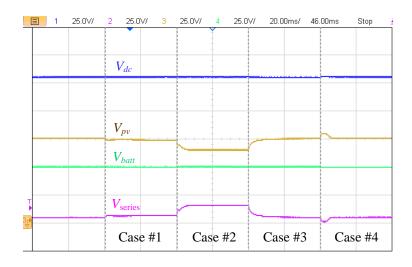

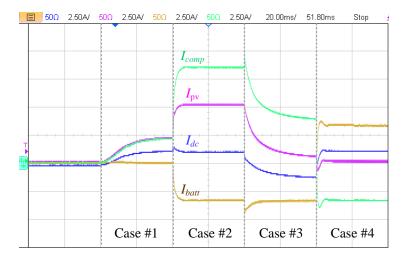

| 4.5.2. Experimental Results                                                                                                               | 84  |

| 4.6. Conclusion                                                                                                                           | 88  |

| 4.7. References                                                                                                                           | 89  |

| CHAPTER 5: CONCLUSION AND FUTURE WORK                                                                                                     | 92  |

| 5.1. Conclusion                                                                                                                           | 92  |

| 5.2. Future Work                                                                                                                          | 93  |

| REFERENCES                                                                                                                                | 95  |

| APPENDIX A: CONTROL AND OPERATING RANGE ANALYSIS OF AN AC-STACKED PV INVERTER ARCHITECTURE INTE-GRATED WITH A BATTERY                     | 99  |

| APPENDIX B: PV-BATTERY SERIES INVERTER ARCHITECTURE: A SOLAR INVERTER FOR SEAMLESS BATTERY INTEGRATION WITH PARTIAL-POWER DC-DC OPTIMIZER | 106 |

# LIST OF TABLES

| TABLE 2.1: DESIGN PROPERTIES OF THE PV-BATTERY ACSTACKED INVERTER                                                                           | 19 |

|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| TABLE 2.2: SUMMARY OF CHIL TEST RESULTS: PEAK MODULATION INDICES AND OPERATING MARGIN OF THE INVERTERS WITH DIFFERENT OPERATING CONDITIONS. | 20 |

| TABLE 2.3: SUMMARY OF CHIL TEST RESULTS: THE DRRC WITH DIFFERENT OPERATING CONDITIONS.                                                      | 22 |

| TABLE 3.1: SYSTEM PROPERTIES - A CASE STUDY OF THE PVBATTERY SERIES INVERTER ARCHITECTURE (1000 $W/m^2$ AND $25^{\circ}C$ )                 | 44 |

| TABLE 4.1: SYSTEM PARAMETERS                                                                                                                | 65 |

| TABLE 4.2: SYSTEM OPERATION CASES                                                                                                           | 66 |

| TABLE 4.3: SYSTEM COMPARISON                                                                                                                | 67 |

| TABLE 4.4: CONVERTER DESIGN PARAMETERS                                                                                                      | 76 |

| TABLE 4.5: CONVERTER PROTOTYPE PARAMETERS                                                                                                   | 84 |

| TABLE 4.6: EXPERIMETNAL RESULTS: VOLTAGE, CURRENT, POWER, EFFICIENCY OF THE PROTOTYPE SYSTEM AND CONVERTER                                  | 86 |

# LIST OF FIGURES

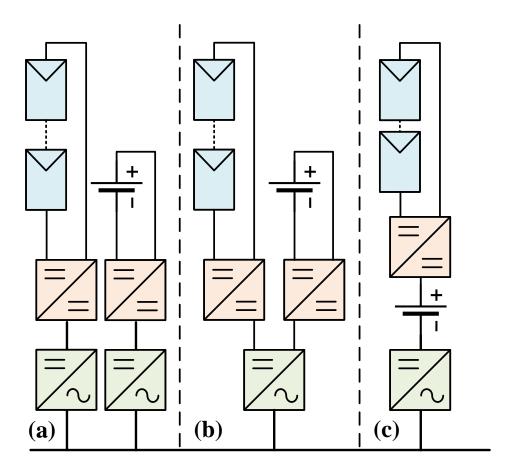

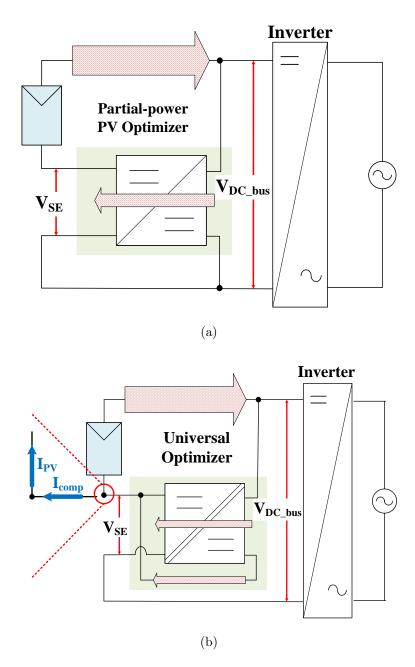

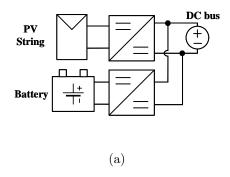

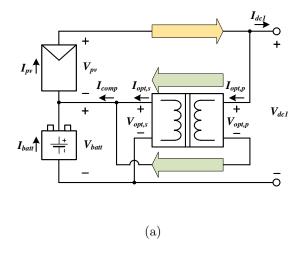

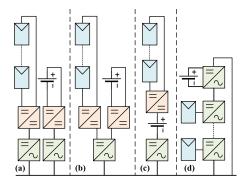

| FIGURE 1.1: State-of-the-art battery integration methods for grid-connected PV inverters in residential and commercial applications (a) AC-parallel integration, (b) DC-parallel integration, and (c) inline integration.                                                                                                                                                                                                                        | 2  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

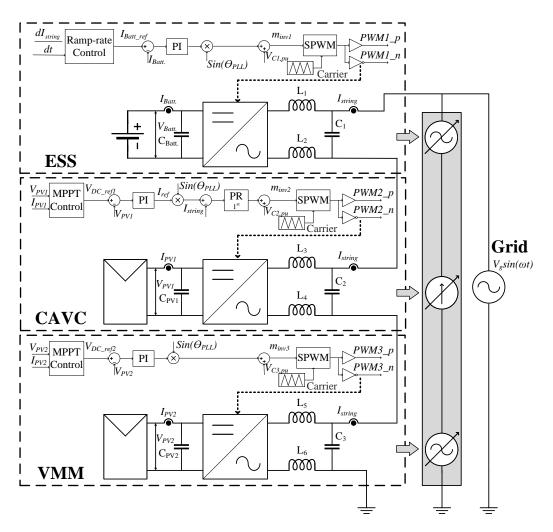

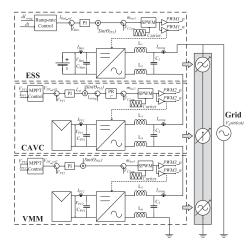

| FIGURE 2.1: PV-battery AC-stacked inverter architecture and control diagram.                                                                                                                                                                                                                                                                                                                                                                     | 13 |

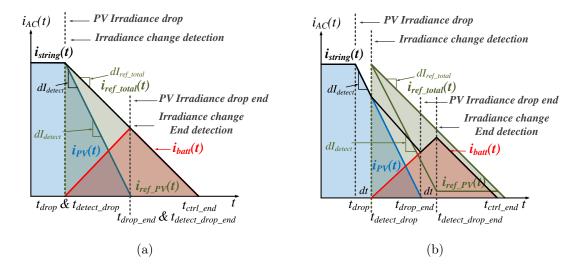

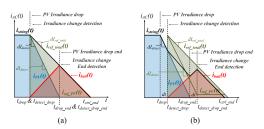

| FIGURE 2.2: Illustration of the DRRC algorithm (a) Ideal case: without detection delay and (b) Practical case: with detection delay.                                                                                                                                                                                                                                                                                                             | 16 |

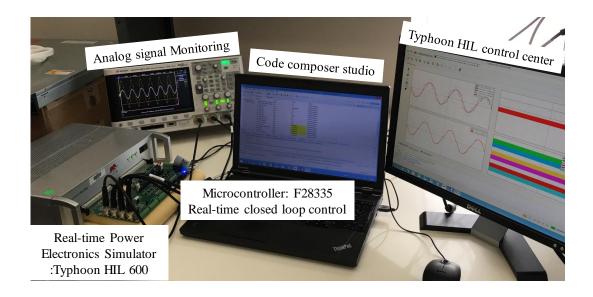

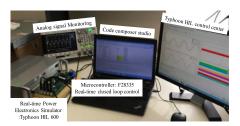

| FIGURE 2.3: CHIL set-up for testing PV-battery AC-stacked inverter system.                                                                                                                                                                                                                                                                                                                                                                       | 18 |

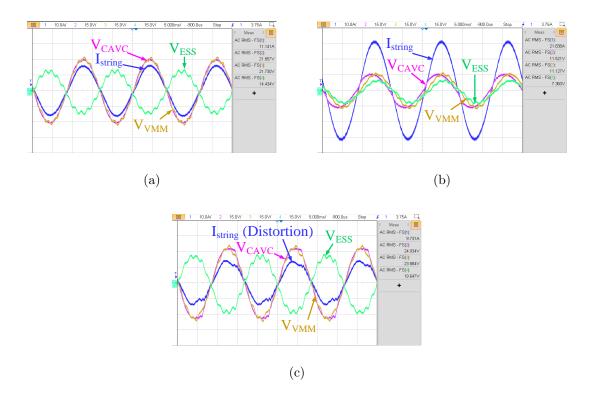

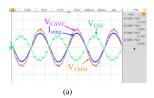

| FIGURE 2.4: Interactive operation of the inverters with battery operating conditions; $I_{string}$ : AC string current, $V_{CAVC}$ : CAVC AC voltage, $V_{VMM}$ : VMM AC voltage, and $V_{ESS}$ : ESS AC voltage, (a) charging mode (-4A), (b) discharging mode (4A), (c) charging mode (-4.8A)                                                                                                                                                  | 21 |

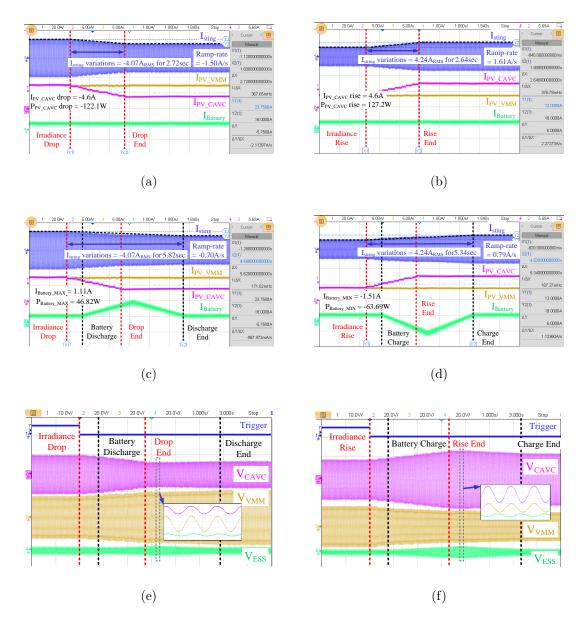

| FIGURE 2.5: DRRC: Asymmetrical irradiance changes on CAVC $(1000W/m^2 \leftrightarrow 500W/m^2)$ , Ramp-rate factor: 50%, (a) Without DRRC: Irradiance drop, inverter currents, (b) Without DRRC: Irradiance rise, inverter currents, (c) With DRRC: Irradiance drop, inverter currents, (d) With DRRC: Irradiance rise, inverter currents, (e) With DRRC: Irradiance drop, inverter voltages, (f) With DRRC: Irradiance rise, inverter voltages | 23 |

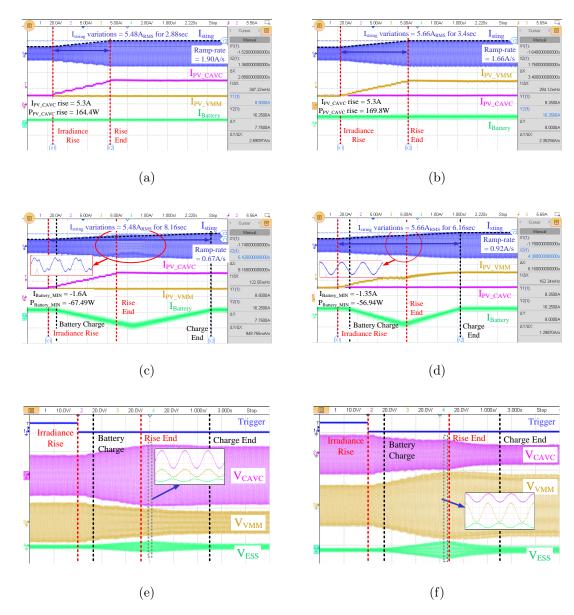

| FIGURE 2.6: DRRC: Severe asymmetrical irradiance changes $(350W/m^2 \rightarrow 1000W/m^2)$ , Ramp-rate factor: 50%, (a) Without DRRC: On CAVC, inverter currents, (b) Without DRRC: On VMM, inverter currents , (c) With DRRC: On CAVC, inverter currents, (d) With DRRC: On VMM, inverter currents, (e) With DRRC: On CAVC, inverter voltages, (f) With DRRC: On VMM, inverter voltages                                                        | 25 |

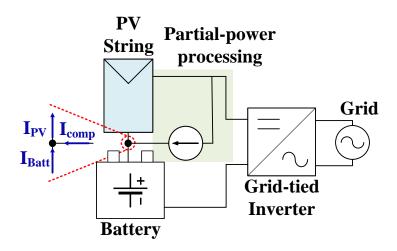

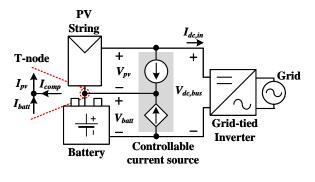

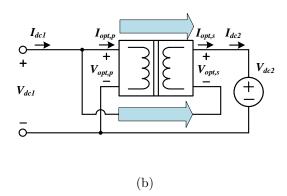

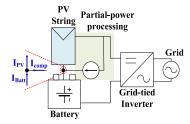

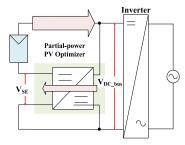

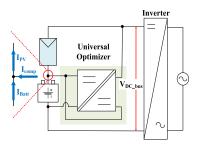

| FIGURE 3.1: The proposed approach: DC-series integration.                                                                                                                                                                                                                                                                                                                                                                                        | 33 |

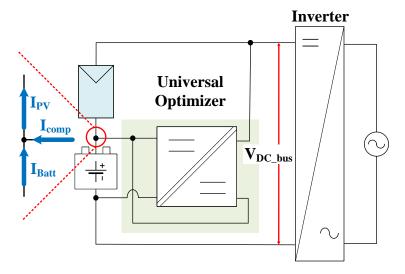

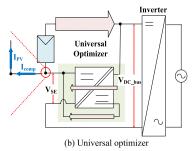

| FIGURE 3.2: Development of partial-power universal optimizer in PV-only mode: (a) Partial-power PV optimizer and (b) Universal optimizer.                                                                                                                                                                                                                                                                                                        | 36 |

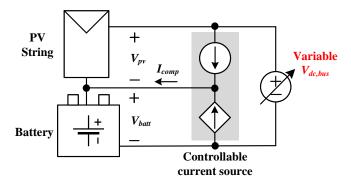

| FIGURE 3.3: The proposed partial-power universal optimizer in PV-battery mode.                                                                                                                                                                                                                                                                                                                                                                   | 38 |

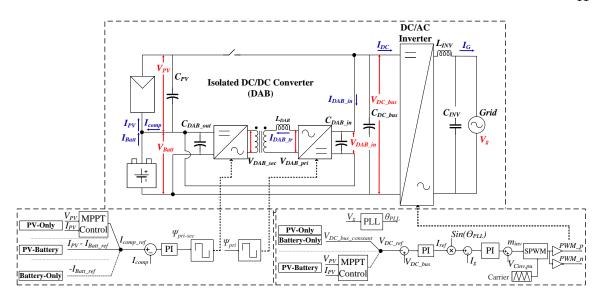

| FIGURE 3.4: Proposed topology for the universal optimizer and control strategy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 41 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

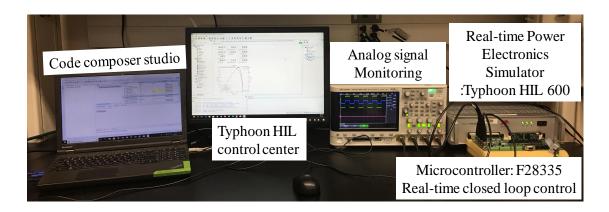

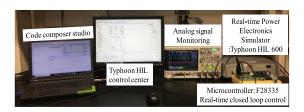

| FIGURE 3.5: CHIL setup for testing the proposed power electronics topology.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45 |

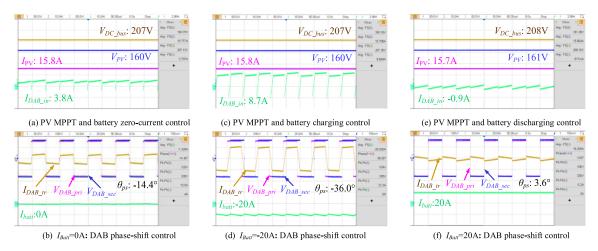

| FIGURE 3.6: CHIL experiment results: Steady-state operation of the PV-battery series inverter architecture in the PV-only mode, PV output power: 2.5kW, (a) PV MPPT control and (b) DAB phase-shift control.                                                                                                                                                                                                                                                                                                                                                          | 46 |

| FIGURE 3.7: CHIL experiment results: Steady-state operation of the PV-battery series inverter architecture in the PV-battery mode, PV output power: 2.5kW (MPPT) and battery output power: $\pm 1$ kW (battery zero-current mode, battery charging mode, and battery discharging mode); (a) PV MPPT and battery zero-current control, (b) $I_{Batt}$ =0A: DAB phase-shift control, (c) PV MPPT and battery charging control, (d) $I_{Batt}$ =-20A: DAB phase-shift control, (e) PV MPPT and battery discharging control, (f) $I_{Batt}$ =20A: DAB phase-shift control | 47 |

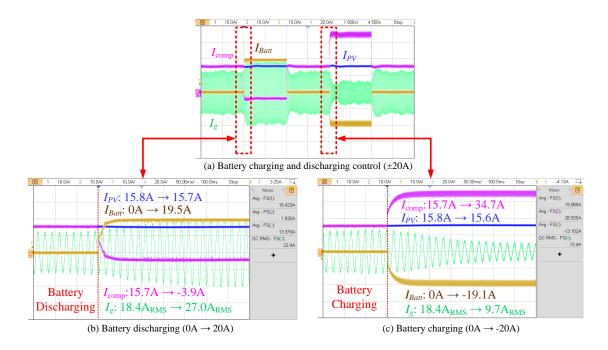

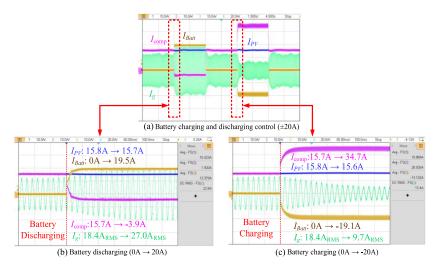

| FIGURE 3.8: CHIL experiment results: Transient operation of the PV-battery series inverter architecture in the PV-battery mode; battery zero-current mode, battery charging mode, and battery discharging mode (PV output power: $2.5 \mathrm{kW}$ and battery output power: $\pm 1 \mathrm{kW}$ )                                                                                                                                                                                                                                                                    | 49 |

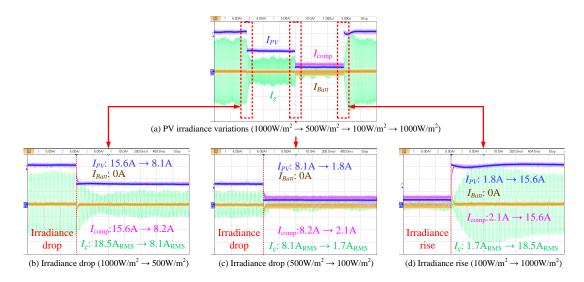

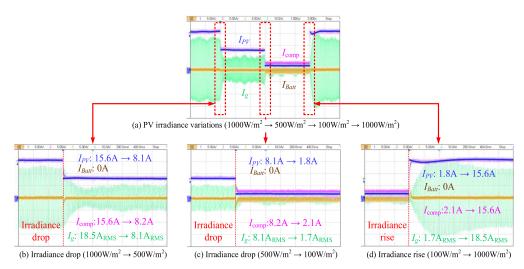

| FIGURE 3.9: CHIL experiment results: Transient operation of the PV-battery series inverter architecture in the PV-battery mode, PV irradiance variations $(1000W/m^2 \rightarrow 500W/m^2 \rightarrow 1000W/m^2)$ and battery zero-current mode.                                                                                                                                                                                                                                                                                                                      | 49 |

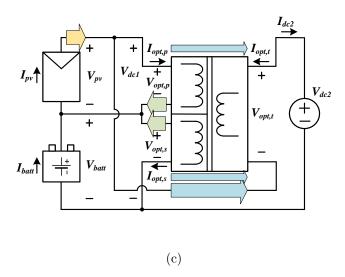

| FIGURE 4.1: DC-coupling PV-battery integration systems: (a) DC-parallel and (b) DC-series.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56 |

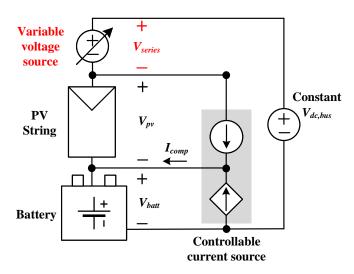

| FIGURE 4.2: PV-battery DC-series integrations: (a) connected to a controllable DC bus (a variable DC voltage source) and (b) connected to a fixed DC bus (a constant DC voltage source)                                                                                                                                                                                                                                                                                                                                                                               | 60 |

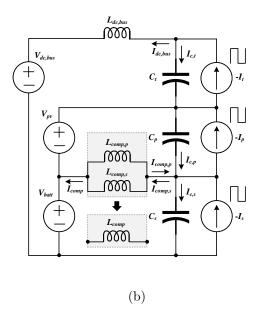

| FIGURE 4.3: Proposed PV-battery-series DC-DC optimizer topology: (a) PV-battery optimizer, (b) Series optimizer, and (c) PV-battery-series optimizer                                                                                                                                                                                                                                                                                                                                                                                                                  | 62 |

| FIGURE 4.4: Proposed PV-battery-series DC-DC optimizer circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68 |

|                                                                                                                                                                             | xiii |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

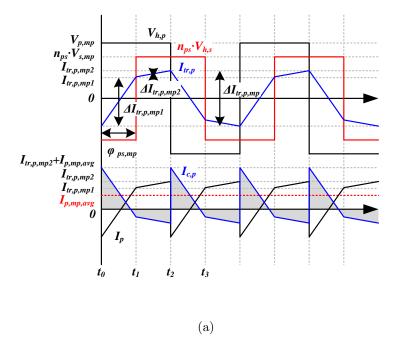

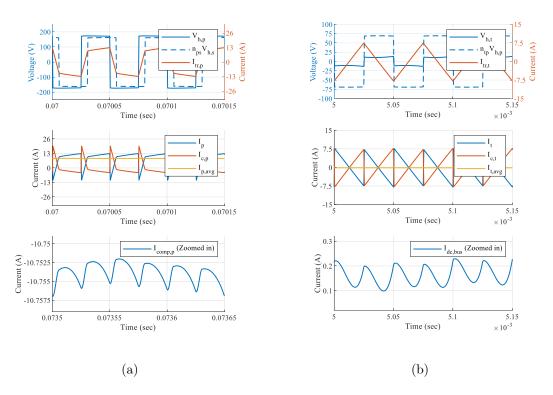

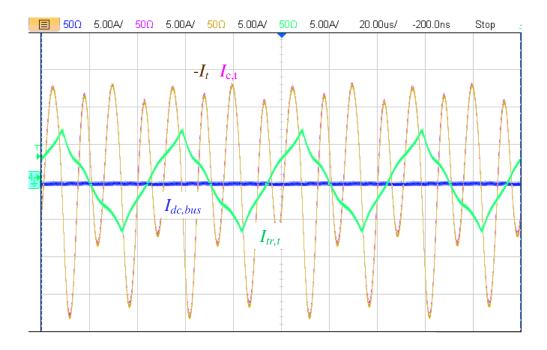

| FIGURE 4.5: TAB transformer voltage and current waveforms (top) and filter capacitor current waveforms (bottom): (a) the PS and (b) the TS.                                 | 71   |

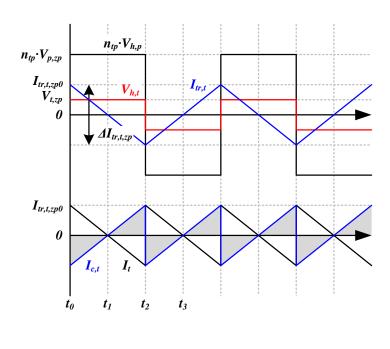

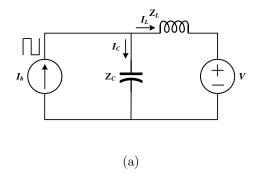

| FIGURE 4.6: HF ripple attenuation inductors: (a) an equivalent LC impedance circuit and (b) implemented HF ripple attenuation inductors in the PV-battery-series optimizer. | 74   |

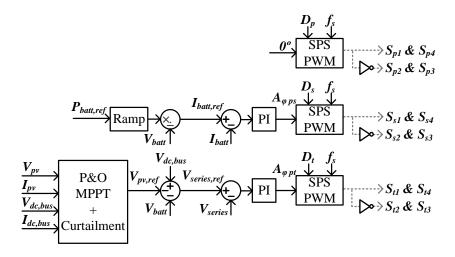

| FIGURE 4.7: SPS PWM based closed-loop control including PV MPPT-plus-Curtailment control, and battery charging and discharging power control.                               | 77   |

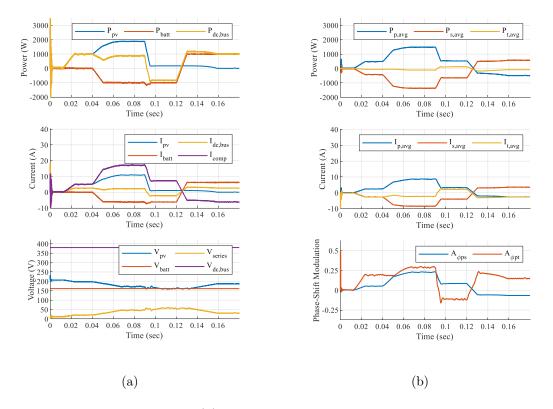

| FIGURE 4.8: Simulation results: (a) system power, current, and voltage waveforms and (b) optimizer power, current, and phase-shift modulation waveforms.                    | 79   |

| FIGURE 4.9: Simulation results: Effect of transformer leakage inductors, filter capacitors, HF ripple attenuation inductors: (a) the PS and (b) the TS.                     | 81   |

| FIGURE 4.10: Hardware prototype of the proposed system.                                                                                                                     | 83   |

| FIGURE 4.11: Experimental setup.                                                                                                                                            | 83   |

| FIGURE 4.12: Experimental results: (a) system voltage waveforms and (b) system current waveforms.                                                                           | 85   |

| FIGURE 4.13: Experimental results: Effect of transformer leakage inductors, filter capacitors, HF ripple attenuation inductors in the TS.                                   | 88   |

# LIST OF ABBREVIATIONS

AC Alternating current

AVG Average

BES Battery energy storage

BESS Battery energy storage system

CAVC Current administrator voltage compensator

CHIL Controller hardware-in-the-loop

DAB Dual active bridge

DC Direct current

DDE Detect drop end

DER Distributed energy resource

DRRC Decentralized ramp-rate control

ESS Energy storage system

FB Full bridge

HF High frequency

KVL Kirchhoff's voltage law

MPP Maximum power point

MPPT Maximum power point tracking

P-V Power versus voltage

P&O Perturb and observe

PE Power electronic

PI Proportional-integral

PLL phase locked loop

PPP Partial power processing

PPR Partial-power rate

PR Proportional-resonant

PS Primary side

PV Photovoltaic

RMS Root mean square

RRC Ramp-rate control

SE Series

SS Secondary side

TAB Triple active bridge

TS Tertiary side

V-I Voltage versus current

VMM Voltage mode members

#### CHAPTER 1: INTRODUCTION

#### 1.1 Motivation

Solar photovoltaic (PV) energy is one of the most promising renewable energy sources. Deployment of solar PV has grown rapidly in the United States over the years. Since 2016, around 10 GW of new PV installation has been made in the U.S. [1, 2]. Although solar PV energy is a clean and sustainable energy resource, the amount of generated electricity is highly dependent on the solar irradiance or panel temperature, which are affected by continuously changing weather conditions [3]. Integration of solar PV generation and battery energy storage (BES), referred to as solar-plus-storage, is an effective energy management solution that improves the utilization of electricity generated by solar PV generation systems [4, 5, 6]. A BES system stores surplus energy when a PV array's output power is higher than a load's power demand and discharges the saved energy when the PV output power becomes lower. This PV-battery integration helps meet power demands from electrical loads or the AC grid, while the generated power from the solar PV generation system varies due to intermittent weather conditions. Solar-plus-storage systems can provide efficient energy yield and management, resilience, and more revenue to residential houses and buildings.

In solar-plus-storage systems, power electronic (PE) converters work as key devices for power transfer from energy sources to loads or the AC grid [7, 8, 9]. The power converters generate the maximum output power from a solar PV array, store or release the energy to or from a BES, deliver the power to electric loads or the grid, and control these internal power distributions. Depending on the used PE converters for each power conversion stage and their coupling locations, different configurations of

solar-plus-storage systems are available [10]—AC-parallel, DC-parallel, and In-line—as shown in Figure 1.1. However, these state-of-the-art system configurations still use and combine legacy PE convert topologies initially designed for a solar PV generation system or a BES system separately. Therefore, they require many power converter stages or high-voltage PV arrays and batteries to interface both PV and battery to the grid. These system integration requirements result in higher system cost, bigger system size, and less round-trip efficiency.

This dissertation focuses on new configurations of solar-plus-storage systems and proposes PV-battery series optimizers—PE converters optimally designed for different residential solar-plus-storage systems.

Figure 1.1: State-of-the-art battery integration methods for grid-connected PV inverters in residential and commercial applications (a) AC-parallel integration, (b) DC-parallel integration, and (c) in-line integration.

#### 1.2 Literature Review

The most common PV-battery integration strategy is the AC-parallel integration that combines multiple distributed energy resource (DER) inverters at an AC coupling bus in parallel [11, 12, 13], as shown in Figure 1.1a. Each DER inverter regulates power flow between its DC energy source and the AC grid. In both solar PV and BES systems, an individual DER inverter commonly consists of two cascaded power conversion stages: a step-up DC-DC converter and a single- or three-phase DC-AC inverter. The step-up DC-DC converter is utilized to perform the main power control functions with DERs, such as PV maximum power point tracking (MPPT) control or battery charging and discharging control and amplify its input voltage to fit with the DC-AC inverter's DC input voltage range. The DC-AC inverter is responsible for maintaining grid-connection with the AC grid and conducting constant or variable DC input voltage control with the regulation of the AC output power. This twostage architecture helps solar-plus-battery system overcome a lack of their DC voltage caused by: a) the PV MPPT operation under low solar irradiance and high panel temperature, b) the limited area of solar panel installation in series, or c) a usage of low-voltage battery.

The AC-parallel integration method has been widely accepted by users—who already have DER inverters integrated to their AC grid—because of its system scalability. Additional DER inverters can be simply added to the AC grid since DER inverters are designed for the standard AC grid and are controlled independently. However, this integration method is not an economical solution due to the large number of PE converter stages. Based on the above-mentioned system configuration, the AC-parallel integrated system requires at least four PE converter stages for the PV-battery integration. The more PE converters, the higher the system cost and the lower the system efficiency. Especially, the round-trip efficiency becomes the lowest among all DER integration methods because of the largest number of converters in

the power flow path from a PV array to a battery.

Another common state-of-the-art PV-battery integration strategy is the DC-parallel integration that combines multiple DER converters at a DC power bus in parallel [14, 15, 16], as shown in Figure 1.1b. Like the DER inverters in the AC-parallel integrated system, each DER converter regulates power flow between its input energy source and output loads or the power bus. In the DC-parallel integration, however, the power bus is a DC coupling bus, referred to as DC-link. Therefore, an individual DER converter commonly consists of a single power conversion stage using a step-up DC/DC converter, and DER converters are connected to a separate power conversion stage delivering the DERs' power gathered at the DC-link to the AC load or grid by using a single- or three-phase DC-AC inverter. The operating principles of a step-up DC-DC converter and a DC-AC inverter are the same as or similar to the ones used in the AC-parallel integration.

Accordingly, the DC-parallel integration method has advantages over the AC-parallel integration in the system's cost, size, and energy conversion efficiency. Since only a single DC-AC inverter is used in the entire integrated system, the DC-parallel strategy has a fewer number of PE converter stages; for example, at least three PE converters are necessary for the PV-battery integration in the above-mentioned configuration. This reduction results in lower system cost and higher system efficiency. Especially, the power loss resulting from the round-trip process decreases by half compared to the one from the AC-parallel integration if it is assumed that the efficiencies of individual PE converters are the same. Also, the DC-parallel integration provides system scalability with the parallel coupling of multiple DER converters at the DC-link and their independent control schemes. However, the expansion at the DC-link is limited by the specifications of the DC-AC inverter used, such as DC input voltage range, maximum DC input current or power, etc., and the integrated system still requires additional DER converters for the expansion resulting in an increase in

system cost and size as well as a reduction in efficiency.

The third state-of-the-art PV-battery integration strategy is the In-line integration that directly inserts a BES in parallel to the DC-link of the two-stage grid-connected PV generation system composed of a DC-DC converter and a DC-AC inverter [17, 18], as shown in Figure 1.1c. Once the battery is directly connected to the DC-link, the control scheme of the DC-AC inverter needs to be adjusted from when the DC-AC inverter is used for the PV-only system. This adjustment changes the main operating function of the DC-AC inverter. Consequently, the system configuration can be redefined based on the individual PE converters' operating functions—the combination of a PV DC-DC converter and a battery DC-AC inverter. The PV DC-DC converter conducts the PV array's MPPT control, which is the same operating function of the PV DER converters used in the above mentioned two other integration strategies. On the other hand, the battery DC-AC inverter performs not only the grid-connection but also the battery charging and discharging control by adjusting the AC output power. In this integration method, the DC-link voltage is not controllable by any PE converters due to the voltage-source nature of the battery.

According to the direct integration of the battery, the In-line integration method has the least number of PE converters among all DER integration methods; at least two PE converters are required. Therefore, simplicity of the hardware architecture and further improvement on the system's efficiency are achieved. For instance, the energy conversions between the PV array and the battery or the battery and the AC grid can be made through only a single PE converter: the PV DC-DC converter or the battery DC-AC inverter, respectively. However, the direct integration also restricts the system's scalability and reconfigurability. In this integration method, the battery voltage needs to be higher than the minimum requirement of the DC input voltage of the DC-AC inverter for the grid-connection, or additional voltage amplification devices, such as a line-frequency transformer, are required, which causes an increase

of system cost and size. Also, like the DC-parallel integration method, the power expansion of PV and battery sources is highly dependent on the DC-AC inverter's specifications. Besides, dynamic response of the PE converters' control scheme needs to be adjusted because the battery integration changes the DC-link's system properties that needs to be considered for the controller design process. Furthermore, in case of single-phase grid applications, additional passive or active buffer decoupling double-line-frequency power pulsation from the DC battery power is required, which results an increase of system cost and size as well [19].

# 1.3 Proposed Solutions

This dissertation proposes a new approach to PV-battery integration, referred to as PV-battery series integration, and develops new PE converter solutions called PV-battery series optimizers for solar-plus-storage system applications.

The state-of-the-art PV-battery integration methods reviewed above require either additional PE converter stages or high-voltage energy sources to integrate a BES into a solar PV generation system. This is mainly because these methods adopt the parallel-integration approach. In the parallelly integrated system, the magnitude and form of output voltages of individual modules must be the same. The voltage magnitude of the parallel coupling node is usually higher than the voltage of the sources since the grid voltage or the DC bus voltage is high to be connected to the standard grid systems. This system integration requirement increases system cost and size and reduces the energy delivery efficiency.

On the other hand, the proposed PV-battery series integration approach can lessen this system integration requirement by connecting the PV module and the battery module in series. The series-connected energy modules can share the high-voltage requirement of each other. Therefore, a more optimal system design can be achieved. This dissertation proposes two PV-battery series integration methods depending on the solar-plus-storage system applications; AC-series and DC-series integrations.

The AC-series integration method adds a battery DC-AC inverter module into the AC power bus by adopting the AC-stacked PV inverter architecture approach. The AC-stacked PV inverter architecture is a novel panel-level residential solar PV inverter that achieves system miniaturization with series integration of modular PV inverters and the decentralized control scheme [20, 21]. The advantages of the ACseries integration over other state-of-the-art PV-battery integration methods are the system miniaturization and the highest energy conversion efficiency from the DERs to the AC grid. Costs of inverter components, installation, and maintenance can be significantly reduced by a) the low-voltage and high-frequency hardware design of individual inverter members and b) the removal of communication requirements among themselves or with the supervisory control center for the main power control functions. Also, only a single PE converter is required for the power delivery from DERs to the AC grid resulting in less power loss from the PE converter. Because of the miniaturized system design, the modular battery inverter in this PV-battery AC-stacked inverter architecture is suitable to mitigate sudden PV power fluctuations caused by weather changes: PV ramp-rate control [22, 23, 24, 25]. The proposed ACseries integration system has restrictions in control due to the interactive operation among the different inverter members under various asymmetrical operating conditions. The proposed system's feasibility and effectiveness are investigated through the controller hardware-in-the-loop (CHIL) simulation results and the operating margin analysis. In addition, the decentralized PV ramp-rate control that uses local feedback information only to conduct the PV ramp-rate control function without communication between the PV and battery inverters is developed to maintain the decentralized control environment in the AC-stacked inverter system.

The DC-series integration method directly connects a PV array and a BES in series. These series-connected energy sources are connected to the DC power bus in parallel. Therefore, the above-mentioned high-voltage system integration require-

ment can be reduced. As the DC-series integration has restrictions on independent current control of two series-connected energy sources, a controllable current source is added to inject a compensation current into the PV-battery DC-series coupling node. The PV-battery series optimizer—adopting partial power processing (PPP) converter topology [26, 27, 28, 29, 30]—is applied in the proposed system to configure this controllable current source. The advantages of the DC-series integration over other state-of-the-art PV-battery integration methods are a) PV-battery voltage support to be connected to a high-voltage DC bus without a fully rated power converter, b) reduction of the rated power of the interfacing DC-DC converter by adopting PPP system architecture, c) single power converter stage between the series-connected energy sources and the DC bus, and d) system reconfigurability without changing circuit topology. The proposed system is suitable for energy backup and resilience applications. In this research, two PV-battery series optimizers are developed for two different grid applications: AC grid and DC grid. In the AC grid coupled system, the coordinated closed-loop control between the PV-battery optimizer and the DC-AC inverter is proposed for different operation modes since the DC-bus voltage varies according to the PV's and the battery's operating conditions. In the DC grid coupled system, especially a regulated DC microgrid, a modification of the DC-series integration by adding a variable voltage source to the PV-battery DC series loop and developing the PV-battery-series optimizer working as both a controllable current source and a variable voltage source are proposed. The operating and control principles and the contributions of the proposed systems are demonstrated through DC analysis, off-line simulation, real-time CHIL simulation, and experimental results.

#### 1.4 Organization of Dissertation

The dissertation is organized as follows: Chapter 2 describes the AC-series integration method and the operating margin analysis of the PV-battery AC-stacked inverter architecture with the decentralized PV ramp-rate control [31]. Chapter 3 presents the

DC-series integration method and the PV-battery series inverter architecture with the coordinated control algorithm [32]. Chapter 4 discusses the modified DC-series integration method for a regulated DC microgrid application and its interfacing converter, PV-battery-series DC-DC optimizer. Chapter 5 presents the conclusions and discussions of the research.

# CHAPTER 2: CONTROL AND OPERATING RANGE ANALYSIS OF AN AC-STACKED PV INVERTER ARCHITECTURE INTEGRATED WITH A BATTERY

This chapter presents a control scheme to operate a battery-integrated AC-stacked photovoltaic (PV) inverter architecture and its operating range analysis. The main operation strategy is the combination of decentralized controls of individual inverter members; PV and battery. In AC-series integration, battery charging and discharging operations affect operating margins of the PV inverter members. The interactive operation needs to be analyzed to identify the system operating range under different conditions. A ramp-rate control which mitigates PV output variations and improves grid stability is a suitable application for the PV-battery AC-stacked inverter architecture utilizing a panel-level modular inverter design. Decentralized ramp-rate control algorithm is proposed and demonstrated to analyze the system operating range. The detailed system control and analysis are performed through controller hardware-in-the-loop testing.

# 2.1 Introduction

The AC-stacked photovoltaic (PV) inverter architecture is a panel-level cascaded modular inverter topology suitable for single-phase grid-tied PV applications [1], [2]. High-frequency and low-voltage PV inverter members are stacked in series to satisfy the AC voltage for grid-connection and extract maximum output power from individual PV panels. To maximize the architecture's effectiveness, each building block is controlled independently without communications among themselves and with minimum handshaking with the supervisory control center for grid-synchronization [2].

Its tangible advantages and capabilities with smart inverter functions are verified through laboratory experiments, controller hardware-in-the-loop (CHIL) testing, and site demonstration in [2]-[7].

In PV applications, integration of a battery into a PV generation system has received significant attention because of the intermittent nature of solar energy sources [8]-[10]. In most of state-of-the-art battery integration methods, legacy PV power electronics systems [11] are used to configure different integration topologies; a) AC-parallel [12], [13], b) DC-parallel [14]-[16], and c) in-line [17]-[19] integrations. In these integration methods, voltage-amplification power electronics stages or high-voltage battery are required to cope with high DC input voltage requirement of a DC-AC inverter. On the other hand, the AC-stacked PV inverter architecture can integrate a battery without the high voltage requirement by adopting AC-series configuration [20], [21]. Besides, system optimization can be achieved by adding a battery inverter unit into the termination box which has already been applied to the AC-stacked PV inverter architecture for protection, phase locked loop (PLL), and communication with the supervisory control center [2], [3].

This research investigates control scheme and operation characteristics of the PV-battery AC-stacked inverter architecture. In this architecture, modular inverter members are cooperating to maintain grid-connection and control the AC string power. Therefore, this cooperation introduces interactive operations among the inverter members when system operating condition varies. Since the interactive operation creates duty cycle changes in the DC-AC inverters, analysis of the inverter members' interaction is required to clarify the operating range of the architecture with battery charging and discharging operation.

Due to the battery charging and discharging limitations caused by the interaction, a ramp-rate control (RRC) is a suitable application for the PV-battery AC-stacked inverter architecture utilizing a panel-level modular inverter design. A RRC mitigates fast-changing, high ramp-rate, PV output variations and regulates the desired ramp-rate of the PV output by controlling the battery charging and discharging current [22]-[25]. Grid stability issues such as voltage and frequency fluctuations caused by high penetration of PV generation in especially weak distribution network can be improved by lowering the PV output ramp-rate. In this chapter, the decentralized ramp-rate control (DRRC) using the differentiation of the AC string current as an indicator of PV output variations is proposed to realize the decentralized control environment and minimize the communication requirements between the inverter members [21]. Since the inverter members are connected in series, the differentiation of the AC string current represents both PV and battery output variations when the battery is charged or discharged. Therefore, new criteria to distinguish PV output variations and create the proper amount of the battery current reference for the DRRC are presented. The control performance of the DRRC and the interactive operation among the inverter members with PV and battery output variations are demonstrated through CHIL testing.

# 2.2 PV-Battery AC-Stacked Inverter Architecture

# 2.2.1 Proposed PV-battery AC-stacked inverter architecture

The proposed PV-battery AC-stacked inverter architecture is composed of three different types of modular inverters: a) current administrator voltage compensator (CAVC), b) voltage mode members (VMM), and c) energy storage system (ESS). By stacking or connecting a group of PV inverters in series, the architecture can support the AC grid voltage requirement for grid-connection with low voltage semiconductor devices. Figure 2.1 presents the AC-series configuration and the control diagram of the three different types of modular inverters. A CAVC controls its DC input voltage,  $V_{PV1}$ , with a closed-loop PI controller. A maximum power point tracking (MPPT) control generates the DC input voltage reference to extract the maximum power from the PV panel. Also, the CAVC is responsible for controlling the AC

string current,  $I_{string}$ , with a closed-loop PR controller. A VMM only controls its DC input voltage,  $V_{PV2}$ , for the MPPT control of its PV panel. Multiple VMMs work as voltage buffers to build up the architecture's AC output voltage. An ESS controls the battery charging and discharging current,  $I_{Batt}$ , with a closed-loop PI controller. The proposed RRC generates the battery current reference to mitigate PV output variations. Individual closed-loop controls generate modulation indices,  $m_{inv1}$ ,  $m_{inv2}$ , and  $m_{inv3}$ , to operate individual inverter members, and the feedforward terms,  $V_{C1,pu}$ ,  $V_{C2,pu}$ , and  $V_{C3,pu}$ , are applied to improve the system control response and lower the impact of grid disturbances.

Figure 2.1: PV-battery AC-stacked inverter architecture and control diagram.

Details of the RRC strategy are explained in section III. Since the PV-battery AC-stacked inverter architecture provides the decentralized environment in terms of both physical topology and control, each modular inverter is controlled autonomously by using its local measurements except grid-synchronization information.

# 2.2.2 Interactive operation between inverter members

The main operation principle of the proposed PV-battery AC-stacked inverter architecture is the combination of the decentralized control algorithm of the individual inverter members connected in series. In the AC string where the same AC current,  $i_{string}$ , is passing through all the inverter members, the inverters' output voltages vary based on the inverter output power. Since the inverters are cooperating to regulate their AC output power in grid-connection, one inverter's output power variations may affect others' AC output voltages corresponding to the inverters' operating margin. Therefore, the interaction between the inverters limits the operating range of the architecture.

When asymmetrical irradiance drop is applied to the PV panels, the PV inverter with the low output power decreases its AC output voltage, and it makes other inverters increase their output voltage to compensate the AC voltage drop and track individual maximum power point (MPP), as presented in previous publications [2], [4]. Likewise, battery charging and discharging operations force PV inverters' AC output voltage changes [21]. When battery charging mode is applied to the ESS inverter, the ESS AC voltage appears to be inverted to have negative power flow through the ESS. The inverted ESS AC voltage makes the CAVC and the VMM increase their AC voltages resulting the PV inverters' higher modulation indices. Higher modulation index requests the use of more operating margin for the inverter. If the amount of the compensated AC voltage is higher than the PV inverters' remaining operating margins, the modulation indices reach the maximum amount (1.0), and abnormal operation such as AC current distortion or losing MPPT occurs because the inverters

have no room to increase their output voltage more. Different control schemes in the CAVC and the VMM introduce the different abnormal operations, AC current distortion and losing MPPT control, since the CAVC utilizes sinusoidal AC string current information as the feedback signal for the closed-loop control and the VMM utilizes DC input voltage information. This interaction is required to be considered to design the reliable PV-battery AC-stacked inverter architecture which has a wide operating range and provides high-quality AC current.

# 2.3 Decentralized Ramp-Rate Control Strategy

In the proposed architecture utilizing a panel-level inverter design, a RRC which smooths out PV output variations is a suitable application of the battery integration due to the battery charging and discharging limitations caused by the interaction addressed in the previous section. In this architecture, the ESS determines its battery current reference without handshaking with PV inverters or supervisory control center to achieve decentralized control environment. In the proposed DRRC strategy, the ESS utilizes its local AC string current measurement,  $i_{string}(t)$ , for detection of PV output variations and battery current calculation. The overall mechanism of the DRRC is shown in Figure 2.2a. The first step is the detection of PV variations with the differentiation of AC string current, as follows:

$$\frac{di_{string\_avg}(t_k)}{dt} = \frac{di_{string\_avg}(t_k) - di_{string\_avg}(t_{k-1})}{t_k - t_{k-1}}$$

(2.1)

where  $t_k$  is the time at the  $k^{th}$  instant,  $t_{k-1}$  is the time at the  $(k-1)^{th}$  instant,  $i_{string\_avg}(t)$  is the RMS average of  $i_{string}(t)$ , and  $dI_{string\_avg}(t)$  is the AC current difference. To ignore small variations caused by the MPPT control, a dead-band,  $dI_{limit}$ , is applied, as follows:

Figure 2.2: Illustration of the DRRC algorithm (a) Ideal case: without detection delay and (b) Practical case: with detection delay.

$$dI_{detect} = \begin{cases} dI_{string\_avg}(t_{detect\_drop}), & dI_{string\_avg}(t_{detect\_drop}) > dI_{limit} \\ 0, & dI_{string\_avg}(t_{detect\_drop}) \le dI_{limit} \end{cases}$$

$$(2.2)$$

where  $t_{detect\_drop}$  is the moment when PV output variation is detected,  $dI_{string\_avg}(t_{detect\_drop})$  is the AC string current difference at  $t_{detect\_drop}$ , and  $dI_{detect}$  is the PV output change detected.

The ESS will start to charge or discharge the battery to achieve the desired ramprate of the inverter architecture's output once the PV output variation is detected. In

the proposed architecture, a criterion to distinguish the PV output changes from the

total AC string output power is required for the decision of the ESS output current

since the output of the ESS also affects the differentiation of the AC string current due

to the series-connection. As shown in Figure 2.2a, two current references  $i_{ref\_PV}(t)$ and  $i_{ref\_total}(t)$  are generated with two different ramp-rates; the detected PV output ramp-rate,  $dI_{detect}$ , and the desired architecture's output ramp-rate,  $dI_{ref\_total}$ ,

respectively, as follows:

$$i_{ref\_PV}(t_k) = i_{ref\_PV}(t_{k-1}) + \frac{dI_{detect}}{dt}T_{step}$$

(2.3)

$$i_{ref\_total}(t_k) = i_{ref\_total}(t_{k-1}) + \frac{dI_{ref\_total}}{dt}T_{step}$$

(2.4)

$$dI_{ref\_total} = dI_{detect} k_{ramp\_rate\_total}$$

(2.5)

where  $T_{step}$  is the controller time step and  $k_{ramp\_rate\_total}$  is the ramp-rate gain (0.1-1.0). By subtracting  $i_{ref\_PV}(t)$  from  $i_{ref\_total}(t)$ , the battery current reference,  $i_{batt}(t)$ , can be calculated, and its absolute value,  $|i_{batt}(t)|$ , is increased until the moment of PV output variations stop denoted as  $t_{drop\_end}$ . After  $t_{drop\_end}$ ,  $i_{ref\_PV}(t)$  is set as constant by forcing  $dI_{detect}$  zero, and  $|i_{batt}(t)|$  decreases constantly until it becomes zero,  $t_{ctrl\_end}$ , as follows:

$$i_{batt}(t_k) = \begin{cases} (i_{ref\_total}(t_k) - i_{ref\_PV}(t_k))k_{ACtoDC}, & t_k \le t_{DDE} \\ (i_{ref\_total}(t_k) - i_{ref\_PV}(t_{DDE}))k_{ACtoDC}, & t_{DDE} < t_k \le t_{ctrl\_end} \end{cases}$$

$$(2.6)$$

where  $k_{ACtoDC}$  is the AC to DC current gain and  $t_{DDE}$  is the moment when the ESS detects PV output variation stop. DDE is the abbreviation of "detect drop end". The detection of PV output variation stop is achieved by monitoring the differentiation of the AC current, as below:

$$|i_{batt}(t_k)| \ decreases, \ if \begin{cases} \frac{di_{string\_avg}(t_k)}{dt} \leq 0, & Charging \ mode \\ \frac{di_{string\_avg}(t_k)}{dt} \geq 0, & Discharging \ mode \end{cases}$$

(2.7)

When PV output variations stop,  $|i_{batt}(t)|$  continues to increase and the differentiation of the AC current is going to be zero. Moreover, the direction of the differentiation

will be reversed unless  $|i_{batt}(t)|$  starts to decrease. The reversed direction of the differentiation can be an indicator of  $t_{DDE}$ . After  $t_{DDE}$ ,  $|i_{batt}(t)|$  decreases to zero  $(t_{ctrl\_end})$  and the proposed DRRC is completed. In Figure 2.2a and Figure 2.2b, ideal and practical cases of the DRRC strategy are illustrated. In Figure 2.2b, each transition of detection sequences such as from  $t_{drop}$  to  $t_{detect\_drop}$  and from  $t_{drop\_end}$  to  $t_{DDE}$  requires the differentiation calculation delay. This sequence delay will cause the mismatch between the final ramp-rate and the desired ramp-rate, and the small fluctuation of the AC power. The ramp-rate mismatch error can be reduced by optimizing the sequence delay.

### 2.4 Results and Discussions

To verify the effectiveness of the proposed architecture and its DRRC strategy, the CHIL test set-up is built, as shown in Figure 2.3 [26]. In this set-up, two PV inverters, a CAVC and a VMM, and an ESS inverter are constructed. The detail system parameters are represented in Table 2.1.

Figure 2.3: CHIL set-up for testing PV-battery AC-stacked inverter system.

Table 2.1: DESIGN PROPERTIES OF THE PV-BATTERY AC-STACKED INVERTER  $\,$

| System Specifications       |                    |        |  |  |  |  |

|-----------------------------|--------------------|--------|--|--|--|--|

| Grid                        |                    |        |  |  |  |  |

| Voltage                     | $V_g (V_{RMS})$    | 30     |  |  |  |  |

| PV pane                     | el                 |        |  |  |  |  |

| MPPT: Power $(1000W/m^2)$   | $P_{MPP}$ (W)      | 255.10 |  |  |  |  |

| MPPT: Voltage $(1000W/m^2)$ | $V_{MPP}$ (W)      | 33.45  |  |  |  |  |

| MPPT: Current $(1000W/m^2)$ | $I_{MPP}$ (W)      | 7.63   |  |  |  |  |

| Battery                     |                    |        |  |  |  |  |

| Nominal voltage             | $V_{Battery}$ (V)  | 42.20  |  |  |  |  |

| Capacity                    | $C_{Battery}$ (Ah) | 20     |  |  |  |  |

# 2.4.1 Interactive operation between PV and ESS inverters

The CHIL test results of the inverters' interaction under asymmetrical PV output variations and battery charging and discharging are presented in Table 2.2. The minimum irradiance level on the CAVC where the architecture provides stable operation is  $320W/m^2$ . In this condition, the peak modulation index of the VMM reaches 1.0 by using all operating margin to cover the CAVC AC voltage drop. Below the minimum irradiance level,  $(100W/m^2)$ , the architecture cannot perform MPPT control because the VMM is required to move its operating point to the right side of the MPP to increase its output voltage. In case of asymmetrical irradiance drop on the VMM, the minimum irradiance level is  $250W/m^2$ . Below the minimum irradiance level,  $(100W/m^2)$ , AC current distortion occurs. The PV inverters' interaction limits the architecture's operating range.

Table 2.2: SUMMARY OF CHIL TEST RESULTS: PEAK MODULATION INDICES AND OPERATING MARGIN OF THE INVERTERS WITH DIFFERENT OPERATING CONDITIONS.

| Detail conditions |                    | Peak modulation indices |      |      |      |               | Operating margin      |           |            |            |

|-------------------|--------------------|-------------------------|------|------|------|---------------|-----------------------|-----------|------------|------------|

|                   | nce level<br>//m²) | Battery current         | CAVC | VMM  | ESS  | Not in<br>MPP | Current<br>Distortion | CAVC      | VMM        | ESS        |

| CAVC              | VMM                | (A)                     |      |      |      |               |                       |           |            |            |

| 1000              | 1000               | -                       | 0.72 | 0.67 | 0.03 | -             | -                     | 28%       | 33%        | 97%        |

| 500               | 1000               | -                       | 0.51 | 0.89 | 0.03 | -             | -                     | -         | 11% (-22%) | -          |

| 320               | 1000               | -                       | 0.39 | 1.0  | 0.03 | -             | -                     | -         | 0% (-33%)  | -          |

| 100               | 1000               | -                       | 0.28 | 1.0  | 0.03 | ✓             | -                     | -         | 0% (-33%)  | -          |

| 1000              | 500                | -                       | 0.91 | 0.46 | 0.03 | -             | -                     | 9% (-19%) | -          | -          |

| 1000              | 250                | -                       | 1.00 | 0.29 | 0.03 | -             | -                     | 0% (-28%) | -          | -          |

| 1000              | 100                | -                       | 1.00 | 0.16 | 0.03 | -             |                       | 0% (-28%) | -          | -          |

| 500               | 500                | -                       | 0.72 | 0.68 | 0.03 | -             | -                     | 18% (0%)  | 32% (-1%)  | -          |

| 1000              | 1000               | Charging: -4            | 0.99 | 0.97 | 0.46 | -             | -                     | 1% (-27%) | 3% (-30%)  | 54% (-43%) |

| 1000              | 1000               | Charging: -4.6          | 1.00 | 1.00 | 0.58 | -             | -                     | 0% (-28%) | 0% (-33%)  | 42% (-55%) |

| 1000              | 1000               | Charging: -4.8          | 1.00 | 1.00 | 0.64 | -             |                       | 0% (-28%) | 0% (-33%)  | 36% (-61%) |

| 1000              | 1000               | Discharging: 13.9       | 0.65 | 0.33 | 0.57 | -             | -                     | 35% (+7%) | 67% (+34%) | 33% (-64%) |

Battery charging mode limits the architecture's operating range, as shown in Figure 2.4. When battery current is  $-4A_{DC}$ , the ESS generates  $-14.37V_{RMS}$  AC voltage. The CAVC and the VMM consume their 96.4% (27%/28%×100=96.4%) and 90.9% (30%/33%×100=90.9%) of available operating margin, respectively, to compensate the inverted ESS AC voltage. The maximum battery charging current is  $-4.6A_{DC}$  and the peak modulation indices of the PV inverters reach 1.0 by using all operating margin. With higher battery charging current than -4.6A, the AC current distortion occurs, as shown in Figure 2.4c. Therefore, the operating range in battery charging mode is related to the operating margin of the PV inverters ( $\approx 28\%$  of CAVC's and  $\approx 33\%$  of VMM's). If the architecture is extended for  $120V_{RMS}$  electrical grid by adding identical PV inverters, the architecture can handle more asymmetrical irradiance drop and battery charging currents. However, the percentage of available operating margin is maintained. The PV inverters must be redesigned with a higher DC input voltage to increase the percentage of available operating margin.

Figure 2.4: Interactive operation of the inverters with battery operating conditions;  $I_{string}$ : AC string current,  $V_{CAVC}$ : CAVC AC voltage,  $V_{VMM}$ : VMM AC voltage, and  $V_{ESS}$ : ESS AC voltage, (a) charging mode (-4A), (b) discharging mode (4A), (c) charging mode (-4.8A)

# 2.4.2 Decentralized ramp-rate control

Table 2.3 and Figure 2.5 present the CHIL test results of the DRRC under different asymmetrical irradiance changes. In this test, the 0.5 ramp-rate gain,  $k_{ref\_total}$ , is applied. When a CAVC irradiance drop  $(1000W/m^2 \rightarrow 500W/m^2)$  is applied, the CAVC output power is decreased by 122.1W for 2.72 seconds introducing the PV output ramp-rate, -1.50 $A_{RMS}/s$ , as shown in Figure 2.5a. Adopting the DRRC, the architecture achieves 47% of the PV output ramp-rate, -0.70 $A_{RMS}/s$ , by discharging the battery, as shown in Figure 2.5c. Detecting the AC power changes, the ESS increases the battery discharging current until the irradiance drop ends. Detecting the reversed sign of the differentiation of  $i_{string}(t)$ , the ESS decreases the battery discharging current from 1.11A to 0A. The interaction between inverters is shown in

Figure 2.5e. The CAVC AC voltage is decreased by the CAVC output power drop. The VMM compensates the CAVC AC voltage drop by increasing its AC voltage. Also, the ESS participates the compensation of the CAVC voltage drop and reduces a burden on the VMM slightly during battery discharging operation. When the CAVC irradiance rise  $(500W/m^2 \rightarrow 1000W/m^2)$  is applied, the PV output ramp-rate,  $1.61A_{RMS}/s$ , is achieved as Figure 2.5b. With the DRRC, 49% of the PV output ramp-rate,  $0.79A_{RMS}/s$ , is achieved by charging the battery, as presented in Figure 2.5d. The maximum battery charging current is 1.51A. In this case, the PV inverters increase their AC voltage to compensate the inverted ESS AC voltage as Figure 2.5f. Therefore, battery charging operation charges more operating margin of PV inverters. As illustrated in Figure 2.2b, the ramp-rate mismatch occurs due to the differentiation calculation delays. The mismatch errors are from 2%  $(1-49\%/50\%\times100=2\%)$  to 12%  $(1-44\%/50\%\times100=12\%)$ . Also, small fluctuation of the AC current is observed.

Table 2.3: SUMMARY OF CHIL TEST RESULTS: THE DRRC WITH DIFFERENT OPERATING CONDITIONS.

| Detail conditions |     |                                      |      | Changes |          |          | Without DRRC        |       | With DRRC             |       | Ramp-                 |                            |            |                        |

|-------------------|-----|--------------------------------------|------|---------|----------|----------|---------------------|-------|-----------------------|-------|-----------------------|----------------------------|------------|------------------------|

| Modular inverter  |     | Irradiance level (W/m <sup>2</sup> ) |      |         | $P_{PV}$ | $I_{PV}$ | Istring             | Time  | Ramp-rate             | Time  | Ramp-rate             | MAX.<br>I <sub>batt.</sub> | rate ratio | Inverter<br>limitation |

| CAVC              | VMM | Type                                 | From | To      | (W)      | (A)      | (A <sub>RMS</sub> ) | (sec) | (A <sub>RMS</sub> /s) | (sec) | (A <sub>RMS</sub> /s) | (A)                        | (%)        | iiiiitatioii           |

| ☑                 | -   | Drop                                 | 1000 | 500     | -122. 1  | -4.6     | -4.07               | 2.72  | -1.50                 | 5.82  | -0.70                 | 1.11                       | 47         | 1                      |

| ☑                 | -   | Rise                                 | 500  | 1000    | 127.2    | 4.6      | 4.24                | 2.64  | 1.61                  | 5.34  | 0.79                  | 1.51                       | 49         | -                      |

| -                 | ☑   | Drop                                 | 1000 | 500     | -127.2   | -4.8     | -4.24               | 2.58  | -1.64                 | 5.86  | -0.72                 | 1.11                       | 44         | =                      |

| -                 | ☑   | Rise                                 | 500  | 1000    | 127.2    | 4.6      | 4.24                | 2.84  | 1.49                  | 6.56  | 0.65                  | 1.35                       | 44         | =                      |

| ☑                 | ☑   | Drop                                 | 1000 | 500     | -254.4   | -9.2     | -8.48               | 5.48  | -1.55                 | 11.34 | -0.75                 | 2.23                       | 48         | =                      |

| ☑                 | Ø   | Rise                                 | 500  | 1000    | 254.4    | 9.2      | 8.48                | 5.62  | 1.51                  | 11.74 | 0.72                  | 2.3                        | 48         | -                      |

| ☑                 | -   | Rise                                 | 350  | 1000    | 164.4    | 5.3      | 5.48                | 2.88  | 1.90                  | 8.16  | 0.67                  | 1.6                        | 35         | V                      |

| -                 | Ø   | Rise                                 | 350  | 1000    | 169.8    | 5.3      | 5.66                | 3.4   | 1.66                  | 6.16  | 0.92                  | 1.35                       | 55         | Ø                      |

Figure 2.5: DRRC: Asymmetrical irradiance changes on CAVC ( $1000W/m^2 \leftrightarrow 500W/m^2$ ), Ramp-rate factor: 50%, (a) Without DRRC: Irradiance drop, inverter currents, (b) Without DRRC: Irradiance rise, inverter currents, (c) With DRRC: Irradiance drop, inverter currents, (d) With DRRC: Irradiance rise, inverter currents, (e) With DRRC: Irradiance drop, inverter voltages, (f) With DRRC: Irradiance rise, inverter voltages

# 2.4.3 Operating range of the decentralized ramp-rate control

Severe asymmetrical irradiance rise  $(350W/m^2 \rightarrow 1000W/m^2)$  is applied to the CAVC and the VMM to analyze operating range of the DRRC in the proposed architecture,

as shown in Figure 2.6. In case of the CAVC irradiance rise, the AC current distortion occurs in the middle of the slope where two interactions caused by asymmetrical irradiance changes and battery charging mode are overlapped at the same time, as illustrated in Figure 2.6c. Since the detection of the PV output change stop is delayed due to the AC current distortion, the DRRC time is extended to 8.16 seconds resulting 35% of the PV output ramp-rate. Therefore, the ramp-rate mismatch error is increased to 30% (1-35%/50%×100=30%). The interaction between inverters is shown in Figure 2.6e. The CAVC reaches its maximum AC voltage to cover the VMM AC voltage drop and the inverted ESS AC voltage. In case of the VMM irradiance rise, the limitation of the AC current occurs in the middle of the slope due to the overlapped interactions, as presented in Figure 2.6d. Therefore, the VMM moves its operating point from the MPP. This results in the PV current decrease. Since the AC current limitation allows for early detection of the PV output change stop, the DRRC time is shortened to 6.16 seconds resulting 55% of the PV output ramp-rate. Therefore, the negative ramp-rate mismatch error occurs as -10% (1-55%/50%×100=-10%).

Figure 2.6: DRRC: Severe asymmetrical irradiance changes  $(350W/m^2 \rightarrow 1000W/m^2)$ , Ramp-rate factor: 50%, (a) Without DRRC: On CAVC, inverter currents, (b) Without DRRC: On VMM, inverter currents, (c) With DRRC: On CAVC, inverter currents, (d) With DRRC: On VMM, inverter currents, (e) With DRRC: On CAVC, inverter voltages, (f) With DRRC: On VMM, inverter voltages

## 2.5 Conclusion

This chapter presented a control scheme for the PV-battery AC-stacked inverter architecture and its analysis of system operating range. The PV and ESS inverters' interactive operation and the feasibility of the DRRC were verified through the CHIL

test results. Operation constraints on the constructed architecture were asymmetrical irradiance drop,  $320W/m^2$  on CAVC and  $250W/m^2$  on VMM, and the -4.6A battery charging current. Operating margins of inverters are critical in designing a reliable inverter architecture. A RRC mitigating PV output variations is a suitable application for the proposed architecture due to the battery charging and discharging limitations caused by the interaction. The DRRC can realize the decentralized control environment and minimize the communication requirements between the inverters. Applying the DRRC, the architecture achieved desired total AC output ramp-rates during the irradiance changes on PV panels. The overlapped interactions (the asymmetrical irradiance level and battery charging mode) affected on the performance of the DRRC. The AC current distortion and early detection of the PV output change stop were observed once the PV inverters use all of their operating margins. Further improvement can be made by implementing PV output curtailment control which can reduce the required amount of the battery charging current.

#### 2.6 References

- © 2018 IEEE. Reprinted, with permission, from N. Kim and B. Parkhideh, "Control and operating range analysis of an AC-stacked PV inverter architecture integrated with a battery," *IEEE Transactions on Power Electronics*, vol. 33, no. 12, pp. 10032-10037, Apr. 2018.

- [1] S. Bhowmik, "Systems and methods for solar photovoltaic energy collection and conversion," U.S. Patent 9531293 B2, Dec. 27, 2016.

- [2] H. Jafarian, S. Bhowmik, and B. Parkhideh, "Hybrid Current-/Voltage-Mode Control Scheme for Distributed AC-Stacked PV Inverter With Low-Bandwidth Communication Requirements," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 1, pp. 321-330, Jan. 2018.

- [3] H. Jafarian, R. Cox, J. H. Enslin, S. Bhowmik, and B. Parkhideh, "Decentralized

- Active and Reactive Power Control for an AC-Stacked PV Inverter With Single Member Phase Compensation," *IEEE Transactions on Industry Applications*, vol. 54, no. 1 pp. 345-355, Jan. 2018.

- [4] H. Jafarian, N. Kim, and B. Parkhideh, "Decentralized Control Strategy for AC-Stacked PV Inverter Architecture Under Grid Background Harmonics," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 6, no. 1 pp. 84-93, Mar. 2018.

- [5] H. Jafarian, N. Kim, B. Parkhideh, and J. Enslin, "Analysis of smart inverter functions of decentralized grid-connected AC-stacked PV inverter architecture," in *Proc. IEEE Applied Power Electronics Conference and Exposition*, 2017, pp. 3594-3600.

- [6] H. Jafarian, N. Kim, and B. Parkhideh, "A distributed active and reactive power control strategy for balancing grid-tied cascaded H-bridge PV inverter system," in *Proc. IEEE Energy Conversion Congress and Exposition*, San Antonio, TX, USA, 2017, pp. 1667-1672.

- [7] EPRI Report #3002011366, "Program to technology innovation: investigation of a series-connected solar inverter architecture," Release date: June 2017.

- [8] C. A. Hill, M. C. Such, D. Chen, J. Gonzalez, and W. M. Grady, "Battery energy storage for enabling integration of distributed solar power generation," IEEE Transactions on smart grid, vol. 3, no. 2 pp. 850-857, Jun. 2012.

- [9] T. D. Hund, S. Gonzalez, and K. Barrett, "Grid-tied PV system energy smoothing," in *Proc. IEEE Photovoltaic Specialists Conference*, Honolulu, HI, USA, 2010, pp. 002762-002766.

- [10] J. Traube, F. Lu, D. Maksimovic, J. Mossoba, M. Kromer, P. Faill, S. Katz, B. Borowy, S. Nichols, and L. Casey, "Mitigation of solar irradiance intermit-

- tency in photovoltaic power systems with integrated electric-vehicle charging functionality," *IEEE Transactions on Power Electronics*, vol. 28, no. 6, pp. 3058-3067, Jun. 2013.

- [11] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Transactions on Industry Applications*, vol. 41, no. 5, pp. 1292-1306, Sep. 2005

- [12] V. Vega-Garita, L. Ramirez-Elizondo, G. R. C. Mouli, and P. Bauer, "Review of residential PV-storage architectures," in *Proc. IEEE Energy Conference*, Leuven, Belgium, 2016, pp. 1-6.

- [13] G. Oriti, A. L. Julian, and N. J. Peck, "Power-electronics-based energy management system with storage," *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 452-460, Jan. 2016.