# INVESTIGATIONS ON MULTILEVEL AND SURGELESS SOLID-STATE CIRCUIT BREAKERS

by

## Tiancan Pang

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2022

| Approved by:            |  |

|-------------------------|--|

| Dr. Madhav Manjrekar    |  |

| Dr. Sukumar Kamalasadan |  |

| Dr. Tiefu Zhao          |  |

| Dr. Meera Sridhar       |  |

©2022 Tiancan Pang ALL RIGHTS RESERVED

#### **ABSTRACT**

TIANCAN PANG. Investigations on Multilevel and Surgeless Solid-State Circuit Breakers. (Under the Direction of Dr. MADHAV MANJREKAR)

The Solid-State Circuit Breaker (SSCB), as an emerging semiconductor-based circuit protection technology, is featured with its extremely fast fault interruption/isolation speed and regarded as a promising alternate to the electromechanical circuit breakers in the DC systems.

However, in the conventional SSCBs, large surge voltages are clamped across their semiconductor switches when the breakers open and the dynamic voltage unbalance is incurred when the series-connected switches are used. With these technical defects, the efficiencies and reliabilities of the SSCBs are impaired and their wide adoption to the DC distribution systems is set back.

To overcome these technical limits of conventional SSCBs, four types of Multilevel and Surgeless Solid-State Circuit Breakers have been proposed in this dissertation. By utilizing the fast switching speeds of the semiconductor switches, the proposed SSCBs can commutate the fault current to the different conduction paths of the circuit breakers and attain significant benefits on efficiency and fault isolation speeds in comparison with the conventional SSCBs. Particularly, for the proposed Multilevel Solid-State Circuit Breaker (MLSSCB), the series-connected switches are clamped to their voltage dividing capacitors during their switching transience and then the dynamic voltage unbalancing issues among the switches can be averted. For the proposed surgeless SSCBs, with surge voltage suppressed, the semiconductor switches do not need to be overdesigned for the voltage ratings and the conduction efficiencies of the SSCBs

can be improved on the ground that the semiconductor device with higher voltage block capability has thicker drift regions and larger on-state resistance. Derived from the integration of the Ground-Clamped Surgeless SSCB and the Multilevel SSCB, the proposed Surgeless Multilevel SSCB (SMLSSCB) can solve both the surge voltage and dynamic voltage unbalancing issues in the medium voltage DC SSCBs and attain higher efficiency and an ultra-fast isolation speed prior to the other SSCBs. A fault-tolerant configuration of the SMLSSCB has also been proposed to improve the reliability of SMLSSCB and make it prior to that of the conventional SSCBs.

In this dissertation, the operating principles of the proposed SSCBs have been presented. Besides, to demonstrate the proposed SSCBs' advantages over the conventional SSCBs on fault isolation speeds, power efficiencies and reliability, the comparisons between the proposed SSCBs and their counterparts of the conventional SSCBs have been made in terms of several key parameters of the circuit breakers. Additionally, the simulation/experiment results and design considerations of the proposed circuit breakers have been introduced to validate their technical feasibilities and practical uses.

#### **ACKNOWLEDGEMENTS**

I would like to first express my deepest thanks to Dr. Madhav Manjrekar, my supervisor, for his continuous help and support in my research and study with his kind patience and immense knowledge. His advice always stimulates my inspiration whenever I meet with obstacles in my research. Without his aid, it would have been impossible for me to have completed this dissertation.

I would also like to extend my deepest gratitude to my dissertation committee members, Dr. Sukumar Kamalasadan, Dr. Tiefu Zhao and Dr. Meera Sridhar for their invaluable suggestions and great assistances to this dissertation and my coursework.

I must also give my thanks to Dr. Ehab Shoubaki, Dr. Somasundaram Essakiappan, Dr. Pankaj Kumar Bhowmik, Dr. Prasanth Kumar Sahu and Dr. Clint Halsted, for their kind help and great encouragement in my research and study.

Last but not the least, I would thank my elite teammates, Sakib Nazmus, Muhammad Foyazur Rahman, Rodney Itiki, Rasik Sarup, Arunodai Chanda, Chandrashekhar Goli and Prithwiraj Roy Chowdhury, for their great friendship and immense help in my research and graduate assistant work.

# DEDICATION

This dissertation is dedicated to my mother, Caixian Li, my father, Dr. Haonong Pang and my partner, Zifen Zeng, for their profound love and great support.

# TABLE OF CONTENTS

| LIST OF TABLES                                                                  | X  |

|---------------------------------------------------------------------------------|----|

| LIST OF FIGURES                                                                 | xi |

| CHAPTER1: INTRODUCTION                                                          | 1  |

| 1.1 Unbalanced and Surge Voltage Issues in Solid-State Circuit Breakers         | 2  |

| 1.2 Proposed Solution to the Dynamic Unbalanced and Surge Voltage Issues        | 5  |

| 1.3 Outline of the Dissertation                                                 | 7  |

| CHAPTER 2: A REVIEW OF SOLID-STATE CIRCUIT BREAKER                              | 8  |

| 2.1 SCR Based Solid-State Circuit Breaker                                       | 9  |

| 2.2 Si IGCT Based Solid-State Circuit Breaker                                   | 15 |

| 2.3 Si IGBT/ SiC MOSFET Based Solid-State Circuit Breaker                       | 18 |

| 2.4 SiC JEFT based Solid-State Circuit Breaker                                  | 23 |

| 2.5 Comparisons of the Reviewed Solid-State Circuit Breakers                    | 26 |

| CHAPTER 3: CONCEPT OF THE PROPOSED MULTILEVEL SOLID-STATE CIRCUIT BREAKER       | 29 |

| 3.1 Conventional Snubber Circuits for Dynamic Voltage Unbalancing Issues        | 30 |

| 3.2 Operating Principle of the Multilevel Solid-State Circuit Breaker           | 31 |

| 3.3 Design Considerations of the Multilevel Solid-State Circuit Breaker         | 38 |

| 3.3.1 Capacitor Selection                                                       | 39 |

| 3.3.2 MOV Selection                                                             | 44 |

| 3.3.3 Power Semiconductor Devices Selection                                     | 45 |

| 3.4 Bi-directional Configurations of the Multilevel Solid-State Circuit Breaker | 46 |

| 3.4.1 Symmetric Bi-directional Multilevel Solid-State Circuit Breaker           | 46 |

| 3.4.2 Hybrid Bi-directional Multilevel Solid-State Circuit Breaker              | 49 |

| CHAPTER 4: CONCEPTS OF THE PROPOSED SURGELESS SOLID-STATE CIRCUIT BREAKERS                                                  | 50 |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 Operating Principle of Surge Voltage Free Solid-State Circuit Breaker                                                   | 51 |

| 4.2 Design Considerations of the Surge Voltage Free Solid-State Circuit Breaker                                             | 56 |

| 4.2.1 Current Limiter Selection                                                                                             | 56 |

| 4.2.2. Semiconductor Switches Selection                                                                                     | 57 |

| 4.3 Comparison between the Surge Voltage Free Solid-State Circuit Breaker and the Conventional Solid-State Circuit Breaker. | 58 |

| 4.3.1 Isolation Time                                                                                                        | 58 |

| 4.3.2 Efficiency                                                                                                            | 61 |

| 4.4 Operating Principle of Ground Clamped Solid-State Circuit Breaker (GCSSCB)                                              | 63 |

| 4.5 Design Considerations of the Ground Clamped Solid-State Circuit Breaker                                                 | 67 |

| 4.5.1 Source resonant capacitor design                                                                                      | 67 |

| 4.5.2 The integration of the Ground Clamped Solid-State Circuit Breaker with buck converter.                                | 70 |

| 4.6 Comparison between the Ground Clamped Solid-State Circuit Breaker and the Conventional Solid-State Circuit Breaker.     | 71 |

| 4.6.1 Isolation Time                                                                                                        | 71 |

| 4.6.2 Surge Protector.                                                                                                      | 72 |

| CHAPTER 5: CONCEPT OF THE PROPOSED SURGELESS MULTILEVEL SOLID-STATE CIRCUIT BREAKER                                         | 74 |

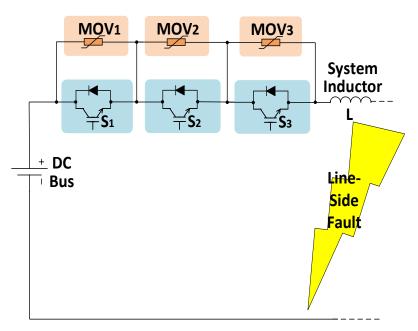

| 5.1 Operating Principles of the Surgeless Multilevel Solid-State Circuit Breaker                                            | 76 |

| 5.2 Design Considerations of the Surgeless Multilevel Solid-State Circuit Breaker                                           | 86 |

| 5.2.1. Snubber Circuit Design                                                                                               | 87 |

| 5.2.2. MOV Selection                                                                                                        | 89 |

| 5.2.3. Capacitor Selection                                                                                                  | 90 |

| 5.3 Comparisons between the Surgeless Multilevel Solid-State Circuit Breakers and the conventional Solid-State Circuit Breaker | 94          |

|--------------------------------------------------------------------------------------------------------------------------------|-------------|

| 5.3.1. Isolation Time                                                                                                          | 94          |

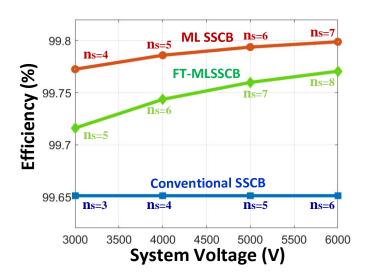

| 5.3.2. Power Efficiency                                                                                                        | 96          |

| 5.4 Bi-directional Configurations of the Surgeless Multilevel Solid-State Circuit Breaker                                      | 100         |

| CHAPTER 6: CONCEPT OF THE PROPOSED FAULT-TOLERANT MULTILEVEL SOLID-STATE CIRCUIT BREAKER                                       | 104         |

| 6.1 Operating Principles of the Fault-Tolerant Multilevel Solid-State Circuit Brea                                             | aker<br>105 |

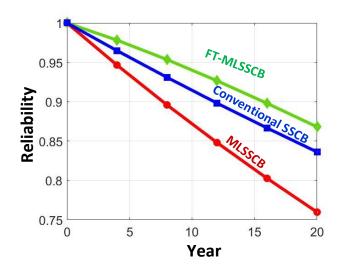

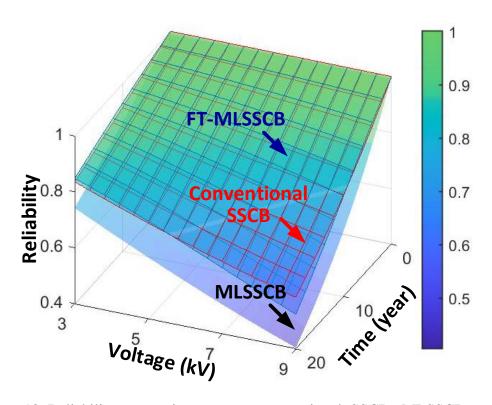

| 6.2 Reliability Analysis of Fault-Tolerant Multilevel Solid-State Circuit Breaker                                              | 117         |

| 6.3 Comparisons between the Fault-tolerant Multilevel Solid-State Circuit Breaker and Conventional Solid-Sate Circuit Breaker  | 122         |

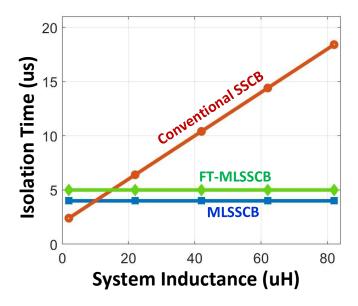

| 6.3.1 Isolation Time                                                                                                           | 122         |

| 6.3.2 Power Efficiency                                                                                                         | 123         |

| CHAPTER 7: CONCLUSION AND FUTURE WORK                                                                                          | 127         |

| REFERENCES                                                                                                                     | 130         |

# LIST OF TABLES

| TABLE 2 - 1: Comparisons among the Reviewed Solid-State Circuit Breakers              | 28  |

|---------------------------------------------------------------------------------------|-----|

| TABLE 3 - 1: Key Parameters in the Simulation Case                                    | 42  |

| TABLE 4 - 1: Key Parameters in the Simulation Case                                    | 53  |

| TABLE 5 - 1: Key Parameters in the Simulation Case                                    | 79  |

| TABLE 5 - 2: Switches Used in Breakers' Efficiency Comparison                         | 97  |

| TABLE 6 - 1: Switches Used in Breakers' Efficiency Comparison                         | 118 |

| TABLE 6 - 2: Quantities of the Components in Conventional SSCB, SMLSSCB and FT-MLSSCB | 120 |

| TABLE 6 - 3: Switches Used in Breakers' Efficiency Comparison                         | 124 |

| TABLE 6 - 4: Comprehensive Comparison of Conventional SSCB, SMLSSCB and FT-MLSSCB     | 126 |

# LIST OF FIGURES

| Figure 1. 1: Simplified schematic of the conventional SSCB with series-connected switches.            | 3     |

|-------------------------------------------------------------------------------------------------------|-------|

| Figure 1. 2: Dynamic voltage unbalancing issue in a conventional SSCB with series-connected switches. | 3     |

| Figure 1. 3: Surge voltage issue in Solid-State Circuit Breaker.                                      | 5     |

| Figure 2. 1: General structure of SSCB.                                                               | 9     |

| Figure 2. 2: Basic SCR based SSCB with forced commutation capacitors.                                 | 11    |

| Figure 2. 3: SCR based SSCB in DC system.                                                             | 12    |

| Figure 2. 4: Z source SSCB.                                                                           | 14    |

| Figure 2. 5: Modified Z source SSCB.                                                                  | 15    |

| Figure 2. 6: Z source SSCB with a coupled inductor.                                                   | 15    |

| Figure 2. 7: RB-IGCT based bidirectional SSCB.                                                        | 17    |

| Figure 2. 8: Bus stray inductor deployment in the parallel IGCT based SSCB.                           | 18    |

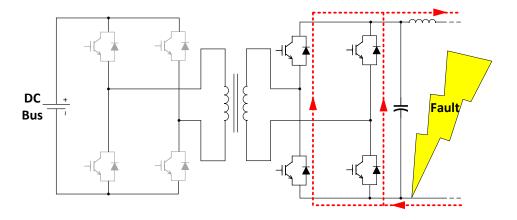

| Figure 2. 9: DAB converter based circuit protection.                                                  | 18    |

| Figure 2. 10: MMC based circuit protection.                                                           | 20    |

| Figure 2. 11: SSCB with self-adapting fault current limiting capability.                              | 21    |

| Figure 2. 12: Surgeless SSCB with grounded MOV.                                                       | 22    |

| Figure 2. 13: Self-powered SSCB.                                                                      | 24    |

| Figure 2. 14: Supercascode SSCB.                                                                      | 26    |

| Figure 3. 1: The conventional capacitive snubber circuit for series-connected switches                | 3. 31 |

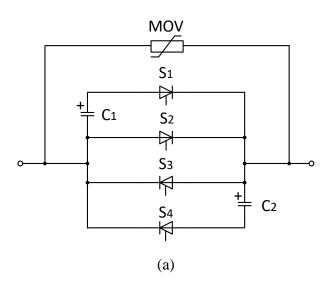

| Figure 3. 2: Multilevel SSCB. (a) 3 level SSCB. (b) n levels.                                         | 32    |

| Figure 3. 3: Subintervals during the MLSSCB's operation.                                              | 34    |

| Figure 3. 4: Simulation waveforms of a 3-level MLSSCB during its circuit breaking process (CDC1 = CDC2 = $0.5$ mF, VDC = $1000$ V, Iload = $40$ A).                                                   | 35 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

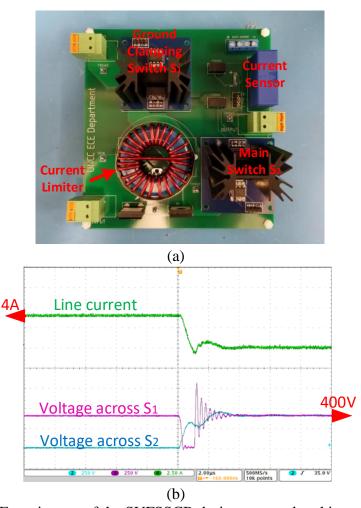

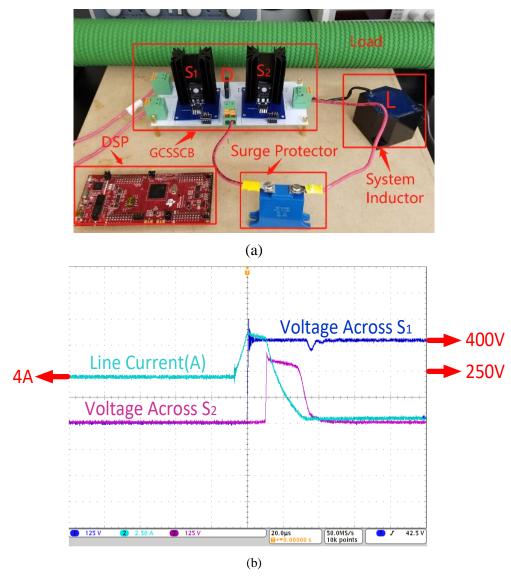

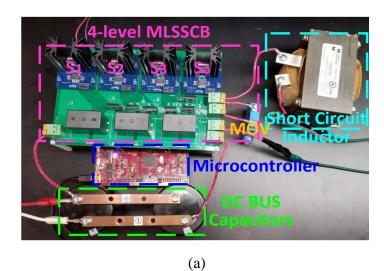

| Figure 3. 5: Experiments of a 3-level MLSSCB during its circuit breaking process ( $C_{DC1} = C_{DC2} = 1$ mF, $V_{DC} = 400$ V, $I_{load} = 4$ A). (a) Experimental setup. (b) Experimental results. | 36 |

| Figure 3. 6: Simulation waveforms of a 3-level MLSSCB during its reclosing process.                                                                                                                   | 36 |

| Figure 3. 7: Simulation waveforms of a 6-level MLSSCB during its circuit breaking process (CDC1 = CDC2 = $12\mu F$ , VDC = $5000V$ , Iload = $300A$ ).                                                | 37 |

| Figure 3. 8: Simulation waveforms of a 6-level MLSSCB during its circuit reclosing process (CDC1 = CDC2 = $12\mu F$ , VDC = $5000V$ , Iload = $300A$ ).                                               | 38 |

| Figure 3. 9: The relationship between <i>iL</i> and <i>iCDC</i> 1.                                                                                                                                    | 40 |

| Figure 3. 10: Simulation case for capacitor design in the MLSSCB.                                                                                                                                     | 43 |

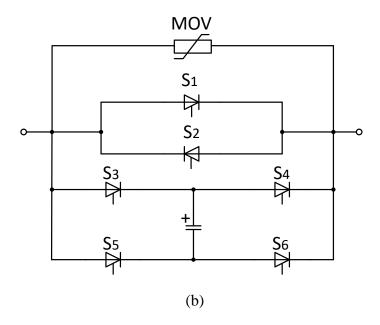

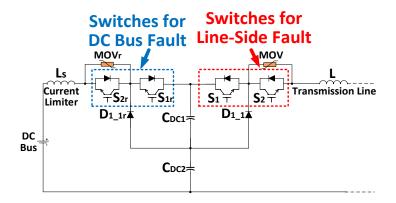

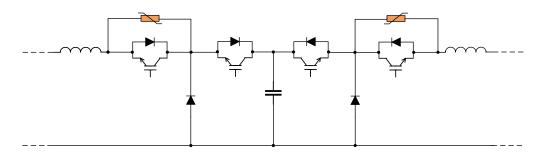

| Figure 3. 11: Symmetrical bidirectional configuration of a 3-level MLSSCB.                                                                                                                            | 47 |

| Figure 3. 12: Series resonant loop of the symmetrical bidirectional MLSSCB during a DC bus fault.                                                                                                     | 47 |

| Figure 3. 13: Hybrid bidirectional configuration of a 3-level MLSSCB.                                                                                                                                 | 49 |

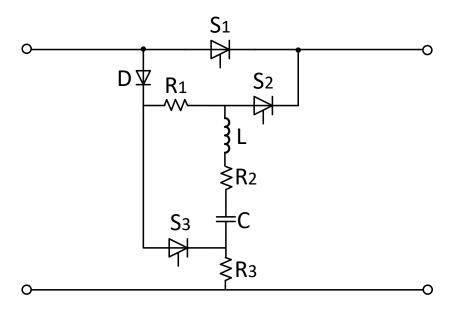

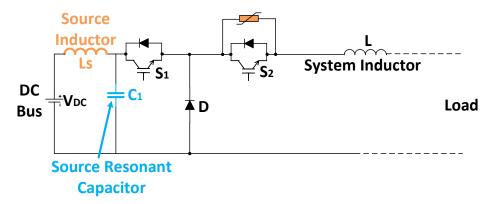

| Figure 4. 1: The topology schematic of the proposed SVFSSCB.                                                                                                                                          | 52 |

| Figure 4. 2: The simulation waveforms of the proposed SVFSSCB.                                                                                                                                        | 53 |

| Figure 4. 3: The subintervals of the SVFSSCB during a line-side fault.                                                                                                                                | 54 |

| Figure 4. 4: Experiments of the SVFSSCB during current breaking process. (a)Experimental setup. (b) Experimental results.                                                                             | 55 |

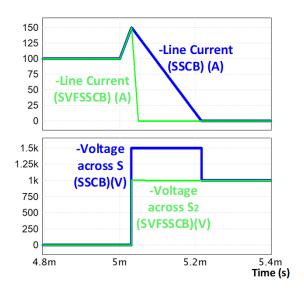

| Figure 4. 5: Comparison between a SVFSSCB and a conventional SSCB.                                                                                                                                    | 60 |

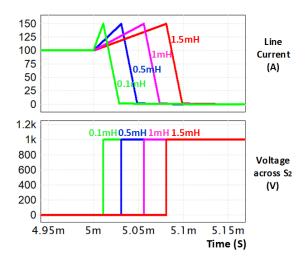

| Figure 4. 6: Switch voltage and line current of the SVFSSCBs having different current limiting inductors (0.1mH, 0.5mH, 1mH and 1.5mH).                                                               | 60 |

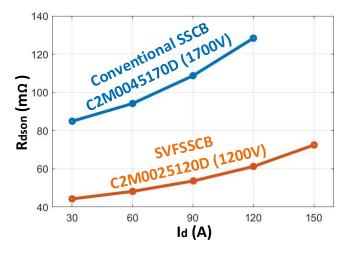

| Figure 4. 7: Comparison between the Rdson of the SiC MOSFETs applied to the circuit.                                                                                                                  | 62 |

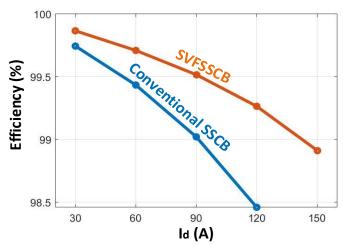

| Figure 4. 8: Comparison between the efficiencies of the SVFSSCB and conventional SSCB. (Vgs = $20V$ , Tj = $150^{\circ}$ C, VDC = $1000V$ ).                                                          | 63 |

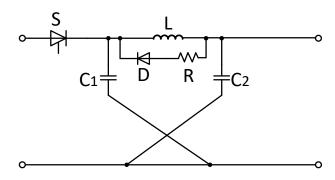

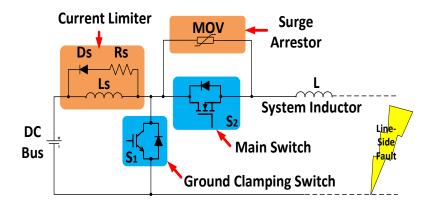

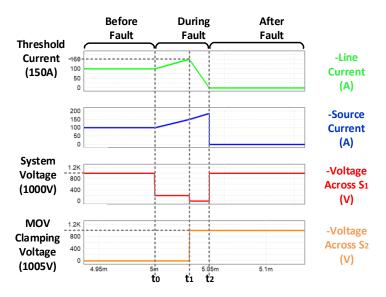

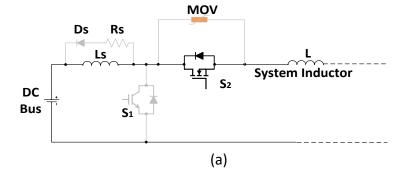

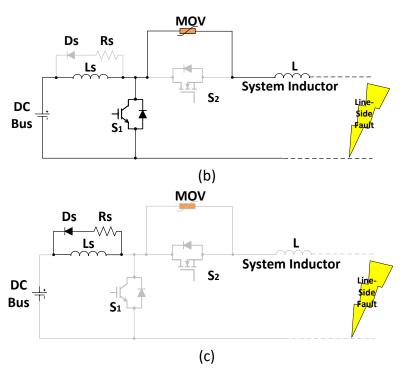

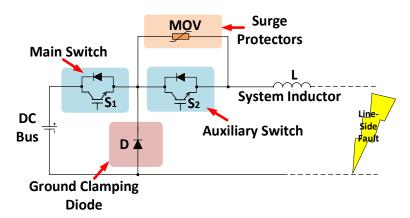

| Figure 4. 9: The simplified schematic of the proposed GCSSCB.                                                                                                        | 64 |

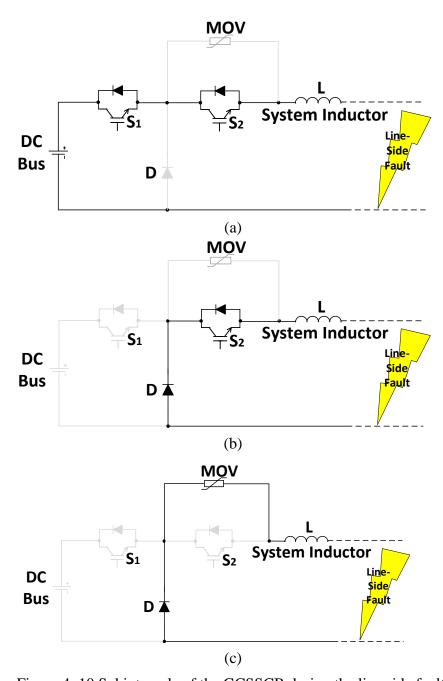

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4. 10: Subintervals of the GCSSCB during the line side fault.                                                                                                 | 65 |

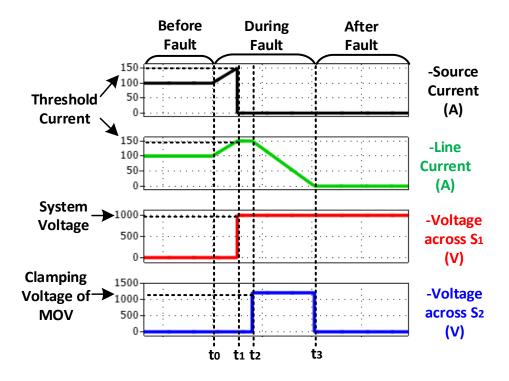

| Figure 4. 11: Simulation results of the GCSSCB during the line side fault.                                                                                           | 66 |

| Figure 4. 12: Experiments of the GCSSCB during a current interruption process. (a) Experimental setup, (b) Experimental results.                                     | 67 |

| Figure 4. 13: Source inductor and source resonant capacitor in GCSSCB.                                                                                               | 68 |

| Figure 4. 14: Oscillation on the switch voltage in a GCSSCB.                                                                                                         | 69 |

| Figure 4. 15: Bidirectional configuration of the GCSSCB.                                                                                                             | 69 |

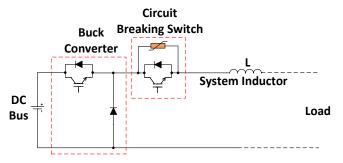

| Figure 4. 16: Buck converter integrated GCSSCB.                                                                                                                      | 71 |

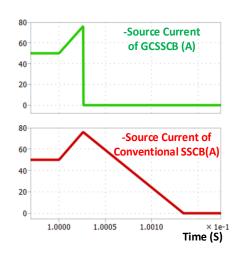

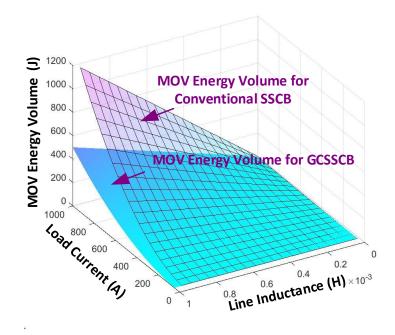

| Figure 4. 17: Simulation waveforms of source current in a conventional SSCB and a GCSSCB.                                                                            | 71 |

| Figure 4. 18: The comparison between the minimum MOV energy volume of a conventional SSCB and a GCSSCB.                                                              | 73 |

| Figure 5. 1: Topology of the conventional medium voltage SSCB using series-connected switches.                                                                       | 75 |

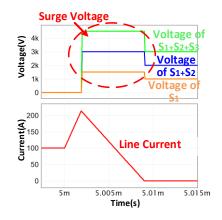

| Figure 5. 2: Simulation results of the conventional medium voltage SSCB.                                                                                             | 76 |

| Figure 5. 3: Simplified schematic of the proposed SMLSSCB (3 levels).                                                                                                | 76 |

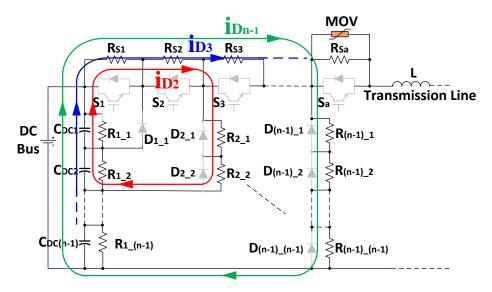

| Figure 5. 4: General structure of the proposed SMLSSCB (n levels).                                                                                                   | 77 |

| Figure 5. 5: Subintervals of a 3-level SMLSSCB during current breaking process.                                                                                      | 81 |

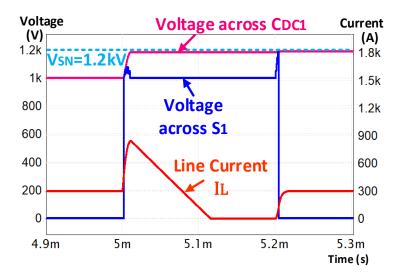

| Figure 5. 6: Simulation waveforms of a 3-level SMLSSCB during current breaking process.                                                                              | 81 |

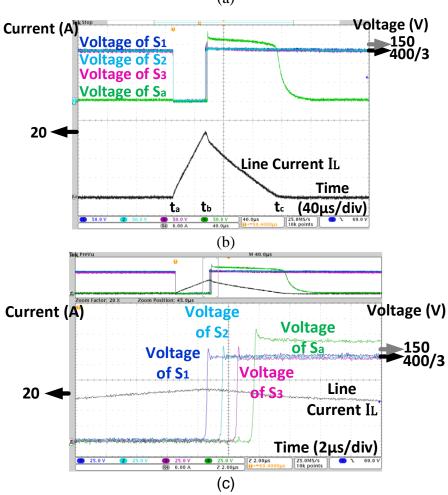

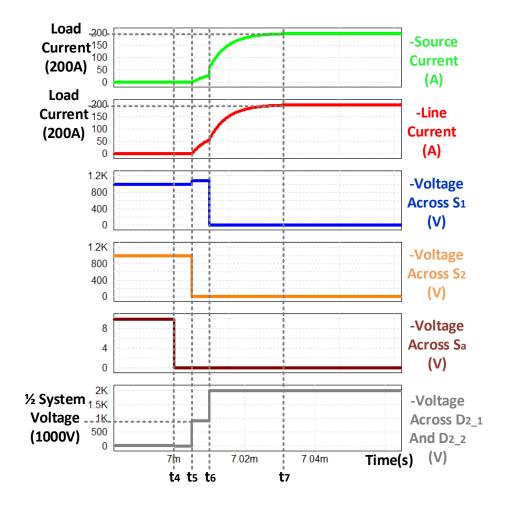

| Figure 5. 7: Experiments of the proposed 4-level SMLSSCB, (a) Experimental Setup. (b) Experimental results during fault current interruption, 40μs/div. (c) 2μs/div. | 82 |

| Figure 5. 8: Simulation waveforms of a 3-level SMLSSCB during circuit reclosing process.                                                                             | 85 |

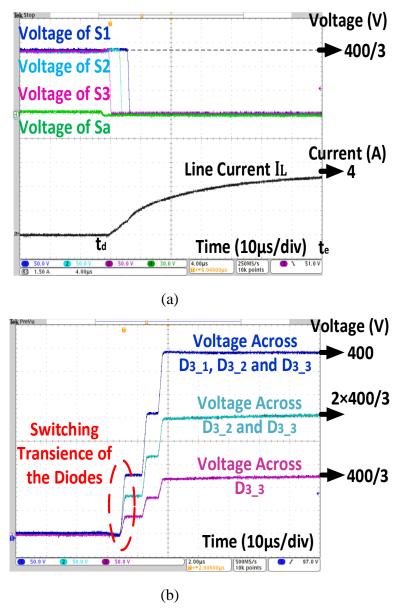

| Figure 5. 9: Experimental results of the 4-level SMLSSCB during circuit reclosing. (a) Switches' voltages and line current. (b) Diodes' voltages.                    | 86 |

| Figure 5. 10: The conduction loops of the diode's snubbers when the breaker opens.                                                                                   | 88 |

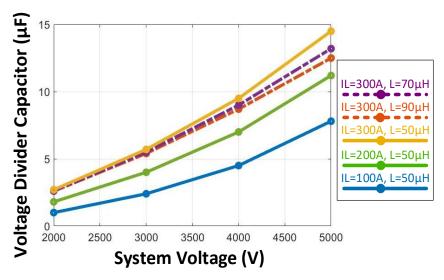

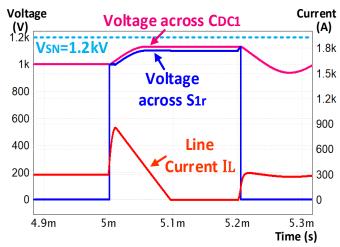

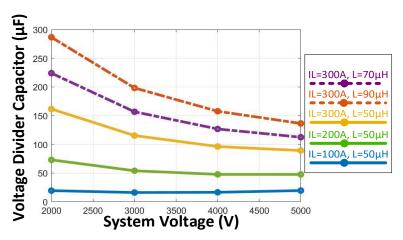

| Figure 5. 11: Minimum capacitances in voltage divider for proposed SMLSSCBs in typical medium voltage DC distribution systems.                                     | 93  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5. 12: Voltages across CDC1 and S1 during the operation of the 6-level SMLSSCB in a 5000 V, 300 A and 50 $\mu H$ applied system.                            | 93  |

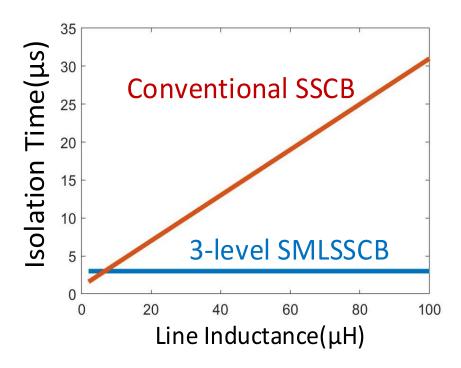

| Figure 5. 13: Comparisons between the isolation time of a conventional SSCB and that of a 3-level SMLSSCB in a 2000 V 200 A DC system.                             | 95  |

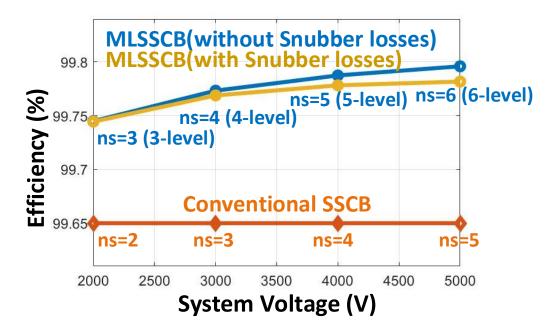

| Figure 5. 14: Comparison between the efficiencies of the proposed SMLSSCB and those of the conventional SSCB ( $IL = 50 \text{ A}$ ).                              | 99  |

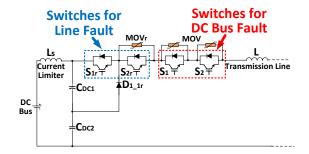

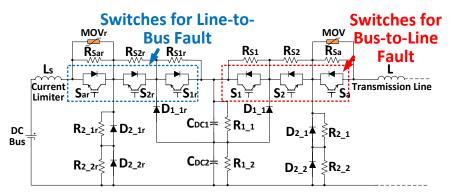

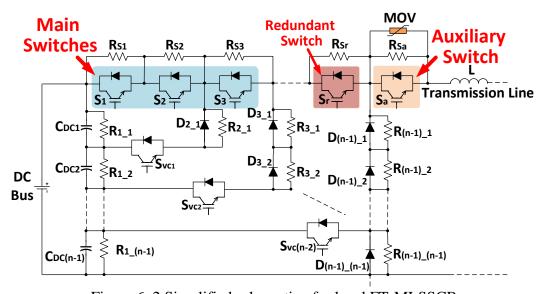

| Figure 5. 15: Symmetrical bidirectional configuration of a 3-level SMLSSCB.                                                                                        | 100 |

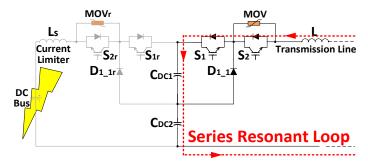

| Figure 5. 16: Series resonant loop of the symmetrical bidirectional SMLSSCB during a line-to-bus fault.                                                            | 100 |

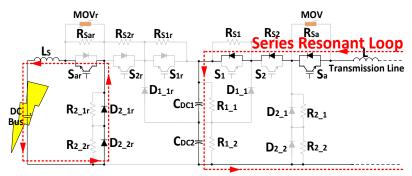

| Figure 5. 17: Voltages across CDC1 and S1r during the operation of the symmetrical bidirectional 6-level SMLSSCB in a 5000 V, 300 A and 50 $\mu H$ applied system. | 103 |

| Figure 5. 18: Minimum voltage divider capacitances of the symmetrical bidirectional SMLSSCBs in typical medium voltage DC systems.                                 | 103 |

| Figure 5. 19: Hybrid bidirectional configuration of a 3-level SMLSSCB.                                                                                             | 103 |

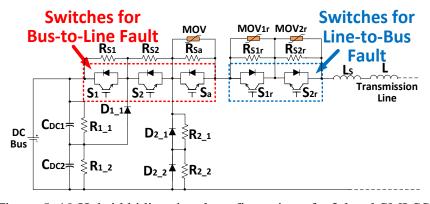

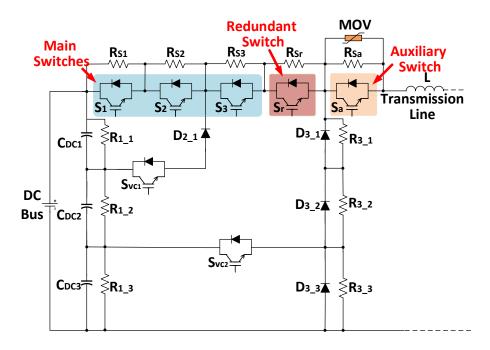

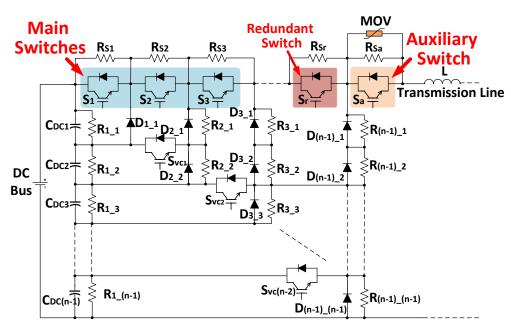

| Figure 6. 1: Simplified schematic of 4-level FT-MLSSCB.                                                                                                            | 106 |

| Figure 6. 2: Simplified schematic of n-level FT-MLSSCB.                                                                                                            | 106 |

| Figure 6. 3: Subintervals of a 4-level FT-MLSSCB during current breaking process.                                                                                  | 109 |

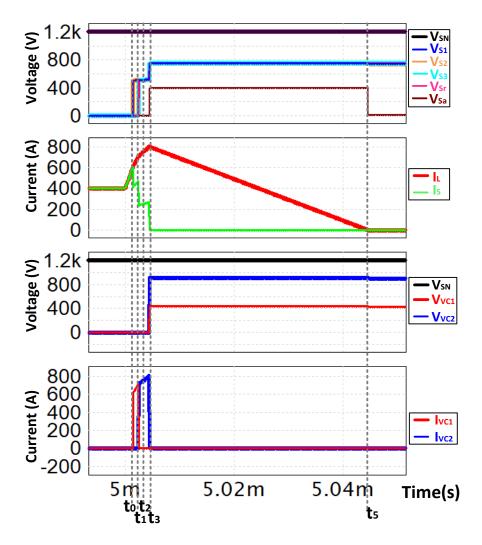

| Figure 6. 4: Simulation waveforms of a 4-level FT-MLSSCB during current breaking process.                                                                          | 110 |

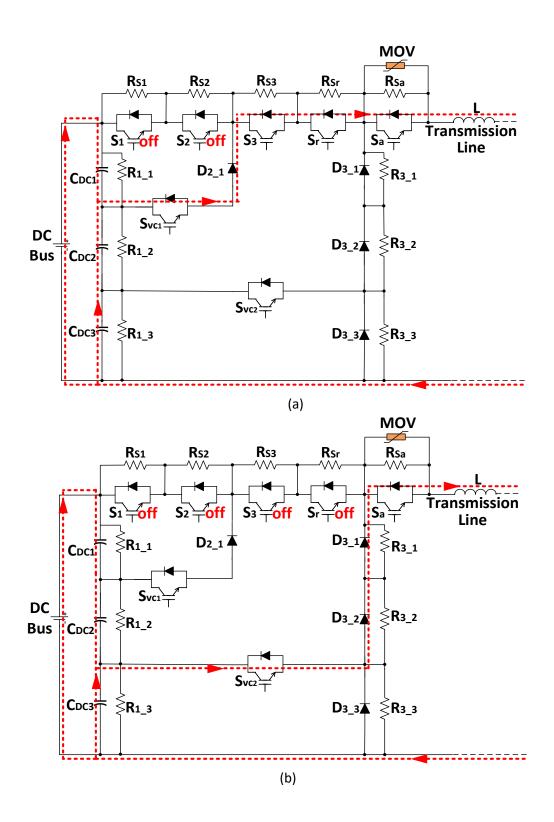

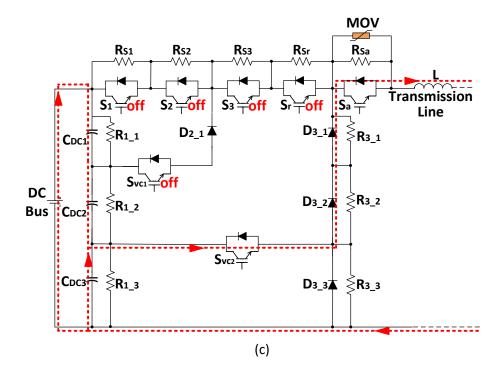

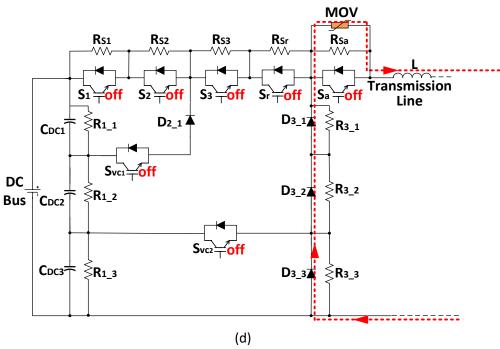

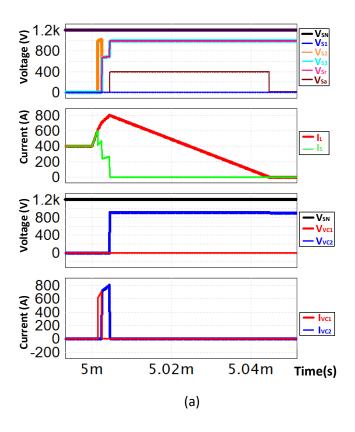

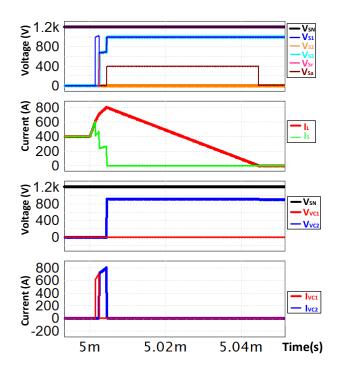

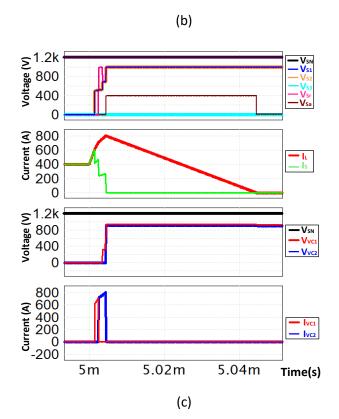

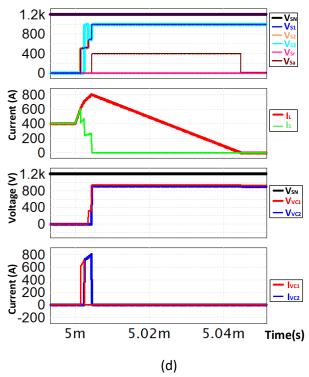

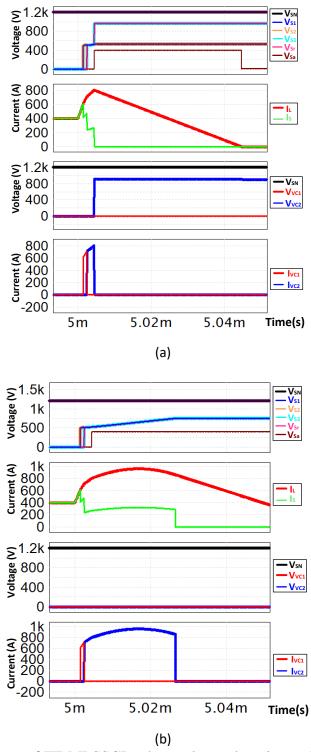

| Figure 6. 5: Simulation results of FT-MLSSCB under fault tolerant operations. (a) S1 fails. (b) S2 fails. (c) S3 fails. (d) Sr fails.                              | 113 |

| Figure 6. 6: Operations of FT-MLSSCB when voltage clamping switches in short failure. (a) <i>SVC1</i> fails. (b) <i>SVC1</i> and <i>SVC2</i> fails.                | 114 |

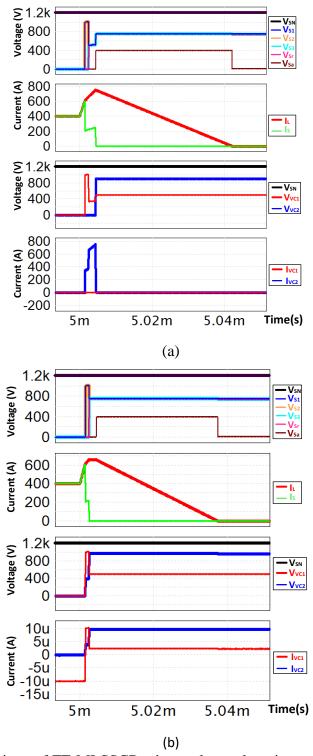

| Figure 6. 7: Simplified schematic of n-level FT-MLSSCB with voltage clamping diode.                                                                                | 115 |

| Figure 6. 8: Operations of FT-MLSSCB when voltage clamping switches in open failure. (a) SVC1 fails. (b) SVC1 and SVC2 fails.                                      | 116 |

- Figure 6. 9: Reliability comparison among conventional SSCB, MLSSCB and FT-MLSSCB in 4kV.

- Figure 6. 10: Reliability comparison among conventional SSCB, MLSSCB and FT- 121 MLSSCB in higher voltages.

- Figure 6. 11: Isolation time comparisons among conventional SSCB, MLSSCB and 123 FT-MLSSCB.

- Figure 6. 12: Comparison among the efficiencies of conventional SSCB, SMLSSCB 125 and FT-MLSSCB (IL = 50 A).

#### CHAPTER1: INTRODUCTION

Recently, great interests have been aroused in DC distribution systems because of their high efficiency and flexibility in the integrations of renewable energy resources and electronic loads [1] [2]. However, resulting from the absence of the natural zero-crossing points of current/voltage, the limited over-current-sustaining capability of the power converters and the relatively small inductances of the power cables, the DC systems have a high demand on the response speeds of their circuit protection devices. The conventional electromechanical circuit breakers that have been time-tested in AC systems have their operation speed limited by the critical momentum of their movable parts and are incompetent to protect the DC systems in many cases [3]. As a result, the DC circuit protection has become a well-known challenging problem hindering the deployment of the DC distribution systems.

The Solid-State Circuit Breaker (SSCB), as an emerging semiconductor-based circuit protection technology, is featured with its extremely fast current interrupting speed and regarded as a promising solution to the protection problems in the DC systems [4] [5].

However, due to the system line inductances, surge voltages are induced across the SSCBs when they interrupt the current. Although the MOVs are used in the SSCBs to clamp the surge voltages under the appliable voltage ranges of the semiconductor devices, the clamped surge voltages are still significantly higher than the system voltages to attain the fast isolation speeds and avert the premature aging on the MOV. As a result, the semiconductor switches of the SSCBs have to be overdesigned in terms of their voltage ratings to sustain the surge voltages, which may seriously impair the efficiencies of the circuit breakers.

On the other hand, with the increment of the system voltages, series-connected switches are needed in the SSCBs. Nevertheless, due to the mismatch of the switches' parasitic capacitances and the turn-off delays originating from the gate drivers, the series-connected switches may fail to turn off simultaneously and incur harmful dynamic unbalanced voltage.

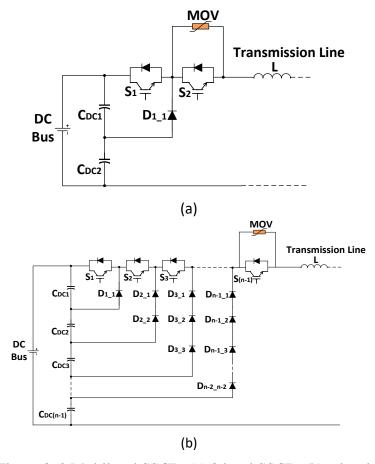

To deal with these issues in the different applications of DC distributions, several new topologies of solid-state circuit breakers have been proposed in this dissertation, namely Multilevel Solid-State Circuit Breaker, Surge Voltage Free Solid-State Circuit Breaker, Ground Clamped Solid-State Circuit Breaker and Surgeless Multilevel Solid-State Circuit Breaker. Besides, to compensate the deficiency of reliability caused by the advanced topologies, a fault-tolerant configuration of Surgeless Multilevel Solid-State Circuit Breaker has been proposed. The operating principles, simulation/ experiment results, design considerations of the proposed SSCBs have been presented to validate their technical feasibilities and practical values.

## 1.1 Unbalanced and Surge Voltage Issues in Solid-State Circuit Breakers

In the medium voltage DC systems, the operating voltages vary from 1kV to 35kV, but the maximum voltage ratings of the commercially available monolithic IGBT modules usually range from 6.5-8.5kV [6]. The wide-bandgap semiconductors, such as SiC MOSFETs and SiC JFETs, which have a great potential in the SSCB applications because of their low on-state resistances and high junction temperature tolerances, have theoretically higher voltage-blocking capability than the Si switches, but, due to the limitation of the current manufacture crafts, the voltage ratings of their existing

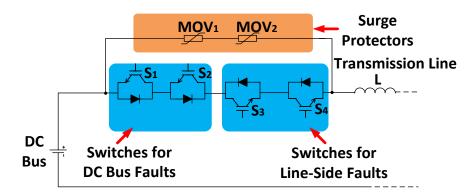

commercial products are commonly set only at 1.2 and 1.7kV [7] [8]. Besides, due to the larger chip thickness and lower manufacturing yield, the costs of the high-voltage modules are much higher than that of their series-connected low-voltage counterparts. As a result, series-connected switches as in Figure 1. 1 appear to be an option more applicable to construct the medium-voltage DC SSCBs [9] [10] [11].

Figure 1. 1 Simplified schematic of the conventional SSCB with series-connected switches.

Figure 1. 2 Dynamic voltage unbalancing issue in a conventional SSCB with series-connected switches.

Same as in the other applications of power electronics, the voltage unbalancing among the series-connected switches is also a big concern in SSCBs. Due to the mismatches of the operating speeds of the semiconductor switches and their gate drivers, the series-connected switches may fail to turn off simultaneously during the current interruption of the breaker [12] [13]. As a result, dynamic overvoltage arises across a single switch as shown in Figure 1.2. The overvoltage may exceed the voltage blocking limits of the applied semiconductor switch and cause the failure of the protection.

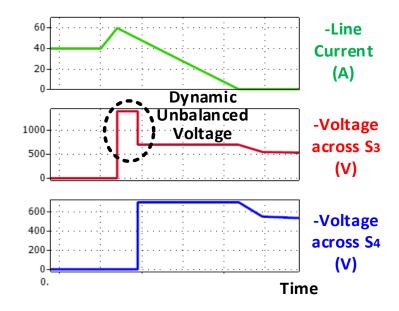

On the other hand, in SSCBs, back Electromotive Forces (EMF) need to be synthesized across the breakers to absorb the electromagnetic energy stored in the system inductors and ultimately clear the fault current. For the conventional SSCBs, their isolation time changes reversely with the back EMF synthesized from the difference between the clamped surge voltage and the system voltage. In that case, to isolate the faults with a fast speed, the clamping voltages of the surge arrestors in the SSCBs are expected to be much higher than the system voltage [14]. Besides, almost all the commercially available MOVs have clamping voltages much higher than their continuous rated voltage to avert the premature aging on the MOVs during their standby phase [15] [16]. Thus, after MOVs are selected with continuous rated voltages conforming to their system voltages, their clamping voltages will be much higher than the system voltage and enforce the switches in the SSCBs to sustain large surge voltage. Some previous works reduce the surge voltage value of their SSCBs by using the MOVs with continuous rated voltages lower than their applied system voltages. The downsizing of the MOVs causes their repeated intervention after the breakers open and seriously impairs the life spans of the MOVs along with the reliabilities of the SSCBs. For these reasons, large surge

voltage is imposed on the semiconductor switches of the SSCBs as shown in the operating waveforms in Figure 1. 3 [17]. Accordingly, the voltage ratings of the switches cannot be selected as regards their shared system voltages like that in other power electronic applications, but always have to be overdesigned according to their surge voltage values. As the same type of power semiconductor switches with higher breakdown voltages have higher drain-source on-state resistances along with higher cost caused by their thicker drift regions and larger chip thickness, the large surge voltages imposed on the conventional SSCBs seriously impair the efficiencies and cost effectiveness of the breakers.

Figure 1. 3 Surge voltage issue in Solid-State Circuit Breaker.

## 1.2 Proposed Solution to the Dynamic Unbalanced and Surge Voltage Issues

A Multilevel Solid-State Circuit Breaker (MLSSCB) has been proposed in this dissertation to deal with the dynamic voltage unbalancing issue of the series-connected switches. In the proposed MLSSCB, switches are clamped to the voltage dividing

capacitors after they turn off and therefore do not incur dynamic voltage unbalances. Besides, during the operations of the breaker, the switches can be turned off sequentially with significant time differences and basic gate drivers with inherent different working delays can be used in the MLSSCBs. After that, to alleviate the surge voltage across the SSCBs during their operations, two Solid-State Circuit Breaker named Voltage Free Solid-State Circuit Breaker (SVFSSCB) and Ground Clamped Solid-State Circuit Breaker (GCSSCB) have been proposed in this dissertation. In the SVFSSCB, the DC source is actively grounded to minimize the surge voltage on the semiconductor devices during the energy absorbing phase. In the GCSSCB, as its ultrafast fault isolation speed is decoupled from the clamping voltage of its MOV, the MOV and its auxiliary switch can be rated at low voltages and the surge voltage across the breaker can be effectively suppressed. Afterward, by integrating the GCSSCB with the MLSSCB, a Surgeless Multilevel Solid-State Circuit Breaker (SMLSSCB) has been derived to effectively solve both the surge voltage and dynamic voltage unbalancing issues of the conventional SSCB technologies in medium voltage DC distribution systems. Compared to the MLSSCB in the same operating scenarios, the SMLSSCB has faster isolation speed as well as lower demands on the voltage dividing capacitors. Furthermore, compared to the conventional SSCBs, SMLSSCB exhibits both higher efficiency and faster isolation speed. At last, a Fault-Tolerant Multilevel Solid-State Circuit Breaker has been proposed that inherits all the technical advantages of SMLSSCB and also has significantly higher reliability through the fault-tolerant operations.

#### 1.3 Outline of the Dissertation

The rest of the dissertation is organized as follows. In Chapter 2, a review of the latest technologies of SSCBs is made including SCR based SSCB, Si IGCT based SSCB, Si IGBT/SiC MOSFET based SSCBs and SiC JFET based SSCB. The comparisons among the circuit breakers are also included in the chapter. In Chapter 3, the Multilevel Solid-Solid State Circuit Breaker (MLSSCB) is proposed. The operating principle, design considerations and bi-directional configuration of the MLSSCB are discussed in the chapter. In Chapter 4, the operating principles of two surgeless Solid-State Circuit Breakers are presented along with their design considerations and their comparisons with the conventional SSCBs. Chapter 5 presents the concept of the Surgeless Multilevel Solid-State Circuit Breaker (SMLSSCB). The breaker's operating principles, design considerations, comparisons with the conventional SSCB and bi-directional configurations have been dealt with. Chapter 6 introduces the fault-tolerant configuration of the SMLSSCB, or Fault-tolerant Multilevel Solid-State Circuit Breaker (FT-MLSSCB). The operating principle of the breaker has been presented with the simulation results. The comparisons among FT\_MLSSCB, SMLSSCB and conventional SSCB have been made on their reliabilities, efficiencies and isolation speeds. Eventually, a chapter of conclusion and future work has been presented.

#### CHAPTER 2: A REVIEW OF SOLID-STATE CIRCUIT BREAKER

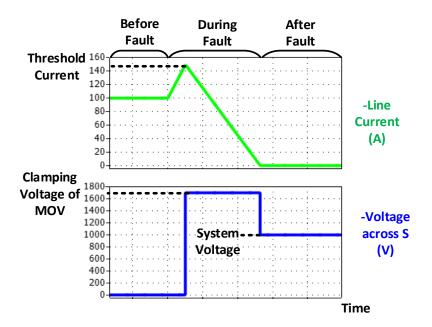

Solid-State Circuit Breaker (SSCB) is an emerging circuit protection technology implementing power semiconductor switches. Unlike the electromagnetic circuit breakers, the SSCBs have no movable units and do not induce electric arc during their current interruption. Besides, thanks to the shorter switching transience of the semiconductor switches, the SSCBs can interrupt fault current in a speed several order of magnitude faster than the mechanical circuit breakers. Moreover, with a high controllability of their semiconductor switches, the SSCBs can perform advanced functions including remote operation, dynamic time-current curve adjustment and system soft start [18].

The general structure of the conventional SSCB is as shown in Figure 2.1. In the figure, the SSCB is mainly composed of semiconductor switches, surge arrestors, current sensors, controller and gate drivers. During normal operation, the semiconductor switch turns on and have load current conduct through it. When a fault happens, the line current starts to increase and gets monitored by the current sensor. Once the current value increases to be higher than the preset threshold, the controller will generate a trip signal to turn the semiconductor switch off and interrupt the increment of the fault current immediately. After that, the fault current is transferred to the surge arrestor where the surge voltage caused by the stray line inductor is clamped. After the surge arrestor absorbs all the energy stored in the line inductor, the line current is cleared and the fault is isolated from the normally operating areas of the system.

Theses years, studies of SSCBs have been mainly focused on introducing emergent semiconductor technologies and developing new circuit topologies aiming to improve the breakers' conducting efficiencies, operating speed and cost effectiveness. As

the topologies of the SSCBs usually varies with the characteristics of their applied switches, in this dissertation, the review of the SSCBs is categorized by the implemented semiconductor switches in the circuit breakers.

Figure 2. 1 General structure of SSCB

#### 2.1 SCR Based Solid-State Circuit Breaker

Silicon Controlled Rectifier (SCR) is a type of thyristor that have been widely used in power electronics application for rectification of AC to DC. Due to its relatively low conduction loss, high operating power range and low material cost, SCR has been seen as an applicable option to construct SSCBs. As the SCR cannot be actively turned off by its gate signal, an extra auxiliary circuit known as force commutation circuit needs to be designed to forcedly commutate the current thorough the SCR to zero and then turn the circuit breaker off. Owing to the rarity of the switching activity in the SSCB applications, the commutation circuit for the SCR in SSCBs can be well simplified compared to those in power rectifiers.

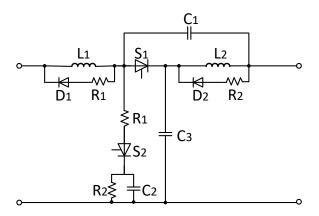

The simplified schematic of the SCR based SSCBs with basic commutation circuit are shown in Figure. 2.2(a) and (b). In Figure. 2.2(a), the SSCB consists of two antiparallel SCR as its main current conduction paths, two fully controlled switches in series with commutation capacitors as auxiliary paths and a MOV as surge arrestor. During normal operations, SCRs turn on, the auxiliary switches turn off and the load current follows through the SCRs bidirectionally. When the fault happens, the auxiliary switches turn on and provide discharging loop for the commutation capacitors and forcedly transfer the line current from SCRs to the auxiliary paths. After the current through the SCR decreases to zero, the auxiliary switches turn off and transfer the line current to the MOV. Eventually, the line inductor is demagnetized and the breaker clears the line current. To decrease the number of the commutation capacitors and shorten the capacitors' pre-charging periods, a SCR based SSCB with a H-bridge commutation circuit has been introduced as shown in Figure 2.2(b). In the breaker, only a single capacitor is used but, in exchange, two more auxiliary switches are needed to convert the current through the capacitor.

Figure 2. 2 Basic SCR based SSCB with forced commutation capacitors.

As the following basic SCR based SSCBs cannot have their commutation capacitors charged by a unidirectional source current, the SSCBs are more suitable for AC systems. In DC application, additional power supplies are needed to pre-charge the commutation capacitors. Although in Figure. 2.2(b), the capacitor can be charged by DC current after adjusting the operating quadrant of the auxiliary switches, additional control loop along with sensors are needed to regulate the pre-charged voltage value.

Several ways have been presented to design SCR based SSCBs without external pre-charging circuits [19]. Nevertheless, these breakers can only charge their commutation capacitors after the breaker closes which enhances the risks of their failure during the reclosing process [20] [21]. A large capacitance can alleviate the drawback, but will compromise the compactness of the breaker.

Lately, a novel SCR based SSCB has been proposed that can charge its commutation capacitor during the period when the breaker is off and do not need extra sensor and source to interrupt current under DC sources. The simplified schematic of the

breaker is drawn in Figure 2.3. All the switches in the breaker are SCRs. During normal operation, the switch,  $S_1$ , turns on and conducts load current. When the fault happens, the switches,  $S_2$  and  $S_3$ , turn on simultaneously and allow the capacitor provides a reverse current to offset the current through  $S_1$ . After the current of  $S_1$  decreases to zero, a resonant loop of the commutation capacitor and line inductor is produced. Once the resonance damps, the switches  $S_2$  and  $S_3$  turn off. At the same time, the diode, D, conducts and recharges the commutation capacitor by the DC source. During the operation of the breaker, the charging/discharging periods of the capacitor need to be compatible to the reverse recovery of the SCR switches and the resonance of the line current. Therefore, the design of the commutation capacitor in the breaker is very challenging to the breakers operating in a wide range of current rating. In addition, as the line current can be eventually cleared only after the resonances between the capacitor and line current are damped, the responding and isolating time of the breaker are significantly longer than the basic SCR SSCBs.

Figure 2. 3 SCR based SSCB in DC system.

To attain a fast fault responding and isolating speed, a series of SCR based SSCB named Z-source SSCB has been proposed arousing the great interests in academia. Compared to the other SCR based SSCB, the Z source SSCB operates autonomously when the fault happens and therefore can have a much faster operating speed. It is worthwhile mention that although the Z source SSCBs do not need control signals to trip their current breaking operation, but they still need sensors and controllers to assist grounding the gate signal of the SCR after the device's current decreases to zero. The schematic of the original Z source SSCB is as shown in Figure. 2.4. In normal situation, load current follows through the SCR and the two inductors in the breaker. At the moment when a fault occurs, the line current starts to conduct through the capacitors in the breaker in that the current increasing rate in the capacitors can be much larger than that in the inductors. Since the total capacitor voltage is twice of the source voltage, the SCR is reverse biased and its current drops to zero at a very fast speed. After that, the fault area is isolated from the DC source and the inductor is resonant with the capacitor until the diode-resistor branch damps the inductor current to zero. From its working principle, the Z source SSCB operates only when the increasing rate of the fault current is sufficiently high. For the fault current having slower transience, the Z source breaker may fail to respond and result in the extension of the faults. Besides, the following researches show that the Z source SSCB also fails to operate when the amplitude of the fault current is not prominent compared to the load current [22].

Several methods have been presented to improve the controllability of the Z source SSCB and make them to operate successfully in different fault scenarios. In [22], the circuit topology modified from the original Z source SSCB has been proposed as in

Figure 2.5. The operating principle of the breaker is similar to the original one except a common ground for the source and the power ground is attained by making a tradeoff of a little isolation speed. Besides, an additional grounding switch is added in the circuit as  $S_2$  in Figure 2.5 to actively ground the Z source SSCB when a fault is detected by the relay and enforce the breaker to operate in less severe fault scenario. In addition, the boundary of the minimum fault current amplitude and ramp rate for the breaker to spontaneously operate has been derived in the paper to determine the working range for the active grounding switch and optimize the responding speed of the breaker. In [23], a Z source breaker with a coupled inductor has been proposed as shown in Figure 2.6. The threshold current value for the breaker's spontaneous operation can be set by adjusting the turn ratio of the coupled inductor. In that case, the controllability of the Z source SSCB can be further improved.

Figure 2. 4 Z source SSCB.

Figure 2. 5 Modified Z source SSCB.

Figure 2. 6 Z source SSCB with a coupled inductor.

Except for the controllability issues, the passive component selection is also a big concern in Z source SSCBs. Since the inductor in the breaker conducts continuous current in normal situations, the size of the inductors and capacitors may be unacceptably large in the applications with high voltage and current ratings.

## 2.2 Si IGCT Based Solid-State Circuit Breaker

The Integrated Gated-Commutated Thyristor (IGCT) is a type of semiconductor switch related to Gate Turn-Off (GTO) Thyristor. After it is turned on, the IGCT device

operates in deep latch-up mode and has generally higher conduction efficiencies in comparison with their counterparts of fully controlled switches, such as IGBT and MOSFET switches. In exchange, the switching losses of the IGCT switches are relatively higher. With the above attributes, the IGCT devices are well suitable for the applications of SSCB where the switching frequency is extremely low and conduction loss dominate the power losses. In [24], a 2.5kV IGCT switch was applied to a SSCB. Under a testing scenario of 1kV/1.5kA DC system, the on-state voltage across the IGCT device is only 0.9 V, which translates into a principal power efficiency of 99.9%. In [25], a new IGCT semiconductor device named Low On-state voltage Integrated Gate-Commutated Thyristor (LO-IGCT) has been proposed specified in SSCB applications. In the device, the on-state voltage is optimized by reducing the total base length, lowering the doping rate in the base region and prolonging the bipolar length. Although the switching power needed for the device turns out to be higher than the standard IGCT switches, it is not a big concern in the SSCBs. As shown in the experimental results in [25], the proposed LO-IGCT device maintains a significantly lower on-state voltage in a wide range of operating currents compared to the commercialized IGCT switches.

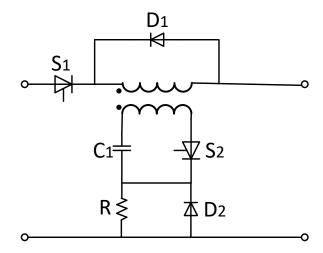

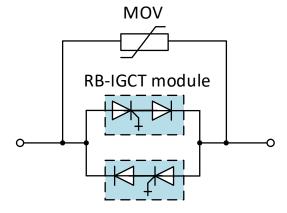

Except for the material characteristics of the IGCT devices, their potential of bidirectional voltage blocking also makes them suitable for the SSCB applications. By integrating its die with a diode, the IGCT device can attain the reverse voltage blocking capability and have a substantial reduced power loss. This type of IGCT switch with expanded operating quadrant is named Reverse Blocking IGCT (RB-IGCT) switch. The RB-IGCT switches can construct bidirectional SSCBs with antiparallel configuration as shown in Figure. 2.7. Compared to IGBT based bidirectional SSCB with two back-to-

back switches, the RB-IGCT based SSCB has one less semiconductor device on its conduction path and therefore can attain improved power efficiency.

In SSCBs, parallel connected switches are applied to enhance their current interrupting limits. However, when it comes to the IGCT devices, due to their negative temperature coefficients, their parallel connection cannot attain a balanced current sharing and may cause over current and temperature imposed on a single switch. In [26], mathematic model has been determined to quantify the effect of the bus bars' stray inductors on the transient current deviation among the devices. Besides, the effectiveness of the devices' threshold voltage, on-state resistance and negative temperature coefficient on the steady-state current sharing of the devices are also discussed. In the paper, the current balancing among three parallel connected 5kA rated IGCT devises is roughly achieved under a 15kA load current by matching the devices' characteristics and carefully deploying bus stray inductors in the breaker as shown in Figure 2.8. Nevertheless, under a long term of operation, the negative temperature coefficient may still compromise the static current balance of the switches. Besides, the current deviation to the changing rate of the current still needs to be further studied.

Figure 2. 7 RB-IGCT based bidirectional SSCB.

Figure 2. 8 Bus stray inductor deployment in the parallel IGCT based SSCB

## 2.3 Si IGBT/ SiC MOSFET Based Solid-State Circuit Breaker

Insulated-Gate Bipolar Transistor (IGBT) and Metal–Oxide–Semiconductor Field-Effect Transistor (MOSFET) are two types of the most-commonly applied semiconductor devices in power converters due to their high technical maturity and low manufacturing cost. IGBTs utilize conduction modulation to attain lower conduction losses [27]. On the other hand, although MOSFETs which are unipolar devices cannot use conductivity modulation to improve their conduction efficiencies, they may take lower conduction losses than their IGBT counterparts by applying Silicon Carbide (SiC)

Figure 2. 9 DAB converter based circuit protection.

material [28] [29]. The applications of Si IGBT and SiC MOSFET in solid-state circuit protection have been widely discussed in both industries and academia. The recent studies of the area represent two main trends.

The first is to integrate the circuit protecting function into the power converters and use IGBT/MOSFET in the converters to interrupt the fault current. In [30] [31], a Dual-Active-Bridge (DAB) DC/DC converter has been used to clear a fault happening on the DC microgrid as in Figure 2.9. When there is a fault happening, all the switches of the DAB converter are tripped off and the power source from the AC grid is isolated from the fault through the switches in the inverter phase of the converter. In other words, only the DC bus capacitor, C<sub>2</sub>, supplies the fault current. After all the energy stored in the capacitor is discharged, the line current stops increasing and conducts through the freewheel diodes of the DAB converter as highlighted in Figure 2.9. Eventually, the line current is cleared after the line inductive energy is dissipated by the internal resistor of the power cable.

In the DAB converter based circuit protection, the fault current following through the converter can be interrupted but the line current is only interrupted after the DC bus voltage reduces to zero. Thus, the protection scheme may fail to interrupt the fault current before it increases too much when the fault spot is close to the DC bus. To avert the problem, in [32] [33], the Modular Multilevel Converter (MMC) with H-bridge submodules is used to interrupt the line current when a fault occurs on its DC bus. During the fault, all the switches in the MMC turn off and the current through the MMC is transferred to the conduction loop charging the submodule capacitors as in Figure 2.10. Since then, the increment of the fault current ceases and the DC voltage twice as high as

the original DC bus voltage can be synthesized across the AC source and the line inductor. Consequently, a large negative EMF is introduced over the faulted line and the fault current decreases to zero after the line inductor is demagnetized. Although the H-bridge based MMC can effectively interrupt its line current, it has to use much more power switches than the other half-bridge MMC and correspondingly brings about much higher material costs and conduction losses. Besides, as the back EMF across the faulted line is synthesized by the capacitors in the converter, the capacitance and size of the capacitors needs to be larger for avoiding the overcharge of the capacitors during the fault interruption. For the reasons mentioned above, nowadays, the converters alone can hardly execute effective circuit protection and so the independent SSCBs are seemed to be a more practical way to perform solid-state circuit protection.

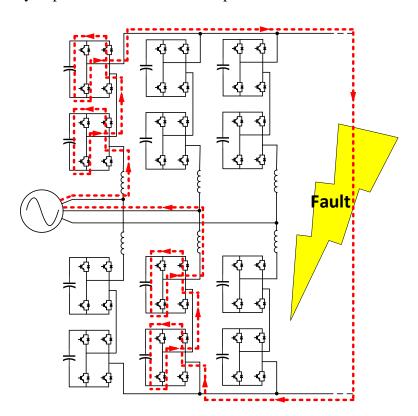

Figure 2. 10 MMC based circuit protection.

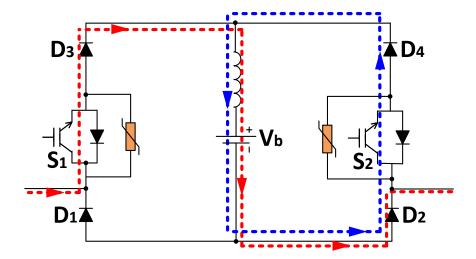

Another trend of the IGBT/MOSFET based SSCB is to use the high controllability of the devices to enhance the performances of the breakers. In [34], a SSCB with self-adapting fault current limiting capability has been proposed as depicted in Figure 2.11. In the breaker, an auxiliary source, as V<sub>b</sub> in Figure 2.11, is used to sustain a consistent current following though the current limiting inductor, L<sub>r</sub>. As the current through D<sub>2</sub> and S<sub>2</sub> tracks the changes in the line current, the current limiter's current stays constant during the normal situations and can be preset according to the current limiting threshold of the breaker. When a fault happens, the line current increases abruptly until it reaches the current limiting threshold. At the moment, the current through D2 reduces to zero and all the increased amount of current is forced to conduct through the current limiting inductor. Therefore, the increasing rate of the fault current is limited. Unlike the conventional current limiting tactics of directly increasing line inductance, the introduced SSCB inserts the current limiter into the circuit only after a fault happens. In this way, the breaker does not impair the fast transient response of the applied system. In addition, during the energy absorbing process of the breaker, once the

Figure 2. 11 SSCB with self-adapting fault current limiting capability.

line current decreases to be lower than the current limiting threshold, the current limiter is bypassed again and therefore the energy volume of the MOV does not need to be scaled up with the current limiting inductor. At the same time, the isolation time of the breaker is not prolonged significantly by the current limiter.

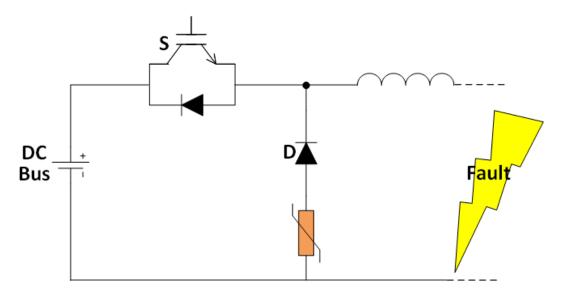

On the other hand, in [35], a surgeless SSCB with the grounded MOV has been proposed as in Figure 2.12. During its current breaking process, fault current is transferred from the DC bus to the branch of the ground connected MOV after the switch  $S_1$  opens. As the DC bus is bypassed by the diode,  $D_2$ , the clamping voltage of the MOV does not need to be higher than the DC bus voltage for synthesizing a negative EMF across the line inductor. For this reason, the surge voltage imposed on the switch during the breaker's operation can be reduced effectively. As a result, the material cost of the breaker may be lower than its counterpart of conventional SSCBs.

Figure 2. 12 Surgeless SSCB with grounded MOV.

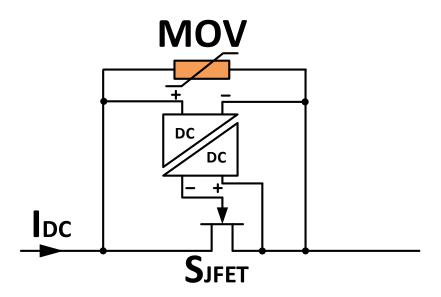

#### 2.4 SiC JEFT based Solid-State Circuit Breaker

SiC Junction-gate Field-effect Transistor (JFET) is an emergent commercialized WBG semiconductor switch. Unlike most of the fully-controlled semiconductor switches, such as IGBT and MOSFET, SiC JFET is normally-on, meaning when there is no drive signal on its gate terminal it maintains on-state and it is turned off only if a negative signal is imposed on its gate. Relying on the normally-on trait, the SiC JFET switches can be applied to the construction of advanced SSCBs, such as self-powered SSCB and supercascode SSCB that have some practical advantages over the conventional SSCBs. Besides, same as the other SiC based semiconductor devices, such as SiC MOSFET, SiC JFET exhibits a very low on-state resistance and a robust performance at high temperature. As regards the energy handling capability, SiC JEFT is potentially better from the testing results in [36]. In addition, without a change of the device structure, the SiC JEFT can further decrease its on-state resistance by shortening the channel length and advance a new semiconductor device named SiC Static Induction Transistor (SiC SIT) [37]. So, it seems that SiC JEFTs have a great potential in solid-state protection industry. Several state-of-art SiC JFET based SSCB with great practical values have been proposed.

Self-powered SSCB utilizes the normally-on characteristics of the SiC JFET devices to realize spontaneous fault interruption and can have a response speed much faster than the SSCBs relying on current sensor and relay [38]. Besides, as its drive energy all drawn from the fault, the breaker does not need any auxiliary sources for its gate driving and the faults happen in the gate driving circuit of the semiconductor switch does not affect the operation of the breaker. The simplified schematic of the self-powered SSCB is shown in Figure 2.13. In the breaker, the output of the DC/DC converter,

namely the gate voltage of the switch, is directly associated with the drain to source voltage of the switch. In normal situation, the voltage across the JFET is low and correspondingly the output voltage of the DC/DC converter sustains lower than the gate threshold voltage of the device. The SiC JFET is turned on and the load current conducts through it. When a fault occurs, the output voltage of the DC/DC converter increases along with the switch's current. While the voltage value is higher than the threshold voltage, the switch turns off and interrupt the fault current. As the polarities of the input and output of the DC/DC converter is reversed, the flyback converter is generally applied to the self-powered SSCB.

Figure 2. 13 Self-powered SSCB.

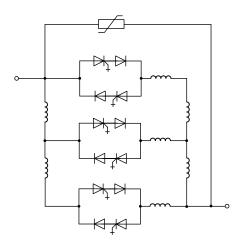

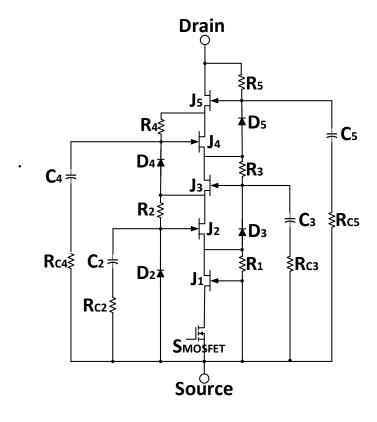

Supercascode SSCB is another type of SSCB utilizing SiC JFET switches. With the increment of the voltage ratings, the number of the gate drivers and the isolated DC/DC converters increases along with the number of the series-connected switches in the SSCB. For this reason, the conventional SSCBs in medium/high voltage applications contain a large amount of auxiliary components for gate driving, which enhances their

costs and impairs their reliabilities. The schematic of a typical supercascode SSCB is as drawn in Figure 2.14. From the figure, the supercascode switch of the breaker contains multiple high voltage SiC JEFT switches and a low voltage MOSFET. Only the MOSFET operates relying on the gate driver and the JFETs do not need drivers to switch their states. In that case, by applying the supercascode structure, the number of the auxiliary driving components in the breaker can be effectively reduced and the high voltage isolated DC/DC converters for the gate signals of the upstream switches can be saved. When there is a fault detected, the MOSFET turns off and its drain-to-source voltage enhances and induces a negative voltage across the gate of the J1. After the amplitude of the voltage exceeds the threshold of the JFET, J1 turns off and has its drainto-source voltage starts to increase along with the voltages of the snubber capacitors, C2 to C<sub>5</sub>. When the voltage value is higher than the clamping voltage of the TVS diode, D<sub>2</sub>, the voltage of C2 is clamped and the voltages of C3 to C5 keep increasing. When the voltage difference between C2 and C3 is higher than the threshold of the SiC JEFTs, J2 turns off. Similarly,  $J_3$ ,  $J_4$ ,  $J_5$  turns off sequentially. After  $J_5$  turns off, the whole line current is transferred from the supercascode circuit to the MOV and decreases to zero gradually. After the fault is cleared, the breaker operates to reclose. The low voltage MOSFET turns on firstly and then the gate voltage of  $J_1$  drops to zero. After  $J_1$  turns on, the snubber capacitor  $C_2$  discharges and the gate voltage of  $J_2$  reduces to zero. Similarly, the Switches, J<sub>3</sub>, J<sub>4</sub>, J<sub>5</sub>, turn on sequentially and the power supply of the loads restores.

Figure 2. 14 Supercascode SSCB.

# 2.5 Comparisons of the Reviewed Solid-State Circuit Breakers

In this chapter, the existing SSCB technologies have been reviewed in the categories of the semiconductor devices applied to these breakers. From the reviews, the SCR based SSCBs present benefits of large power ratings, high conduction efficiencies and low material costs. However, as the SCR switches cannot be actively turned off, additional commutation circuits are required, which makes the design of the SCR based SSCB sophisticated and impairs the reliability of the breaker. The IGCT based SSCBs are also compatible to high voltage/current applications. Besides, the reverse current blocking capability of the RB-IGCT allows it to perform bi-directional current interruptions in an anti-parallel structure. Thus, unlike other SSCBs, the RB-IGCT based

SSCB does not trade off its power efficiency for its bidirectional protection capability. Due to the negative temperature coefficients of the IGCTs, the parallel connected IGCT may fail to share equal amount of current and the effective solution for the current deviation problem still needs further studies. The Si IGBT and SiC MOSFETs based SSCB have a wide range of power ratings that cover most applications of power electronics due to the wide uses of the semiconductor devices. Furthermore, the high controllability and fast transience of the devices enables the breakers to perform advanced functions such as surge voltage suppression and self-adapting current limiting. The SiC JEFT based SSCBs seem to have lower power ratings due to the contemporary low maturity of the device. Nevertheless, counting on the normally-on attribute, SiC JEFT based SSCB can operate without sensor and relays in the self-powered topology and perform with only a single gate driver in a supercascode configuration containing multiple series-connected SiC JFETs. The main attributes and comparisons of the reviewed SSCBs have been summarized in TABLE 2-1. In the table, the voltage ratings and the current ratings of the breakers are determined by the parameters of their semiconductor devices. The voltage ratings of the breakers are set to be 1/1.5 time of the ratings of semiconductor switches to ensure the breakers to sustain the surge voltages during their operations and the current ratings of the breakers are 1/1.5 time of the switches' ratings considering the increment of current during the breaker's response time.

TABLE 2 - 1: Comparisons among the Reviewed Solid-State Circuit Breakers

|   | Size                         | Medium                                 | Large            | Medium                               | Medium                               | Medium                | Small                  | Large                |

|---|------------------------------|----------------------------------------|------------------|--------------------------------------|--------------------------------------|-----------------------|------------------------|----------------------|

|   | Design<br>Comple<br>xity     | Medium                                 | High             | High                                 | Medium                               | Low                   | Medium                 | High                 |

|   | Surge Voltage<br>Suppression |                                        |                  | 7                                    | 7                                    |                       |                        |                      |

|   | Fast Fault<br>response       |                                        | ٨                |                                      |                                      |                       | ٨                      |                      |

|   | Fast Fault<br>Isolation      |                                        | ~                |                                      | ~                                    |                       |                        |                      |

|   | Fault Current<br>Limiting    |                                        | ^                | 7                                    |                                      |                       |                        |                      |

| • | Typical<br>Topologies        | SSCB with<br>Commutation<br>Capacitors | Z Source<br>SSCB | Self-Adapting Current Limiting SSCR  | Surgeless<br>SSCB with<br>Ground MOV | RB-IGCT<br>Based SSCB | Self-Powered<br>SSCB   | Supercascode<br>SSCB |

|   | Current<br>Ratings<br>(A)    | (1405~2630)/<br>1.5                    |                  | (50~3600)/1.<br>5                    | (5~765)/1.5                          | (1290~2660)/<br>1.5   | (3.4~85)/1.5           |                      |

|   | Voltage<br>Ratings<br>(kV)   | (2.8~6.5)/1.5                          |                  | (0.05~6.<br>5)/1.5                   | (0.65)                               | (2.8~4)/1.5           | (0.65~1.7)/1.5         |                      |

|   |                              |                                        |                  | IGBT                                 | SiC<br>MOSFE<br>T                    |                       |                        |                      |

|   | SSCBs<br>Categories          | SCR Based<br>SSCB                      |                  | Si IGBT/ SiC<br>MOSFET<br>based SSCB |                                      | IGCT Based<br>SSCB    | SiC JFET<br>Based SSCB |                      |

# CHAPTER 3: CONCEPT OF THE PROPOSED MULTILEVEL SOLID-STATE CIRCUIT BREAKER

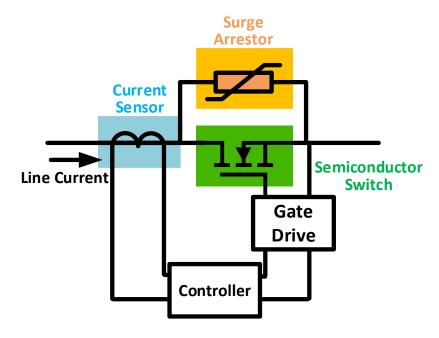

These years, low-voltage SSCBs have gradually become technically mature and started to come into market. However, with the increment of the operating voltage, seriesconnected switches are needed in the conventional SSCBs and result in dynamic voltage unbalance among the switches. The series-connected devices may fail to turn off simultaneously because of the different dynamic performances of both switching devices and gate drivers, which causes overvoltage across a single switch when the SSCBs open. Serval auxiliary circuits dealing with the voltage transient unbalancing problem were proposed in [39]. However, these auxiliary circuits increase the complexity of SSCBs and may fail to maintain the switches' voltage balance in some cases. To solve the problem, a new Multilevel Solid-State Circuit Breaker (MLSSCB) has been proposed in this dissertation. In the proposed SSCB, switches are turned off sequentially rather than simultaneously during the faults. The voltages across the switches depends on the voltages of the capacitors associated with the switches and the camping voltage of the MOVs. Hence, the voltage dynamic unbalancing issues can be averted in the MLSSCB and the voltage imposed on the switches can be assured lower than their voltage blocking limits. Besides, the requirement for the total clamping voltage of the MOVs in the MLSSCB is much lower than that of the conventional SSCB so that the surge voltage induced during the breaker's operation is effectively reduced. The working principles of the snubber circuits for dynamic voltage unbalancing issues and the proposed MLSSCB are presented here along with the design considerations of the MLSSCB.

### 3.1 Conventional Snubber Circuits for Dynamic Voltage Unbalancing Issues

Capacitor snubber circuits have been widely applied to the disposal of the dynamic voltage unbalance among the series-connected semiconductor switches. In the snubber circuit as depicted in Figure 3.1, the capacitors are equally placed in parallel with each of the switches on the series-connected string to provide transient current paths that bypass the early recovered semiconductor devices and allow the latterly recovered switches to recover and to support the source voltage. The minimum required capacitance of the snubber capacitor has been determined as in Expression (3.1) under the worst scenario where a single switch recover for zero charge and the others only recover when they attain their maximum required recovery charge.

$$C_{sb} \ge \frac{(n_s - 1)Q_{max}}{n_s(1 - k_s)V_{sn}}$$

3.1

In the expression,  $n_s$  is the number of the series-connected switches,  $Q_{max}$  is the maximum recovery charge of the semiconductor switch provided by the manufacturers,  $V_{sn}$  is the rated voltage of the switches and  $k_s$  is the voltage sharing factor equaling  $\frac{V_{DC}}{n_s}/V_{sn}$  and indicating the voltage margin of the selected switches in the applied system.

Although the snubber circuit can effectively obviate the dynamic overvoltage among the semiconductor switches caused by their different recovering speed, the dynamic voltage balance among the devices still cannot be guaranteed because of the potential asynchronous delay in the switches' gate drivers and controllers [40]. For this reason, exclusive gate drivers are usually used along with the snubber circuits, which increases the complexity and impairs the reliability of the design. In addition, the

capacitive snubbers bring about large surge current when the switches turn on, which may damage the switches and cause their misoperation during the reclosing [25]. For these drawbacks, the existing technologies of the snubber designs may not be sufficient to solve the dynamic voltage unbalancing issue in the Solid-State Circuit Breakers that have a high demand on the reliability of their switches' operations. To deal with the dynamic voltage unbalance in the conventional SSCBs, the Multilevel Solid-State Circuit Breaker has been proposed in this dissertation as a competitive alternate to the conventional snubber based strategies.

### 3.2 Operating Principle of the Multilevel Solid-State Circuit Breaker

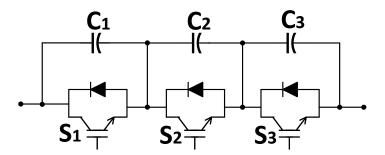

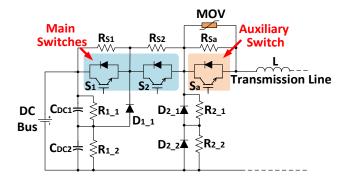

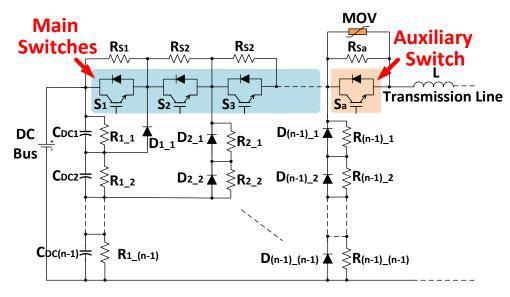

The general structure of the MLSSCBs in 3 level and n level are drawn in Figure 3.2(a) and (b). The levels of the breakers here are determined by the numbers of the voltage levels across the faulted areas during the breakers' operation. The MLSSCB is mainly composed of the semiconductor switches for current interrupting and voltage blocking, the capacitors for voltage dividing and the diodes for clamping the switches' voltage to the different voltage levels of the breaker.

Figure 3. 1 The conventional capacitive snubber circuit for series-connected switches.

Figure 3. 2 Multilevel SSCB. (a) 3 level SSCB. (b) n levels.

In the MLSSCB, the capacitors,  $C_{DC1}$  to  $C_{DCn}$ , work as voltage dividers and have the same capacitance to share the DC-bus voltage equally. After the switches turn off, the voltages across the switches will be clamped to the voltage of the capacitors, equaling the DC bus voltage divided by the number of the capacitors. In other words, the operating voltage of the breaker can be as high as the product of the employed switches' rated voltage and the switches' number.

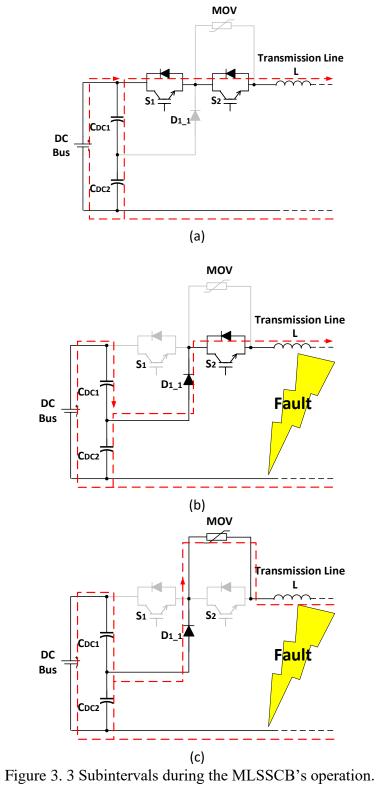

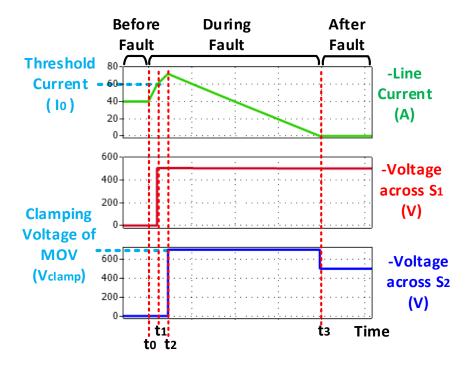

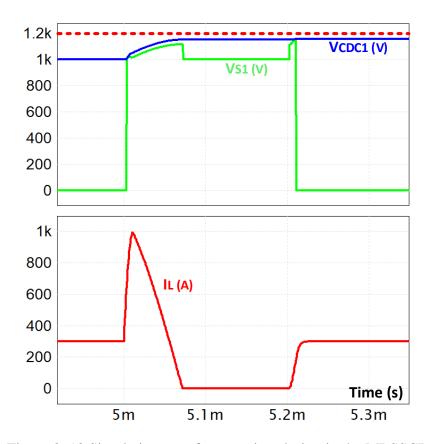

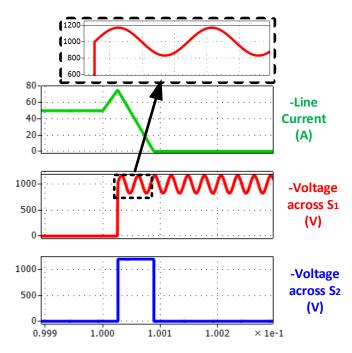

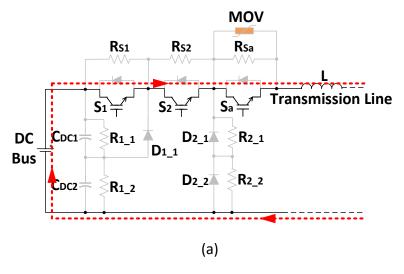

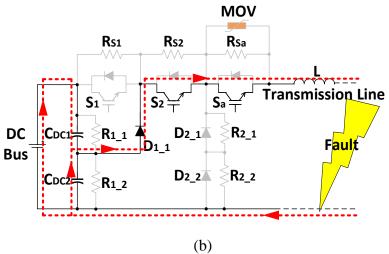

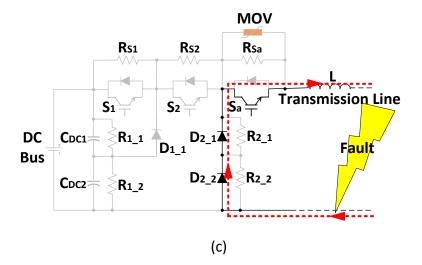

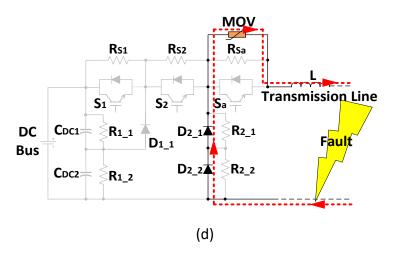

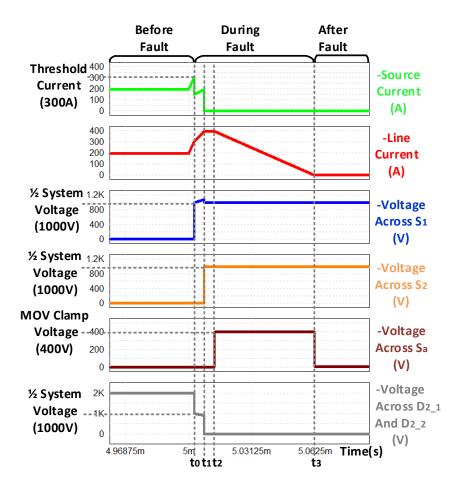

The subintervals of a 3-level MLSSCB dealing with a line-side fault are shown in Figure 3.3 and the simulation waveforms are shown in Figure 3.4 depicting the line

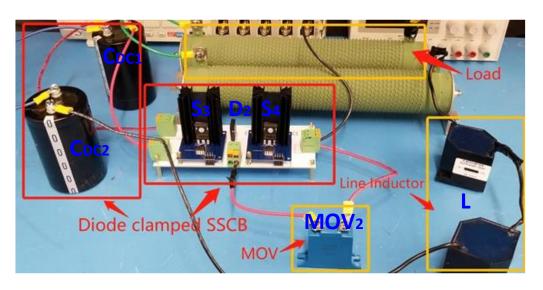

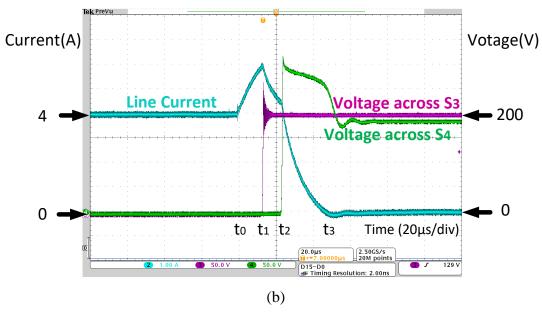

current as well as the voltage of switches in the breaker when the breaker operates. During normal operations, all the switches are turned on and the conduction path through the MLSSCB is as shown in Figure 3.3(a). Whenever the relay detects the line-side fault current exceeding the threshold current, Switch S<sub>1</sub> will be tripped to open and transfer the fault current to the conduction loop shown in Figure 3.3(b). During this subinterval, the voltage across the fault is decreased to half of the DC-bus voltage, so the increment of the fault current slows down as shown in Figure 3.4 from t<sub>1</sub> to t<sub>2</sub>. After a short period of delay time, S2 is turned off and the fault current is commuted into the MOV where the energy stored in the transmission line is absorbed. After that, the fault current decreases gradually to zero as shown in Figure 3.4 from t<sub>2</sub> to t<sub>3</sub>. It can be seen from the waveforms of the voltages on  $S_1$  and  $S_2$ , that the two switches are not turned off at the same time and there is no overvoltage imposed on either of the switches during the whole breaking process. This demonstrates that the proposed MLSSCB does not incur dynamic voltage unbalancing issues. After the fault is cleared, the static voltage balance among the switches can be easily attained by connecting snubber resistors in parallel with each of the switches. Therefore, if the capacitor values are properly selected, there will be neither dynamic nor static overvoltage imposed on the devices. Consequently, auxiliary circuits for voltage dynamic balancing of the switches are not needed in this topology. The experimental waveforms are also achieved for a 3-level MLSSCB in a laboratory-scale short-circuit scenario as shown in Figure 3.5. The experimental results conform to the simulation results of the proposed breaker and its operating principles get further validated.

Figure 3. 4 Simulation waveforms of a 3-level MLSSCB during its circuit breaking process ( $C_{DC1}=C_{DC2}=0.5 mF$ ,  $V_{DC}=1000 V$ ,  $I_{load}=40 A$ ).

(a)

Figure 3. 5 Experiments of a 3-level MLSSCB during its circuit breaking process (  $C_{DC1}=C_{DC2}=1 \mathrm{mF},\ V_{DC}=400 \mathrm{V},\ I_{load}=4 \mathrm{A}$  ). (a)Experimental setup. (b)Experimental results.

Figure 3. 6 Simulation waveforms of a 3-level MLSSCB during its reclosing process.

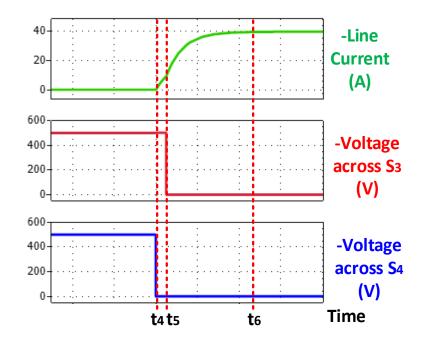

After the fault is cleared, the circuit breaker needs to be reclosed to restore the power supply for the load. By means of proper gate signals, the MLSSCB can be reclosed without the voltage unbalancing issues. There is no auxiliary devices or external sources required to reclose the proposed breaker. The simulation waveforms of the Diode Clamped SSCB during it reclosing process are plotted in Figure 3.6. In the waveforms,  $S_2$  is turned on first at  $t_4$  and followed by  $S_1$  at  $t_5$ . Since the switches in the breaker have their voltage clamped by the capacitors when they are off, they do not incur any overvoltage while they are reclosed sequentially with a time difference between  $t_4$  and  $t_5$ . After a short period of time for the line inductor to be charged, the line current increases to the rated current at  $t_6$  and then the power supply to the load is restored.

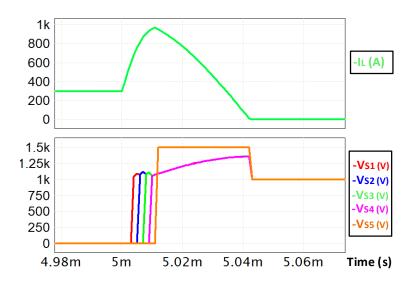

Figure 3. 7 Simulation waveforms of a 6-level MLSSCB during its circuit breaking process ( $C_{DC1} = C_{DC2} = 12\mu F$ ,  $V_{DC} = 5000V$ ,  $I_{load} = 300A$ ).

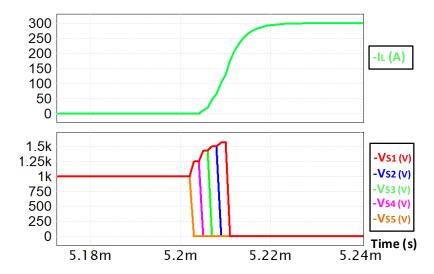

Figure 3. 8 Simulation waveforms of a 6-level MLSSCB during its circuit reclosing process ( $C_{DC1} = C_{DC2} = 12 \mu F$ ,  $V_{DC} = 5000 V$ ,  $I_{load} = 300 A$ ).

The opearting process of the 3-level MLSSCB may be easily extended to the n-level MLSSCB. The simulation results of a 6-level SSCB during its circuit breaking and reclosing are drawn in Figure 3.7 and Figure 3.8 respectively.

### 3.3 Design Considerations of the Multilevel Solid-State Circuit Breaker

To warrant the normal operation of the MLSSCB, several technical considerations need to be made during the design of the breaker. First, the capacitances of the capacitors,  $C_{DC1}$  to  $C_{DCn}$ , need to be selected carefully to avert the overvoltage imposed on the switching devices after the interruption of current. Second, the energy required to be absorbed during the breaking process should be quantified to make sure that the energy volume of the selected MOV is large enough for the situation. Finally, special considerations have been taken into of the selection of the semiconductor devices in the

breaker design to make the selected devices meet the requirements of operating voltage, operating current and conduction efficiency of the applied system.

## 3.3.1 Capacitor Selection

In Figure 3.2 (a) and (b), after Switch  $S_1$  opens, the line current in the breaker is transferred to the conduction loops charging capacitor  $C_{DC1}$ . At the same time, the voltage across  $C_{DC1}$ ,  $V_{CDC1}$ , increases gradually until the line current is extinguished by the breaker. As the voltage across  $S_1$  is clamped by  $C_{DC1}$  when the breaker recloses, the voltage increment on  $C_{DC1}$  is imposed directly on the Switch  $S_1$ . With the enhance of the levels of the breaker, the voltage increment also occurs on other switches but is always the most serious in the switch  $S_1$  as shown in Figure 3.8. To avert the damages on the switches during the breaker's operation, the value of  $V_{CDC1}$  should be limited below the rated voltage of  $S_1$  and this can be achieved by the proper selection of the capacitors. Since all the capacitors in the breaker have equal capacitances, after the voltage of  $S_1$  is suppressed successfully, the voltages across the other switches are also limited under their voltage ratings.

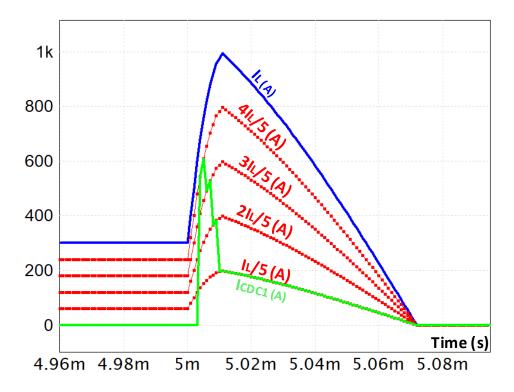

If the breaker detects the fault and starts to operate at the time instant when t=0, the increment of  $V_{\text{CDC1}}$  can be expressed as

$$\Delta V_{CDC1} = \frac{1}{C_{DC1}} \int_{0}^{T_{iso}} i_{CDC1}(t) dt$$