# DESIGN OF SECURE BOOT PROCESS FOR RECONFIGURABLE ARCHITECTURES

by

### Ali Shuja Siddiqui

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2020

| Approved by:          |   |

|-----------------------|---|

| Dr. Fareena Saqib     | _ |

| Dr. Arindam Mukherjee |   |

| Dr. Madhav Manjrekar  | _ |

| Dr. Milind V. Khire   |   |

©2020 Ali Shuja Siddiqui ALL RIGHTS RESERVED

#### ABSTRACT

ALI SHUJA SIDDIQUI. Design of Secure Boot Process for Reconfigurable Architectures. (Under the direction of DR. FAREENA SAQIB)

VLSI advancements have enabled proliferation in the Internet of Things(IoT) domain where small scale System-on-a-Chip (SoC) are employed as sensors or actuators. IoT devices are connected with other IoTs and with backend facilities. In today's world IoT is ubiquitous and pervasive, as system designers continue to use IoT based designs. In order to improve the lifespan of a device, hardware reconfigurability has security and functional applications for IoTs. Connectivity, while essential to the operation for an IoT device, also acts as a door for malicious actors. This work explores and identifies the threats to emerging IoT in the spaces of authentication, integrity, confidentiality and communication. For reconfigurable devices, the work extends boot time security and provides solution for Over the Air update mechanisms for reconfigurable architectures. This work uses automotive and smart grid to demonstrate applications of the research outcomes.

#### **DEDICATION**

I would to like to begin by thanking God Almighty for giving me the opportunity to travel half way around the world to earn my education, for providing for me and specially for giving me ideas when nothing seemed to work.

I dedicate this work to my parents and my siblings, who have always believed in me and have encouraged me to further myself. I thank them for all the support, wisdom and the strength they have given me and for being with me when I needed them the most.

This work is also dedicated to my wife Yameena, for being supportive, patient and encouraging throughout. Her support made this degree a lot easier.

Lastly, I dedicate this work to my friends, Yutian Gui, Manikanta Bhagwatula, Harsha Ganti, Amit Singh and Suyash Mohan Tamore.

#### ACKNOWLEDGEMENTS

I would like to thank and acknowledge the committee members for being a part of my committee and for putting in the time and effort to make my research better. I would also like to acknowledge the Graduate School for providing me with GASP grants that helped me tremendously towards my degree. This research has been funded by National Science Foundation Grant "CRII: SaTC: Hardware based Authentication and Trusted Platform Module functions (HAT) for IoTs", NSF Award Number 1819687.

# TABLE OF CONTENTS

| LIST ( | OF TABLI    | ES                                                                           | 2  |

|--------|-------------|------------------------------------------------------------------------------|----|

| LIST ( | OF FIGUE    | RES                                                                          | X  |

| СНАР   | TER 1: IN   | NTRODUCTION                                                                  | 1  |

| 1.     | 1. Motiva   | tion                                                                         | 1  |

| 1.     | 2. Contrib  | outions                                                                      | 2  |

| 1.     | 3. Organiz  | zation                                                                       | 3  |

| LIST ( | OF ABBR     | EVIATIONS                                                                    | 1  |

|        |             | ackground Study on Secure Boot and Overview of Hard-<br>cy Primitives        | 4  |

| 2.     | 1. Interne  | t of Things                                                                  | 4  |

|        | 2.1.1.      | Smart Grid                                                                   | 5  |

|        | 2.1.2.      | Automotive Security                                                          | 6  |

| 2.     | 2. Reconfi  | gurable Architectures                                                        | 7  |

| 2.     | 3. Threat   | Models                                                                       | 8  |

|        | 2.3.1.      | Eavesdropping, Replay and Man in the Middle attacks                          | 8  |

|        | 2.3.2.      | Private Key Exposure                                                         | Ş  |

|        | 2.3.3.      | Unauthorized Modification to Firmware and Reconfigurable Logic Configuration | 10 |

|        | 2.3.4.      | Nonsecure Communication with Content Provider                                | 11 |

| 2.     | 4. Security | y Concepts                                                                   | 11 |

|        | 2.4.1.      | Confidentiality, Integrity and Availability                                  | 11 |

|        | 2.4.2.      | Physical Unclonable Functions                                                | 12 |

|        |             |                                                                              |    |

|      |                   |                                                      | V1: |

|------|-------------------|------------------------------------------------------|-----|

|      | 2.4.3.            | Secure Attestation                                   | 13  |

|      | 2.4.4.            | Trusted Platform Module                              | 14  |

|      | 2.4.5.            | Secure Boot                                          | 14  |

|      | 2.4.6.            | Secure Over-the-Air Updates (OTA)                    | 15  |

|      | 2.4.7.            | Trusted Execution Environment and the ARM Trust-Zone | 16  |

| 2.5  | . Secure I        | Boot                                                 | 17  |

|      | 2.5.1.            | Early implementations                                | 17  |

|      | 2.5.2.            | Secure Boot Solutions in Desktops                    | 18  |

|      | 2.5.3.            | Secure Boot in Embedded Systems                      | 19  |

|      | 2.5.4.            | Secure Boot in Reconfigurable Computing              | 20  |

| 2.6  | . Logic Lo        | ocking                                               | 23  |

|      | ER 3: Bo<br>FPGAs | ot Time Security and Over-the-Air Update Mechanisms  | 25  |

| 3.1. | . Introduc        | ction                                                | 25  |

| 3.2  | . Threat          | Model for Secure Boot of FPGA Bitstreams             | 27  |

|      | 3.2.1.            | Bitstream Spoofing                                   | 27  |

|      | 3.2.2.            | Runtime Malicious Modification                       | 27  |

|      | 3.2.3.            | Non-secure Communication with Content Provider       | 28  |

| 3.3  | . Root of         | Trust Architecture                                   | 28  |

|      | 3.3.1.            | Hardware Overview                                    | 28  |

| 3.4  | . Design (        | Objectives and Operations                            | 30  |

|      | 3.4.1.            | Establishing Source of Trust                         | 30  |

|    |      |           |                                                  | viii |

|----|------|-----------|--------------------------------------------------|------|

|    |      | 3.4.2.    | Secure Over the Air (OTA) Update Mechanism       | 32   |

|    | 3.5. | Impleme   | ntation                                          | 36   |

|    | 3.6. | Security  | Analysis                                         | 41   |

|    | 3.7. | Conclusi  | on                                               | 42   |

| СН | APT. | ER 4: Ru  | ntime Logic Camouflaging and Obfuscation         | 43   |

|    | 4.1. | Introduc  | tion                                             | 43   |

|    | 4.2. | PCAP P    | rogramming                                       | 44   |

|    | 4.3. | FPGA B    | Eitstream Architecture                           | 46   |

|    |      | 4.3.1.    | Bitstream Contents                               | 46   |

|    |      | 4.3.2.    | FAR Addressing                                   | 47   |

|    |      | 4.3.3.    | Reading and Writing to the PL Fabric             | 48   |

|    |      | 4.3.4.    | Mapping FAR to Resource                          | 51   |

|    | 4.4. | Proposed  | l Scheme for Multi-layer Camouflaged Secure Boot | 52   |

|    |      | 4.4.1.    | Device Enrollment                                | 53   |

|    |      | 4.4.2.    | Device Authentication                            | 55   |

|    | 4.5. | Security  | Analysis                                         | 57   |

|    | 4.6. | Conclusi  | on                                               | 58   |

| СН | APT. | ER 5: Sec | cure Communication Framework for Automotive      | 59   |

|    | 5.1. | Secure E  | CU Communication                                 | 59   |

|    | 5.2. | Hardwar   | e based Resource Isolation                       | 65   |

|    | 5.3. | Secure C  | ode Execution                                    | 66   |

|    |      | 5.3.1.    | Scenario 1: Code Execution from Read Only Memory | 66   |

|                                                                           | ix |

|---------------------------------------------------------------------------|----|

| 5.3.2. Scenario 2: Hardware-Based/Assisted Core Root of Trust Measurement | 67 |

| 5.4. Security Analysis                                                    | 68 |

| 5.5. Conclusion                                                           | 69 |

| CHAPTER 6: Smart Grid Security                                            | 71 |

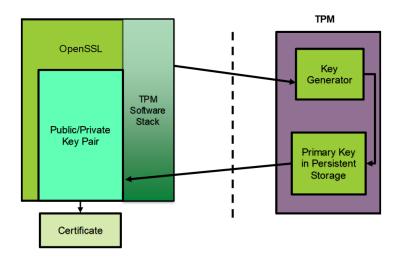

| 6.1. Secure Key Provisioning                                              | 71 |

| 6.1.1. Experimental Setup                                                 | 74 |

| 6.1.2. Performance Analysis                                               | 76 |

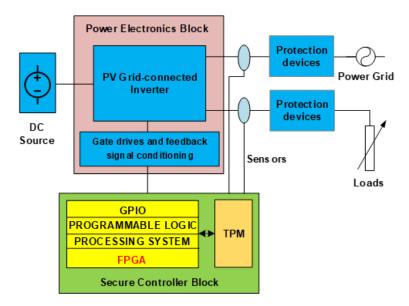

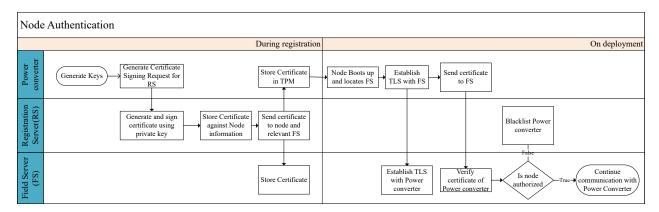

| 6.2. Design for secure reconfigurable power converters                    | 77 |

| 6.3. Security Analysis                                                    | 81 |

| 6.4. Conclusion                                                           | 82 |

| CHAPTER 7: Conclusions and Future Work                                    | 83 |

| REFERENCES                                                                | 85 |

# LIST OF TABLES

| TABLE 2.1: Comparison between TPM 1.2 and TPM 2.0                                                            | 14 |

|--------------------------------------------------------------------------------------------------------------|----|

| TABLE 4.1: Xilinx PCAP Type 1 Packet [1]                                                                     | 44 |

| TABLE 4.2: Xilinx PCAP Type 2 Packet [1]                                                                     | 45 |

| TABLE 5.1: Standard Classical CAN Bus Frame                                                                  | 60 |

| TABLE 5.2: Comparative Analysis of block comparatives speeds at different system clocks rates[2].            | 63 |

| TABLE 5.3: Overhead overview at standard CAN connection speeds[2].                                           | 64 |

| TABLE 5.4: Secure Zone API[3]                                                                                | 65 |

| TABLE 5.5: Overhead overview at Standard CAN connection speeds with CANFD speed of 8mbps in normal operation | 66 |

| TABLE 6.1: Average operation times for 100 runs[4]                                                           | 77 |

# LIST OF FIGURES

| FIGURE 2.1: Common Applications of Internet of Things.                        | 4  |

|-------------------------------------------------------------------------------|----|

| FIGURE 2.2: Symmetric Encryption                                              | 10 |

| FIGURE 2.3: Secure Attestation in devices.                                    | 13 |

| FIGURE 2.4: Secure Boot Software Chain of Trust.                              | 16 |

| FIGURE 3.1: Proposed Secure Boot System Architecture.                         | 29 |

| FIGURE 3.2: Content Provider client FPGA's connection.                        | 30 |

| FIGURE 3.3: Key exchange in a trusted environment.                            | 31 |

| FIGURE 3.4: Keys shared between a client and server.                          | 32 |

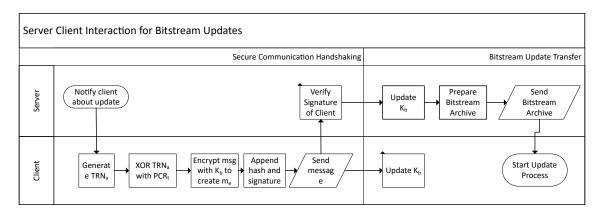

| FIGURE 3.5: Server Client Interaction for Bitstream Updates.                  | 33 |

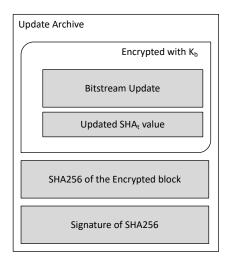

| FIGURE 3.6: Bitstream Update Archive                                          | 34 |

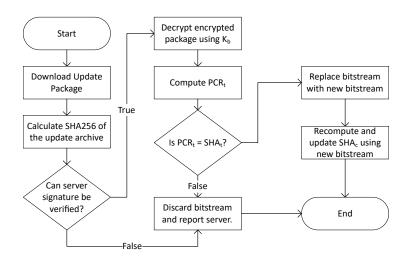

| FIGURE 3.7: Bitstream Update Application Process                              | 35 |

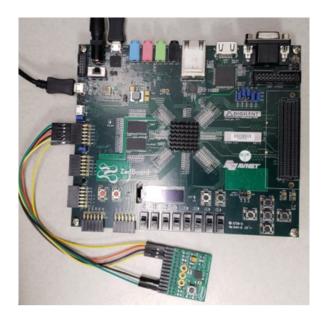

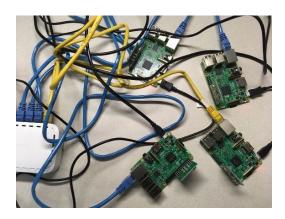

| FIGURE 3.8: Hardware Setup                                                    | 37 |

| FIGURE 3.9: Secreenshot of tpm_xfer function.                                 | 38 |

| FIGURE 3.10: Screenshot of TPM Driver Extend Functions.                       | 39 |

| FIGURE 3.11: ComputeHashLoc4 function computes cummulative hash over the TPM. | 40 |

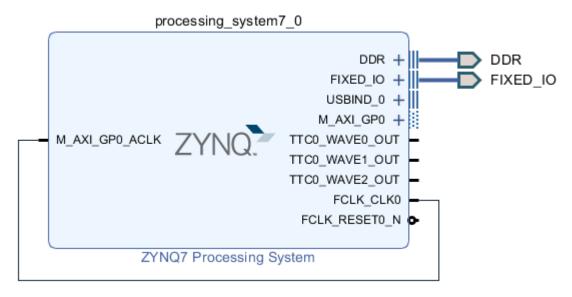

| FIGURE 4.1: Vivado Processing System Block Diagram.                           | 44 |

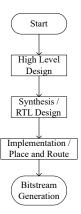

| FIGURE 4.2: Bitstream Generation Flow Diagram                                 | 46 |

| FIGURE 4.3: Bitstream Header Snapshot                                         | 47 |

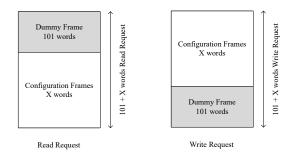

| FIGURE 4.4: FAR Read / Write requests.                                        | 49 |

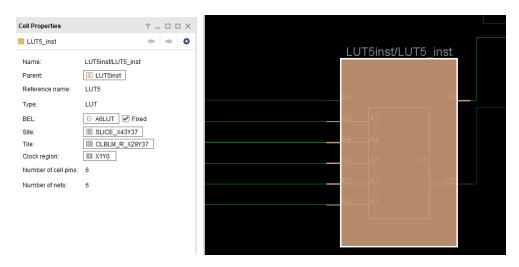

| FIGURE 4.5: Test LUT5 Instantiation                                           | 50 |

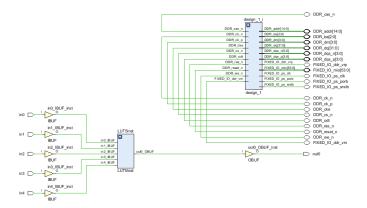

| FIGURE 4.6: Experimental design for evaluating bitstream mapping              | 50 |

|                                                                                | xii |

|--------------------------------------------------------------------------------|-----|

| FIGURE 4.7: Experimental Setup for LUT5 placement.                             | 51  |

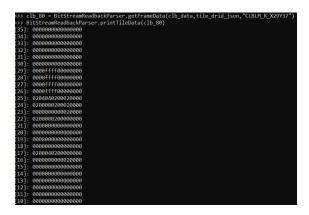

| FIGURE 4.8: Snapshot of the resource CLBLM_R_X29_Y37 from target test circuit. | 52  |

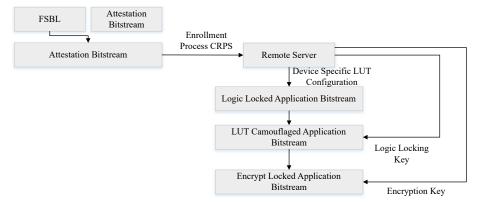

| FIGURE 4.9: Overview of the enrollment process [5].                            | 53  |

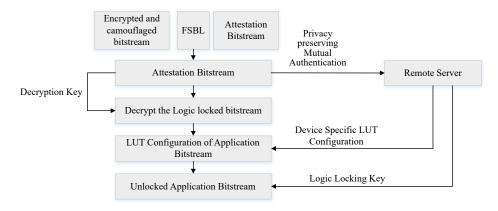

| FIGURE 4.10: Overview of the in-field operation [5].                           | 53  |

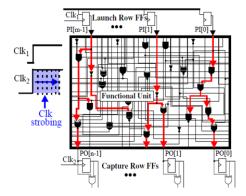

| FIGURE 4.11: Computing Latch-Capture Interval in HELPUF [6].                   | 54  |

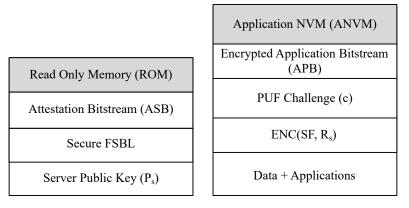

| FIGURE 4.12: Client Device Memory View on enrollment [5].                      | 55  |

| FIGURE 4.13: Authentication and Application Bitstream Programming [5].         | 56  |

| FIGURE 4.14: FSBL code excerpt for LUT reconfiguration [5].                    | 57  |

| FIGURE 4.15: On-fabric LUT reconfiguration [5].                                | 57  |

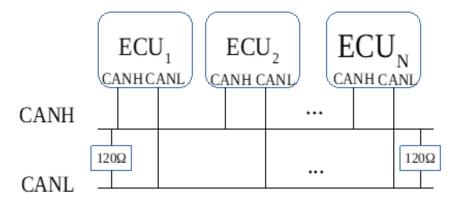

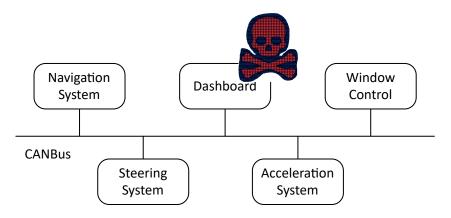

| FIGURE 5.1: Controller Area Network Bus Connection Diagram[2].                 | 59  |

| FIGURE 5.2: CANBus connection in a vehicle.                                    | 60  |

| FIGURE 5.3: Demonstration of spoofing and Denial of Service[2].                | 61  |

| FIGURE 5.4: RX Buffer at node CAN0 is overflowed[2].                           | 61  |

| FIGURE 5.5: Hardware based Secure Communication Framework for ECUs[2].         | 62  |

| FIGURE 5.6: HELP PUF Construction[2].                                          | 63  |

| FIGURE 5.7: On the field code unsealing [7].                                   | 68  |

| FIGURE 6.1: Secure architecture for Smart Grid[4].                             | 71  |

| FIGURE 6.2: Certificate generation[4].                                         | 72  |

| FIGURE 6.3: Secure communication channel establishment[4].                     | 73  |

| FIGURE 6.4: Smart Grid test bed[4].                                            | 74  |

| FIGURE 6.5: TPM based RSA encryption[4].                                       | 75  |

|                                                                             | xiii |

|-----------------------------------------------------------------------------|------|

| FIGURE 6.6: TPM based RSA encryption and decryption process[4].             | 75   |

| FIGURE 6.7: TPM based certificate generation[4].                            | 76   |

| FIGURE 6.8: ECC Curve Parameters[4].                                        | 76   |

| FIGURE 6.9: ECC Key Blob[4].                                                | 77   |

| FIGURE 6.10: Certificate generation[4].                                     | 77   |

| FIGURE 6.11: Reconfigurable secure power electronic converter framework[8]. | 79   |

| FIGURE 6.12: Node Authorization Scheme for Power Converters[8].             | 80   |

| FIGURE 6.13: Iviea Atlas-I-Z8 board for Power Converter [8].                | 81   |

#### CHAPTER 1: INTRODUCTION

#### 1.1 Motivation

There is an estimated 19.4 billion connected devices in the year 2019, and this number is expected to increase to 34.2 billion by the year 2025 [9]. It consists of devices connected wirelessly, via a wired connection or through some proprietary network stacks. The connection may either be one directional or bi-directional.

Networked devices have pervaded every domain of life in many forms. In the form of computers, laptops tablets, mobile phones, smart watches, and other small scale devices. Depending on the application, these devices may exist as smart appliances, industrial sensors and actuators, and personal smart devices. They may be connected with a comparatively resourceful backend server with or with an array of similar devices in a mesh or similar network. Small scale devices are resource constrained in terms of computing and storage. These limitations impact the effectiveness of the device in the field. This requires systems designers to carefully plan the resources that are available on a device, and plan what features can be effectively implemented on the device.

When a system is designed, the basic two components of design are firstly the hardware ware and then the software stack. The software stack is only limited by the hardware limitations. In terms of fixed fabricated hardware, once the hardware has been fabricated, it cannot be altered in any way. In case there is some fault later discovered in the hardware or an improvement in the architecture, it cannot be integrated. This limitation can be overcome by integrating reconfigurable hardware design. Reconfigurable hardware, such as FPGAs have an array of hardware components implemented on the fabric of a device. This fabric can be configured after the device fabrication

using in-field reconfigurable architectures. The use of FPGAs in the market is only expected to increase from \$63 billion in the year 2019 to \$117.97 billion by the year 2026[10] [11].

Connected devices open a device to unwanted, rogue and malicious actors. These actors pose various threats to the operations of the connected devices. This may lead to sensitive information leakage, communication corruption and even malicious modification of the on-board software and in the case of reconfigurable devices, hardware configuration. This research focuses on addressing issues in resource constrained reconfigurable hardware and presents novel hardware-based approaches.

#### 1.2 Contributions

This research has following contributions towards improving boot and runtime security in reconfigurable architectures:

- Identifies security threats and presents threat models that affect boot and runtime security of an IoT in the field. Existing work and their shortcomings are also discussed.

- Proposes a novel boot time security and Over-the-Air update framework for FPGAs. This scheme employs hardware assisted cryptographic systems, such as Trusted Platform Module (TPM) to present a key update and a secure communication scheme. To implement secure over-the-air update mechanism, the server verifies the integrity of the client device. This ensures in-field security compliance.

- Presents a novel mechanism for implementing FPGA based logic obfuscation.

Pre-boot in-field device authentication scheme is extended to implement runtime logic obfuscation. This obfuscation method is to best of knowledge the first of its kind. This scheme manipulates application bitstream before being deployed onto a device. Once the device has been authenticated with the con-

tent provider, only then will it provide the device with correct and complete bitstream configuration. In combination with the logic obfuscation, this scheme uses key based logic locking to improve logic runtime bitstream security.

- Proposes hardware based secure communication and secure code isolation framework for vehicular Electronic Control Units (ECUs).

- Provides a key provisioning scheme for IoT devices in the power grid and puts forward a design for secure reconfigurable power converters for the power grid.

#### 1.3 Organization

This document is divided into the following chapters. Chapter 2 describes the background information on the topics involved in this research. It also gives an overview on the history and the progression of the existing work performed in the research and commercial spheres. The remaining chapters explain the research conducted.

Chapter 3 details the contributions on proposing secure boot and over-the- air update mechanisms for securely updating FPGA bitstreams. Chapter 4 presents a mechanism for implementing runtime logic locking and bitstream logic obfuscation scheme. Chapter 5 extends the research to secure communication and secure code execution in the automotive domain. Chapter 6 proposes key provisioning and in the smart-grid and a design for secure reconfigurable power converters using FPGAs. Lastly, conclusions of the research are presented in Chapter 7.

# CHAPTER 2: Background Study on Secure Boot and Overview of Hardware Security Primitives

In this capter, we will overview the security concepts and hardware security primitives for system integration.

#### 2.1 Internet of Things

The term Internet of Things (IoT) was first coined in the year 1999 by Kevin Ashton[12]. Initially, Internet of Things was designed for the purposes of supply chain management, but with time, its application scope was widened to include other domains as well. IoT is the network of connected devices which are automated in nature and are used for sensing and/ or actuation. Sensing based IoTs result in generating knowledge base for taking decisions on, whereas an IoT can use different actuation mechanisms to manipulate with the environment it is located in.

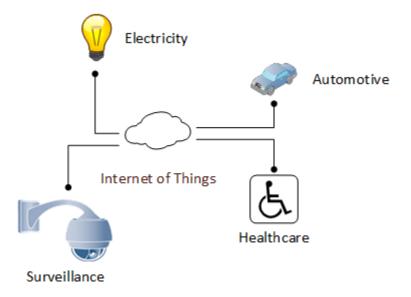

Figure 2.1: Common Applications of Internet of Things.

IoT systems consists of three entities, the backend, the middleware, and the end

device. Depending on the scale and application of the system, the backend can be a personal computer, a dedicated server to even a scalable cloud environment. For sensing applications, where an IoT device is resource constrained and cannot make decisions itself, the decision-making is left at the backend. The information gathered from sensors is sent off to the backend, where it can take an informed decision based on the information gathered. Big Data analytics has gained traction in IoTs for data handling[13]. The middleware consists of the connecting technologies that connect an end device with the backend. It comprises not just the networking elements, such and router and switches etc., but also of any intermediary data collection and decision-making nodes that lie between the backend and the end device[14].

For the end devices in an IoT system, there are various technological factors that have resulted in the rapid adoption and growth of IoTs over the years. Two of such factors are the constant improvement in the embedded systems computing domain and the wireless connection mediums such as Wi-Fi, Bluetooth Low Energy (BLE) and Zigbee, etc., With each iteration of these technologies, the focus has been on improving speed of the network, the cost of computing and power efficiency [15].

Internet of Things have found its ground in several areas, including consumer electronics, smart grid, automotive industry and automation. For the purpose of this research, I have focused my efforts on IoT devices in the smart grid.

#### 2.1.1 Smart Grid

With the introduction of smart grid, the energy grid is no longer comprised from the uni-directional (i.e. from the backend to the end nodes) data communication path, but bi-directional. All electrical and computation-oriented devices generate data that is communicated over a data communication network to the backend Supervisory Control and Data Acquisition system (SCADA). Additionally, end consumers also participate on the network using IoT devices, e.g. smart meters, smart appliances and even electrical car chargers which exchange data with the smart grid middleware.

Smart grid allows inclusion of Distributed Energy Resources (DER) to the grid. DERs are power generation systems that contribute to the electrical grid by producing power. The generated power can come from different sources such natural gas, hydro, wind and solar etc. DER are equipped with IoT devices that communicate with the SCADA backend. The communication between DER and SCADA is performed using the standard IEC 61850[16].

#### 2.1.2 Automotive Security

Vehicles are composed of individual systems that are connected together. They are mechanical and electronic in nature. These systems include engine, steering[17], brakes, air conditioning, the infotainment system, parking assistance, etc. Modern vehicles are pushing towards increasingly making interaction between all on-board systems digital. As such, instead of using the physical state of a system an Electronic Control Unit (ECU) is connected, which broadcasts the state of the physical system as a data message. All ECUs are connected with each other over a network. Currently, there are several network protocols being used. Some of the more widely used are Controller Area Network (CAN), CAN with Flexible Data-rate (CANFD), and EtherCAT etc.

ECUs had originally started as a way to fine tune an engine on a vehicle. However, in 1996, it was made mandatory that all vehicles provide access to On-Board Diagnostics using an OBD-II port. This law pushed car manufacturers to add a digital interface to the components embedded in a car. Nowadays, automation in automotive has progressed enough to offer self-driving vehicles. Additionally, cars are also connecting with each other and with a growing roadside infrastructure to form a V2V and V2X infrastructure [18].

#### 2.2 Reconfigurable Architectures

Application Specific Integrated Circuits (ASICs) are fabricated circuits that designed to perform one task. Whereas microprocessors, on the other hand provide freedom of what tasks can be performed on it. Tasks that can be performed on a microprocessor are dictated by code that is executed on it. The ability of a microprocessor is defined by its Instruction Set Architecture (ISA). Code itself cannot modify the underlying architecture.

Reconfigurable architectures, most popular being the Field Programmable Gate Arrays (FGPAs) lie in between the spectrum of a microprocessor and an ASIC. FPGA allow reconfiguration of hardware. FPGAs are composed of Programmable Logic fabric (PL) consisting of programmable logic gates that are connected together to form a digital logic circuit. The gates in an FPGA are made of Look-up Tables (LUTs). Current generation of Xilinx FPGAs are composed of either five input or 6 input LUTs. Additionally, based on the size, and application target, FPGAs also provide adders, registers, block memory, Digital Signal Processing (DSP) components, as well as embedded microprocessors(PS). Following are the introductory FPGA concepts that are referenced and used in this research:

- Slice: Slice is a collection of logic components in an FPGA. In Xilinx's 7000 series of FPGAs, each slice consists of four LUTs, eight storage elements (flip-flops and latches), carry logic elements and multiplexers. There are two different kinds of slices, namely SLICEM and SLICEL. A SLICEL can only contain the components listed above, whereas SLICEM can contain additional components such as distributed RAM components as well as 32-bit shift registers.

- Configuration Logic Block (CLB): CLBs consists of two slices. These slices can either be a combination of SLICEL and SLICEM or two SLICELs.

- PCAP and ICAP: PCAP stands for Processor Configuration Access Port

and ICAP stands for Internal Configuration Access Port. An ICAP port is a microprocessor based (PS) interface to the PL. PCAP interface provides capabilities for reading and writing CLBs LUTs and memory elements as well partial bitstream loading and bitstream readback. At the time the FPGA boots up, the access to the PL fabric is first given to PCAP. FPGAs also provide an additional Internal Configuration Access Port (ICAP). This port is used by PL fabric internally to modify itself on the run.

• Dynamic Partial Reconfiguration: When an FPGA needs to be reprogrammed, the execution of the PL must first be shutdown, the updated bitstream is copied to the fabric and then the fabric can be brought up again. Dynamic Partial Reconfiguration mitigates the issue of shutdown by enabling allowing areas of the fabric to be set as Dynamic Partially Reconfigurable areas. Such areas can be reprogrammed on the fly. The surrounding logic around these areas stays the same throughout the operation. One common use case of DPR is to have an area that can be used to implement multiple implementations of the same design entity.

#### 2.3 Threat Models

There is plethora of vulnerabilities found in IoT devices ranging from remote network-based vulnerabilities, local as well as physical vulnerabilities. Different components of this research delve into presenting solutions against the following threats faced at different levels of operation of a device.

#### 2.3.1 Eavesdropping, Replay and Man in the Middle attacks

In a network of devices, all devices with access to a medium can access information travelling over that medium. As such, there is always a chance for an eavesdropper listening to the conversation occurring over the medium. If the communication is not encrypted, the eavesdropper can listen to this conversation and extract sensitive information. Additionally, this information can be replayed to introduce unexpected behavior at an unsuspecting victim. Furthermore, a malicious actor can then perform a man in the middle attack by posing as a trusted node and communicating with a legitimate node on the network.

An example of this attack is the 2015 attack that was performed on Jeep Cherokee [19]. The vehicle uses a service called Uconnect which runs on the car's infotainment dashboard. This service connects to the internet to communicate with a backend infrastructure. The hackers got access remote access to the infotainment system using a remote vulnerability found on the service. The infotainment system is connected with the rest of the car ECUs using CAN bus. Hackers were able to communicate with the other systems using CAN messages. They were able to have total control over systems such as braking, steering, AC etc. Since the ECUs connected over the CAN network perform no identity check, they accepted and reacted to all the malicious information being broadcasted.

#### 2.3.2 Private Key Exposure

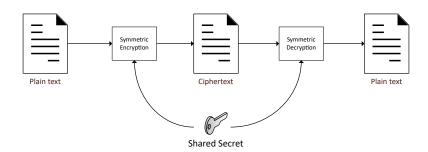

For implementing private communication between two nodes over an untrusted network, encryption is used. Encryption uses one-way function and an encryption key to convert plain text input into cipher text. In case of symmetric key encryption e.g. AES encryption, the encryption key is shared between the two communicating parties beforehand. In case this key is leaked to an eavesdropping adversary, the adversary can decrypt the entire flow of traffic between the nodes sharing the key. The effect is exacerbated when a collection of devices uses the same key. Therefore, it is a priority to store private keys in a secure area on a device. Recently, hackers were able to retrieve encryption keys to a database encrypting personal information on staying guests at a hotel chain[20].

Figure 2.2: Symmetric Encryption

In case of asymmetric cryptography, for each node there is a pair of keys generated, a pair of public and private keys. The public key can be distributed whereas the private key must be key in a safe environment. A node uses its private key to sign a message. When the message is received at the recipient, the public key of the sender is used to verify the signature received. If the private key of a node is compromised, a malicious node can pose as the sender.

# 2.3.3 Unauthorized Modification to Firmware and Reconfigurable Logic Configuration

A microprocessor-based system performs the actions that are defined by the code existing on its memory. The code may be low level firmware code, operating system or any application. Depending on the system, it can also be bare metal application that is application centric and does not require an additional operating system layer. The interest of an attacker is to redirect the normal flow of execution to an unauthorized piece of code[21][22].

In reconfigurable computing domain, SRAM based FPGAs allow modification in the field. In SRAM based FPGAs, PL is populated at boot time. This process is either performed by the Zeroth Stage Boot Loader software commonly referred to as BootROM[23] or by the First Stage Boot Loader (FSBL)[24] depending on the type of FPGA. If the FPGA is equipped with a PS, it is the responsibility to load the PL bitstream, otherwise BootROM takes care of the PL bitstream loading process.

A bitstream can also be modified at runtime if the target FPGA is equipped with a PCAP or ICAP port. In an FPGA, an attacker is interested in modifying the bitstream. An attacker can either replace the PL logic to perform entirely different tasks, add or remove functionality (e.g. hardware trojan), or may even add a leakage side channel for secret information extraction [25]. There are two points of attack for an attacker namely, at boot or during runtime. At boot, before the bitstream is loaded, an attacker may replace the bitstream with a malicious bitstream. Whereas at runtime, once the bitstream has been loaded an attacker may target dynamic reconfigurable partitions or may want to target certain portions of the configuration. To achieve this, an attacker can use the PCAP or the ICAP.

#### 2.3.4 Nonsecure Communication with Content Provider

For an FPGA device placed in the field, bitstream updates can be provided manually physically by an engineer, through a physical update mechanism or through the use of remote updates over a network. If a content provider over a network is not secure, an adversary may spoof its identity to become a content provider. Therefore, an adversary may be able to push malicious updates to the client. On the other hand, an adversary can also impersonate a device on the field to download bitstream updates from a content provider not meant for it.

#### 2.4 Security Concepts

#### 2.4.1 Confidentiality, Integrity and Availability

Confidentiality, Integrity and Availability (CIA) are core concepts of information security. This triad is a notion of guiding security policies. Confidentiality refers to the property that no unauthorized party is able access to secure information in a system. Confidentiality can be achieved through two ways. One way is by guaranteeing that communicating parties are physically in an isolated environment. The other way is to encrypt communication between the two communicating parties. Encryption allows

communicating parties to exist in an unsecure environment while freely communicating with each other. Integrity is a guarantee that all information part of a process is safe from any unauthorized modification from a malicious actor or from a compromised authorized actor. Integrity can be ascertained through various scheme. Once common scheme is by the use of MAC or Message Authentication Code. (MAC) or Key Hashed Message Authentication Code (HMAC). Availability ensures that even under less favorable conditions the system is still operational. This can be achieved using redundancy and isolation.

#### 2.4.2 Physical Unclonable Functions

Physical Unclonable Functions (PUF) are a new type of cryptographic primitive used in hardware security to implement identity or secret keys. They rely on the inherent manufacturing process variations, which are used to produce reliable and device-unique output [26][6]. PUFs are based on a challenge-response pair (CRP) mechanism. Challenges are input to the PUF circuit. They are defined using a string of 0s and 1s. The length of the challenge input is decided by the PUF implementation. PUF output, or its response is produced by the combination of the challenge input and the fabric variation caused due to the challenge input.

There two different types of PUFs, namely Weak and Strong PUFs. A major difference between the two is that the weak PUFs have few challenges for which they can uniquely generate a key whereas strong PUFs have a large challenge space and therefore have a unique response for most of the challenges. The bit generation for cryptographic applications is a two-step process that is enrollment and registration. During the enrollment process, each PUF is given a set of challenges and the response pairs are recorded. Later when the PUF is in field, these responses are regenerated for use in identification and encryption applications.

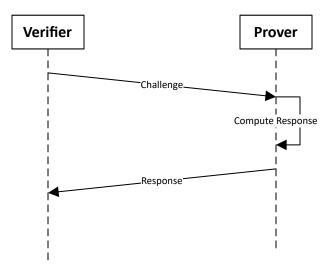

#### 2.4.3 Secure Attestation

In the current landscape with IoTs, connectivity of a device dictates its reach. On the other hand, connectivity also makes a device vulnerable to different security issues. There is a need to maintain integrity of the state of the device. To be certain that the device has not deviated the concept of secure attestation has been introduced. Secure attestation introduces the concept of a prover and a verifier. These two entities work together with each other to verify the integrity of a system. A verifier is a trusted party on the system. The prover on the other hand cannot be trusted initially and must earn its trust with the verifier. Verifier's task is to query the prover with the set of challenges. The prover in turn responds to these challenges by collecting data from the running system. Verifier based on the responses can attest the integrity of the system.

Figure 2.3: Secure Attestation in devices.

There has much work on software attestation in embedded devices. SWATT[27] is one of the earlier works in this domain. This work implements a software attestation framework on over-the-shelf components. It uses time as a measure for integrity. The verifier keeps a model for timing for response times. In case there is deviation, it

corresponds to an attacker who has compromised the system to use code redirection to get to the prover function. The verifier the time difference with the reference value and may deny attestation.

#### 2.4.4 Trusted Platform Module

Trusted Platform Module (TPM) is a hardware module that implements cryptographic functions. These functions can be encryption, data signing and data sealing. TPMs follow TPM specifications put forward by the Trusted Computing Group (TCG)[28]. All TPM implementation must follow the specifications however, the specifications do provide flexibility in terms of the functionality it can provide. TPM also has a limited tamper resistant non-volatile memory. This memory can be used for storing cryptographic objects including keys and other user defined values. There are currently two specifications that are being followed are TPM 1.2 and 2.0. However, there is a shift from TPM 1.2 to TPM 2.0 due to the advanced features that TPM 2.0 provides. An overview of the differences between the two standards is given in Table 2.1.

Table 2.1: Comparison between TPM 1.2 and TPM 2.0

| Algorithm | RSA      | RSA  | ECC      | ECC    | AES      | AES      | SHA- | SHA- |

|-----------|----------|------|----------|--------|----------|----------|------|------|

|           | 1024     | 2048 | NISTP256 | BNP256 | 128      | 256      | 1    | 2    |

| TPM 1.2   | Yes      | Yes  | No       | No     | Optional | Optional | Yes  | No   |

| TPM 2.0   | Optional | Yes  | Yes      | Yes    | Yes      | Optional | Yes  | Yes  |

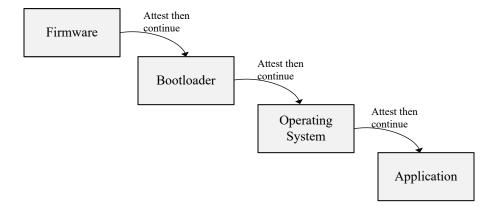

#### 2.4.5 Secure Boot

Secure Boot is a secure attestation mechanism to establish Root of Trust at boot time. This mechanism works by attesting each layer of software before it can be executed on a system. Since the first layer of execution is the firmware or BootROM, trust is first established at this level. Each next level is first attested by the running layer before execution can be passed to it. As such, in a typical system, where succeeding the layers of execution are firmware, operating system, user applications,

etc., the firmware will attest the operating system, the operating system will attest the user applications and so on.

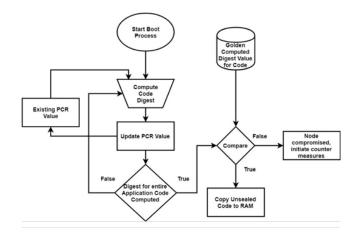

Secure boot is also commercially available as a part of personal computers. Commercial secure boot implementations (e.g. Microsoft Windows, Trusted Grub, UEFI etc.) rely on TPM to provide a trust anchor. TPM offers provisions for implementing measurable boot using Platform Configuration Registers (PCR). PCRs are registers that hold cumulative hash values. These registers are populated using TPM\_PCR\_Extend and or the data streaming enabled TPM\_HASH structures. 256 bits of data is hashed using either SHA-1 or SHA-2 hashing algorithm on the TPM. Once the process is completed, the computed SHA value is added to an existing selected PCR value. Equation 1 shows the process of PCR extension.

The boot process can be divided into stages, e.g. firmware, operating system, applications etc. For measuring the boot process, the PCR is computed and verified for the next layer in the process before the execution can be passed to that layer. At the end of the process, the value of the PCR provides sequential attestation of the all the components in the chain.

#### 2.4.6 Secure Over-the-Air Updates (OTA)

Over the Air (OTA) updates is a mechanism for a system to push updates to embedded systems, mobile market, automotive industry and IoT devices. IoT devices placed in a field communicate with a specified backend environment over their lifetime for receiving updates. In such a scenario, an attacker would impersonate the update server to be able to push malicious updates to an IoT device. In case of reconfigurable hardware, this update can be to the reconfigurable logic fabric aboard a device. On the other hand, an attacker may even want to appear as a connected device so that it may download software not meant for it to access. As such there is a requirement for establishment of trust between the two actors.

Secure OTA ensures that an update server and a connected client can trust each

other. One way of establishing this trust is by using identity. Identity can be established using concepts such as digital certification. One the field, during connection establishment, the client and the server verify the communicating node's identity using these certificates. Additionally, to mitigate eavesdropping, encryption is implemented between the two nodes.

#### 2.4.7 Trusted Execution Environment and the ARM TrustZone

Trusted Execution Environment (TEE) provides on-chip environment for trusted code execution. Being on-board makes it difficult for snooping or man-in-the-middle attacks. The environment depending on its implementation provides an isolated cell for running trusted code. TEE gives developers the access to write their own functions, for example, proprietary encryption algorithms. Examples of commercial Trusted Execution Environments are ARM TrustZone, Intel SGX and Intel TXT.

Figure 2.4: Secure Boot Software Chain of Trust.

ARM TrustZone is a Trusted Execution Environment which is implemented within the processor fabric as a co-processor. ARM TrustZone provides isolation for main memory elements, peripherals and provides isolation for system bus elements. It divides the system into two worlds, namely secure and non-secure. The secure world has complete access over all the resources; however, the non-secure world is a configured as an isolated sandbox. The non-secure can be configured to execute general purpose code such as Linux operating system. Secure world can instead run a custom min-

imal operating system that may run some security specific code. Some examples of commercial systems ARM TrustZone are Samsung KNOX, Samsung Pay and Apple TouchID.

#### 2.5 Secure Boot

#### 2.5.1 Early implementations

There is no set singular implementation of secure boot and is dependent on the domain and the security requirements of the system. For the desktop systems, one early approach was the adaption of minimal lightweight kernel design[29]. The kernel was suggested to be minimal and verifiable by manual code inspection. This design forced exokernel design, where every other module excluding the defined core kernel exists in the user space. The purpose of the exokernel is to allocate and dis-allocate memory securely. This scheme pushes the burden of security on the programmer alone by suggesting use of using secure programming practices, inline cross domain function calls and by use of type safe languages as the only form of security. Presently, this scheme has limited practical applicability because of the large code base and short development time.

A microprocessor-based system depends on external code sequence. Basic Input/Output System (BIOS) historically is the first software code that is executed by a processor. The BIOS performs critical hardware initialization and passes control to a bootloader that loads the operating system. Authors in [30] use BIOS of the motherboard as the root of trust. This secure bootstrap structure is called AEGIS. The software is divided into layers. BIOS holds public keys and digital signatures to verify the integrity of next layer. The architecture also holds recovery alternate code that is loaded if the verification process fails. This system implements a chain of trust. The secure BIOS after verifying the integrity of the bootloader stage using cryptographic hash verification, gives the control to it. The bootloader will subsequently verify the operating system and finally the operating system verifies the software layer. Public

keys are stored in X.509[31] certificates. Shortcoming of such a system is the reliance on external components to implement the security scheme.

[32] is one of the earlier works in integrity checking for intrusion detection. Integrity plays an integral role in measurable boot. This paper presents a software system written checking integrity in a Unix environment. The scheme keeps track of new files, modifications and deleted files during execution. This is useful in detecting an attacker making unexpected changes to the running root file system. The system stores difference with the original files and provided support for MD5 signature for maintaining the integrity of files. However, the attack to the file system can be extended to the tripwire system such that the attacker can cover up their tracks.

#### 2.5.2 Secure Boot Solutions in Desktops

Unified Extensible Firmware Interface (UEFI) is a modern alternative and a replacement to BIOS in desktop PCs. It offers several boot time and runtime services, including support for device drivers, an operating system (OS) independent time service, runtime variable store, UEFI booting and secure boot. To mitigate the possibility of executing unauthorized malicious bootkits[33], UEFI based secure boot enables execution of digitally signed OS loaders that exist in UEFI executable formats (EFI). Approved OS loaders are signed against the UEFI's master signatures. These signatures are verified every time the OS loader is executed. UEFI based secure boot support does not extend to the operating system. Every operating system has their own version of measured boot.

Of the current commercial proprietary and open source operating systems, Microsoft Windows has one of the more popular implementations of measured boot. It uses TPM to support measured boot. At the end of secure boot, UEFI sends the hash of the next software components, i.e. the kernel, Early Launch Anti-Malware (ELAM) drivers and boot drivers, to the TPM. Additionally, TPM is also used for signing the collected measured boot logs. These logs can also be used for remote

attestation of the platform before boot. TPM is also used to provide cryptographic store for Microsoft's BitLocker drive encryption capabilities. In different distributions of Linux operating systems, the concept of measured boot is still under development [34].

#### 2.5.3 Secure Boot in Embedded Systems

Unlike the PC market, embedded systems have a constrained environment for applications that are allowed to execute on a platform. Embedded systems and IoTs designers are much involved in the software development for the application stack. As such, it allows system designers to be more flexible in their approach. A group of researchers has proposed use of special architecture for implementing on chip security[35]. This work is mainly focused towards real time systems and allows secure loading of tasks, secure communication between processes and the mechanisms for local and remote attestation. TrustLite architecture extends the security to runtime by providing a hardware based exception handling and recovery mechanism [36].

As IoTs and embedded systems are designed to perform a specific set of tasks; this allows designers to perform control flow analysis of the entire system. Control Flow Integrity (CFI) analysis is one such static code analysis technique that records all possible branches a code can take. Using CFI, advanced code-based attacks such as Return Oriented Programming (ROP) can be mitigated. Using hardware based trusted isolated execution environments such as ARM's TrustZone, CFI can be implemented on an embedded system, where jump to each branch can be verified prior execution [37]. Hardware Performance Counters (HPCs) are special registers that count the occurrence of hardware events. These counters are used in performance tuning of applications. ConFirm architecture uses the HPC counters to count triggered events embedded in the control flow graph. CFI is ensured by use of these HPC counters [38].

There are also commercial embedded systems specific solutions for implementing

secure boot. NXP offers secure boot for their architectures. Their secure boot mechanism called High Availability Boot (HAB) is a part of the on-chip ROM. HAB provides a root of trust to the remaining software components running on top of the device. It can provide just signing or both signing and encryption for the software starting from the First Stage Boot Loader (FSBL). Efuses on a device must be configured to use the feature. Private keys are also stored on the efuses. Which means that one the keys have been generated, they cannot be changed. However, the system allows for up to four SRKs to be used. If needed, a SRK's use can be revoked. There is also support for open-source second stage boot loader U-boot for this technology to extend support to the Operating System, such as the Linux Kernel[39].

#### 2.5.4 Secure Boot in Reconfigurable Computing

Commercial FPGA vendors have increasingly incorporated new security features over the years, but that is not consistent across the reconfigurable devices and does not include legacy devices. These security features target various aspects of security, such as secure boot, encryption, and data integrity. Here, we give an overview of those features targeted towards Secure Boot. Zyng 7000 FPGAs, the FPGA SoC provides an AES 256 based encryption engine. Additionally, RSA asymmetric authentication is used to ensure an authenticated source. These functions are implemented as a hardware-based function on the FPGA fabric and are part of EDA tools with no access to the end user [24]. Both the encryption and authentication processes use keys to be defined before deployment. In the Zyng 7000 architecture, there are two ways of key storage, namely Battery-Backed RAM (BBRAM) and one-time programmable fuses. BBRAM is an on-chip volatile memory region, that has to be battery powered. One-time programmable efuses are configurable fuses that are burned into the fabric once they are programmed. There are caveats of using these technologies for holding keys. The BBRAM is dependent on the presence of a dependable power source. In the case there is any fluctuation in the power supply, the keys will be lost. On the other hand, the efuses are once programmable. In the case the programmed keys leak, there is no way to refresh them. Another serious flaw is that these keys are stored unencrypted in the memory. Access can be gained to them through physical means and through side channel attacks.

These cryptographic processes are invoked as part of the secure boot process implemented in the Xilinx provided zeroth stage boot loader called BootROM[24]. BootROM code exists in non-volatile memory on the FPGA fabric. It is executed by the Processing System on FPGA at the beginning of the boot cycle. Once the execution is completed by the BootROM code, control is passed to user-defined code, which can be an operating system or a user level application. The vendor provided no access to the code implementation of BootROM and neither is there any read or write access to the memory holding the BootROM code.

Much recently, in the newer Zynq UltraScale architecture, Xilinx has built upon the schemes in the Zynq 7000 architecture to add more security solutions[40][41]. The major revision is in the addition of Physical Unclonable Function (PUF) based key support. Whenever keys are generated for encrypting bitstreams, they are given as input to the on-board PUF to generate an encrypted key. This key can be stored onto the efuses, the BBRAM or externally in any unencrypted space. Since an attacker does not have access to the PUF implementation, they will not be able to decrypt the encryption key. Once the host system sends an encrypted bitstream to the FPGA board, the encrypted key is decrypted at runtime to reveal the bitstream decryption key. This key is used by the encryption subsystem to decrypt the bitstream.

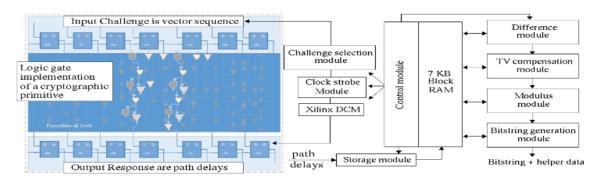

Recent work on the secure bitstream configuration at the boot level proposes the use of PUF technology and on-board peripherals for FPGA bitstream secure boot [42]. Internal Configuration Access Port (ICAP), that is a programmable interface[1], is used to retrieve the configuration of the current programmable logic. A Hardware-Embedded Delay Physical Unclonable Function (HELPUF[6]) uses SHA3 digest as

the challenge input. The generated output is used as a key for decrypting the image of the operating system and the application software to realize self- authentication. This enables the second stage boot loader to program the programmable logic PL and processing system PS. Since, vendor-provided secure boot is not used with this system, ICAP also allows readback of on-chip memory elements such as the block RAM and registers. If an adversary can capture the readback process, they will also be able to read the PUF output as well and therefore will have access to decryption keys.

Another recent work implements self-authentication of the logic fabric design and extends the protection to include processor design[43]. As opposed to [42], this work has employed the use of Elliptic Curve Cryptography based asymmetric keys with Diffie Helman key exchange for the key generation for encryption. A fuzzy key extractor is used to use extract hardware-based variations and to generate a key. This extracted key is used in the design by various cryptographic functions such as remote attestation and encryption key generation.

Dynamic Partial Reconfiguration (DPR) allows reconfiguration of pre-defined sections of the FPGA fabric during runtime. Static design reconfiguration requires the FPGA to be shut down before it can be reprogrammed. Following current security standards followed by FPGA manufacturers[44][24], the static encryption key must also be shared with the third party. Thus, adding more actors who would have access to the key. In [45], authors improve the security with the integration of hardware vendors in the distribution process. Each end device has a Unique ID. This ID is exchanged with the IP provider during an IP purchase transaction. The IP provider passes the unencrypted IP bitstream and the obtained ID of the end device to the vendor. The vendor has a database of IDs of end devices and their corresponding encryption keys. It encrypts the bitstream using the end device's stored encryption key before it is transmitted to the device. This solution does limit the issue of dis-

tribution of the encryption key between parties, however, promotes the use of static symmetric encryption keys. Attacks on vendor provided security, such as Xilinx's Secure Boot have also been reported. Outsourced trusted third-party IPs, based on their application also have access to the main memory of the system. Since the main memory is also used by secure boot to store the unencrypted Second Stage Boot Loader (e.g. U-boot) used by the system, a hardware trojan can target the main memory to manipulate the Second Stage Boot Loader to execute a malicious executable. [46] suggests wrapper logic to be added to IPs before the IP is connected to the system bus. Hardcoded configuration of the wrapper defines the scope of memory access by the connecting IP.

#### 2.6 Logic Locking

Logic locking is a technique for combating IP piracy. In the semiconductor industry, the chip designer has outsourced the manfucturing process to offshore untrusted foundaries. Because of the costs involved in manufacturing, there are separate industries that deal with design and manufacturing. Chip designers outsource their fabrication needs to these companies. For the IP design owners, it is difficult to monitor their IP at a remote site. Their IP may become a prey to piracy in the form of overbuilding, reverse-engineering and cloning.

Logic locking is a design for security mechanism that adds a lock into the circuit. Gates with key inputs are placed at various locations in the target circuit. Until the correct input key is not given as input, the circuit will not produce the correct output. Logic locking can be incorporated into the IC manufacturing process to mitigate IP piracy. [47] is one of the earliest solutions proposing use of logic locking via combinational locking. A combinational lock is embedded into the fabrication process. The key is kept hidden from the foundry and is only punched into the design, once the fabricated chip is returned to the vendor. The foundry not having access to the key is not able to unlock the chip. This method was defeated by [48],

as it notes that the method presented in [47] uses testing mechanisms that give out details of the implementation. [48] presents methods that factor the test pattern inputs. Logic locking is seen as a satisfiability problem. An attacker having access to the inputs and the system's expected responses, can use a satisfiability solver to solve for the key input values. This is known as a SAT attack[49]. Researchers were able to find the keys for 95% of the 441 locked circuits considered.

More recently, work has been done to make circuits resistant to SAT attacks. SARLock[50] is a mechanism that adds complexity by adding a masking block. If the key input cannot be asserted against a system input, the output is flipped. Therefore, the circuit cannot be probed without the correct key input. An alternate method to counter SAT attacks is Anti-SAT[51]. This method adds complexity to the output by adding another layer of logic. For incorrect key input, the output regardless of the expected output will either be a 0 or a 1 depending on the inputs. This way, an attacker will not be able to ascertain if the correct key input is given or not. [52] presents an attack mechanism for AntiSAT and SARLock. This work proposes to reduce the complexity of ANTI-Sat or SARLock locked circuit to the level where it can be solved by a SAT solver. It does by trying to find random key inputs that may reduce the output corruptibility for a system input. A recent approach towards implement logic locking is Stripped Functionality Logic Locking (SFLL)[53]. In SFLL, parts of the logic are removed from the logic circuit in a controlled manner. These removed parts are expected to be added to target device in the form key input dependent circuit.

# CHAPTER 3: Boot Time Security and Over-the-Air Update Mechanisms For FPGAs

#### 3.1 Introduction

Internet of Things (IoT) are ubiquitous devices that have limited functionality and computational resources with the capabilities of connecting with other electronic devices and the Internet. Additionally, they have long life cycles spanning over years. Changing requirements of a deployed embedded device are generally addressed through software or firmware updates. Software updates can be provided either manually or physically by using cables and programmer interfaces. Physical access to a device for firmware upgrade is always not possible and requires the configuration of the devices in the field through secure channels. The connected nature of IoTs makes them accessible remotely, and firmware updates for devices can be provided using Over the Air (OTA) firmware updates [54][55].

Software firmware updates change the functionality of the software; however, the scope is limited by the hardware capabilities and its architecture. Depending on the application and the expected life of a product, reconfigurable hardware architecture can improve the hardware update needs to evolve an IoT's device architecture. Reconfigurability allows the manufacturer to update the hardware design while the machine is in the field. Using OTA, hardware updates allows for updating the device hardware configuration without the need for physically replacing it. Over the air (OTA) updates are critical in the embedded system consumer domain such as the cellular phone and the automotive industry. The requirements for availability and quality of service is high in the growing and ubiquitous electronics on the move or electronics on the wheel. For the vehicular domain, the requirement for availability is

directly tied to safety. Furthermore, it is not feasible for a car owner to take the car to a service station, whenever there is a software update available. Instead, firmware updates can be provided remotely with OTA updates that can be transferred via the cellular network directly by the manufacturer[56].

Root of Trust is an anchor for implementing trust in a device[57]. Maintaining Root of Trust (RoT) is crucial once a device has been deployed in an untrusted field. Tainted firmware updates can break the trust. The software domain employs various techniques for maintaining Root of Trust. Some popular examples include Universal Extensible Firmware Interface (UEFI) secure boot extensions[58] and Microsoft Windows' Secure Boot[59]. The former provides maintaining Root of Trust at the boot level and the latter extends it to the operating system (OS) level. The root of trust at this level can also be implemented using cryptographic processors, such as Trust Platform Modules (TPM).

With new advancements, reconfigurable hardware has become pervasive in the Internet of Things domain, there is a requirement for extending the root of trust to the hardware. Commercial FPGA vendors provide limited security to the programmable logic fabric and those security mechanisms are limited in application. Additionally, the provided methods have closed access which the users can use in their systems but cannot inspect themselves. There is a need for an open and reliable security structure for the programmable fabric that can be integrated into the device's Root of Trust.

In this work, we present a framework to establish the Root of Trust for secure boot and OTA updates of reconfigurable hardware. Bi-directional or mutual trust is established between an FPGA device and server or the content provider. A scheme for the provision of symmetric encryption keys is also presented. The novelty of this work also extends into the integration of TPM with FPGA boot process to assist in secure boot, key provisioning, and secure communication. Additionally, we present schemes for runtime mitigation of malicious logic insertion.

## 3.2 Threat Model for Secure Boot of FPGA Bitstreams

The FPGA market is dominated by proprietary tools, Intellectual Properties (IPs) and closed hardware implementation. There are a handful of vendors that provide varying architectures and interfaces to those architectures. It forces reliance on the vendor and the effectiveness of their often, closed source tools. The reconfigurable fabric on FPGAs is programmed using bitstreams. The bitstream configures the Look Up Tables (LUTs) in the logic fabric. These LUTs act as combinatorial logic and sequential data paths for the hardware design. Bitstreams also configure other fabric elements, e.g. on-chip memory, Digital System Processing (DSP), clocking blocks and wire connections. An attack on the bitstream can affect the entire system operation of a device on the field. This work focusses its efforts towards the security of the bitstream on the device and on providing security between a content provider and a device.

# 3.2.1 Bitstream Spoofing

Bitstream spoofing is a way of updating the victim device with an update that may seem to come from an authorized source. One way for performing bitstream spoofing is by the use of relay and replay attacks[60]. An adversary can act as a man in the middle between a bitstream content provider and a device. Once an authenticated session has been set up between the two nodes, the adversary can replace the original bitstream with a malicious one. Additionally, in case where the victim device is using one single key for bitstream encryption, replay attacks can be used by an adversary. An attacker can forward an older copy of the bitstream which has limited functionality compared to the current version.

# 3.2.2 Runtime Malicious Modification

Our work focuses on mitigating malicious logic insertion in the bitstream during runtime. Once a bitstream has been programmed onto an FPGA programmable logic fabric, an FPGA device may provide interfaces to the outside world for readback and modification of the running bitstream[61]. Using these interfaces, faults or trojans can be introduced in the design[62]. Additionally, the same interfaces can be used to make unauthorized modifications to the original design.

## 3.2.3 Non-secure Communication with Content Provider

For an FPGA device placed in the field, bitstream updates can be provided manually physically by an engineer, through a physical update mechanism or through the use of remote updates over a network. If a content provider over a network is not secure, an adversary may spoof its identity to send malicious updates. On the other hand, an adversary can also impersonate a device on the field to download bitstream updates from a content provider not meant for it.

#### 3.3 Root of Trust Architecture

In the proposed scheme there are two actors, the content provider or the server and client nodes. The content provider is a server that exists over a network for all client nodes. It serves the latest bitstream to all clients. A client node is any authorized FPGA device that is connected to the network of nodes. The authentication and authorization privileges for a client to join the network is open to the implementation and is left at the discretion of the designer. There are two components in this framework, namely the proposed hardware and the Secure First Stage Boot Loader (SFSBL).

#### 3.3.1 Hardware Overview

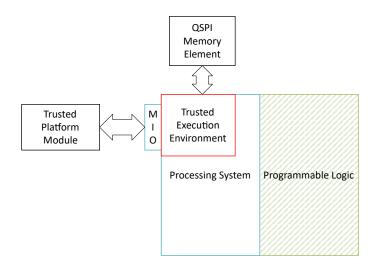

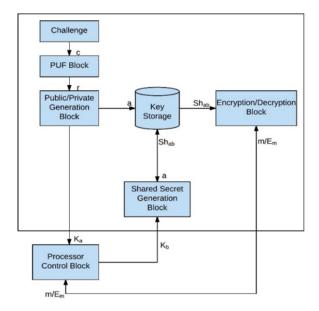

The reference reconfigurable platform is an SRAM based FPGA SoC that has a hard-core Processing System (PS) and a Programmable Logic (PL) fabric. The PS is a trusted verifier and the PL design is the prover. The verifier is a trusted source, whereas the prover needs to prove its legitimacy to the verifier. We investigate the secure co-processor integration with the SoC and export the security functions and key

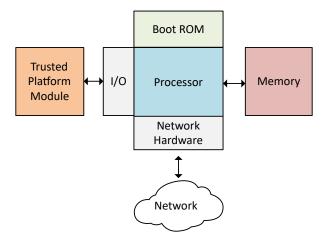

Figure 3.1: Proposed Secure Boot System Architecture.

provisioning onto an external cryptographic processor, such as the Trusted Platform Module (TPM).

To provide isolation for a higher level of security functions that is for Secure OTA update functions, the framework uses a Trusted Execution Environment (TEE), such as ARM's TrustZone. TPM is interfaced using the Multiplexed Input /Output (MIO) port of the FPGA via serial SPI interface on Xilinx Zynq 7000 series FPGA. An MIO port is directly connected to the hard core of the PS and does not require any additional routing from the PL. The MIO based connection to the TPM is essential since in the case PL based configuration is used, the PL will be needed to be programmed first, thus introducing a possible attack vector for the target platform.

To mitigate any damage caused due to privilege escalation attacks, PL programming port and the TPM are configured to be accessible only through TrustZone's secure world. The prototype is tested on the Xilinx platform that incorporates external Quad Serial Peripheral Interface (QSPI) based flash memory to hold the SFSBL and the bitstream. The write access to the flash memory is limited to TrustZone configured secure world. This hardware is described in Figure 3.1.

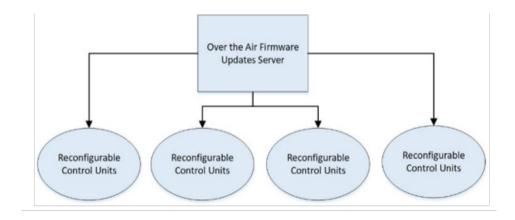

Figure 3.2: Content Provider client FPGA's connection.

# 3.4 Design Objectives and Operations

The proposed framework is designed to provide three security services for reconfigurable hardware, namely establishing a source of trust, secure over the air updates and secure boot process.

## 3.4.1 Establishing Source of Trust

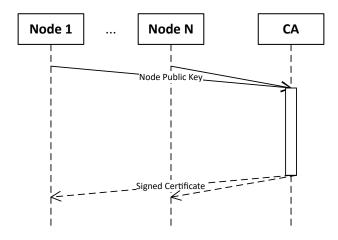

A content provider/server may serve multiple client nodes, as illustrated in Figure 3.2. The server is assumed to be secure. To establish the identity of the content provider and a client node, asymmetric digital keys are used. The proposed framework uses Elliptic Curve Digital Signature Algorithm based NISTP256 curve keys [63] for data signing. A pair of asymmetric signing keys are generated on the server as well as each client node. The client nodes use the equipped TPM to generate the key pairs. Additionally, a unique shared symmetric key is generated for each client. This key acts as a base encryption key( $K_b$ ) and is updated during the bitstream update process. The update process of the symmetric encryption key is discussed in detail in the following subsections. A client's own private key ( $K_{cpr}$ ), public key ( $K_{cpb}$ ), the server's public key ( $K_{ps}$ ) and the base encryption key are stored on a client's TPM, in its NVM. The exchange of keys occurs in a trusted environment. The server's private

key (K<sub>rs</sub>) does not leave the system.

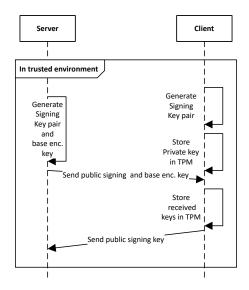

Figure 3.3: Key exchange in a trusted environment.

The server maintains a database of all its client's public keys and the base encryption keys. This system supports key renewal; however, the lifetime of the keys is left at the discretion of the system designer. To mitigate chances for key theft, it is assumed that the renewal process occurs in a trusted environment. Once deployed, the public key of the server and private key of the client cannot be retrieved from the TPM, however, they can be addressed for use within the TPM. The key exchange process is illustrated in Figure 3.3.

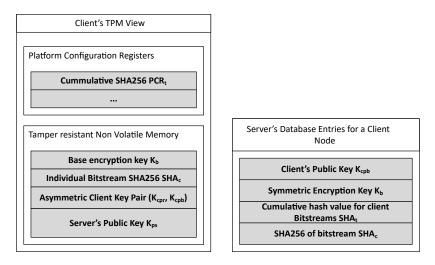

Bitstreams are stored in the QSPI Flash on the hardware. The initial bitstream is stored by the vendor in the trusted field. The proposed framework uses Platform Configuration Registers (PCR) to measure the boot process and to maintain prolonged integrity of the bitstream. PCR register, PCR<sub>t</sub> is used to store the cumulative SHA256 of all the bitstreams loaded onto the client. Initially, the value of PCR<sub>t</sub> is set to the SHA256 of the initial bitstream. The server also calculates the same cumulative hash locally (SHA<sub>t</sub>). For use during secure boot at the client, the SHA256 of the bitstream (SHA<sub>c</sub>) is stored on the NVM in the TPM. Figure 3.4 shows the keys

Figure 3.4: Keys shared between a client and server.

on a client node and shared between a server.

## 3.4.2 Secure Over the Air (OTA) Update Mechanism

When the updated bitstream available on the server, the connected and authorized client nodes receive a notification from the server. This triggers a client to initiate secure communication with the server. At a client, the mode of operation switches from normal mode to the update mode. The update mode is handled by the trusted execution environment at the client. In the case of TrustZone, the processor mode switches from the non-secure world to the secure world. The update process is assigned its own memory area, isolated from the non-secure world. The update procedure consists of the following processes:

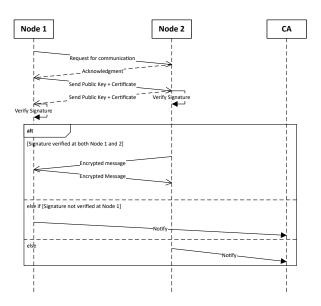

## 3.4.2.1 Secure Communication Handshaking

To enable secure communication between the server and the client, as well to maintain that the integrity of the bitstreams is maintained between two subsequent updates, we propose a handshaking scheme. The scheme is summarized in Figure 3.5. A client generates a True Random Number (TRN<sub>a</sub>) using the True Random Number Generator equipped on the TPM. The PCR register value PCR<sub>t</sub> is XORed with TRN<sub>a</sub> and is then symmetrically encrypted using the base encryption key  $K_b$ .

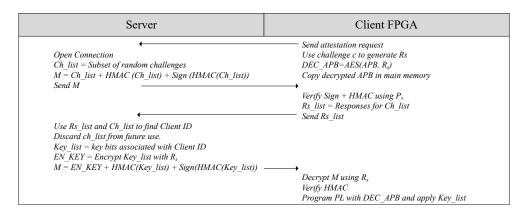

Figure 3.5: Server Client Interaction for Bitstream Updates.

$$m_e = AES128((PCR_t \oplus TRN_a), K_b) \tag{3.1}$$

The construction of the encrypted message  $(m_e)$  is shown in Equation 3.1. Hash of  $m_e$  is asymmetrically signed using  $K_{cpr}$ . Message  $m_e$  and its hash is sent to the server. After transmission, the  $K_b$  is updated client side by taking a XOR with  $TRN_a$ .  $K_b$  on the TPM is also replaced with the newly computed value. Equation 3.2 illustrates the update process.

$$K_b = K_b \oplus TRN_a \tag{3.2}$$

The server using its copy of  $K_{cpb}$  recalculates the hash of the received message  $m_e$ . Once the client has been authenticated, the server decrypts me using the stored key  $K_b$ . To retrieve  $TRN_a$ , the server computes the XOR of  $SHA_t$  with the decrypted message. Like the client node,  $K_b$  is updated at the server.

## 3.4.2.2 Secure Update Packaging and Transfer

The bitstream update is compiled into an archive package before it is sent to a client. Using the bitstream update and  $SHA_t$ , the server calculates the new cumulative hash and updates  $SHA_t$ . The updated bitstream and  $SHA_t$  are combined and encrypted using the updated key  $K_b$ . This encrypted block is copied to the update archive

Figure 3.6: Bitstream Update Archive

package along with its SHA256 value. The SHA256 value is signed using its own private key  $K_{rs}$ . The signature is appended to the package. This update archive is sent to the client. The client stores the package in its NVM and triggers the update process. Figure 3.6 shows the archive package.

# 3.4.2.3 Applying the update

The process of applying the update on the target platform is handled by the secure update process running on the client FPGA. Once the bitstream package has been downloaded, SHA 256 of the package is recalculated client side and is compared with that in the download package. The signature of the computed hash is recomputed using the key  $K_{ps}$  on the TPM. This signature is compared against the signature packaged in the update archive. Once the identity of the server has been verified, the encrypted archive is decrypted using  $K_b$ . Using the TPM PCR functions, PCR<sub>t</sub> is updated and verified against the archived SHA<sub>t</sub> value. If the updated PCR<sub>t</sub> and SHA<sub>t</sub> values are equal, the initial bitstream on the NVM is replaced by the update, otherwise if in case any check fails during the update process, the node is assumed to be compromised and the server is notified. On completion of the update process, the individual SHA256 of the bitstream calculated and SHA<sub>c</sub> is updated. The process is

Figure 3.7: Bitstream Update Application Process

described in the flowchart in Figure 3.7.

#### 3.4.2.4 Secure FSBL Boot Process

We have designed a Secure First Stage Boot Loader(SFBSL) that is integrated with the Trusted Platform Module with custom device drivers that enable the device to communicate with the TPM before the device has booted. In an FPGA, the zeroth stage boot loader referred to as BootROM is executed by the Processing System on FPGA at the beginning of the boot cycle. BootROM code exists in a non-volatile memory of the FPGA fabric and is assumed to be secure. Once the BootROM has completed its execution, the control is passed to the proposed SFSBL that exists in the on-board QSPI memory. The SFSBL code extends and integrates the security functions to the FSBL. FSBL configures the device with the hardware bitstream and configures the processing system with a bare-metal application or loads the second stage boot loader to the RAM. This, in turn, loads the operating system. The vendor FSBL design does not verify the integrity of the bitstream or what it is programming the processing system. This lack of security at the boot process can be circumvented with the proposed secure FSBL that integrates key management and security features to validate the configuration files before programming the device.