# ENHANCED THERMALY MANAGED PACKAGING FOR III-NITRIDE LIGHT EMITTERS

by

# Nicolas Kudsieh

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctorate of Philosophy in Optical Science and Engineering

Charlotte

2014

| Approved by:             |

|--------------------------|

| Dr. M. Yasin Akhtar Raja |

| Dr. Muhammad Khizar      |

| Dr. Vasily Astratov      |

| Dr. Yong Zhang           |

| Dr. Gregory Gbur         |

| Dr. Janos Gergely        |

©2014 Nicolas Kudsieh ALL RIGHTS RESERVED

#### **ABSTRACT**

NICOLAS KUDSIEH. Enhanced thermally managed packaging Of III-nitride light emitters. (Under the direction of Dr. M. YASIN AKHTAR RAJA and Dr. MUHAMMAD KHIZAR)

In this Dissertation our work on 'enhanced thermally managed packaging of high power semiconductor light sources for solid state lighting (SSL)' is presented. The motivation of this research and development is to design thermally high stable costefficient packaging of single and multi-chip arrays of III-nitrides wide bandgap semiconductor light sources through mathematical modeling and simulations. Major issues linked with this technology are device overheating which causes serious degradation in their illumination intensity and decrease in the lifetime. In the introduction the basics of III-nitrides WBG semiconductor light emitters are presented along with necessary thermal management of high power cingulated and multi-chip LEDs and laser diodes. This work starts at chip level followed by its extension to fully packaged lighting modules and devices. Different III-nitride structures of multi-quantum well InGaN/GaN and AlGaN/GaN based LEDs and LDs were analyzed using advanced modeling and simulation for different packaging designs and high thermal conductivity materials. Study started with basic surface mounted devices using conventional packaging strategies and was concluded with the latest thermal management of chip-on-plate (COP) method. Newly discovered high thermal conductivity materials have also been incorporated for this work. Our study also presents the new approach of 2D heat spreaders using such materials for SSL and micro LED array packaging. Most of the work has been presented in international conferences proceedings and peer review journals. Some of the latest work has also been submitted to well reputed international journals which are currently been reviewed for publication.

#### **DEDICATION**

This dissertation is not merely the result of one person's hard work. This dissertation was completed through the love and support of many unique individuals who gave everything to make this work a reality. I dedicate this Dissertation first to my aunt Souhila Kudsieh whom always had faith in me and spent her life pushing me in the right direction of knowledge. I also dedicate this work to my parents Salim & Fadia Kudsieh for all the love they gave and the hardships they endured to make this day come true. I also dedicate this dissertation to my guarding angles Farid & Mary-Jean Tranjan who helped me every step of the way to finish my studies and were my family for the last seven years. Mind always asks the how-questions, however only heart asks the why-questions. I found my answer in my love and life partner Elaine whose love and kindness were the final motivation in finishing this work. In all religions God knows everything, and I believe that we as humans are created to ask questions and seek answers. The more we know the closer to our creator we become so let us make knowledge be our stairs to heaven.

#### **ACKNOWLEDGEMENTS**

First of all, I would express my sincere thanks to Professor M. Yasin Akhtar Raja and Dr. Muhammad Khizar, my advisors for their support and guidance throughout my academic career. I would like to thank the Department of Physics and Optical Science at the University of North Carolina at Charlotte for all the academic, technical and financial resources that were generously provided. I acknowledge the Graduate School for the Graduate Assistant Support Plan (GASP) for being an immense supporter throughout my years of study. Special thanks are due to my dissertation committee members, Dr. Vasily Astratov, Dr. Gregory Gbur, Dr. Yong Zhang, and Dr. Janos Gergely for their input, valuable discussions, suggestions, and their time. I would also like express my sincere gratitude towards Professor Farid Tranjan and Dr. Awad Gerges for their invaluable mentorship, support, and patience. I would like to express special thanks to Professor Angela Davies and Mr. Mark Clayton for their continued administrative support, official paper work, and timely directions. Finally, I would like to thank my fellow OSE program graduate students for all the comradery, and growth opportunities they provided both directly and indirectly during my graduate school period for MS and PhD and I wish them all the best of luck in their future endeavors. In the last but not the least I want to acknowledge with gratitude the support I enjoyed from parents and family, as well as recently from my fiancé' and her family.

# TABLE OF CONTENTS

| CHAP  | TER 1: INTRODUCTION AND BACKGROUND                                        | 1  |

|-------|---------------------------------------------------------------------------|----|

|       | 1.1 Wide Bandgap Semiconductors as Light Emitters                         | 1  |

|       | 1.2 Bandgap Engineering of WBG Semiconductor Emitter Structures           | 5  |

|       | 1.3 Device Packaging, Needs and Considerations                            | 17 |

|       | 1.4 Surface Mounted Devices (SMD)                                         | 20 |

|       | 1.5 Flip-Chip Mounted Device (FCD)                                        | 22 |

|       | 1.6 Heat Effects on High Power LEDs                                       | 24 |

|       | 1.7 Summary                                                               | 29 |

| CHAP  | TER 2: DESIGN AND NUMERICAL METHODS                                       | 32 |

|       | 2.1 Research Development                                                  | 32 |

|       | 2.2 Modeling and Simulation Tools                                         | 37 |

|       | 2.3 Mathematical Model                                                    | 45 |

|       | 2.4 Summary                                                               | 51 |

| CHAP' | TER 3: TRANSIENT THERMAL ANALYSIS OF InGaN/GaN HIGH<br>POWER LASER DIODES | 53 |

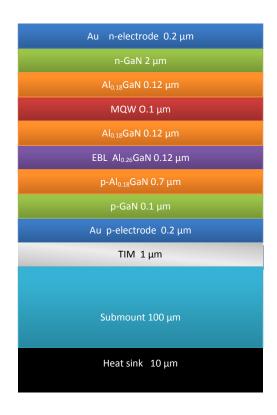

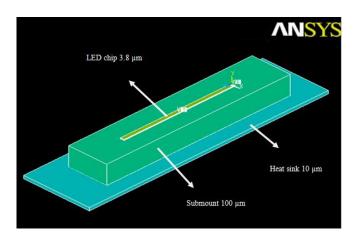

|       | 3.1 Device Structure and Design                                           | 53 |

|       | 3.2 Modeling and Simulation                                               | 56 |

|       | 3.3 Results and Discussion                                                | 61 |

|       | 3.4 Summary                                                               | 69 |

| CHAPTER 4: ON-CHIP SIMULATION AND THERMAL ANALYSIS OF AlGaN/GaN ULTRAVIOLET LIGHT EMITTING DIODES | 71  |

|---------------------------------------------------------------------------------------------------|-----|

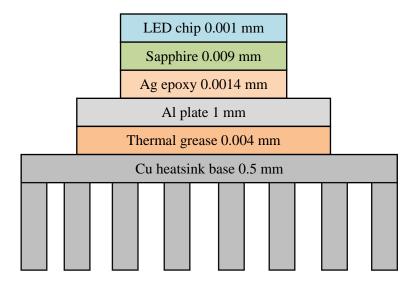

| 4.1 Device Simulation and Packaging Materials of AlGaN/GaN UV LEDs                                | 72  |

| 4.2 Device Packaging Design and Materials                                                         | 76  |

| 4.3 Thermal Modeling and Simulation                                                               | 78  |

| 4.4 Package Thermal Resistance Circuit Model                                                      | 80  |

| 4.5 Results and Comparative Study                                                                 | 83  |

| 4.6 Summary                                                                                       | 92  |

| CHAPTER 5: THERMAL ANALYSIS OF COP PACKAGED AlGaN/GaN BACK-EMITTING LEDS                          | 94  |

| 5.1 Chip-on-Plate (COP) Packaging Technique                                                       | 94  |

| 5.2 Multiple Package Designs Modeling                                                             | 97  |

| 5.3 Thermal Modeling                                                                              | 100 |

| 5.4 Thermal Resistance Model for Advanced Packaging                                               | 102 |

| 5.5 Results and Discussions                                                                       | 106 |

| 5.6 Summary                                                                                       | 115 |

| CHAPTER 6: HIGH POWER LED ASSEMBLIES FOR SOILD-STATE LIGHTING                                     | 118 |

| 6.1 LED Assemblies General Considerations                                                         | 119 |

| 6.2 LED Assembly's Thermal Uniformity Analysis                                                    | 121 |

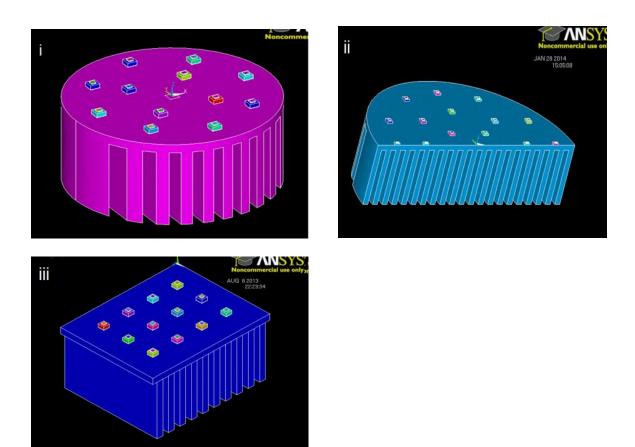

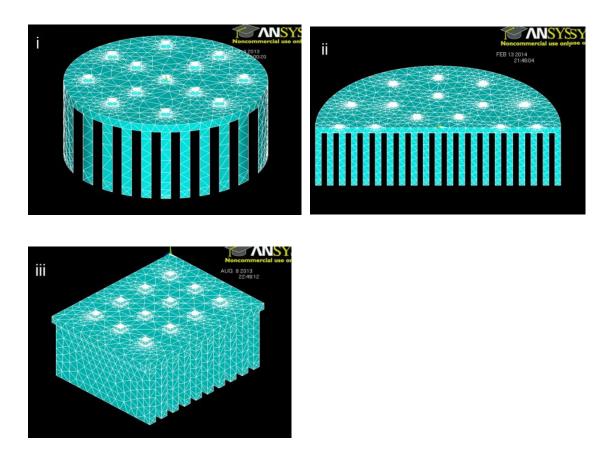

| 6.3 Light Modules Modeling                                                                        | 126 |

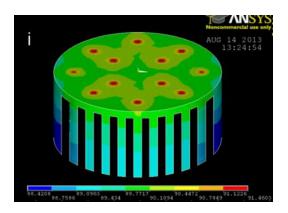

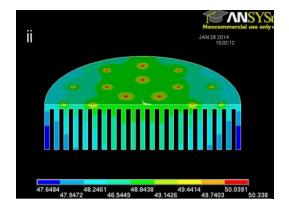

| 6.4 Results and Discussion                                                                        | 129 |

| 6.5 Summary                                                                                       | 134 |

| CHAPTER 7: NOVEL GRAPHENE HEAT SPREADERS FOR MIRCO LED ARRAYS                 | 135 |

|-------------------------------------------------------------------------------|-----|

| 7.1 Graphene's Thermal Properties and Heat Spreaders Potential                | 136 |

| 7.2 Proof of Concept Package Modeling                                         | 138 |

| 7.3 Graphene Heat spreaders for micro-LED arrays                              | 140 |

| 7.4 Micro LED Array Structure Modeling                                        | 142 |

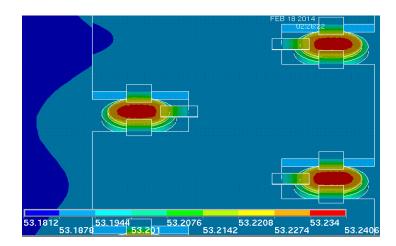

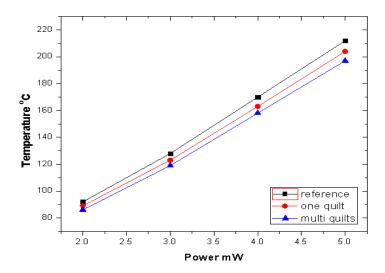

| 7.5 Results and Comparative Study                                             | 145 |

| 7.6 Summary                                                                   | 149 |

| CHAPTER 8: CONCLUSION                                                         | 150 |

| 8.1 Thermal Analysis of InGaN/GaN Laser Diodes                                | 150 |

| 8.2 On-chip Thermal Analysis of AlGaN/GaN LD and Packaging Material Selection | 151 |

| 8.3 Chip-on-plate Packaging and Heat Sink Design                              | 151 |

| 8.4 Thermal Analysis of LED Assemblies                                        | 152 |

| 8.5 Graphene Heat Spreaders for Micro-LED Arrays                              | 153 |

| 8.6 Future Work and Research Intentions                                       | 153 |

| REFERENCES                                                                    | 154 |

| APPENDIX A: TIM MODELING DATA                                                 | 165 |

#### CHAPTER 1: INTRODUCTION AND BACKGROUND

Photonic devices such as solid-state light emitters have gained tremendous attention over the last two decades for their unique features and commercial applications. Light Emitting Diodes (LEDs) and Laser Diodes (LDs) became very common in many applications enabling compact lighting, information transmission, storage, and flat-panel displays. Compact size and durability makes such devices ideal to be embedded in other systems or modules such as cell phones, computers, flat-panel TV screens and other displays [1]. Wide variety of semiconductor materials offer a broad spectral range of light emitters that meets the demand for many applications such as, data storage, chemical sensing, displays, traffic signals and of course the solar cells the inverse of the lightemitters. The growth of semiconductors light sources applications has increased their market share of the systems used in their fabrication as well. Millions of dollars are invested in such technologies; statisticians expect increasing demand on MOCVD systems that won't be even met before 2015 [2]. Additional systems such as wafers scribing and dicing, wafer level packaging, wire bonding, flip-chip bonding and thermal packaging equipment are also in high demand and keep increasing which reflects the growing production of LEDs/LDs modules and light engines in the consumer market.

#### 1.1 Wide Bandgap Semiconductors As Light Emitters

III-V wide bandgap semiconductors have always been categorized as most suitable material system for light sources, which heavily depend on their energy-band

structures. Doped semiconductors have extra free charge carriers - electrons and holeswhich tend to exist in the lower more stable energy states in thermal equilibrium [3]. Two main energy levels involved in light emission process, are conduction- and valence-bands. In thermal equilibrium the free-electrons will be at the bottom of the conduction-band and holes will be at the top of the valence-band. Suitable electron excitation/injection will cause electrons to jump across the bandgap up to the lower states of the conduction-band. After a series of relaxation transits within the conduction band [4], electrons will end up in the bottom of the conduction band. Light is emitted when an electron drops from the bottom of the conduction-band to fill a hole in the top of the valance-band, this process releases amount of energy equal to the bandgap in the form of electro-magnetic waves (photons) with energy

$$E = h \times \nu$$

1.1

where v is the frequency of the emitted photon.

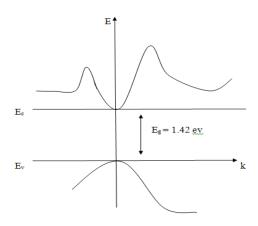

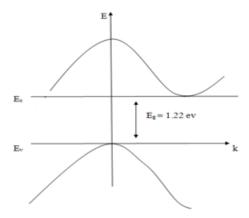

Semiconductors materials that have the conduction-band minimum states and valence-band maximum states corresponding to the same value electron momentum (wave-number/k vector) are called direct bandgap materials while semiconductors that have the former values of minima and maxima corresponding to different momentum values are called indirect bandgap materials [5]. It was found that direct bandgap materials are efficient photon emitters because the process of absorbing and emitting energy satisfies the conservation momentum and energy principles without the need of any extra momentum changes and would make photon emission process a higher probability [3]. As for indirect bandgap such as Silicon, extra momentum is needed to

satisfy the conservation laws and that is achieved by emitting or absorbing phonons, this results in more relaxation time of the electron in the conduction-band and decrease the probability of photon emission thus all semiconductor light sources uses direct bandgap materials. Figures 1.1 and 1.2 shows the part of band structure of both direct and indirect bandgap semiconductor materials, respectively [3]

Figure 1.1: Direct bandgap structure in GaAs [3]

Figure 1.2: Indirect bandgap structure in Si [3]

Elemental semiconductors provide limited selection of wavelengths due to their inherent energy band structures, in addition to the fact that most of them are indirect bandgap materials. For the indirect bandgap, semiconductors the momentum vectors of holes in the maxima of valence-bands and  $K_e$  of electrons in the minima of conduction bands are different. Therefore, the momentum conservation requires phonon emission this affects the radiative recombination lifetime and rate and makes—photon emission process less probable [6]. On the other hand compound semiconductors such as binary III-V like GaAs or GaN as well as several II-VI semiconductors have their minima of conduction and maxima of valence bands match as K=0. Thus, they readily satisfy momentum conservation along with energy conservation for recombining carriers (electrons-holes) and resulting photons [4]. These compound semiconductors provide a wide range wavelength selection. Table 1.1 shows some compound semiconductor materials and their bandgap and the accompanied emission wavelengths.

Table 1.1: Common semiconductor compounds bandgap and emission wavelengths [3]

| Material | Bandgap type | Bandgap energy | Bandgap emission |

|----------|--------------|----------------|------------------|

|          |              | (eV)           | wavelength (nm)  |

| GaN      | D            | 3.39           | 366              |

| GaP      | I            | 2.26           | 549              |

| GaAs     | D            | 1.42           | 873              |

| GaSb     | D            | 0.73           | 1700             |

| AlAs     | I            | 2.16           | 574              |

# 1.2 Bandgap Engineering of WBG Semiconductor Emitter Structures

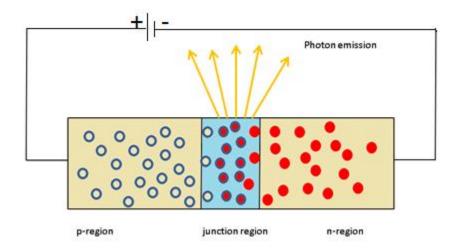

Conceptually, semiconductor light sources are made by combining two high-quality thin layers of p- and n- doped direct bandgap semiconductor materials together on an appropriate substrate. Metallic electrodes are added to the structure for applying a suitable forward voltage to inject current. Driving voltage injects the free electrons from the n-side towards the p-side while pushing holes from the opposite direction so that excitons (e-h pairs) are formed in the junction region [6]. Light is generated when electrons and holes combine radiatively. In other words, when electrons fall from the bottom of the conduction-band to fill a hole at the top of the valence-band photons are emitted. Wavelength of the emitted light is dependent on the bandgap of the material. Intensity of the emitted light is dependent on the number of electron-hole pairs that recombine radiatively in the junction region. LEDs and LD devices are made of appropriate layers of semiconductor materials that are deposited on the suitable substrate using various techniques such as MBE (molecular beam epitaxy), MOCVD (metalorganic chemical vapor phase epitaxy), e-beam evaporation, and gas ions sputtering.

Most of the LEDs or LD structures are fabricated at thicknesses of several micrometers scale with internal layers of several nanometers thickness. Using photolithographic and etching process various LEDs and LDs dies are mass produced on relatively large area wafers with diameters from 0.5 to 6 inches. Metal contacts are then deposited on both p and n regions for current injection and then tested. For non-conducting substrates, the processed devices wafers must be etched to expose the n-layer of the device for probing/injecting current into the device. Individual devices are

obtained by slicing and dicing the wafers. Figure 1.3 below shows the basic structure and operation of a semiconductor light emitter.

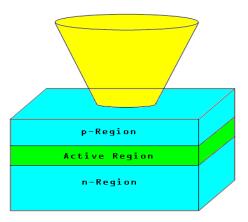

Figure 1.3: Basic structure of a LED device

The main parameter that determines the quality of a semiconductor light emitter is the internal quantum efficiency  $\eta$ , which is the ratio between radiative and non-radiative electron-hole recombinations. It can also be defined as the ratio between the number of photons emitted to the number of electrons excited to conduction band. The higher the internal quantum efficiency the better the device will be. Never the less, it is the external quantum efficiency that matters the most because it represents the light output of the device. It has been found that the external quantum efficiency is always smaller that

internal quantum efficiency due to many factors such as total internal reflection and diffraction limitations. Increasing external quantum efficiency is a major part of the device design and packaging process and it will be discussed thoroughly in the following chapters.

Within the doped semiconductor material electron-hole recombinations have certain rates of occurrence per unit time, the total rate of these recombination include both radiative and non-radiative ones.

Considering the rate of radiative recombinations  $R_r$  and the rate for non-radiative recombination  $R_{nr}$ , the total rate of recombinations can be written as [3]:

$$R = R_r + R_{nr} 1.2$$

Based on the definition of internal quantum efficiency  $\eta$  is calculated as follows:

$$\eta = \frac{R_r}{R_r + R_{nr}}$$

1.3

Whereas, the internal quantum efficiency can also be written in terms of the lifetime of each type of recombinations. Considering the lifetime of radiative recombination is  $\tau_r$  and the lifetime of non-radiative recombination is  $\tau_{nr}$ ,  $\eta$  can be expressed as:

$$\eta = \frac{\tau_{nr}}{\tau_r + \tau_{nr}}$$

1.4

Examining equation 1.4 it can be seen that for a semiconductor material to have high internal efficiency  $\tau_r$  must be much smaller than  $\tau_{nr}$ . In this case radiative recombinations will have much higher rate and overcome non-radiative recombinations.

This explains why indirect bandgap semiconductors are poor emitters, because the shape of the energy bands electrons has to pass several relaxation stages by emitting phonons this process will increase the lifetime for radiative recombinations therefore decrease the quantum efficiency. For example Si, which is an indirect bandgap material, has  $\tau_r = 10$  ms while  $\tau_{nr} = 100$ ns this results in Si have internal quantum efficiency of  $10^{-5}$ .

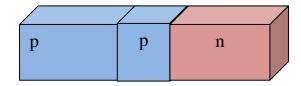

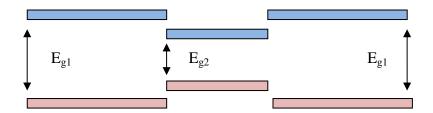

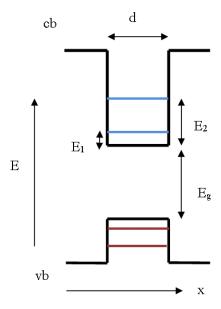

Conserving high concentration of opposite charge carrier in the junction region is a very important factor to increase internal quantum efficiency however due to the forward biasing of such devices charge carrier may leak from the junction region to the opposite layer of the device where they are not desired and most likely to end up in nonradiative recombinations. Thus it is useful to keep the free carriers confined within the junction region. One of the common methods to achieve charge carrier confinement is the double heterojunction [4]. This technique is achieved sandwiching a smaller - usually p-doped- bandgap material between two opposite-doped larger bandgap material slabs, bandgap difference between the middle material and the side ones creates localized jumps in bandgap diagram, this discontinuity creates barrier that prevent selected charge carries form diffusing to undesired regions in a p-n junction type devices. This will also reduce the minority carrier current and increase the confinement of majority charge carrier in the junction region. Figure 1.4 shows the basic structure for p-p-n double heterojunction usually used in semiconductor light emitters. Figure 1.5 shows the energy bands diagram for such structure.

Figure 1.4: A Double p-n heterojunction structure

Figure 1.5: Energy band structure for a double heterojunction p-n device

The use of different bandgap semiconductor materials within the same device allows the selection of specific regions of the structure where light is absorbed. On the other hand, semiconductor materials with bandgap larger than the photon energy would be transparent and considered as window layers. Different bandgap energies will also give rise in refractive index difference; this difference can be used to create optical waveguides within the structure due to total internal reflection (TIR) [7].

The concept of confinement using double heterojunction was further improved by the introduction of quantum confinement structures. It was found that when the thickness of the middle layer of a double heterojunction is compared or smaller than de Broglie wavelength of the thermal electron of the material. The energy of the electron residing in this layer has to be quantized and limited into specified levels. This creates much better confinement and also allows the selection of desired energy levels needed for the desired emission spectra (wavelength). Each electron will have three degrees of freedom (x,y,z), the introduction of quantum confinement structures will decrease these degrees of freedom accordingly. 1D confinement is achieved by creating quantum wells within the structure a thin enough layer ( $\leq 50$  nm in the case of GaAs) by sandwiching it between two layers of a larger bandgap materials (barrier layers).

Figure 1.6 shows the energy bands diagram in a quantum well structure along with the allowed energy levels within the quantum well in a semiconductor material. The allowed energy levels of a particle of mass m confined in one dimensional infinitely deep quantum well is given as [4]:

$$E_n = \frac{n \cdot h^2 \pi^2}{2md^2}$$

$n = 1, 2, 3, 4, 5, \dots$  1.5

Where h is Planck's constant

m is the mass of the electron

d is the width of the quantum well

Figure 1.6: Energy levels diagram for one dimensional quantum well of semiconductor material

Considering the 1D case presented above it can be seen that electrons are only confined in the x-direction, so they should be treated as if they move in bulk semiconductor material in the (y,z) plane. The general electron energy-momentum equation in the conduction band of a bulk semiconductor is given as[4]:

$$E = E_C + \frac{h^2 k_1^2}{2m_c} + \frac{h^2 k_2^2}{2m_c} + \frac{h^2 k_3^2}{2m_c}$$

1.6

Where  $k_1$ ,  $k_2$ , and  $k_3$  represent the wave vector in x,y,z directions, respectively and  $E_c$  is the electron energy at the bottom of the conduction band. Considering the one dimensional quantum well case presented above the energy in the x direction is quantized and equation 6 can be written as [4]:

$$E = E_C + E_{nx} + \frac{h^2 k_2^2}{2m_C} + \frac{h^2 k_3^2}{2m_C}$$

n= 1, 2, 3, 4, 1.7

Equation 1.7 shows that the x component of the electron energy is now limited to quantized values which mean that the motion of the electron in the x direction is also limited by the allowed values of  $k_1$  which means confinement.

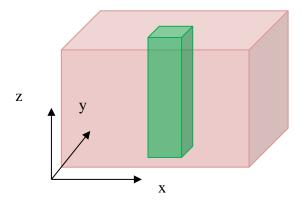

Further confinement can be achieved using different structures. For 2D confinement quantum wires are utilized where a thin wire of lower bandgap material is surrounded by a wider bandgap material if the wire was oriented in the z direction then electron energy components on both x and y will be quantized as presented in equation 5, electrons will move in the z direction as if they were moving in a bulk wire material. Figure 1.7 shows 3D structure of quantum wire.

Figure 1.7: Basic quantum wire stretched in the z direction of semiconductor material

This type of 2D confinement changes the energy-momentum equation for electrons in the conduction band as follows [4]:

$$E = E_C + E_{nx} + E_{my} + \frac{h^2 k_3^2}{2m_c}$$

n,m = 1,2,3,4,... 1.8

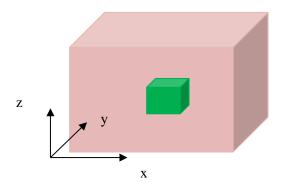

Carrier confinement can be extended to 3D by using Quantum dots, these structures composed of islands of low-bandgap semiconductor materials surrounded by higher-bandgap materials from all directions. The size if these dots should also be comparable to De Broglie wavelength cubed. Figure 1.8 illustrates the basic structure of a single quantum dot. In such structures the quantization of energy is achieved in all directions this would increase the selectivity of the desired energy levels involved in light emission and narrows the emission spectrum of the semiconductor light source.

Figure 1.8: Basic quantum dot structure

Total energy of the electron in the conduction band is now fully quantized as can be seen in equation 1.9 below [4]:

$$E = E_C + E_{nx} + E_{my} + E_{lz}$$

$n,m,l=1,2,3,4,...$  1.9

Although the basic structure of a LED or LD is a p-n junction, with a double heterojunction, or multi quantum wells (MQW), but there are many additional material layers needed to create efficient light emitters. Substrates and sometimes interface layers are needed to adjust the lattice during the growth process, while cladding layers are needed to control the charge carriers and emitted photon in the desired direction. Electron rich layers are also added above the junction layer in the direction of the p side of the device to act as electron blocking layer to decrease the flow of electrons out of the junction region and increase carrier confinement [4]. Metals are added as contact layers to provide suitable uniform driving current to operate the device. These layers are included in the device design depending on the type and application desired.

Various designs have been developed for solid state light emitters using the concepts presented above with different epi-layers structures to increase light emission, quantum efficiency, output intensity and directionality. Based on its planar wafer-grown structures, semiconductor light emitters fall into two main categories: surface (front/back)-emitters, and edge-emitters.

Surface-emitters are relatively the simpler of the two; they include an active region sandwiched between two opposite doped layers as depicted in figure 1.9. Thick substrate provides mechanical support and often as an n-type conductance, it is also used as a cathode for current injection into the device; suitable metal contacts are deposited on

the n-side substrate or entrenched by etching away epi layers to expose the n-region of the device. The p metal contacts (p-electrodes) are deposited on the top i.e., p-side surface of the device serving as anode [8].

As noted earlier, when the current is injected, the electrons flow in from n-side and "holes" flow in from the p-side and both type charge carries reach in the p-n junction region. Back emitters can have a simple double heterojunction as an active region or it can have single/multi quantum well structures. 2Light is generated in the active region by radiative recombination of excitons (electron-hole) pairs and emitted in all directions. The light output of such devices is collected from the top surface of the device (not covered by metal p contact). Emission pattern of such devices is suitable for general lighting purposes, because of the beam shape and divergence; these parameters can be controlled by some techniques that will be discussed further in this chapter.

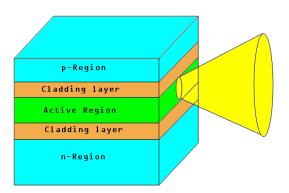

Edge-emitters, on other hand, are relatively complicated in their internal structure because of the need to include additional layers for optical guidance (wave-guiding) and light confinement, these lower index layers along with the higher index active region act as a waveguide in which light is confined and directed to the edge of the device. Light output is collected form the edge of the active region. Light pattern emitted by edge emitters is different from that of surface emitters, the rectangular shape and small dimensions of the active region generate narrow, elliptical, diverging beams of light. The divergence and beam pattern are affected by the active region dimensions. The output of edge emitters has more directionality, thus they are not suitable for solid state lighting (SSL), but they are preferred in optical communications applications. Although this research is more directed toward SSL application, several edge emitters were modeled

and studied because of their important applications. Figure 1.10 shows the basic structure of an edge emitter device [9].

Figure 1.9: Basic structure of top emitter semiconductor light source

Figure 1.10: Basic structure of an edge-emitter semiconductor light source

Optical cavities can be added/embedded in both structures to provide optical feedback and therefore create a laser diode (LD). High refractive index contrast between semiconductor materials and air leads to high reflectivity on the interfaces. Thus laser diode die can be etched to create the optical cavity depending on the high reflectivity at both ends. This concept can be added to edge-emitters as in Fabry-Perot lasers and also to back emitters which create vertical cavity surface-emitting lasers (VCSELs) diodes [10]. The inclusion of multiple quantum wells (MQW) in laser diode structures enables obtaining very narrow band output due to the quantization of the energy levels at MQW region, and selective optical gain due to Fabry-Perot cavity. Additional technologies can also be added to the LD structure for such as Distributed Breagg Reflectors (DBR) or micro lenses and collimators.[11]

# 1.3 Device Packaging, Needs and Considerations

Semiconductor photon sources in both forms LEDs and LDs have great capabilities as electronic to photonic transducers; they also can perform inverse process as photodetectors. Semiconductor light sources are essential in many applications due to their high efficiency, durability, compact size, and high brightness along with low-cost. However, all of these devices are grown as thin layers (from nano and/or micro meter thicknesses) on substrate wafers by large numbers. The epitaxially grown wafers are processed by photolithography, variety of etching techniques and final metallization or contact deposition. On-wafer devices (on substrates) or diced chips are not useful for practical applications, as they are fragile small and very difficult to move or probe. For any practical applications, devices must be separated from the diced wafers and put into a form that will make them ready to be implemented in other systems and applications; this

process is called "Packaging". Packaging is of a great importance because it gives the devices their final shape and size, with input leads for current/voltage supply, output windows for light-emission and sometimes micro optics for beam-shaping. Thus "optoelectronic packaging" determines the possible application of the devices and their modules.

A primary role of "packaging" of LED devices used in SSL is that it provides leads/terminals for voltage supply to the device to ensure suitable and easy current injection into chips by connecting to the power supply; and avoid any cut or shorting of the chip circuitry. This part of packaging have seen a lot of development from the traditional gold wires and contacts to the use of electrically conductive substrate materials, and flip-chip solder bump supported electrodes and ports [12].

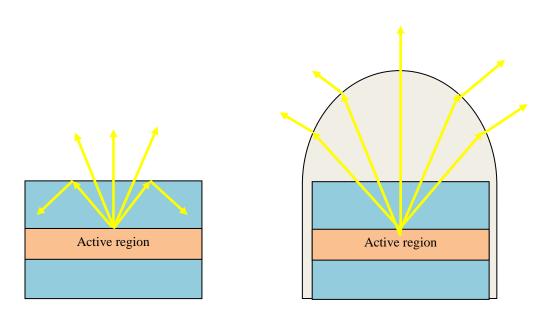

As defined above internal quantum efficiency is the ratio of the photon emitted to the electrons injected into the active region. However, even with good internal quantum efficiency most of the generated light stays trapped inside the device. High index contrast between the semiconductor materials and air not only creates high reflectivity at the interfaces but also results in small critical angles at these interfaces which enhance total internal reflection at these interfaces. This effect is of concern for light emitters because it decreases the light output of the device. Light extraction is one of the most important aspects of the packaging process, considering that most of the commercial LEDs would typically have about 20 % external quantum efficiency.

Light extraction is enhanced by packaging through various methods, the most common most noticeable is encapsulation. Using transparent polymers the device is encapsulated by a dome that engulfs it creating intermediate index value between the chip

material and air, therefore decreases the reflectivity at the interfaces. Due to the lower index contrast between the polymer and air the value of the critical angle at this interface become larger, also the spherical or aspherical shape of the encapsulation decreases the probability of TIR (total internal reflection) to take place. Encapsulation became a standard procedure for LED/LD packaging process. Figure 1.11 shows the effect of encapsulation on light extraction efficiency of a back emitter LED device.

Figure 11: Encapsulation effects on light extraction efficiency for back emitter LED

Efficient light extraction should be always considered in any packaging design all packaging materials must be carefully selected to ensure a stable efficient output from the devices. Many designs and geometries have been introduced to increase light extraction

such as surface roughness and the inverted pyramids, and integrated Fresnel lenses. [13]

Based on the presented information above, it is evident that Packaging is the final stage of the fabrication process. Packaging dictates the final shape of the device and its performance and reliability; all high power LED packages must be designed to meet the following requirements:

- 1. control size of the device

- 2. ease of installation and maintenance

- 3. device protection and ease of handling

- 4. enhance performance and lifetime of the device

- 5. ensure high efficiency light extraction

- 6. ease of integration with electrical and optical components

- 7. Achieve thermal stability and long lifetime for the devices

- 8. low-cost and mass production capability

Like other electronic chips, there are two main methods for LED/LD packaging.

Surface mounted device (SMD) and Flip-Chip mounted devices.

### 1.4 Surface Mounted Devices (SMD)

In SMD packaging, chip package comprises a supporting block with electric circuit patterns and at least one LED/LD attached to the supporting block. Circuit patterns of holes/vias, insulating layers, and conducting traces/pads are formed on and in the supporting block. SMD type LED/LD packages can be further assembled in groups and arrays to form a light modules that allow emitted light to travel in parallel with the mounting surfaces (in case on edge-emitters). The SMD manufacturing process is a

mature production process and thus easy for mass production with relatively low cost. Figure 1.12 shows the diagram of a typical SMD packaged LED. The use of this method is growing nowadays as vertical chip LED and VCSELs become more common. This method is preferred for low current density applications, and has low packaging density in unit area due to metal leads stands for power supply. New device designs such as vertical LEDs and new substrate materials have given SMD the ability of high power operation using conductive substrate. In these cases SMD allows the use of conductive substrate (SiC, Si, metals) which have very useful thermal, structural and economical properties. [14]

Figure 1.12: (SMD) surface mounted device LED

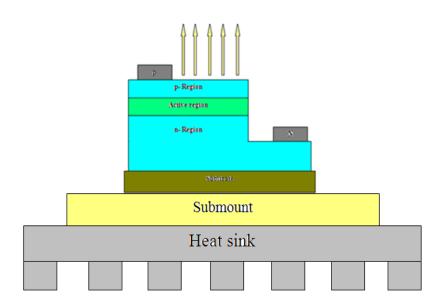

# 1.6 Flip-Chip Devices (FCD)

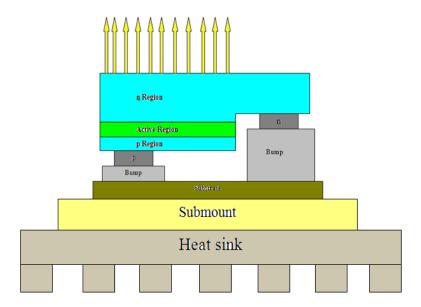

Flip-chip concept is based on the idea of fixing the LED/LD chip upside down on the supporting submount with the probing electrode attached by solder bumps underneath it. The LED/LD chips must have both p and n electrodes on the same side, epi-layers must be etched using various techniques in order to expose/reach the n-side of the chip. Using appropriate thermal interfacial materials (TIM/solders) the chips are connected to the two electrodes properly for forward biasing and current injection. For surface/back emitters most of the light is emitted from the back of the chip through the insulating/transparent substrate, and that makes Flip-Chip a more suitable packaging option for such devices. Probing metallization is patterned on the substrate and bumps (planner or stud types) are deposited at the intended locations of the devices. This method achieves the maximum device density per unit area. Figure 1.13 shows the basic diagrams of Flip-Chip for surface emitting devices. [15]

Figure 1.13: Flip-Chip packaged LED schematic

Intended applications and chip materials dictate the size and method of packaging. Packaging is concerned of many aspects of the device performance and light extraction is one of the top priorities of any package design. Small area, non-transparent metallization pads, and total internal reflection (TIR) results in most of the light produced by the device being trapped within the chip itself. An optimized and suitable package will always ensure low resistance current input with a maximum light output. This is usually done by final encapsulation which is the final stage of packaging to decrease the effects of TIR. Reflecting cups are also considered in some packages to direct the emitted light to a desired direction. Fiber-optic ports and micro lenses are also added in some cases to maximize coupling of the emitted light into an optical system.

Great expansion in the use of semiconductors light sources and the advent of replacing conventional lighting with solid state lighting requires that large number of semiconductors emitters are to be produced and arranged in arrays on industrial levels. This process reveals lot of challenges regarding the efficiency, ease of fabrication, power consumption, and cost of these devices. Packaging development is an essential part to overcome these challenges and ensure efficient, cost-effective, and power-saving light sources for the future.

This research is aimed on the development of numerical and simulations models to design and evaluate efficient and low-cost packaging techniques. This is for the applications in high power LEDs for solid state lighting and with a focus to improve thermal stability and life-time of point light sources and related devices. This study starts at chip scale level, packaging material selection and comparative performance analysis, fully packaged device modeling and simulations. It expands to include heatsinks' design and cost optimization, and thermal analysis of high power LED assemblies and arrays, and finally the use of newly discovered nano-structures in the packaging of high power micro LED arrays. This work will help industry's increasing demands and to ensure more marketable and appealing lighting modules and light engines to consumers worldwide.

## 1.7 Heat Effects on High Power LED Devices

Generated heat in high-power LEDs and subsequent chip-packaging with efficient thermal management are the main focus of this work. Solid state lighting requires high performance, thermally stable low cost devices with improved lifetime, spectral stability, and device durability are needed to ensure good quality SSL modules. Beside the traditional issues of light extraction and internal quantum efficiency, thermal stability is one of the most important concerns when designing packaging of high power LEDs. Typically, low internal quantum efficiency means that the majority of the electron-hole

pairs in the active region will recombine non-radiatively. The non-radiative energy loss and extra energy of the electron-hole pairs beyond the band-edge transitions is released in the lattice as phonons which are quantized vibrations and deposits excess energy in such devices. This process results in increasing the device temperature and decrease of quantum efficiency [16]. In addition to this intrinsic problem, epi-layers growth processes contain high level of defects especially for III-Nitride wide bandgap structures. Defects and micro cracks create discontinuities in the lattice and become electron traps that keep excited electrons localized in the same vicinity, eventually these electrons release their extra energy as phonons thus increase the device temperature. All these effects take place as injected current flow across the epi layers of the device, also various epi-layers of semiconductor have intrinsic resistance which also causes Joule-heating The device heating due to Joule effect, non-radiative energy loss, and internal quantum efficiency loss all add up to overall thermal effects.

Considering that in typical LED devices about 20% of the electric energy is converted to light; it is evident that driving current produces a considerable amount of thermal energy that is dissipated within the LED epi-structure. This phenomenon is more dominant for high power LEDs considering the higher driving current used and more heat deposited in a small volume. Heat generated within LED structures can have serious effects on the device performance. Ultimately, this has negative impact on both the optical output power, color temperatures, color rendering index, color purity and the spectral properties of the emitted light.[17-18]

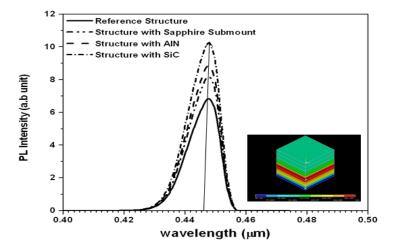

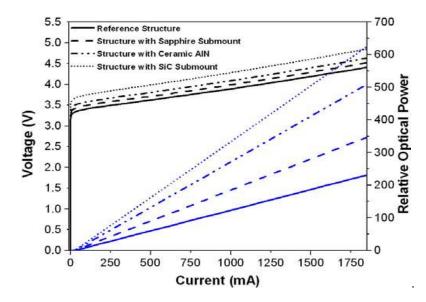

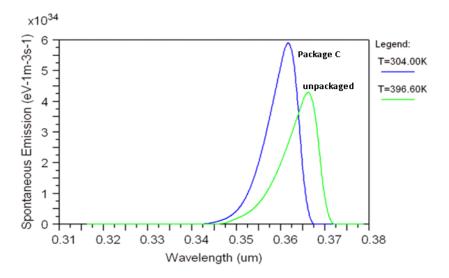

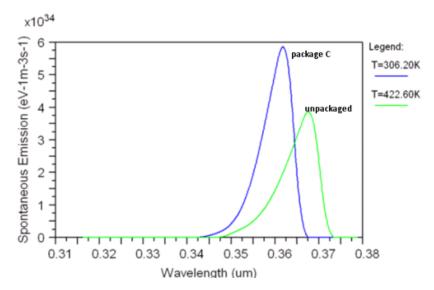

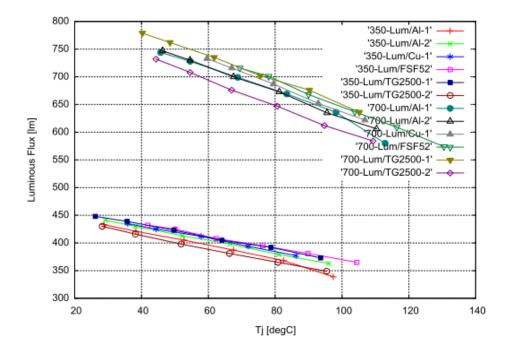

Figure 14 illustrates the drop in the output light intensity for a typical InGaN/GaN LD for different thermal management packages (different chip temperatures), a close

look at figure 1.14 shows the importance of packaging quality for the device performance, and output intensity. High quality materials achieve good thermal management and keep the chip junction temperature at suitable levels so the output is at maxima. Poor selection of packaging materials leads to thermally unstable light sources that suffer self-heating which results in compromised output intensity and poor lifetime. It has been found that a careful selection of the packaging design and thermal interfacial materials play critical role to create thermally managed light sources of high optical power densities with improved lifetimes. [19]

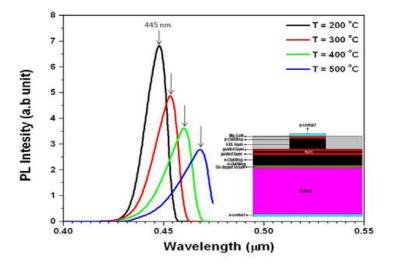

Figure 14: PL spectra of the MQWs InGaN/GaN LD structure after connected to different submounts [19]

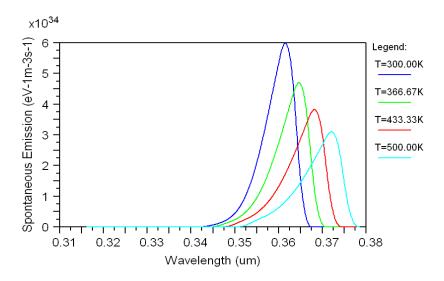

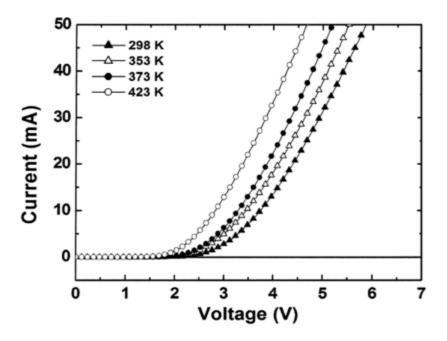

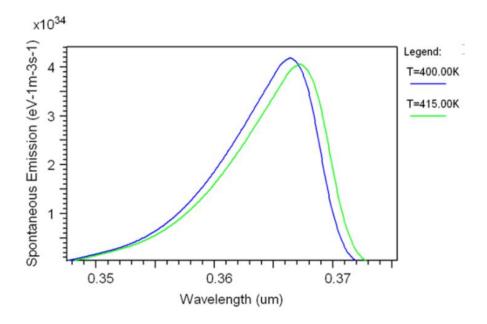

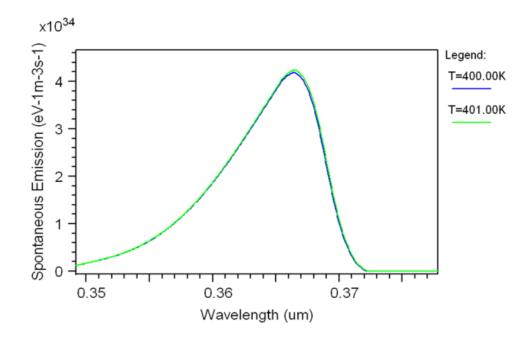

On the other hand, this unwanted heat also affects the energy bands of the semiconductor device narrowing the bandgap which leads to red-shifts in the emitted light, and creates unexpected undesired wavelengths at the output spectrum. This will result in scattering electrons at deeper levels in the valance and conduction bands and gives rise to unexpected energy levels transactions of longer wavelengths [20]. Figure 1.15 shows the PL spectra for AlGaN/GaN LED at different temperatures with a 25 nm red shift and 50% drop in the optical output intensity was observed. Such redshift might be acceptable in some application such as SSL, but it can't be tolerated in other applications such as optical communication and some medical application. The large drop in output is not acceptable for any type of applications, especially SSL where multiple devices are assembled together to create high output.

Figure 1.15: PL spectrum for AlGaN/GaN LED device at different chip temperatures

It has been observed that the decrease in the optical output intensity and red-shift in the emission spectra are the immediate impact of the generated heat within the junction layer of the device structures. Also, this heat also causes serious effects on the overall performance of these light sources. Where some of the stresses such as thermal stress and strain might cause serious degradation effects and ultimately results to a catastrophic failure of such devices [21]

In order to replace conventional incandescent light bulbs with solid state light sources such as high power LEDs, the later have to operate at the same color temperatures and should have equivalent or better color rendering index, color purity and optical power densities. Semiconductor light sources are suitable for SSL due to their compact size and low energy consumption. Phosphors converted white light sources are needed for SSL, however single low power LED based packages may not be able to produce high illumination intensities. The answer to the first problem would be to mix the three basic colors (red, blue and green) by placing three different LEDs that emit these colors on the same chip to create white light. This method is expensive and complicated and does not meet mass production demands. The other method is to use short wavelength devices (blue to UV) to excite a phosphors slab. The short wavelength high energy photons emitted by these LEDs excite phosphors atoms which generate various other colors via photoluminescence. III-Nitride based LEDS/LDs have that desired emission spectrum which makes them essential for any SSL application, thus they were the devices of choice for this work [22].

As mentioned earlier, dissipation of the generated unwanted heat is a priority for any package design. Careful selection of package materials is essential to achieve thermal

stability of light sources. Many packaging techniques have been developed over the years. They vary depending on the devices of interest (edge emitter, back emitter). In brief, thermal management has two types, namely passive and active. Passive thermal management deals with package designs that are designed to extract heat away from the structure and dissipate it to the ambient efficiently; this includes submount materials, thermal interfacial materials selection and heatsink designs. Active thermal management is focused on cooling techniques for photonic devices such as fan attached heatsinks, cooling by air or liquid gel channels. Serious efforts and resources have been dedicated toward the development of wide bandgap semiconductor light emitters to meet the goal of converting these into high power light sources for solid state lighting. More efficient high-power devices are needed, and larger assemblies and arrays of devices are required in order to replace conventional light sources. All of these demands have to be met by low-cost solutions to increase the marketability of these devices and speed up the transition into SSL. The need for cost-efficient and effective thermal management became more imminent. Industry is always on the look for new packaging materials and techniques to answer the expanding needs for high performance durable devices. This study is aimed to develop packaging options for thermal stability that is both costefficient and effective

## 1.8 Summary

In this chapter, we have presented a short introduction and basic principles of semiconductor light sources. Important parameters such as internal and external quantum efficiency were defined. Techniques needed to enhance light output have also been discussed. Quantum confinement through different structural variations has been briefly

explained. Semiconductor light emitters have many applications ranging from general lighting to optical communication and chemical sensing. Different types of devices have been developed over the past decades to fit their intended applications. The two major categories of solid-state light emitters are surface emitters and edge emitters.

The methodology of growing these devices on wafer substrate materials makes the devices very hard to handle or use in any application. Optoelectronic Packaging is the answer for these problems. Well packaged devices can be easily handled, probed and implemented in other systems. Packaging is also responsible for the critical issues linked with the external quantum efficiency and the light extraction, since most of the emitted light in the devices is trapped within their structures. Major packaging trends (SMD and Flip-Chip) methods were presented above along with some common packaging materials. Challenges facing this technology are also considered, total internal reflection, light extraction, encapsulation were all defined and discussed.

The thermal behavior of semiconductor light sources was analyzed; self-heating causes and effects were identified and explained along with the external heat causes due to Joule effect. The impact of device temperature on its performance was illustrated. The drop of output intensity and the red-shift of the emission spectrum were also considered and briefly discussed.

Subsequent chapters describe the work that was carried out following the most recent discoveries in packaging techniques like chip on plate COP packaging in order to improve and evaluate new packaged designs. The newest high potential packaging materials (Carbon nano tubes, Graphene few atomic layers films) are also included and considered in our search for new packaging designs rather than the traditional methods

being tested lately. One of the key contributions of the research is the inclusion of detailed LED structures for the thermal management of photonic devices, contrary to treating the whole device as single bulk material. Because semiconductor materials thermal properties change considerably with doping levels, in most of our modeling and simulation all the layers of these structures are considered with all their different thermal properties extracted from recent literature.

The second chapter of this dissertation includes a brief description of the research especially for the modeling tools and thermal packaging techniques used. Chapters 3 and 4 show our work and results for thermal management of high power LEDs for their wafer bonding, flip-chip bonding, chip on plate type packaging and many more. Chapter 5 presents the thermal analysis of fully packaged devices using new chip-on-plate (COP) technique, along with heatsink designs and related comparative studies. Chapter 6 presents a generalization of the obtained results and their implementation to multiple COP packaged LED assemblies and thermal stability analysis of n×m array. Chapter was concluded with a a new approach of using next generation of higher thermal conductivity smart structures such as Graphene as heat spreader material. Chapter 7 summarizes major findings and comprehensive conclusions.

#### CHAPTER 2: DESIGN TOOLS AND METHOD OF STUDY

The first section of this chapter describes the development and progress of the presented research, from the thermal behavior of on-wafer unpackaged LED/LDs to the complete thermal analysis of fully packaged multiple-chip assemblies. Packaging techniques and novel materials considered in this study are also mentioned.

The later sections present the modeling and simulation modules used for this work. Two well recognized commercial simulation packages such as Rsoft LaserMod<sup>TM</sup> and ANSYS13<sup>TM</sup> were employed for this study. This chapter deals with an overview of the physical and mathematical models used. Along with detailed illustration of used software's capabilities that makes these suitable for presented research.

The final section of this chapter is dedicated to the advanced mathematical modeling used to support the numerical simulation of the design SSL structures and devices and study was concluded with the comparative studies of the designed models. Furthermore, thermal resistance circuit model is explained in details along with all necessary mathematical equations and flow charts.

### 2.1 Research and Development

As summarized in the previous chapter, thermal management of light emitters is an essential technique to develop efficient dependable lighting modules and engines for solid state lighting (SSL). For the last few years, there has been growing industrial demand for better quality yet cost-efficient high power light sources. Lighting modules and engines packages and the related layer by layer high thermal conductivity interfacial

material layers are among the key factors responsible for efficient packages. This work was aimed to design and investigate thermal packaging for SSL through novel high thermal conductivity material designs using mathematical modeling and simulations followed by comparing the calculated results to that of the experimental models available in the literature.

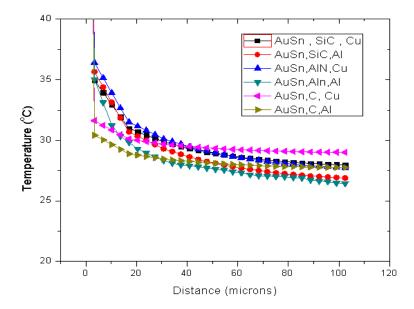

This study deals with some of the critical issues linked with the thermal stability of light sources starting from the basic stages of on-substrate unpackaged chip scale dies to fully packaged arrays and assemblies of high power LEDs. Various light sources which were designed, developed and fabricated in our nanophotonics laboratory were studied, The obtained results were compared to some of the published results for comparison. Using Rsoft design simulator, Light-Current-Voltage (L-I-V) characteristics of the modeled devices were plotted to illustrate ideas about their emission spectra, optical power densities and their illumination intensities. Various die-attach techniques based on solder bumps were considered for comparative thermal analysis along with variety of submount materials. The obtained temperature profiles were used for comparison in order to determine the solder bumps design and the related submount material optimization.

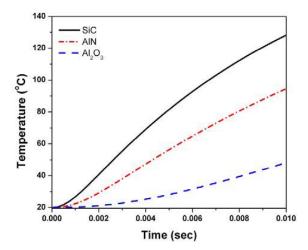

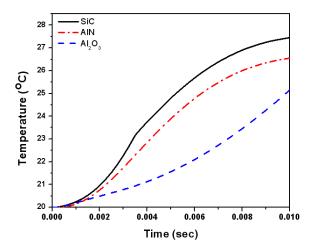

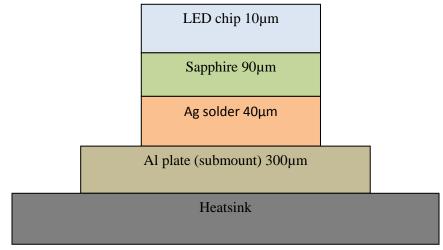

As a next step, the study was extended with the selection of suitable thermal interfacial material (TIM) [34], submount and heatsink materials in modeling. For this, different material groups have been modeled based on their thermal properties in order to achieve best possible material combination for the trial packaging models of AlGaN/GaN LEDs. Consequently, several strategies were modeled and tested through transient thermal analyses. Temperature profiles along top-down and bottom-up

directions within the packages were plotted for comparison. After employing different strategies based on 'best and worst' performing material combinations, thermal resistance circuit concepts were employed to calculate the devices' junction temperatures (for the best and worst performing structure).

At this stage, our research focus was on heat dissipation through conduction. This was mainly because encapsulation and small side areas submounts made negligible heat dissipation through convection. From obtained results, temperature profiles for various structures cross-sections were plotted and compared to ensure results' reliability and consistency.

Group transient thermal analysis of 'thermal interfacial material' (TIM), submount and heatsink were also carried out in order to optimize the best suited materials combination for high thermal stability packaging [23]. In addition to classical thermal interfacial materials, some of the newly developed thermally highly conductive materials were also employed. The most suitable selected material combinations were optimized by considering both performance and cost.

It has been found that "On-Wafer" thermal management has several limitations in terms of device design and geometries which are strictly controlled by the intended usage and the desired wavelengths. Low thermal conductivity of LED die is typically dictated by the type of layer by layer epi-structures and the metallization material used for the fabrication LEDs for the targeted wavelength. Therefore, special care should be involved for the selection of the thermal interfacial material layers of the packages in order to ensure good heat dissipation from the junction/active region to the ambient [24].

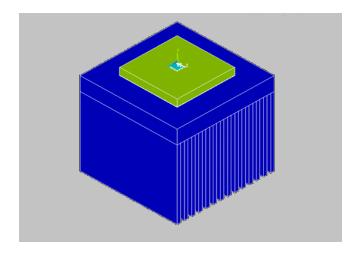

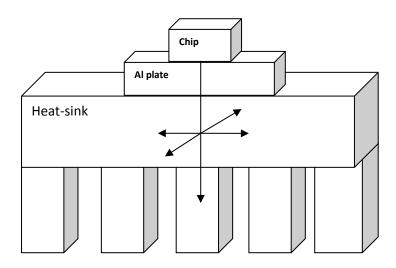

As a next step, the worked carried out as described above was extended for

heatsink design optimization. Briefly, heatsinks are among few critical elements always considered responsible for the dissipating of unwanted heat away from the chip scale die to the ambient through natural forced convection. These are very important components and are specialty designed for packaging. Mainly, our research focus has been towards the design and optimizing of compact yet low cost heatsinks. Excellent performance heatsink always play a critical role for the thermal stability and durability of high power light emitting diodes especially when operated at higher injected current densities.

Quite recently, a new type of packaging technique of Chip-On-Plate (COP) has been introduced for the advanced thermal management of high power lighting emitting diodes [25]. In brief, metallic plates of relatively higher thermal conductivities are used as submounts. These are also important due to their excellent thermal properties and ease of form-factor and readiness of use. Efforts have been to explored and deploy such advanced technique for the modeling and simulation of highly compact light sources. During this study, different high power light sources were analyzed numerically using COP packaging strategy and a comparative study of the junction temperature at different operating power values was performed through steady-state thermal analysis. This is important for the performance evaluation of different COP packages. For this study, mathematical calculations were performed using a TRC model specifically developed for the designed and numerical optimization of these packages [26].

This is noticed worthy that at this stage, the convection was not considered negligible in our modeling. This was mainly because for this technique, heatsink dissipate heat to the ambient. During this study, several heatsink designs such as plate-fins, pin-fins, and staggered pins heatsinks were designed [27-28]. Later these heatsinks were

modeled and simulated using special finite element method to evaluate their performance especially when attached to high power LEDs. Modeling results were corroborated by mathematical TRC calculations, and later these were employed to ensure results consistency. Among few main drivers of this study has been to explore, design and simulate a low cost packaging strategy for high power light sources. It has been found that packaging cost play critical role when it comes to mass production and the marketability of high optical power density lighting sources, modules and light engines. It is often more cost-efficient to choose low-cost heatsinks that ensure temperature of the device remains within the acceptable limits, than to use expensive heatsink that will cool the device much lower than the accepted limits [25].

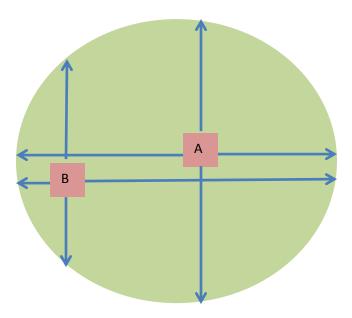

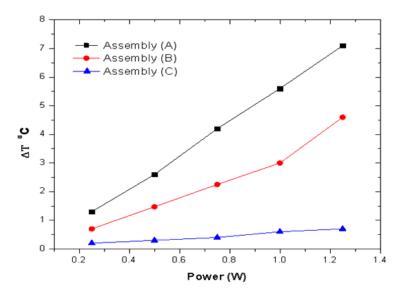

The ultimate goal of this work is to develop a low cost packaging strategy for the thermal management of milli-watt and higher optical power devices for SSL applications. The scope of this work is expanded from a cingulated to that of multi-array of chip scale LEDs for their low cost thermal analysis and packaging. For this, we employed COP packaging technique using cingulated and multi-chip LED assemblies to study the thermal behavior and stability of these lighting modules. Different assemblies were designed for variety of elements (devices) arrangements and types of symmetry. Results showed the thermal effects of neighboring devices upon each other, and these effects were predicted to create chip temperature difference among the assembly elements. The cause of this difference was analyzed qualitatively using TRC model and also heat diffusion equation [29]. Different arrangements to suppress the unequal temperature effect among elements were modeled and simulated at different power levels. This is worth noticed that the obtained results were in good agreement with the theoretical

expectations and symmetrical behavior of each element. As described earlier, unwanted heat removal is very important for a successful thermal package. For this, newly developed packaging strategy of Carbon nano-tubes based nano and micro structures have gained tremendous interest due to their exceptional electrical and thermal properties [30]. The experimental success in using few layer Graphene (FLG) as heat-spreading sheets for GaN field effect transistors (FET)s, has encouraged us to extend the same idea for the packaging of high power LEDs and LDs for SSL applications. A proof of concept structure was designed based on COP package, although the device and FLG sheets dimensions were too large, a small drop in the device temperature was noticed. heatspreading sheet concept was then introduced to micro-LED arrays to overcome the size limitations and enhance the effect of FLG heat spreaders. The small size of such devices made these m comparable to the available Graphene sheets (about 10µ long), and gave place to much higher device temperature reduction. This work is noteworthy and we hope it is a promising start using Graphene heat spreaders for the packaging of photonic devices.

## 2.2 Modeling and Simulation Tools

This research is centered on simulations, and theoretical models and calculations. Two well recognized simulation softwares were employed in this study. Device design and simulations were carried out using RSoft's LaserMod<sup>TM</sup>. 3D packaging modeling and steady-state/transient thermal analyses were carried out using ANSYS13<sup>TM</sup>. Both softwares are primarily finite element FEM analyzers. LaserMod is a 1D/2D photonic devices design software for simulating optical, electronic and thermal properties semiconductor lasers and light emitting diodes and photonic structures. It allows the

design and simulations of variety of photonic devices such as LED, LD, VCSELs, and solar cells. Simulations of various packaging structures are based on Minilase-II program [31], developed at the University of Illinois, at Urbana-Champaign. The graphical user interface (GUI) features enable the users to control every layer within the photonic device's structures and optimize doping levels, bias and dimensions. The software solves the carrier transport, and carrier-photon interactions, using a fully coupled numerical model based on finite element method depending on the device geometry CAD design.

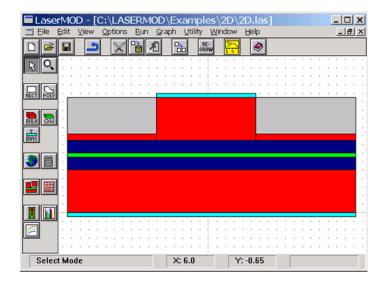

This tool is capable of simulating 1D cross-section, suitable for broad-area lasers analysis, also more complicated structure with higher mode confinement requires a 2D simulation of laser cross-sections. This is necessary when considering the effects of carrier spreading and optical confinement by the changing geometry of ridge waveguide structures. Various available features and capabilities of LaserMod make it suitable for Fabry-Perot edge emitters as well as basic LED devices and also other active photonics such as solar cells. Figure 2.1shows the sample GUI of Rsoft and LaserMod used in this study.

Figure 2.1: LaserMod GUI for CAD design of a 2D LD device.

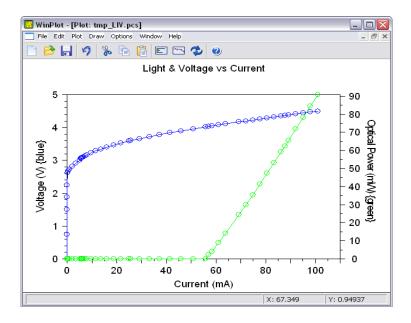

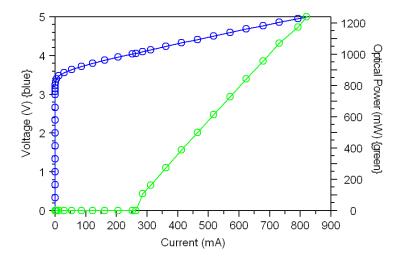

LaserMod can provide steady-state analysis, for CW performance evaluation, in addition to transient analysis capabilities, for pulsed/modulated emission of devices. Various device performance plots, such as index / bandgap profiles, emission spectra, optical gain, and mode confinement can also be created. PL spectrum and optical gain can be simulated depending on carrier concentration and temperature which give the ability to observe and measure the effects of increasing temperature on the device's output. The software offers large material library to choose from with desired characteristics and combinations. Emission spectrum and modes pattern can be observed along with L-I-V characteristics. Figure 2.2 illustrates the L-I-V plots for a Fabry-Perot III-Nitride based LD.

Figure 2.2: LaserMod L-I-V characteristics of a LD device.

Considering that the main focus of this dissertation is thermal management of photonic devices. Thermal analysis of such structures was our workhorse. In this research we carried out two types of thermal analysis, namely steady-state and transient. Steady-state thermal analysis is used to study the thermal behavior of systems when they reach thermal equilibrium and all thermal conditions in and around the structures become constant (steady-state) this type of thermal analysis was used in this research mainly to evaluate the thermal performance of complete packaged devices ie full LED package. On the other hand transient thermal analysis is used to study thermal behavior of systems at different points in time before reaching equilibrium where thermal boundary conditions are subject to changing overt time (transient), this type of thermal analysis was mainly used in comparative study among similar packaged designs that have different packaging

materials to clearly show thermal responses of different packaging material combinations. Thermal analysis of photonic devices was carried out using ANSYS<sup>TM</sup>,13 engineering simulation program, which is finite element method based software [32]. ANSYS has excellent thermal analysis capabilities for both steady state and transient thermal behavior. Interface allows building 2D/3D models of the devices of interest to the appropriate scales. Any materials and their combinations could be modeled in the program based on its specific thermal and mechanical properties such as thermal conductivity, specific heat, and density. Specialty materials can also be modeled since ANSYS has the ability to include materials with anisotropic thermal and properties.

Once the model is built, thermal loads such as convection, heat generation, and initial temperature can be applied to desired volumes, areas, or even points of the structure. Convection is applied on the outer surfaces of the structure by inserting the suitable value for its coefficient; heat generation can be introduced for both areas and volumes depending on the type of the analysis (2D/3D). ANSYS heat generation function is related to the power dissipated in unit volume regardless of the source (electrical, chemical etc...).

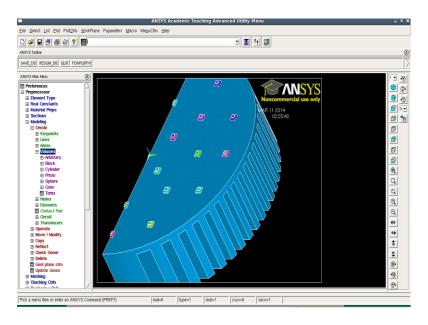

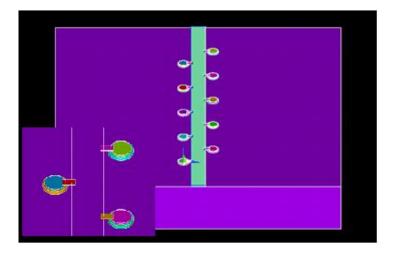

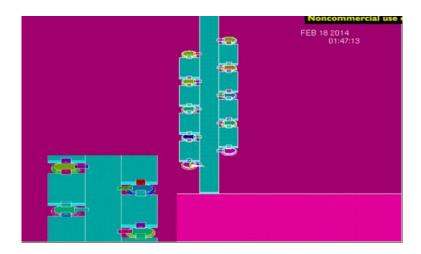

Since ANSYS is a finite element analyzer, meshing is a very important step of any thermal analysis size and number of the elements has to be accounted for because each ANSYS can deal with limited number of elements at a time. Efficient selection of element sizes and mesh fineness at different location in the structure is essential to create the most realistic results [33]. ANSYS GUI is shown in figure 2.3 below as an example.

Figure 2.3: ANSYS13 GUI showing the design of 3D model of the package of multiple LED chips for SSL

ANSYS simulations are based on the first law of thermodynamics, which states that thermal energy is conserved. This law can be expressed as a differential equation of the form [34-35]:

$$\rho.\,C.\left(\frac{dT}{dt} + \vec{V}.\,\vec{\nabla}.\,T\right) + \vec{\nabla}.\,T.\,\vec{q} = \,\vec{q} \qquad \qquad 2.1$$

Where:  $\rho$  is density, C is specific heat, T(x,y,z) is temperature, t is time,  $\vec{V}$  is velocity vector of mass transport of heat,  $\vec{q}$  is thermal flux vector, and  $\ddot{q}$  is heat generation rate per unit volume.

Using Fourier law heat generation is related with thermal gradient and it can be expressed as:

$$\vec{q} = -[D]\vec{\nabla}.T$$

2.2

Where [D] is the thermal conductivity matrix and it is given as:

$$[D] = \begin{bmatrix} Kx & 0 & 0 \\ 0 & Ky & 0 \\ 0 & 0 & Kz \end{bmatrix}$$

2.3

$K_x$ ,  $K_y$ ,  $K_z$  are thermal conductivity values for the material of interest. Combining equations 11 and 12 results in equation 13:

$$\rho. C. \left(\frac{dT}{dt} + \vec{V}. \vec{\nabla}. T\right) = -[D] \vec{\nabla}. T + \ddot{q}$$

2.4

Expanding equation 13 to more familiar form we get

$$\rho. C. \left( \frac{dT}{dt} + Vx \frac{dT}{dx} + Vy \frac{dT}{dy} + Vz \frac{dT}{dz} \right) =$$

$$\ddot{q}$$

+  $\frac{d}{dx} \left( Kx \frac{dT}{dx} \right) + \frac{d}{dy} \left( Ky \frac{dT}{dy} \right) + \frac{d}{dz} \left( Kz \frac{dT}{dz} \right)$  2.5

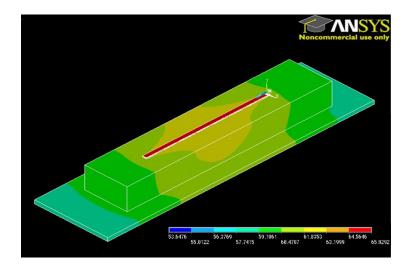

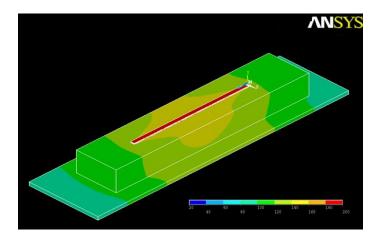

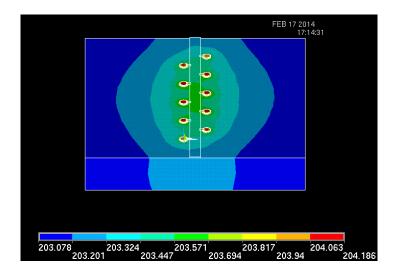

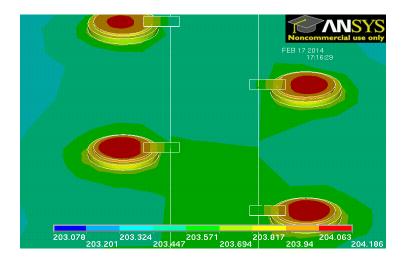

ANSYS uses finite element method (FEM) to solve the differential equations for obtaining the temperature at any time and any point of the structure after providing all loads and boundary conditions. Temperature distribution can be viewed at any point or anytime across the structure nodes localized temperature values can be obtained and

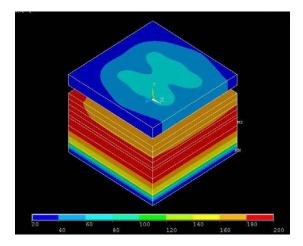

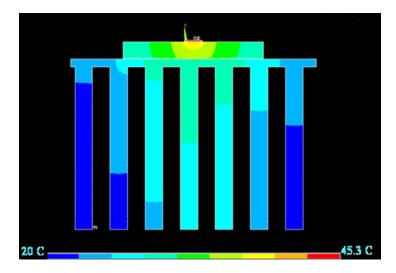

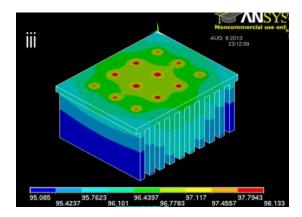

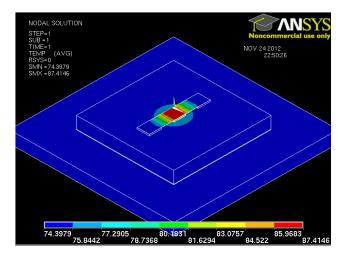

listed for every element of the model package and devices. Figure 2.4 shows temperature distribution in the package of high power LD device at the end of transient thermal analysis.

Figure 2.4: Temperature distribution in a packaged Laser Diode GaN/AlGaN Laser Diode.

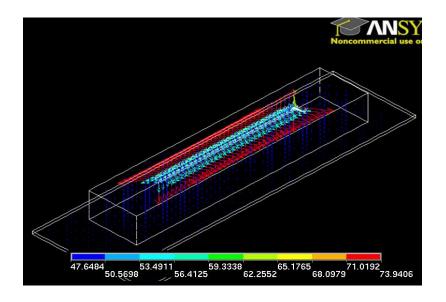

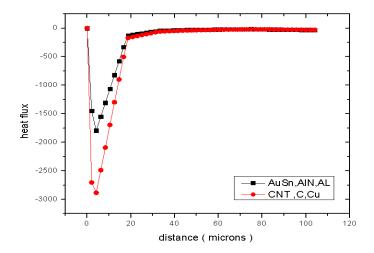

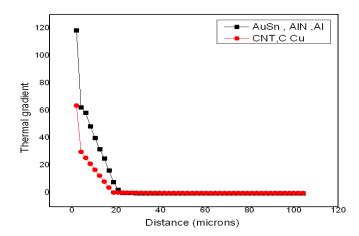

Other thermal parameters such as thermal flux and thermal gradient can also be measured and plotted in a vector or contour plots of the 3D structure which is very helpful to understand the thermal behavior of the packages and view thermal paths within the structures. Path operations allow the users to define paths of several points throughout the structure and map any thermal parameter onto it in order to create parametric profiles. Animations of the results over time capabilities are also available to clearly show the

thermal behavior of the modelled packages. Figure 2.5 shows an example 3D vector plot of heat flux inside a fully packaged LED device. All features mentioned above made ANSYS-13 the tool of choice for all thermal analysis conducted in this research.

Figure 2.5: 3D vector plot of heat flux in a fully packaged LED chip mounted on heatsink.

## 2.3 Mathematical Model

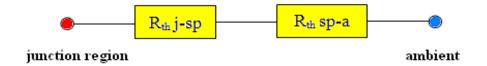

Theoretical calculations are always considered very important for thermal mangement of chip-scale devices; mathematical models were used to calculate some critical simulation parameters such as convection coefficients, heat generation functions, and junction temperature. Thermal resistence circuit (TRC) [26] is a mathematical model based on the analogy between thermal and electrical circuits. This model was modefied,

adapted, and employed in this study for calculating device junction temperatures. Thermal cuircuits are representation of device and packaging structures. Each different package would be represented by certain TRC diagram depending on its size, design and thermal path within the package.

Thermal resistance circuits used in our work contain only one component, which is thermal resistances. By definition theraml resistance is a thermal property of materials that represents the measurement of a temperature difference by which an object or material resist heat flow (heat per time unit or thermal resistance). Thermal resistance is highly size dependent. Each package and device layer contributes an independent thermal resistance to the total thermal resistance circuit.

Temperature difference between any two points is treated as potential difference; heat flow is the equivalent of electric current. In this sense calculating the temperature will be based on the simple Ohm's law for a given power value as:

$$P = \frac{\Delta T}{R_{th}}$$

2.6

Where P is the thermal flux (based on power dissipated) analogous to electric current "I",  $\Delta T$  is the temperature difference between two points (just like potential difference), and  $R_{th}$  is the total thermal resistance between the two points. Knowing the power dissipated in the device packages and careful calculations of the total thermal resistance of the packages allows determining the device temperature considering that first point of interest is located within the active region and the second point is at the ambient.

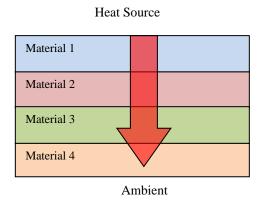

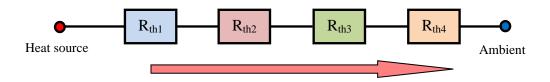

Thermal resistances are treated as 'Ohmic resistances' in electric circuits; those can be connected in series or in parallel. Finding the total resistance similar rules apply as those in electrical circuits. It is important to identify and figure out when thermal resistances are in series or parallel. This is done based on tracing thermal paths in the structure, e.g., when there is only one thermal path through which heat flows/progresses in the structure, all thermal resistances of the material layers are considered to be in series as shown in figures 2.6 and 2.7, respectively.

Figure 2.6: Thermal path in four-section stack of material layers

Figure 2.7: Series TRC diagram for one heat path through four-section stack of material layers

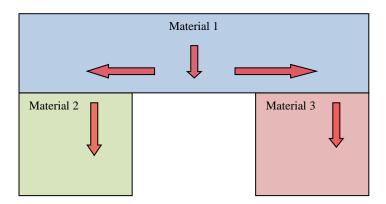

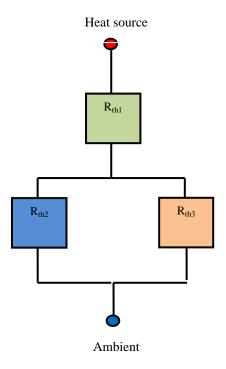

For more complicated thermal paths, thermal resistances can be found in parallel and series combinations. This often happens when thermal path branches out based on the structure or due to different material layers. In other words, when there are multiple thermal paths within the structure of interest, then thermal resistances can be modelled as combination of parallel and series. Figures 2.8 and 2.9 show an example of branching thermal paths and the thermal resistance circuit that represents it.

Figure 2.8: multiple thermal paths in gate-like arrangement of material layers

Figure 2.9: Parallel TRC diagram multiple heat path through bridge-like arrangement material layers

Thermal path definition is the first and most important step in TRC analysis approach. Once TRC diagrams are finalized, thermal resistances have to be evaluated in order to obtain the total thermal resistance of the structure.

Heat transfer occurs via three methods; conduction, convection, and radiation. Conduction takes place at the interfaces between solid objects thus in the case of solid-state light emitters it is the major method for heat transfer. Heat spreads from the active region to the other parts of the device mainly through conduction. However, thermal stability is achieved when the device temperature is relatively constant at a fixed operating power which requires a thermal equilibrium. Considering limited size of the

packaged device, it can be realized that heat is dissipated to the surrounding ambient to maintain that equilibrium. Heat transfer between solids and gases/fluids is achieved through convection. It this study, conduction and convection were only considered. Radiative heat transfer was not included in the analysis due to the small dimensions of the light emitting device surfaces; and thereby its small impact on the thermal behavior of the device.

As TRC diagram is defined, it is important to determine the nature of each thermal resistance. Conductive thermal resistances represent any thermal path within one material layer (solid material) such resistance values are calculated using the following equation:

$$R_{conductive} = \frac{L}{K \times A}$$

2.7

Where L is the length of the thermal path inside the material, K is the material thermal conductivity, and A the surface area perpendicular to the thermal path

'Convective thermal resistances' are located at every material/ambient interface.

This includes the main thermal path, and the secondary paths branching out from it.

Convective thermal resistances are calculated using the following equation:

$$R_{convective} = \frac{1}{h \times A}$$

2.8

Where h is the convection coefficient for material ambient interface.

After, all thermal resistance of the TRC are calculated, total thermal resistance is obtained using the basic rules of electrical resistors. When both ambient temperature and the dissipated power are known junction temperature can be easily found using Eq. 2.6

Each of the device packages are analyzed based on thier geometry and all thermal paths are considred taking into account conductive and convective thermal resistences. Chip temperatures are then calculated based on the power injected and the ambient temperature. In order to use this model effectivly many parameters have to be accounted for and thereby calculated. Convection coefficients, thermal resistances, and heatsink thermal resistance must be calculated for each fo the packaging design. Other theoretical concpts such as thermal mass and thermal diffusion are also employed to understand and justify the simulation results.

Theoretical results were put into comparison with the simulation data and the model proved to give staisfactory results. each different strucutre will be represented different thermal circuit which requier different calculations and thermal paths to be taken to consideration. This model was proved to give consistenent results with an acceptable error values.

## 2.4 Summary

In this chapter an overview of the research is presented, the methodolgy and aproach to the problem of self-heaing in semiconductor based lighgt sources were illustrated in a progressive manners from on-wafer unpackaged devices to fully packaged arrays. Conventional and new packaging techniques considered in this stduy were presented. Common and novel packaging materials included in this research were also

presented along with the modifications needed to include them effciently in the packaging process.

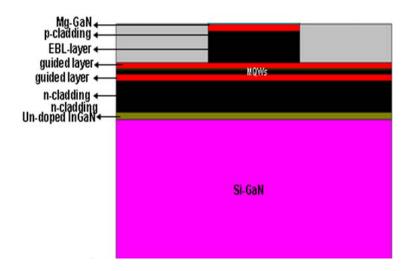

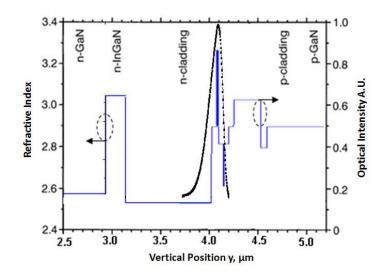

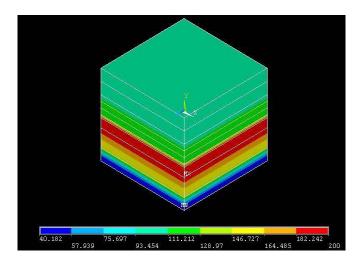

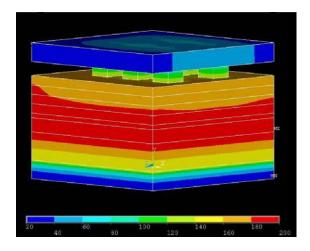

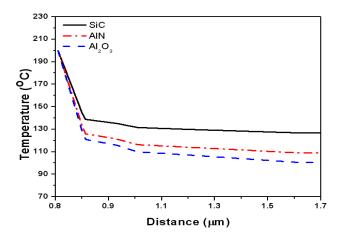

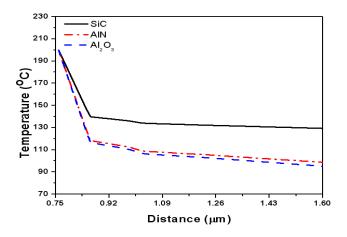

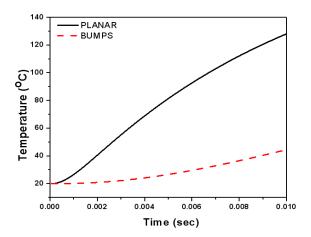

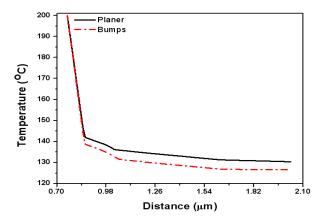

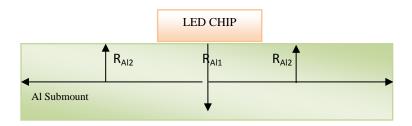

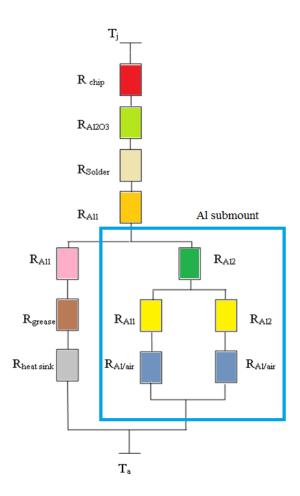

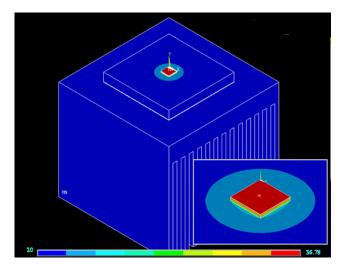

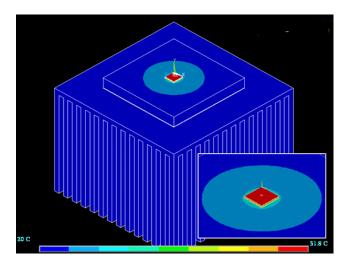

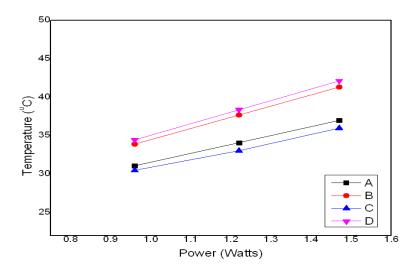

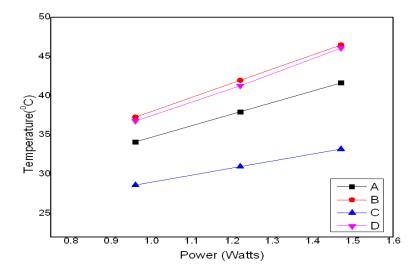

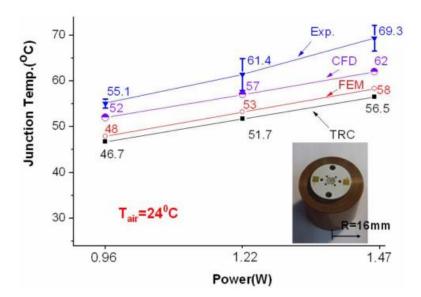

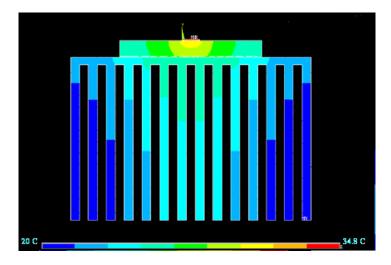

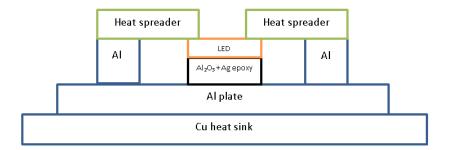

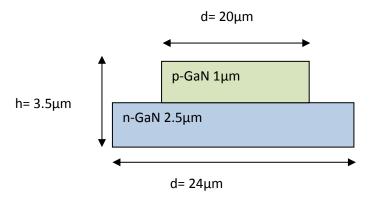

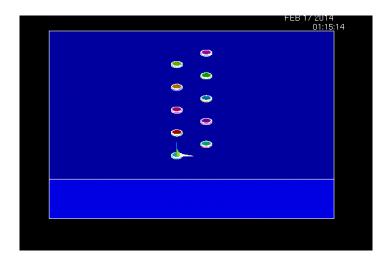

Simulation softwares employed in this research were presented, along with their mathematical base and useful capabilities that made them the workhorse for this study. Mathematical foundation of thermal resistance circuit model used in the study was presented along with the needed formulas and equations.