# POLYDYNE DISPLACEMENT INTERFEROMETER USING FREQUENCY-MODULATED LIGHT

by

## Masoud Arablu

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Mechanical Engineering

Charlotte

2019

| Approved by:              |

|---------------------------|

| Dr. Stuart T. Smith       |

|                           |

| Dr. Jimmie Miller         |

| De Ladas Tadastas         |

| Dr. Joshua Tarbutton      |

| Dr. Konstantinos Falaggis |

| Dr. Konstantinos raraggis |

| Dr. Tsinghua Her          |

| Dr. Tsinghua Her          |

©2019 Masoud Arablu ALL RIGHTS RESERVED

#### **ABSTRACT**

MASOUD ARABLU. Polydyne displacement interferometer using frequency-modulated light (Under the direction of DR. STUART T. SMITH)

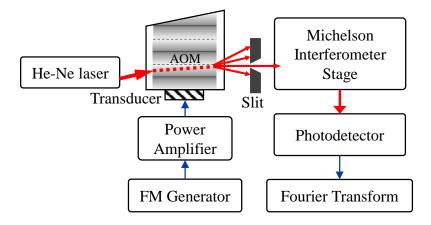

A novel multi-frequency (polydyne) optical interferometry method is introduced and a prototype developed to evaluate its performance in a Michelson displacement interferometer configuration. The polydyne interferometer contains three main parts of 1) synchronous Radio-Frequency Frequency-Modulated (RF-FM) electrical signal generation, 2) electrical-to-optical signal patching by an Acousto-Optic Modulator (AOM), and 3) signal detection and processing unit. Each of these three parts are discussed briefly in a separate chapter as well as the basic concept of phase extraction from the interference of FM light beams.

A novel synchronous RF-FM signal generation method is introduced that uses an atomic clock for timing all frequency components of the signal. The RF-FM signal generator uses a modulated, voltage-controlled time delay to correspondingly modulate the phase of a 10 MHz sinusoidal reference from the atomic clock. This modulated reference signal is, in turn, used to clock a Direct Digital Synthesizer (DDS) circuit resulting in an FM signal at its output. The modulating signal that is input to the voltage-controlled time delay circuit is generated by another DDS that is synchronously clocked by the same 10 MHz sine wave signal before modulation. Therefore, all the digital components are timed from a single sinewave oscillator that forms the basis of all timing.

The resultant output electrical signal comprises a center, or carrier, frequency plus a series of phase-synchronized sidebands having exact integer harmonic frequency separation.

The RF-FM electric signal is transferred into a He-Ne laser beam by diffraction of the beam through an Acousto-Optic Modulator (AOM). The first diffraction side-beam emerging from the AOM is selected by a slit to be used in a Michelson interferometer topology. Frequency spectra of the interfered FM light beams contains the harmonics of modulation frequency. The displacement measurement is derived from the phase measurement of selected modulation harmonic pairs. Individual modulation harmonic amplitudes are measured using Fourier transform applied to the signal from a single photodetector. Lock-in amplifiers were first used to perform Fourier transform on the detected signal. Displacement of the moving target was measured by harmonic pairs chosen from harmonics 1 to 5 of the modulation signal.

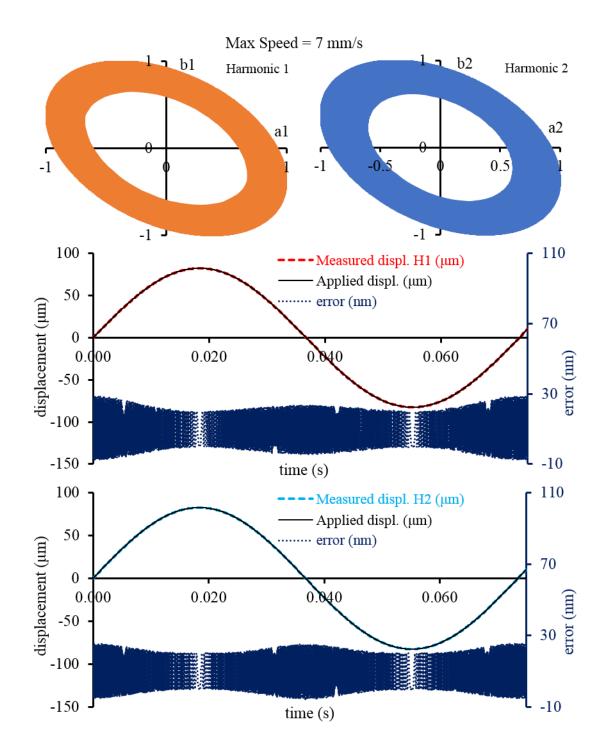

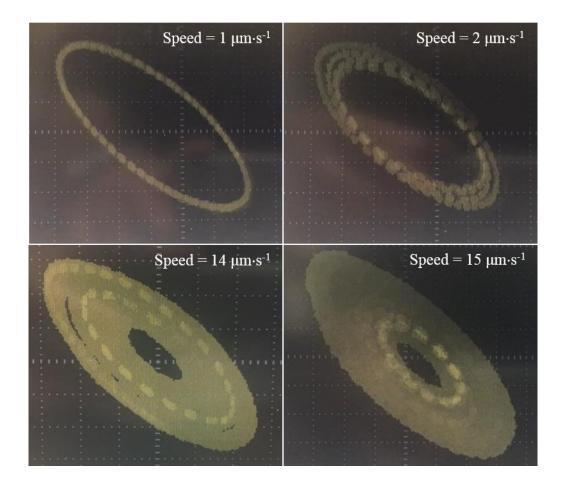

Since the analog Lock-In amplifiers use low-pass filters to detect the signal of interest, they limit the bandwidth of measurement to one-tenth of measured signal frequency. This limit reduces the speed of measurement to a few  $\mu m \cdot s^{-1}$  in our system. Therefore, after validating the feasibility of displacement measurement using the changes in the amplitudes of harmonic pairs detected by Lock-in amplifiers, a Discrete Fourier Transform (DFT) algorithm was developed on a Field Programmable Gate Array (FPGA) microchip to increase the bandwidth and speed of measurement as well as to miniaturize

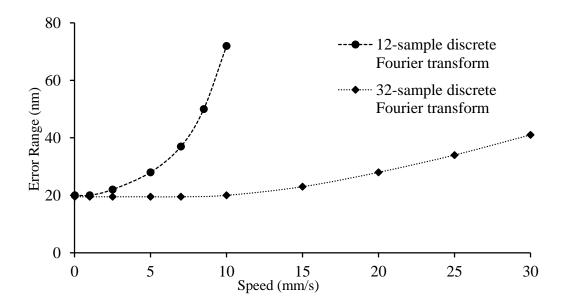

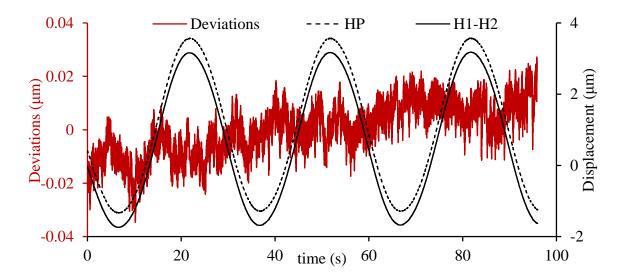

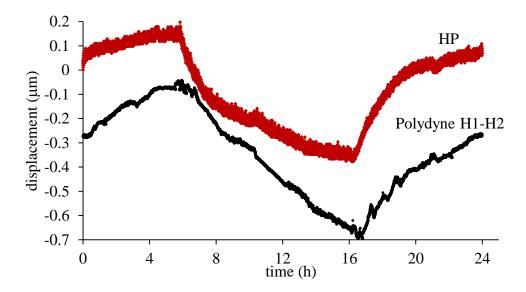

the signal processing unit. The timing of the FPGA microchip was developed from a Phase Locked Loop (PLL) synchronous to the same 10 MHz sine wave from the atomic clock that is timing all the frequency components of the RF-FM signal. This synchronizes all the timings in the signal generation and detection units. The developed synchronous DFT provides measurements with speeds up to 10 mm·s<sup>-1</sup>, a limit that can be always improved using larger FPGA microchips and faster analog-to-digital convertors on the photodetector output. In the developed synchronous DFT algorithm, displacement-related-phase-change is derived from the amplitudes of harmonics 1 and 2 of the modulation signal. The measured displacements are compared with a commercial heterodyne interferometer being used as a reference for these studies. Displacements of the moving mirror of the interferometer over ranges up to 10 µm with speeds up to 10 mm·s<sup>-1</sup> all show differences of less than 50 nm between the polydyne interferometer and the reference interferometer measurements. A drift test is also used to evaluate long-term stability and repeatability of measurements with the developed polydyne interferometer.

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank my professor Dr. Stuart T. Smith. It has been a great honor to be his student. His idiosyncratic approach toward his research was contagious and motivational for me, even during tough times in my Ph.D. pursuit. Not only he educated me in different subjects of mechatronics, but also reshaped my personality to be eternally passionate to learn new technologies. I appreciate all his contributions of time, ideas, and funding to make my Ph.D. experience productive.

I gratefully acknowledge the funding sources that made my Ph.D. work possible. I was funded by the Graduate Assistantship Program for all my five years of education at UNC Charlotte and was honored to conduct a fruitful research at the Center for Precision Metrology (CPM) that funded my project for about three years. The professors of the CPM have contributed immensely to my personal and professional time at UNC Charlotte. The center has been a source of friendships as well as good advice and collaboration. I am especially grateful to Dr. Jimmie Miller who helped me with his laboratory facilities as well as his insightful comments especially on the drift test setup and results that were very crucial for evaluating long-term stability of the instrument developed in my thesis. Thanks to Jennifer Chastain for her extensive helps to procure the required material used in my setup. I would like to acknowledge Dr. Christopher Evans who has supported my project as the head of the center. I would like to thank Mr. John Brien for his valuable advice during the development of the frequency-modulator

circuit. I also thank Dr. Thomas Weldon from electrical engineering department at UNC Charlotte, for use of his laboratory facilities to test my electronic boards. For this dissertation I would like to thank my reading committee members: Dr. Falaggis, Dr. Her, Dr. Miller, Dr. Smith, and Dr. Tarbutton for their time, interest, and helpful comments.

My time at UNC Charlotte was enjoyable especially due to many friends who have become a part of my life. I am grateful for time spent with friends, for our memorable trips to the mountains, for Farid Javidpour, Amirreza Sahami, Faraz Hedayati, Vahid Hemmati, Saeed Heysiattalab, Fatemeh Mirzaee's hospitality. Many thanks to my great lab-mates, Jeffery Thousand, Kumar Arumugam, and Sajad Kafashi who helped me in programming a lot of codes. I would like to thank Pedram Poshtiban from IUST for teaching me the VHDL language for programming FPGAs.

Last but not least, I am grateful to my family for all their love and encouragement. For my parents who raised me with a love of science and supported me in all my pursuits. Special thanks to my dad for assigning me tough tasks as a kid to prepare me for the rainy days of my life. For my beloved mom who has truly devoted herself to our family. For my elder brothers Yousef and Naser who shed a light into the path that I took as an engineer as well as my lovely sister, Nahid, who has always supported me as her little brother. Thank you all.

Masoud Arablu UNC Charlotte May 2019

# TABLE OF CONTENTS

| CHAPTER 1 INTRODUCTION                                 | 1  |

|--------------------------------------------------------|----|

| 1.1 Literature Review                                  | 1  |

| 1.2 Objectives of this research                        | 7  |

| CHAPTER 2 INTERFERENCE OF FM LIGHT BEAMS               | 9  |

| CHAPTER 3 SYNCHRONOUS FM SIGNAL GENERATION             | 14 |

| 3.1 Digital FM signal generation background            | 14 |

| 3.2 Principle of operation                             | 18 |

| 3.2.1 Modulated clocking of the high bandwidth DDS     | 18 |

| 3.2.2 Theory of Synchronous FM Signal Generation       | 21 |

| 3.3 Modulator Circuit Design                           | 23 |

| 3.4 FM signal generator testing and results            | 27 |

| 3.4.1 Experimental apparatus and test procedure        | 27 |

| 3.4.2 Performance tests on first prototype of FM board | 29 |

| 3.4.3 Final prototype FM board                         | 32 |

| CHAPTER 4 FM LIGHT GENERATION BY AOM                   | 44 |

| 4.1 Acousto-Optic Modulators                              | 44  |

|-----------------------------------------------------------|-----|

| 4.2 Diffraction of Light by FM Waves using an AOM         | 46  |

| 4.3 Experimental Results of Diffraction                   | 51  |

| CHAPTER 5 SIGNAL DETECTION                                | 58  |

| 5.1 Photodetector Design                                  | 58  |

| 5.1.1 First photodetector                                 | 61  |

| 5.1.2 Second photodetector                                | 63  |

| 5.2 Harmonics detection by analog lock-in amplifiers      | 65  |

| 5.3 Harmonics detection by FPGA-based Fourier transform   | 67  |

| CHAPTER 6 DISPLACEMENT MEASUREMENT                        | 84  |

| 6.1 Measurements by analog lock-in amplifiers             | 84  |

| 6.2 Measurements by FPGA-based discrete Fourier transform | 93  |

| 6.3 Synchronization issues                                | 97  |

| 6.4 Future work                                           | 100 |

| REFERENCES                                                | 103 |

| APPENDIX A ARDUINO CODE FOR FM BOARD                      | 112 |

| Appendix A.1 FMGenerate_Arduino                           | 112 |

| Appendix A.2 keywords                                | 114 |

|------------------------------------------------------|-----|

| Appendix A.3 FM_Generate.h                           | 114 |

| Appendix A.4 FM_Generate.CPP                         | 115 |

| APPENDIX B SPECTRA OF ELECTRICAL FM SIGNALS          | 122 |

| APPENDIX C VHDL code for 32-sample Fourier transform | 130 |

# LIST OF TABLES

| Table 3-1- Measured phase differences between sidebands.          | 39 |

|-------------------------------------------------------------------|----|

| Table 3-2- Simulation of AD9951 DDS with PLL multiplier of 20 and | 42 |

| AD9833 DDS with clock frequency of 10 MHz                         |    |

| Table 6-1- RMS of deviations between reference interferometer and | 89 |

| harmonics pairs measurements.                                     |    |

| Table 6-2- Span and RMS of deviations between HP and polydyne     | 97 |

| interferometers measurements.                                     |    |

# LIST OF FIGURES

| Figure 1-1- Schematic of a simple displacement measuring interferometer.               | 2  |

|----------------------------------------------------------------------------------------|----|

| Figure 1-2- Typical detection bandwidth of homodyne and heterodyne                     |    |

| interferometers.                                                                       | 5  |

| Figure 2-1- Absolute value of Bessel functions of first kind, $J_i(\beta)$ , for $i =$ |    |

| 0, 1,, 8 in a normalized scale.                                                        | 12 |

| Figure 3-1- Frequency spectrum of DDS output with a 469.360351 MHz                     |    |

| output showing a 38 dBc Nyquist band spurious-free dynamic range [59].                 | 16 |

| Figure 3-2- Digital Phase Wheel with corresponding normal and modulated                |    |

| clock.                                                                                 | 19 |

| Figure 3-3- Block diagram of the circuit containing the signal path from               |    |

| reference clock to the DDS2.                                                           | 20 |

| Figure 3-4- Details of the phase delay circuit in conjunction with major               |    |

| blocks of other DDS1 and DDS2 circuits.                                                | 23 |

| Figure 3-5- Schematic of the DDS1 circuit with a digital amplitude control.            | 24 |

| Figure 3-6- Schematic of the DDS2 circuit.                                             | 26 |

| Figure 3-7 Variation of the generated delay from the LT1016 comparator as     |    |

|-------------------------------------------------------------------------------|----|

| a function of the voltage applied to the LF353 amplifier.                     | 27 |

| Figure 3-8- Frequency response of the DDS1 circuit over a 2 MHz band.         | 28 |

| Figure 3-9- Frequency response of the DDS2 circuit from 1 to 80 MHz.          | 28 |

| Figure 3-10- First prototype of the FM board.                                 | 29 |

| Figure 3-11- Experimental setup to test the first prototype FM signal         |    |

| generator performance.                                                        | 30 |

| Figure 3-12- Frequency spectrum of FM signal of $f_c = 60$ MHz and            |    |

| $f_m = 100$ kHz generated by the first prototype board.                       | 31 |

| Figure 3-13- Frequency spectrum of FM signal of $f_c = 60$ MHz and            |    |

| $f_m = 250$ kHz generated by the first prototype board.                       | 31 |

| Figure 3-14- Photograph of the final prototype PCB with different sub-        |    |

| circuits components; A) power input and regulators, B) digital input, C)      |    |

| clock input, D) omitted clock-line buffer layout, E) time-delay, F) high-pass |    |

| filter, G) DDS1 circuit, H) digital rheostat to control modulation signal     |    |

| amplitude, I) modulation signal output, J) DDS2, K) transformer, L) low-      |    |

| pass filter with 160 MHz cutoff, M) low-pass filter with 75 MHz cutoff, N)    |    |

| FM output.                                                                    | 33 |

| Figure 3-15- The FM board with separated buffers in the clock line; a) non-                |    |

|--------------------------------------------------------------------------------------------|----|

| inverting adjustable gain amplifier; b) buffer between DDS1 and clock line.                | 34 |

| Figure 3-16- Experimental setup to test the final prototype FM signal                      |    |

| generator performance.                                                                     | 35 |

| Figure 3-17- Measured frequency spectra of signals of $f_c = 30$ MHz and                   |    |

| $f_{\rm m} = 250$ kHz with varying $\beta(0-3.7)$ indicated by $V_{\rm m}(0-2)$ , compared |    |

| with modulation amplitude resulted from Jacobi-Anger expansion.                            | 36 |

| Figure 3-18- Measured frequency spectra of signals with $f_c = 30$ MHz and                 |    |

| $f_m = 250$ kHz with varying $V_m$ values of 0 to 2 V compared with the                    |    |

| absolute value of Bessel functions of first kind, $J_i(\beta)$ , for $i = 0, 1,, 8$ in     |    |

| a dBm scale.                                                                               | 37 |

| Figure 3-19- Schematic of the mixer, AD835, circuit.                                       | 38 |

| Figure 3-20- Schematic diagram of the experimental setup for measuring the                 |    |

| phase difference between odd and even sidebands.                                           | 39 |

| Figure 3-21- Spectra of signals of $f_c = 10$ MHz and $f_m = 50$ , 100, and 150            |    |

| kHz measured with frequency steps of 1 Hz.                                                 | 41 |

| Figure 4-1- Block diagram of the major components of the polydyne                |    |

|----------------------------------------------------------------------------------|----|

| interferometer.                                                                  | 46 |

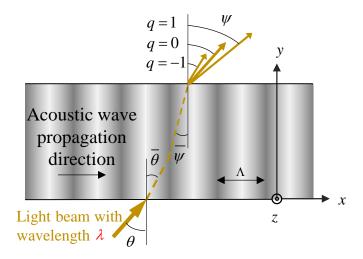

| Figure 4-2- Acoustic waves diffracting light beam like a diffraction grating.    | 47 |

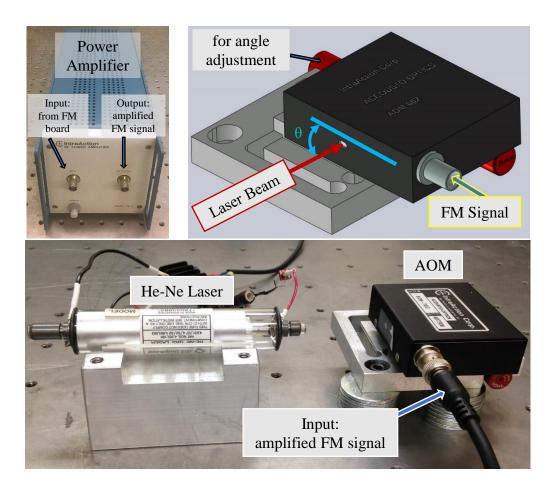

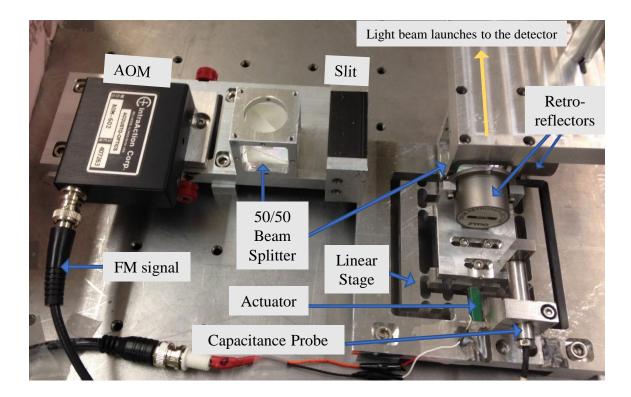

| Figure 4-3- Experimental setup to test the light diffraction by FM waves via     |    |

| an AOM.                                                                          | 51 |

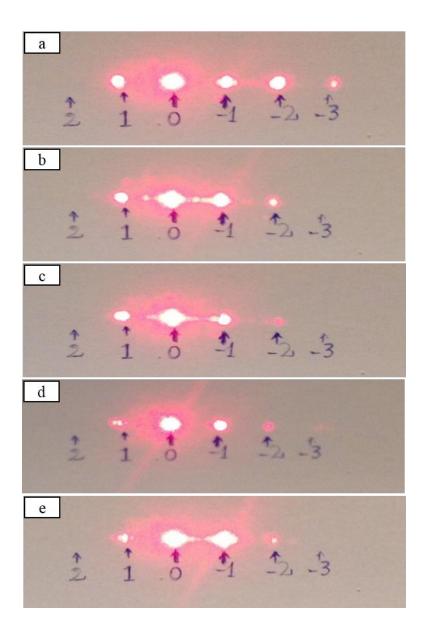

| Figure 4-4- Different diffraction patterns resulted from different incident      |    |

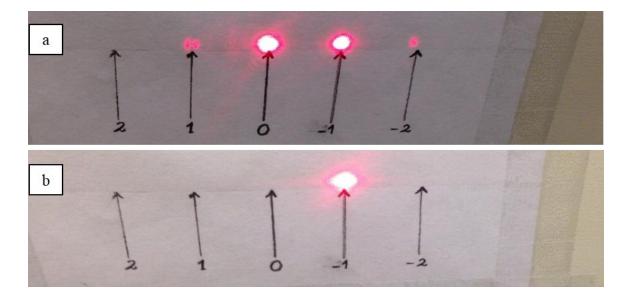

| angles.                                                                          | 52 |

| Figure 4-5- Diffraction side-beam extraction by a slit; a) before using slit; b) |    |

| after passing through the slit.                                                  | 53 |

| Figure 4-6- Experimental setup to evaluate the frequency spectra of              |    |

| diffraction side-beams.                                                          | 54 |

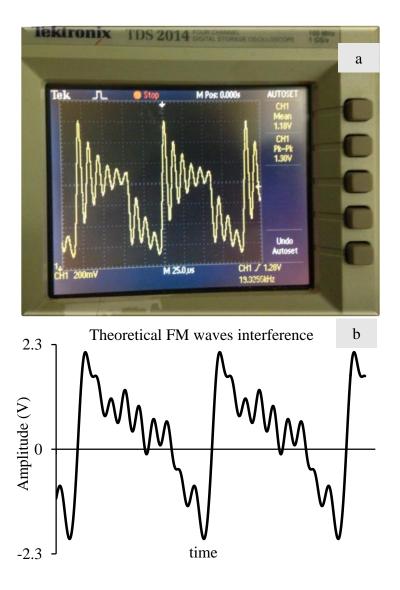

| Figure 4-7- FM light interference resulted from a) experimental setup shown      |    |

| in Figure 4-6 monitored in an oscilloscope, and b) theoretical FM waves          |    |

| interference.                                                                    | 55 |

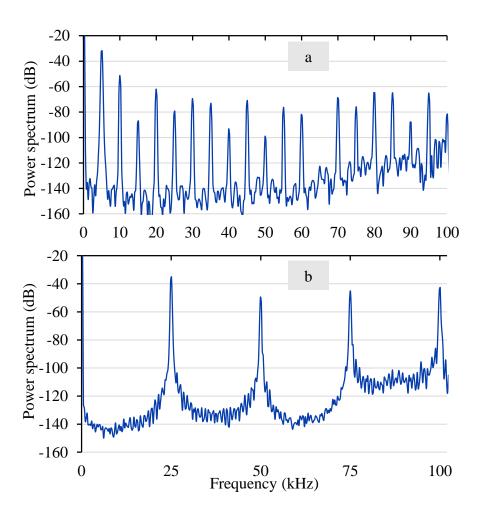

| Figure 4-8- Frequency spectra of the photodetector signal for a) $f_m = 5$ kHz,  |    |

| and b) $f_m = 25 \text{ kHz.}$                                                   | 57 |

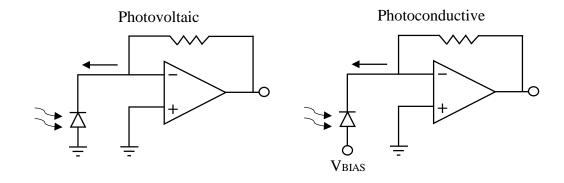

| Figure 5-1- Photovoltaic and photoconductive modes.                              | 59 |

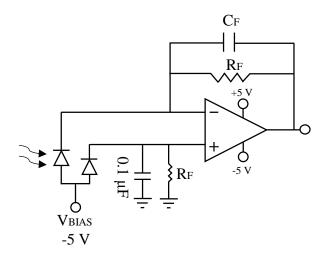

| Figure 5-2- Dark current compensation in photoconductive mode [81].              | 59 |

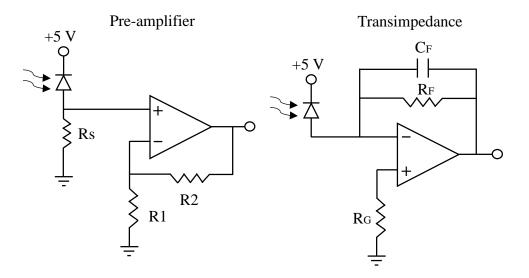

| Figure 5-3- Pre-amplifier and transimpedance configuration of photodetector     |    |

|---------------------------------------------------------------------------------|----|

| circuits.                                                                       | 60 |

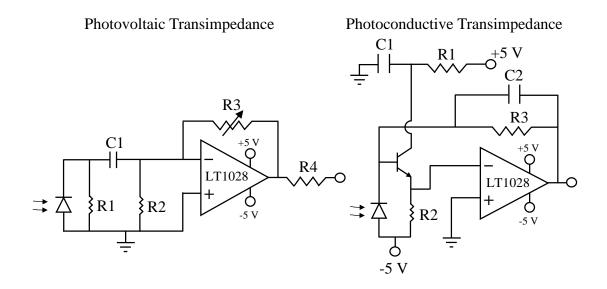

| Figure 5-4- The photovoltaic and photoconductive transimpedance                 |    |

| photodetector circuits.                                                         | 62 |

| Figure 5-5- Different prototypes of the first photodetector.                    | 62 |

| Figure 5-6- Photodiode preamp system with dark current compensation [81].       | 64 |

| Figure 5-7- Modified photodetector for use with FPGA board.                     | 64 |

| Figure 5-8- Schematic of Fourier transform implementation through analog        |    |

| demodulators.                                                                   | 65 |

| Figure 5-9- DSP lock-in amplifiers model SR850 [83].                            | 66 |

| Figure 5-10- Compact lock-in amplifier circuit using AD630 microchip [87].      | 66 |

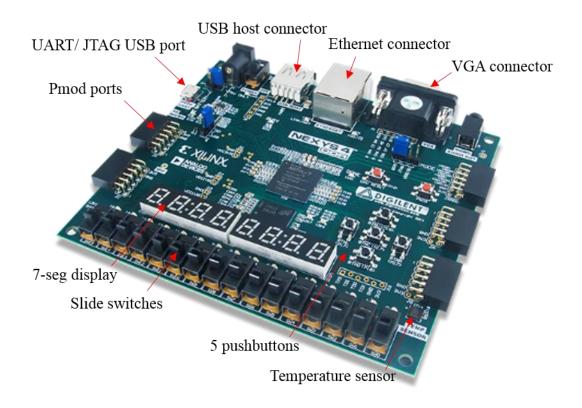

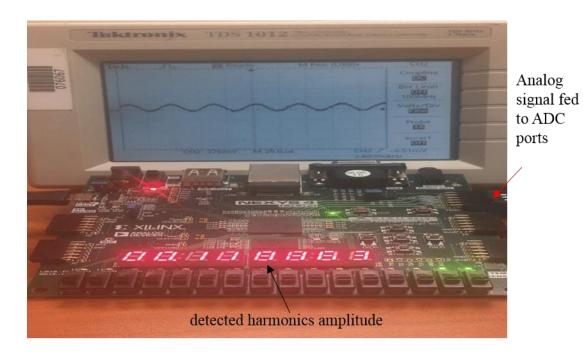

| Figure 5-11- NEXYS 4 DDR board.                                                 | 68 |

| Figure 5-12- Riemann sum approximation involved in calculation of Fourier       |    |

| coefficients from a discrete series, $X_r$ , rather than a continuous function, |    |

| x(t).                                                                           | 69 |

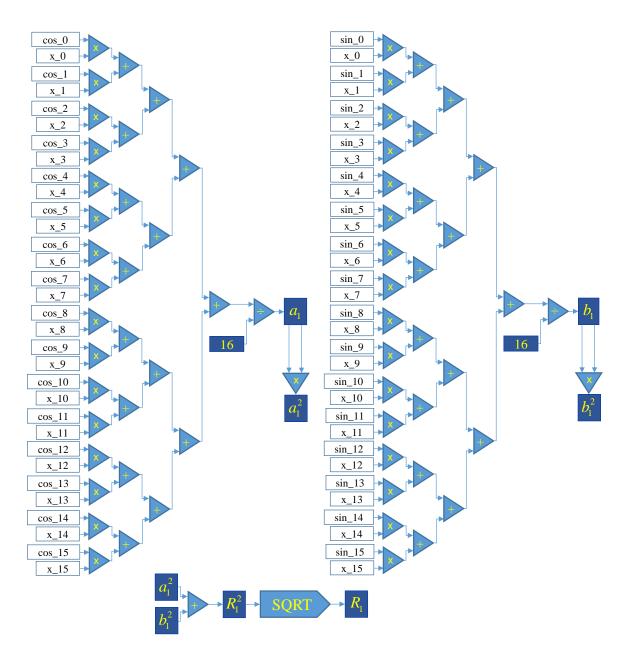

| Figure 5-13- Schematic of FPGA-based, 16 sample, discrete Fourier            |    |

|------------------------------------------------------------------------------|----|

| transform for extraction of the amplitude of first harmonic in the detected  |    |

| signal, $X_r$ .                                                              | 71 |

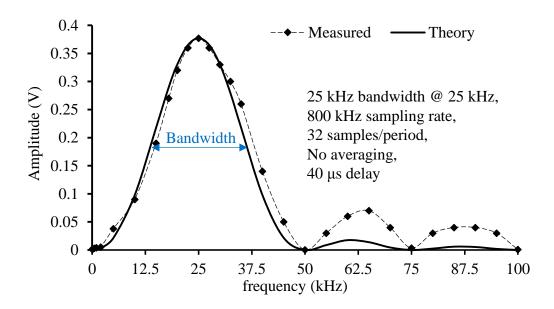

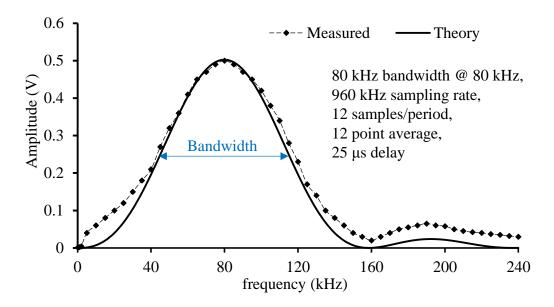

| Figure 5-14- Experimental setup to measure the frequency response of         |    |

| discrete Fourier transform.                                                  | 72 |

| Figure 5-15- FPGA-based Fourier transform spectrum response for 25 kHz       |    |

| signal.                                                                      | 73 |

| Figure 5-16- FPGA-based Fourier transform spectrum response for 80 kHz       |    |

| signal.                                                                      | 73 |

| Figure 5-17- Lissajous of Fourier transform coefficients of first and second |    |

| harmonics, and displacement calculated from these harmonics coefficients,    |    |

| compared with the applied displacement for maximum displacement speed        |    |

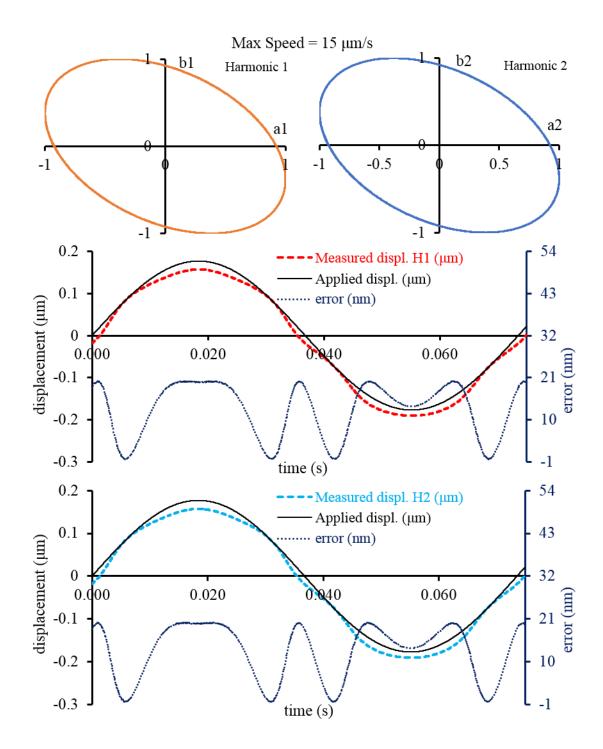

| of 15 μm·s-1.                                                                | 75 |

| Figure 5-18- Lissajous of Fourier transform coefficients of first and second |    |

| harmonics, and displacement calculated from these harmonics coefficients,    |    |

| compared with the applied displacement for maximum displacement speed        |    |

| of 1 mm·s-1.                                                                 | 76 |

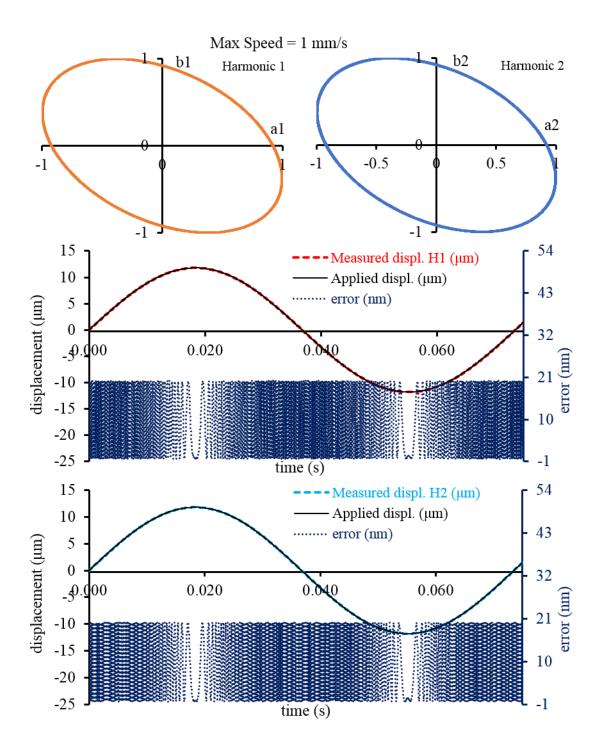

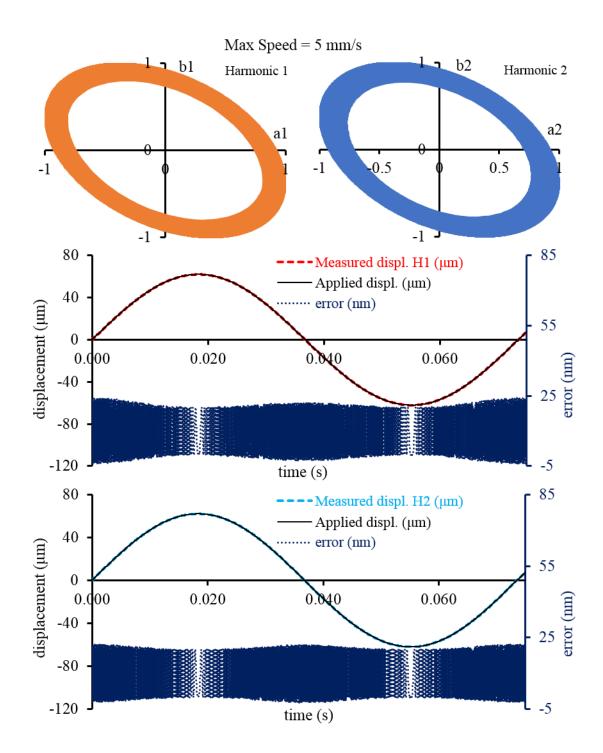

| Figure 5-19- Lissajous of Fourier transform coefficients of first and second |    |

| harmonics, and displacement calculated from these harmonics coefficients,    | 77 |

78

79

82

83

compared with the applied displacement for maximum displacement speed of 5 mm·s-1.

Figure 5-20- Lissajous of Fourier transform coefficients of first and second harmonics, and displacement calculated from these harmonics coefficients, compared with the applied displacement for maximum displacement speed of 7 mm·s-1.

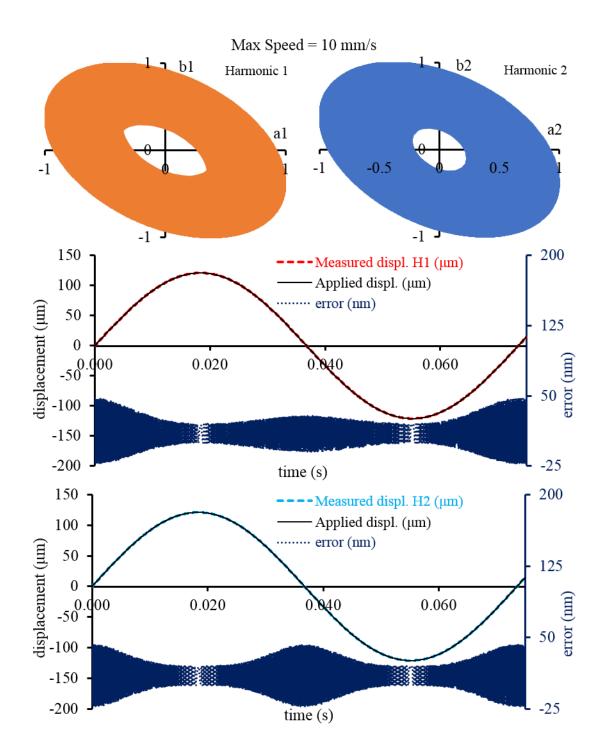

Figure 5-21- Lissajous of Fourier transform coefficients of first and second harmonics, and displacement calculated from these harmonics coefficients, compared with the applied displacement for maximum displacement speed of 10 mm·s-1.

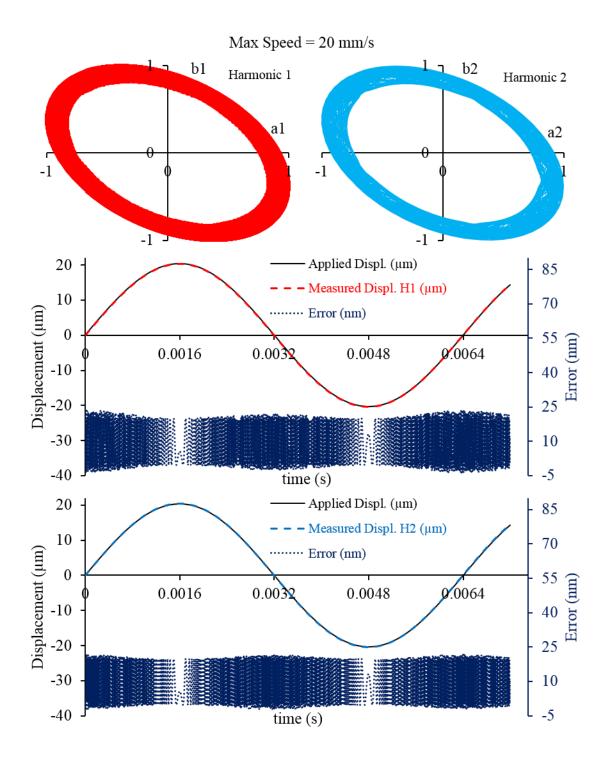

Figure 5-23- Lissajous of 32-sample, 32-averaged Fourier transform coefficients of first and second harmonics, and displacement calculated from these harmonics coefficients, compared with the applied displacement for maximum displacement speed of 20 mm·s-1.

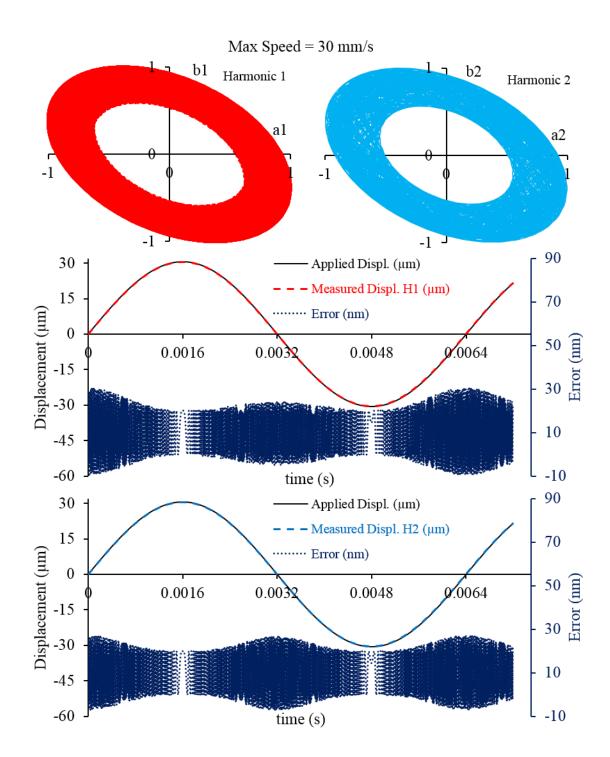

Figure 5-24- Lissajous of 32-sample, 32-averaged Fourier transform coefficients of first and second harmonics, and displacement calculated from these harmonics coefficients, compared with the applied displacement for maximum displacement speed of 30 mm·s-1.

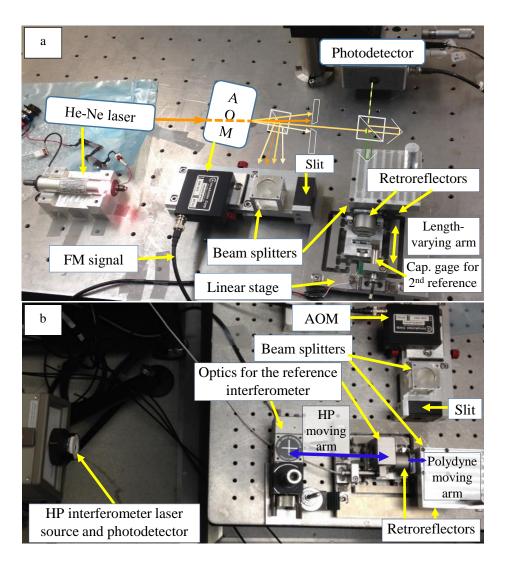

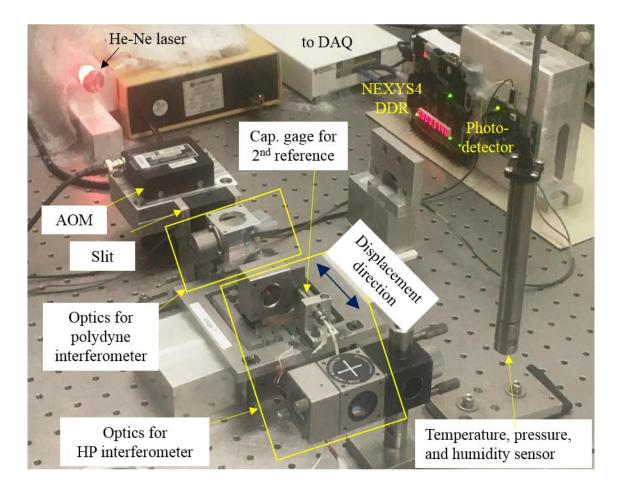

| Figure 6-1- Apparatus for interferometric displacement measurement, a)                |    |

|---------------------------------------------------------------------------------------|----|

| polydyne interferometer setup, b) added optics for the reference                      |    |

| interferometer.                                                                       | 85 |

| Figure 6-2- Modulation harmonics amplitude variations due to a sinusoidal             |    |

| displacement.                                                                         | 86 |

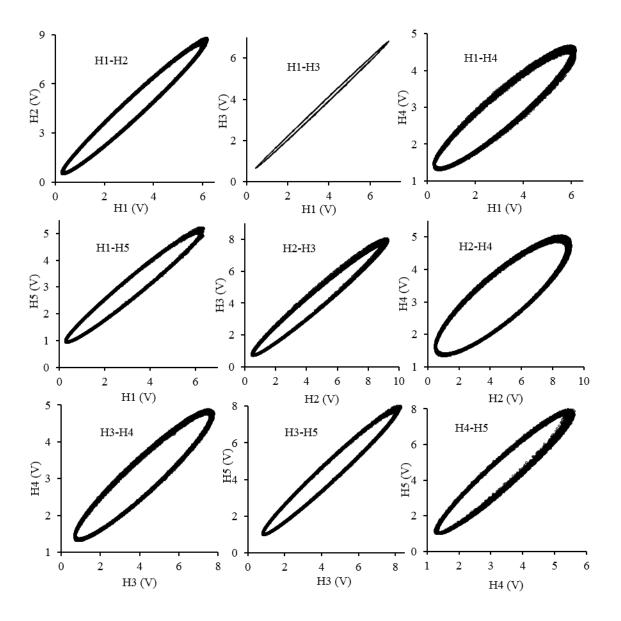

| Figure 6-3- Lissajous curves from different harmonic pairs of $f_m = 10$ kHz.         | 87 |

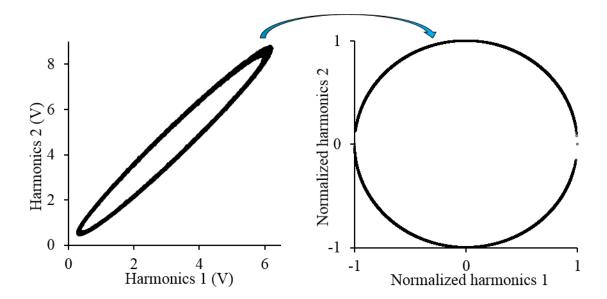

| Figure 6-4- Normalized Lissajous curve.                                               | 88 |

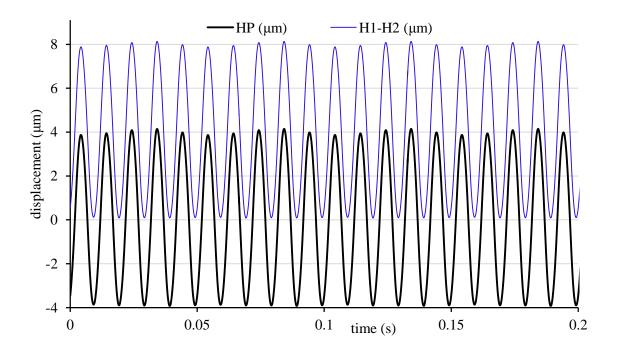

| Figure 6-5- Displacement measured by reference interferometer and H1-H2.              | 89 |

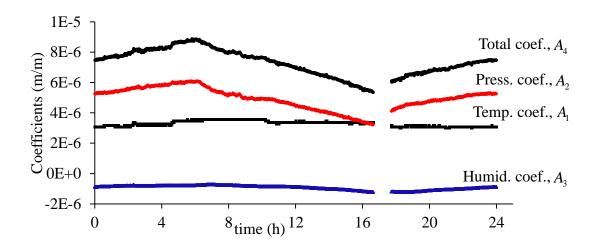

| Figure 6-6- Length correction coefficients for temperature, $A_1$ , pressure, $A_2$ , |    |

| humidity, $A_3$ , and total, $A_4$ .                                                  | 90 |

| Figure 6-7- Drift test results for HP and polydyne interferometer.                    | 91 |

| Figure 6-8- Lissajous measured by AD630 circuits at speeds of 1, 2, 14, and           |    |

| 15 μm·s-1.                                                                            | 92 |

| Figure 6-9- Experimental setup of polydyne interferometer with FPGA-                  |    |

| based Fourier transform.                                                              | 94 |

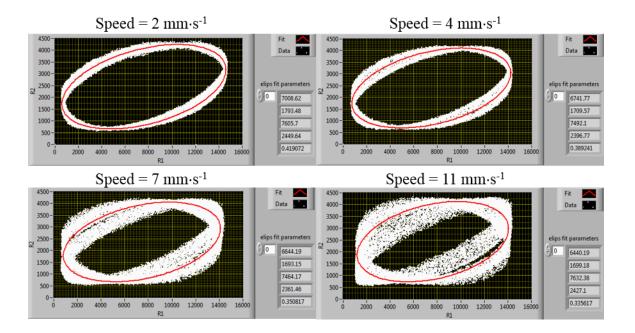

| Figure 6-10- Lissajous and fitted ellipse to the results of measurements by           |    |

| 32-sample, 32-point-averaged Fourier transform with 10 MHz ADC                        | 95 |

124

| mm·s-1.                                                                         |     |

|---------------------------------------------------------------------------------|-----|

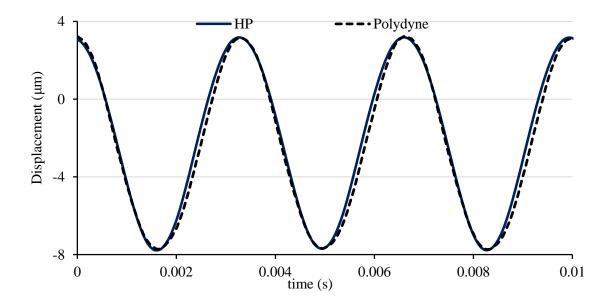

| Figure 6-11- Sinusoidal displacement with maximum speed of 2 mm.s-1             |     |

| measured by polydyne (H1-H2) and HP interferometers.                            | 96  |

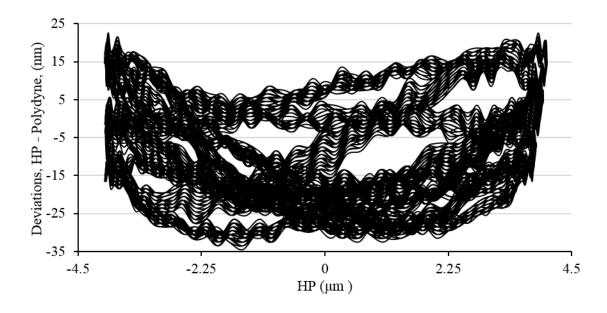

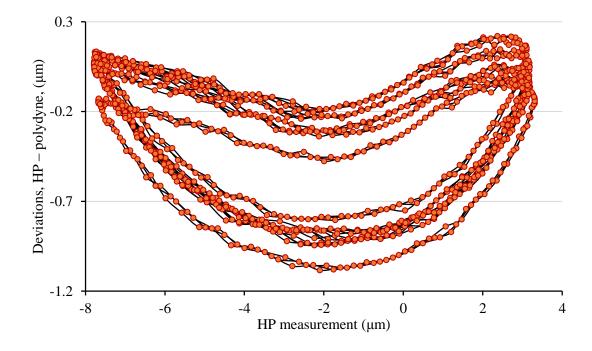

| Figure 6-12- Deviations between HP and polydyne (H1-H2) displacement            |     |

| measurements at maximum speed of 2 mm·s-1.                                      | 96  |

| Figure 6-13- Displacement measurement at maximum speed of 11 mm·s-1.            | 98  |

| Figure 6-14- Deviations between HP and polydyne measurements shown in           |     |

| Figure 6-13.                                                                    | 98  |

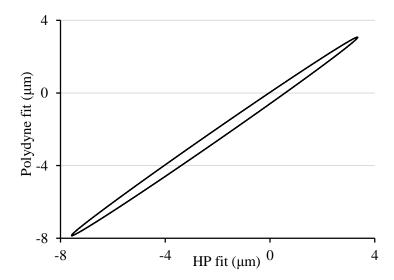

| Figure 6-15- Lissajous generated by depicting fit sine waves to displacement    |     |

| measurements by HP and polydyne interferometers.                                | 99  |

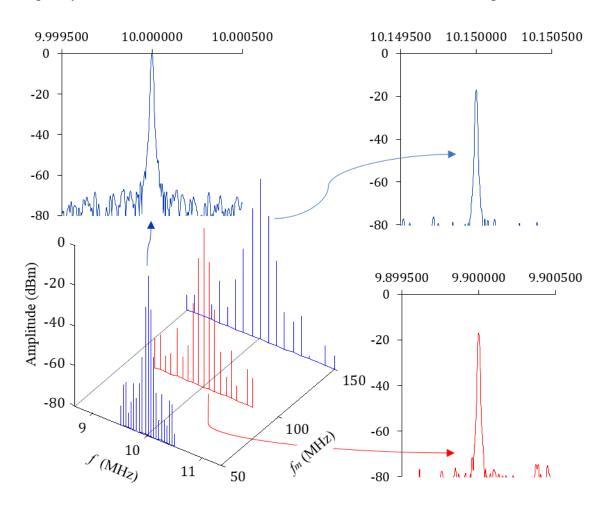

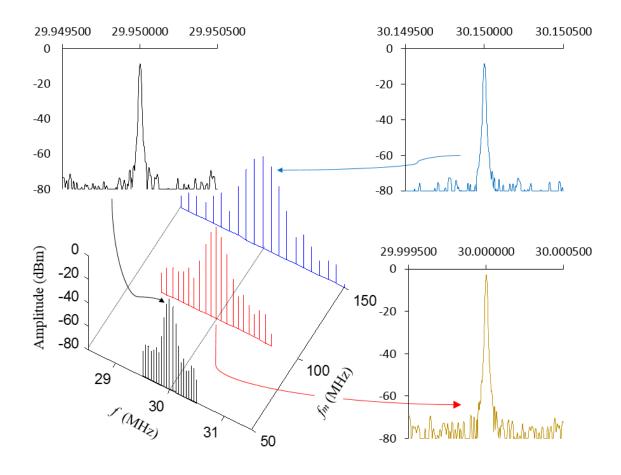

| Figure Appendix B-1- Spectra of signals of $f_c = 10$ MHz and $f_m = 50$ , 100, |     |

| and 150 kHz measured with frequency steps of 1 Hz.                              | 122 |

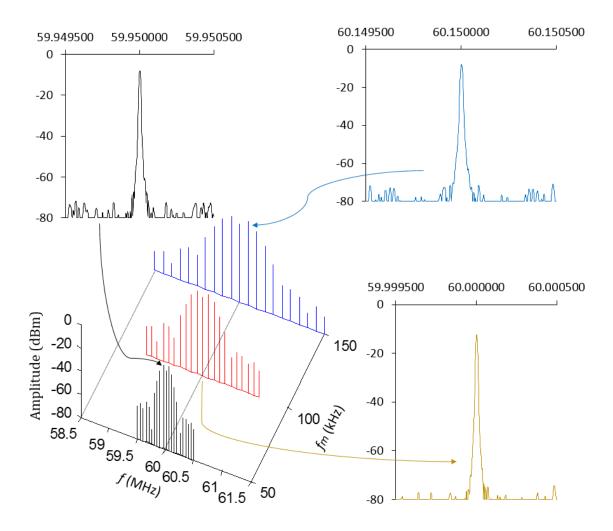

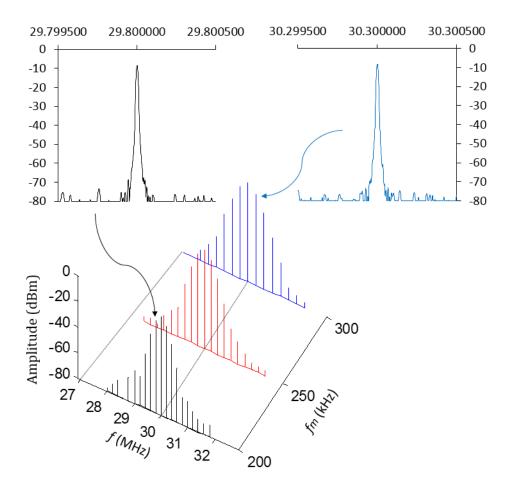

| Figure Appendix B-2- Spectra of signals of $f_c = 30$ MHz and $f_m = 50$ , 100, |     |

| and 150 kHz measured with frequency steps of 1 Hz.                              | 123 |

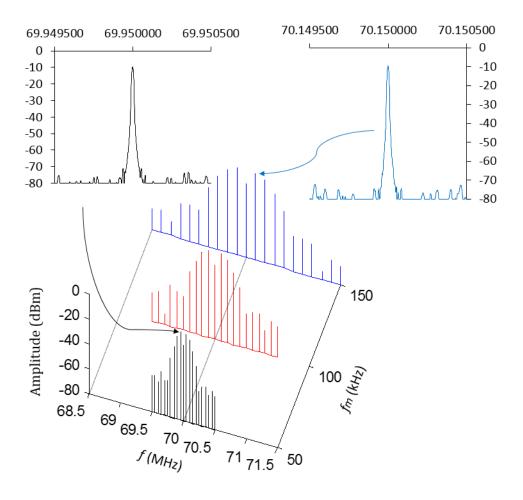

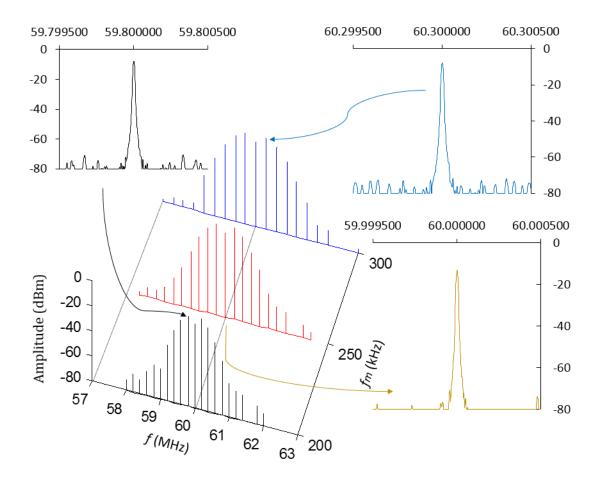

| Figure Appendix B-3- Spectra of signals of $f_c = 60$ MHz and $f_m = 50$ , 100, |     |

and 150 kHz measured with frequency steps of 1 Hz.

sampling rate and different maximum displacement speeds of 2, 4, 7, and 11

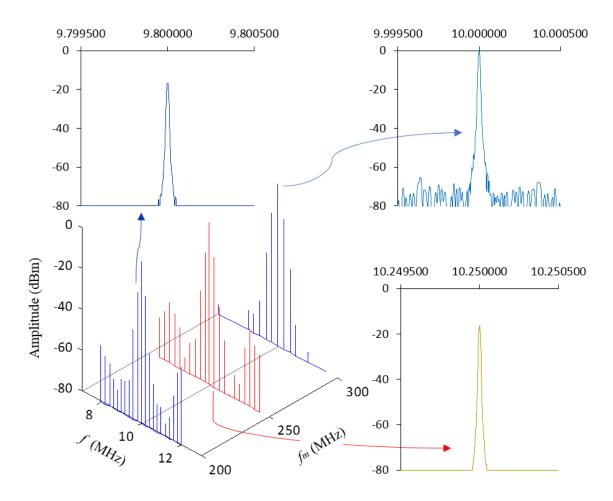

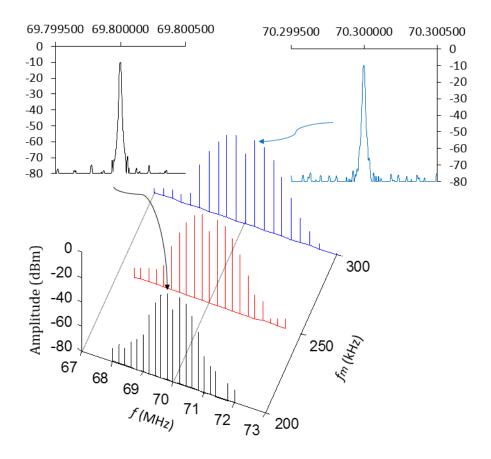

| Figure Appendix B-4- Spectra of signals of $f_c = 70$ MHz and $f_m = 50$ , 100, |     |

|---------------------------------------------------------------------------------|-----|

| and 150 kHz measured with frequency steps of 1 Hz.                              | 125 |

| Figure Appendix B-5- Spectra of signals of $f_c = 10$ MHz and $f_m = 200$ ,     |     |

| 250, and 300 kHz measured with frequency steps of 1 Hz.                         | 126 |

| Figure Appendix B-6- Spectra of signals of $f_c = 30$ MHz and $f_m = 200$ ,     |     |

| 250, and 300 kHz measured with frequency steps of 1 Hz.                         | 127 |

| Figure Appendix B-7- Spectra of signals of $f_c = 60$ MHz and $f_m = 200$ ,     |     |

| 250, and 300 kHz measured with frequency steps of 1 Hz.                         | 128 |

| Figure Appendix B-8- Spectra of signals of $f_c = 70$ MHz and $f_m = 200$ ,     |     |

| 250, and 300 kHz measured with frequency steps of 1 Hz.                         | 129 |

## LIST OF ABREVIATIONS

AOM Acousto-Optic Modulator

ADC Analog to Digital Convertor

BJT Bipolar Junction Transistor

CLCK Clock frequency, (Hz)

DAC Digital to Analog Converter

dBm decibel milliwatts

DDS Direct Digital Synthesizer

DSP Digital Signal Processing

FET Field Effect Transistor

FPGA Field Programmable Gate Arrays

FM Frequency Modulated

FSK Frequency Shift Keying

HP Hewlett-Packard

LiDAR Light Detection And Ranging

LUT Look-Up Table

PCB Printed Circuit Board

PLL Phase Locked Loop

PSK Phase Shift Keying

PZT Lead Zirconate Titanate

RF Radio Frequency

SCLCK System clock frequency inside the DDS after multiplier, (Hz)

SFDR Spurious-Free Dynamic Range

SMA SubMiniature version A

VHDL Very high speed integrated circuit Hardware Description Language

VHF Very High Frequency

### CHAPTER 1 INTRODUCTION

This chapter consists of two sections that present a summary of literature about displacement measurement interferometers in section 1.1, and objectives of this work in section 1.2.

### 1.1 Literature Review

The essential idea behind optical interference is that since light acts as an electromagnetic wave, optical interference results from the superposition of the electric field of two or more light beams as waves. Optical interference has played a prominent role in modern technology. It was first used by Thomas Young to discover the wave nature of light via the well-known double-slit experiment [1]. Albert A. Michelson and Edward W. Morley used white light interference through the well-known Michelson interferometer to show that there was no foundation for the existence of an aether [2]. Since then, there have been numerous advances in optics, interferometry, and supporting fields like; stabilized long coherence lasers, low-noise photodetectors, and ultrahigh speed, ultralow-noise electronic microchips for signal generation, detection and processing. All these advances along with Michelson's technique have produced many great technologies such as spectroscopy [3], displacement measuring interferometry [4], absolute distance measuring interferometry [5], Light Detection And Ranging (LiDAR) velocimetry [6], optical gyroscope [7], and so on.

Twyman and Green modified Michelson's interferometer by collimated light [8].

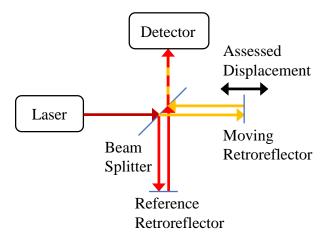

The method used by Twyman and Green is nowadays used in most displacement measurement interferometers for measuring the position change of a target object. A simple schematic of a displacement measuring interferometer is shown in Figure 1-1.

Figure 1-1- Schematic of a simple displacement measuring interferometer.

Typically, the fixed arm is called the reference arm and the moving arm is called the measurement arm. Any displacement in the measurement arm changes the optical path length of the measurement arm causing the intensity of the interfered beam at the detector to vary between destructive and constructive patterns. Assuming a wavelength of  $\lambda$ , displacement of  $\Delta L$  results in a phase change of  $\phi$  in the captured intensity of the interference:

$$\phi = 2\pi n N \Delta L / \lambda . \tag{1-1}$$

where, n is the refractive index of air, N the path factor that is the number of times the light beam traverses the displacement path. Since the measured phase is a modulus of  $2\pi$ , it should be unwrapped to determine the actual displacement.

The primary objective of any displacement measuring system is to perform linear and repeatable measurements. Repeatability as the maximum deviation between the measurements of a measurand under the same conditions and with the same measuring instrument refers to how stable the measurement will be over time. System measurement repeatability consists of two parts of short-term and long-term repeatability. Short-term repeatability is the measurement stability over a period shorter than one hour; long-term repeatability is stability over a period longer than one hour. Repeatability error budgets of a displacement measurement interferometer are categorized as intrinsic (laser wavelength, electronics error, optics nonlinearity), environmental (atmospheric compensation, material thermal expansion, optics thermal drift), and installment (deadpath error, Abbé error, cosine error). Intrinsic error components are the main focus of instrument manufacturers [9].

Displacement interferometers, just like any other displacement measurement systems, can be classified based on their dynamic range and precision. Some applications require high resolution (0.1 nm to 10 nm), low dynamic range interferometers [10] such as metrology for semiconductor fabrication [11], large optics fabrication [12], stellar interferometry [13], and precision robotics in medicine [14]. Another significant group of applications like machine tool metrology [15] require coarser resolutions (about 10 nm to 50 nm) displacement measurement interferometers with measurement ranges of a few meters and speeds of greater than 10 mm·s<sup>-1</sup>.

Through decades of research effort, a wide variety of methods have been developed to overcome the challenges on building a robust, repeatable, linear interferometer [10]. All of these methods are generally categorized as either homodyne

[16] or heterodyne systems [17, 18]. In homodyne interferometers, the phase change is measured from DC-level fluctuations of the intensity of the interference. The major disadvantages of homodyne interferometers are their inherent lack of directional sensitivity and dependence on a constant maximum intensity of signal. The later has been solved by automatic compensation of the changes of the signal level [19]. The former problem has been solved by two different methods of adding directional sensitivity to the homodyne interferometers using: 1) phase quadrature measurement by applying known phase shift to the detected signal [20, 21], 2) amplitude demodulation technique by modulating the laser intensity with a known carrier frequency [4].

Heterodyne interferometers use a laser light containing two distinct frequencies that have a known frequency difference, i.e. beat/heterodyne frequency. These two frequencies are orthogonally polarized so that they can perform direction sensitive displacement detection. Each of the orthogonally polarized optical waves construct one of the arms, i.e. the reference arm and the measurement arm, of the interferometer. Since orthogonally polarized waves do not interfere, the interference is achieved by passing orthogonal beams through a polarizer aligned at 45 degrees [4]. Since the heterodyne interferometers usually have a heterodyne frequency of a few megahertz, they require a high detection bandwidth which is usually achieved by flash photodetectors and other ultrahigh-speed electronics. These requirements make the heterodyne systems more complex and expensive in comparison with homodyne systems.

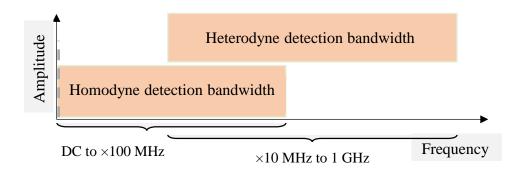

Required bandwidth of homodyne and heterodyne systems are shown in Figure 1-2. The interferometers detection bandwidth limit is drastically increasing by the increase of the electronics microchips speed so that the state-of-the-art miniature

retroreflector homodyne interferometers provide 800 mm·s<sup>-1</sup> with 20 pm resolution [22]. Moreover, state-of-the-art heterodyne interferometers provide extraordinary low noise of 7.1 fm·Hz<sup>-1</sup> at 21 MHz [23].

Figure 1-2- Typical detection bandwidth of homodyne and heterodyne interferometers.

Commercial laser-based displacement measurement interferometer systems typically use tunable [24], Zeeman split [10], or unmodulated Acousto-Optic Modulator (AOM) Doppler shifted lasers [25] to provide a frequency shifted light source. Rapidly tunable lasers are widely used for communication applications, typically with wavelength of 1550 nm, and controlled tuning frequencies up to 1.2 kHz. Consequently, this limits the measurement bandwidth to below 1 kHz [24, 26, 27]. Zeeman split and AOM Doppler shift methods provide only two frequencies thereby providing heterodyne sources.

A new generation of interferometers have recently been introduced that modulate the frequency of the laser beam by a sinusoidal phase. In this method, the phase information of interest is extracted from the harmonics of the modulation frequency as the beats. The sinusoidal phase can be injected into the laser beam by different methods. In the first method [28], the beam propagates in an optical fiber and a piezo applies a

sinusoidal motion to the optical fiber; this method is called deep phase modulation interferometry. In the second method [29, 30], an electro-optical amplitude modulator modifies the laser frequency with a sinusoidal signal; this method is called deep frequency modulation interferometry. Highly compact extrinsic Fabry-Perot interferometers [26, 27] is another example of dynamic sinusoidal frequency modulation technique that uses the same method of deep frequency modulation interferometry for injecting the sinusoidal phase into the laser beam.

The dynamic frequency modulation technique is different from that of phase-shifting interferometry [31-33]. The phase-shifting interferometry applies a sequence of static phase shifts into the light beam to generate a sequence of phase-shifted fringe patterns to measure the profile of smooth surfaces [33]. Since the applied phase-shift is quasi-static, it does not change the frequency band of the measurement. Contrarily, the dynamic frequency modulation techniques change the temporal frequency of the laser beam continuously so that the optical phase of interest is measured in the beat frequencies that are resulted from this dynamic frequency change. This later technique is not as sensitive to low frequency environmental noise as the phase-shifting interferometry.

Deep frequency modulation-based interferometers combine strong sinusoidal laser frequency modulation in unequal arm length interferometers with a non-linear fit algorithm for phase extraction. The demodulation algorithm or the non-linear fit is implemented in a FPGA to miniaturize the system [28]. Extrinsic Fabry-Perot interferometer uses self-homodyning (also used in our method) by sinusoidal frequency modulation of the laser source wavelength to achieve sub-nanometer resolution displacement measurement in a compact sensing volume. Application of compact

interferometers in simple position sensors and high-resolution inertial sensors has been recently reviewed in Ref. [34]. This review provides a summary of variety of optical interferometry techniques and their pros and cons in terms of measurement linearity and resolution, compactness of the interferometer, cost, and finally their inherent susceptibility to shot noise and length noise that couples to their readout [34].

Two methods to generate frequency or phase modulated laser light are: 1) by applying a modulation directly to the light source (direct method), 2) by passing the beam through a frequency shifter (indirect method). Optical serrodyne frequency translation [35] used in LiDAR velocimetry [6] and in optical gyroscopes [7] are examples of an indirect frequency shifting method, whereas changing the drive current through a laser diode to produce FM light is a direct method [36, 37].

## 1.2 Objectives of this research

There is always need for low cost, portable displacement measurement interferometers. The main objective of this research is to design and implement a low cost, portable displacement measurement interferometer with sub 50 nm resolution and measurement speed of about 10 mm·s<sup>-1</sup> for metrology applications. This is achieved by generating a stabilized FM light source for interferometry. This method combines the homodyne and heterodyne interferometry detection bandwidth to extract the phase information from harmonics of modulation frequencies at an update rate of a few hundred kHz. Therefore, it does not require ultrafast flash photodetectors and ultrahigh-speed electronics resulting in a substantial drop in the final cost of the system.

We have developed a new method to transfer the precision of atomic clocks to dynamic frequency modulation interferometry. This method that is being named as

polydyne interferometry technique comprises three main parts: 1) generating a synchronous RF-FM electrical signal, 2) transferring the FM signal into a laser beam using an AOM, and 3) signal detection and processing. The advantages of this approach are that measurement for any single degree of freedom requires only one detector, ultrahigh-speed ultrafast flash detectors and polarization optics are unnecessary, and all the frequency components are synchronous and they all follow the same path around the interferometer paths. More broadly the ability to create multiple, phase-synchronous reference beams enables an arbitrary large number of synchronous interference measurements. Using only a single AOM, multiple diffraction orders are relatively straightforwardly extracted. Each of these diffraction orders contain the same modulation frequency harmonics.

## CHAPTER 2 INTERFERENCE OF FM LIGHT BEAMS

Interference of FM waves are the foundation of the polydyne interferometry technique presented in this thesis. In unequal arm length interferometers such as a Michelson interferometer, the resultant optical signal at the photo diode incorporates the superposition of the beams travelling through the short and the long arm that have an optical path difference of  $\Delta L$  (corresponding to a time delay of  $\tau = \Delta L/c$ , where c is the speed of light in the medium). Assuming an FM light with carrier frequency  $\omega_0$ , amplitude  $E_0$ , and modulation frequency  $\omega_m$  that is split by a 50/50 beam splitter to produce the signals of each arm of a Michelson interferometer,  $u_1$  and  $u_2$ :

$$\frac{u_1(t)}{E_0/2} = \sin\left(\omega_0 t - \beta\cos\left(\omega_m t\right) + \phi_0\right) = -\frac{i}{2} \left\{ e^{i\left[\omega_0 t - \beta\cos\left(\omega_m t\right) + \phi_0\right]} - e^{-i\left[\omega_0 t - \beta\cos\left(\omega_m t\right) + \phi_0\right]} \right\}, \tag{2-1}$$

$$\frac{u_{2}(t)}{E_{0}/2} = \sin\left(\omega_{0}(t-\tau) - \beta\cos\left(\omega_{m}(t-\tau)\right) + \phi_{0}\right)

= -\frac{i}{2} \left\{ e^{i\left[\omega_{0}(t-\tau) - \beta\cos\left(\omega_{m}(t-\tau)\right) + \phi_{0}\right]} - e^{-i\left[\omega_{0}(t-\tau) - \beta\cos\left(\omega_{m}(t-\tau)\right) + \phi_{0}\right]} \right\}$$

(2-2)

where,  $\beta$  is the modulation depth,  $\phi_0$  is the initial phase of light, phase @ t=0, at the photo diode. The intensity of optical signal produced in the photo diode,  $I(t,\tau)$ , is

$$\frac{I(t,\tau)}{E_0^2/4} = \frac{\left(u_2(t) + u_1(t)\right)^2}{E_0^2/4} = \left(\frac{\sin\left(\omega_0(t-\tau) - \beta\cos\left(\omega_m(t-\tau)\right) + \phi_0\right)}{+\sin\left(\omega_0t - \beta\cos\left(\omega_mt\right) + \phi_0\right)}\right)^2.$$

(2-3)

Assuming the initial phase equal to zero,  $\phi_0 = 0$ , the intensity of optical signal is

$$\frac{I(t,\tau)}{-E_{0}^{2}/2} = \begin{pmatrix} \left(e^{i\left[\omega_{0}t-\beta\cos(\omega_{m}t)\right]} - e^{-i\left[\omega_{0}t-\beta\cos(\omega_{m}t)\right]}\right)/2 \\ + \left(e^{i\left[\omega_{0}(t-\tau)-\beta\cos(\omega_{m}(t-\tau))\right]} - e^{-i\left[\omega_{0}(t-\tau)-\beta\cos(\omega_{m}(t-\tau))\right]}\right)/2 \end{pmatrix}^{2}$$

$$= \begin{pmatrix} \left(e^{2i\omega_{0}t}e^{-2i\beta\cos(\omega_{m}t)} + e^{-2i\omega_{0}t}e^{2i\beta\cos(\omega_{m}t)} - 2\right)/4 \\ + \left(e^{2i\omega_{0}(t-\tau)}e^{-2i\beta\cos(\omega_{m}(t-\tau))} + e^{-2i\omega_{0}(t-\tau)}e^{2i\beta\cos(\omega_{m}(t-\tau))} - 2\right)/4 \\ + \left(e^{2i\omega_{0}t}e^{-i\beta\cos(\omega_{m}t)}e^{-i\beta\cos(\omega_{m}t)}e^{-i\beta\cos(\omega_{m}(t-\tau))} + e^{-2i\omega_{0}t}e^{i\omega_{0}\tau}e^{i\beta\cos(\omega_{m}t)}e^{i\beta\cos(\omega_{m}(t-\tau))}\right)/2 \\ - \left(e^{i\omega_{0}\tau}e^{-i\beta\cos(\omega_{m}t)}e^{i\beta\cos(\omega_{m}(t-\tau))} + e^{-i\omega_{0}\tau}e^{i\beta\cos(\omega_{m}t)}e^{-i\beta\cos(\omega_{m}(t-\tau))}\right)/2

\end{pmatrix} \tag{2-4}$$

The intensity equation (2-4) represents some fluctuations at frequencies of  $2\omega_0\pm p\omega_m$ , in which p is an integer number, and other fluctuations at harmonics of  $\omega_m$ . In practice, fluctuations at  $2\omega_0\pm p\omega_m$  occur too fast to measure so that they average out to zero, after which the measured intensity reduces to

$$I(t,\tau) = \frac{E_0^2}{2} \left( 1 + \left( e^{i\omega_0 \tau} e^{-i\beta\cos(\omega_m t)} e^{i\beta\cos(\omega_m (t-\tau))} + e^{-i\omega_0 \tau} e^{i\beta\cos(\omega_m t)} e^{-i\beta\cos(\omega_m (t-\tau))} \right) / 2 \right)$$

$$= \frac{E_0^2}{2} \left[ 1 + \cos\left(\omega_0 \tau + \beta\cos(\omega_m \tau) - \cos\left(\omega_m (t-\tau)\right)\right) \right] \qquad (2-5)$$

$$= \frac{E_0^2}{2} \left[ 1 + \cos\left(\omega_0 \tau + \beta\sin(\omega_m \tau/2)\sin(\omega_m (t-\tau/2))\right) \right]$$

For typical metrology applications, the length of both arms of the interferometer is, at most, of the orders of a meter, from which  $\tau \approx 1 \text{m/c} = 1/299792458 \approx 3.3 \times 10^{-9} \text{ s}$ .

Therefore, for  $\omega_m \approx 10^5$  Hz,  $\omega_m \tau \approx 3.3 \times 10^{-4} << 1$  so that  $\sin(\omega_m \tau/2) \approx \omega_m \tau/2$  and  $\sin(\omega_m (t - \tau/2)) \approx \sin(\omega_m t)$ ; this leads to the simplified form of measured irradiance:

$$I(t,\tau) = \frac{E_0^2}{2} \Big[ 1 + \cos(\omega_0 \tau + \beta \tau \sin(\omega_m t)) \Big]$$

$$= \frac{E_0^2}{2} \Big[ 1 + \cos(\omega_0 \tau) \cos(\beta \tau \sin(\omega_m t)) - \sin(\omega_0 \tau) \sin(\beta \tau \sin(\omega_m t)) \Big]$$

(2-6)

Setting  $\gamma = \beta \tau$  as the effective modulation depth,  $\phi = \omega_0 \tau$  as displacement-related optical phase change, and using Jacobi-Anger expansion [38, 39] for  $\sin(\gamma \sin(\omega_m t))$  and  $\cos(\gamma \sin(\omega_m t))$  gives

$$I(t,\tau) = I_0 \begin{bmatrix} 1 + \cos(\phi) \left( J_0(\gamma) + 2\sum_{p=1}^{\infty} J_{2p}(\gamma) \cos(2p\omega_m t) \right) \\ + \sin(\phi) \sum_{p=1}^{\infty} -2J_{2p-1}(\gamma) \cos((2p-1)\omega_m t) \end{bmatrix}.$$

(2-7)

In which,  $J_p(\gamma)$  are the Bessel functions of first kind,  $I_0 = E_0^2/2$  is the average intensity on the detector,  $I_0J_0(\gamma)\cos(\phi)$  is the homodyne equivalent intensity that will be equal to  $I_0\cos(\phi)$  for  $\gamma=0$  as it is expected from the intensity of unmodulated signals interference,  $\sum_{p=1}^{\infty}J_{2p-1}(\gamma)\cos((2p-1)\omega_m t)$  is the odd harmonics of the modulation frequency whose amplitude changes with odd part of the phase, and  $\sum_{p=1}^{\infty}J_{2p}(\gamma)\cos(2p\omega_m t)$  is the even harmonics of the modulation frequency whose amplitude changes with even part of the phase. Equivalent expressions have been presented in different studies [30, 40] in which all of them have used the same

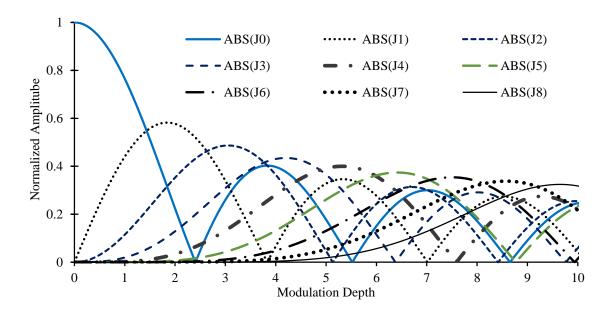

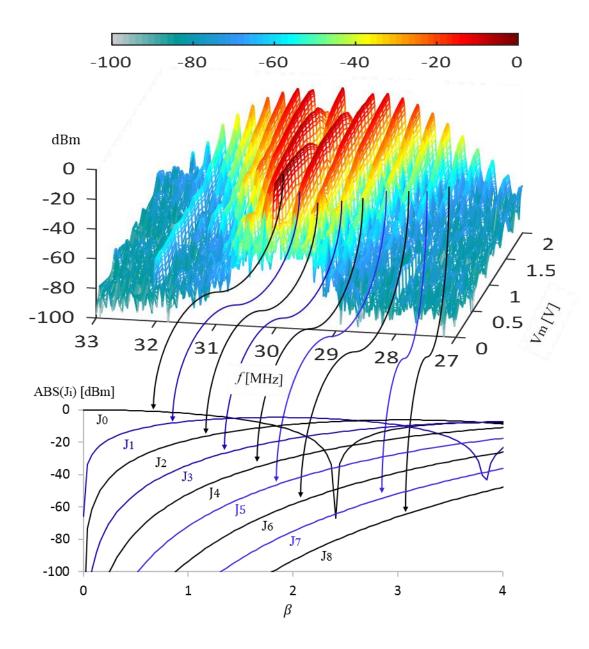

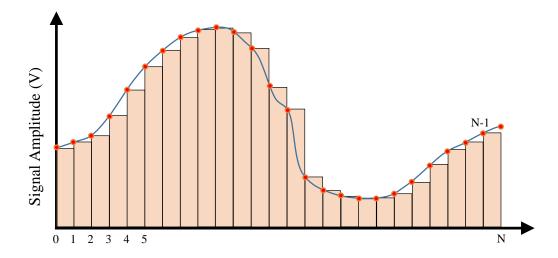

simplifications to derive an expression for the harmonics signals. Increasing the effective modulation depth,  $\gamma$ , spreads the energy of interference among the harmonics of modulation frequency. This can be observed in the absolute value of Bessel functions of first kind,  $J_i(\beta)$ , for  $i=0,1,\ldots,8$ , see Figure 2-1.

Figure 2-1- Absolute value of Bessel functions of first kind,  $J_i(\beta)$ , for i = 0, 1, ..., 8 in a normalized scale.

The amplitudes of the odd and even harmonics are commonly called in-phase,  $I_{2p-1}$ , and quadrature,  $I_{2p}$ , signals, respectively. Applying Fourier transform to the measured intensity, equation (2-7), results in following expressions for the in-phase and quadrature signals from which phase can be extracted [41, 42]:

$$I_{2p-1} \approx I_0 J_{2p-1}(\gamma) \sin(\omega_0 \tau)$$

$$I_{2p} \approx I_0 J_{2p}(\gamma) \cos(\omega_0 \tau)$$

(2-8)

In order to extract the phase from the measured in-phase and quadrature signals, these signals are first normalized and phase-adjusted to fit in a unity circle after which the phase is calculated as

$$\phi = \tan^{-1} \left( \frac{I_{2p-1,u}}{I_{2p,u}} \right), \tag{2-9}$$

where,  $I_{2p-1,u}$  and  $I_{2p,u}$  are the normalized, phase adjusted  $I_{2p-1}$  and  $I_{2p}$ , respectively. Finally, the displacement of the moving arm of the interferometer is derived from the measured phase as

$$\Delta L = \frac{\phi \lambda}{2\pi nN} \ . \tag{2-10}$$

All the equations presented in this chapter represent the ideal condition of perfect FM signals interference. If the interfering beams are not perfect FM waves, the distribution of energy in different frequency components will be different from equation (2-7). In such circumstances, each of the odd and even harmonics of the modulation frequency might carry both  $\sin(\omega_0\tau)$  and  $\cos(\omega_0\tau)$ . This provides the opportunity to calculate the optical phase information,  $\phi = \omega_0\tau$ , by extracting the amplitude of sine and cosine of each of the modulation signal harmonics. The proof of this hypothesis is left as a suggestion for future work.

#### CHAPTER 3 SYNCHRONOUS FM SIGNAL GENERATION

This chapter consists of four sections that present a summary of literature about digital FM signal generation methods in section 3.1, the principle operation mechanism of a new FM signal generation method introduced in this work in section 3.2, the new FM circuit design in section 3.3, and the testing and results of spectrum of generated FM signals by different prototypes of the new FM signal generator in section 3.4.

#### 3.1 Digital FM signal generation background

Frequency modulation in instrumentation and communication include a broad range of sensing strategies and information transmission methods. Such strategies range from single frequency transmission and reception with amplitudes representing the DC value, through to phase/frequency modulation and phase locking and, ultimately, multiple phase and frequency transmission for synchronous, parallel, digital data transfer. All of the modulation techniques share the main concept through which signals are mixed to operate at more conveniently measured harmonic frequencies and intermediates as is the case for heterodyne and super-heterodyne techniques [43]. Such processes find applications in both optical processes and radio transmission [43-45]. Of particular recent interest is the implementation of these modulation techniques for development of optical interferometric instrumentation [24, 26, 46]. In these techniques, the interferometric phase is extracted using multiple sidebands which has led to novel sensing methods.

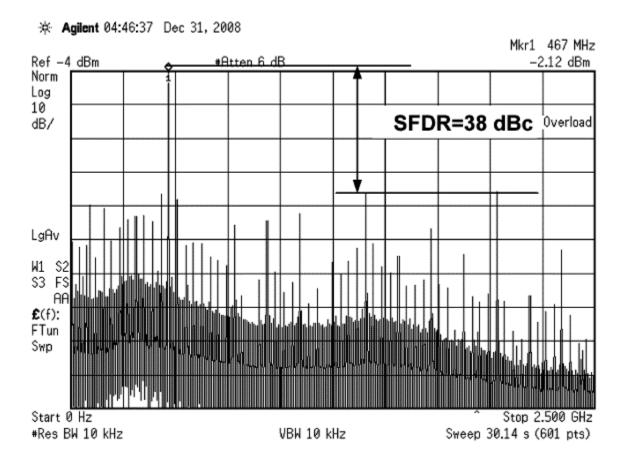

Until the last few decades, most radio frequency modulators were implemented by analog circuits. Since digital phase/frequency modulators are compact and often provide superior frequency stability, they have now evolved as replacements for the bulky analog circuits. One such, digital approach, are Direct Digital Synthesizers (DDS) that provide low distortion signals with frequencies exceeding 400 MHz, a limit that is continuously increasing [47]. The method used in commercial DDS chips to generate modulated signals is based on regularly updating a phase offset word in a look-up table via a serial port [48-50] and is limited by the speed of the port. Furthermore, this method does not necessarily lead to synchronous FM signals, since the serial port is not necessarily timed with the main clock of the system. Recent studies have been focused on high speed DDS technology with FM capabilities over GHz frequencies [51-57]. One such development is the DDS that has been manufactured in Ref. [58] as the first DDS that generates FM signals at frequencies above 1 GHz. The aim reported in Ref. [58] is to provide all functionality of over-GHz FM signal generation in a single microchip. Their DDS architecture uses carry-look-ahead or ripple-carry-adder to boost the speed of registering frequency control word of a precursor design that uses bipolar plus negative metal oxide semiconductor adder architecture [59], and uses a 5 GHz clock to time the data transfer buses. This DDS has been designed to be used in radar technology where the best spurious free dynamic range at higher frequencies, i.e. over-GHz frequencies, is the main functional figure of merit. Also, this DDS provides 38 dBc Nyquist band and 83 dBc narrowband spurious-free dynamic range for over GHz carrier frequencies, see Figure 3-1 [59].

Another research group has produced an all-digital, direct frequency synthesizer that provides direct modulation capabilities at 20 Mbps with 3 µs startup latency [60]. In this work, they have claimed that a synthesizer can generate desired frequencies over a wide range by digitally manipulating time-shifted copies of a temperature-compensated film bulk acoustic resonator signal based on the outputs from a sigma-delta modulator. Performance of a working circuit has not been reported yet.

Figure 3-1- Frequency spectrum of DDS output with a 469.360351 MHz output showing a 38 dBc Nyquist band spurious-free dynamic range [59].

In principle, it is possible to generate a phase modulated signal by dynamically updating the phase offset control of some commercial DDS chips (such as AD9834, and the AD9951 used in our design). Phase Shift Keying (PSK) and Frequency Shift Keying

(FSK) are two common data encoding methods that are used in these DDS architectures for modulating the phase and frequency of the desired output signal, respectively. In PSK, the phase of the transmitted signal is changed, while the frequency of the carrier remains constant. FSK allows a binary shifting of the frequency of a continuous carrier to one or the other of two discrete frequencies. Two frequency registers are required to achieve a fast tuning into these two frequencies as it is used in AD9834 [50]. The range and precision of modulation by FSK and PSK is inherently limited, primarily by the speed of the serial peripheral interface and the accuracy of timing for triggering FSK and PSK registers. This limits the achievable values of the modulation depth so that side-band amplitudes of only about -40 dB are achievable for different modulation frequencies, while the noise level is about -70 dB to -80 dB.

Early attempts to create frequency modulated signals using the methods outlined in the previous paragraph experienced numerous problems in dynamically updating the phase accumulator of commercial DDS boards to generate phase/frequency modulated electric signal so that our efforts resulted in a synchronous FM signal with spurious glitches that could not be removed. Therefore, we designed and manufactured a novel digital FM signal generator that produces electrical FM signal in which the modulation frequency is phase synchronized with the carrier frequency. This has the benefit of phase synchronization in all generated frequencies using an atomic clock. This method uses two DDS chips, one for generating the carrier frequency and the other one for producing the modulation through an analog time-delay circuit. This removes the necessity to update the phase offset word and eliminates the limitation of serial data transfer speed, though the modulation and carrier frequencies are limited by the frequency limits of the

corresponding DDS chips. This FM signal generator also solves another common problem of noise spikes in the generated signals caused by dynamic effects of the register updates. Using this particular method, frequencies of carrier and harmonics are not influenced by the analog circuit variations; however, drifts in the delay circuit frequency will affect relative amplitudes of the harmonics either side of the carrier, i.e. the modulation depth. Since the electrical FM signal is aimed to drive AOMs with 60 and 70 MHz operation frequencies, the manufactured FM signal generator was designed to provide an output frequency band of 1 Hz to 80 MHz. This is achieved by two stages of passive and active low-pass filters at the output of the board outlined in section 3.3.

### 3.2 Principle of operation

### 3.2.1 Modulated clocking of the high bandwidth DDS

DDS microchips comprise a processor that uses a pointer to increment through a Look-Up Table (LUT) to determine values that are sent to a Digital to Analog Converter (DAC) through which the analog signal is generated. Regularly clocking the pointer at equal time intervals as it steps through a LUT of sinewave values results in a digital output equivalent to the function represented in the LUT. Dependent on the values in the LUT and the frequency of the clock, periodic shapes of any function can be produced. Consequently, to produce a sinewave, a DDS is implemented using a reference clock, an address counter, a digital sine LUT, and a DAC. An amplitude word is picked from the sine LUT by the address counter and is sent to the DAC to generate the equivalent analog sinewave. The output frequency depends on the clock frequency and the LUT jumper value set by the user.

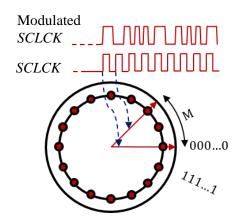

Figure 3-2- Digital Phase Wheel with corresponding normal and modulated clock.

A "phase wheel" representation shown in Figure 3-2 illustrates the DAC transfer process in a DDS. As shown, generation of sinewave oscillation can be visualized as a vector rotating around a circle containing values for the DAC. Each designated point on the phase wheel corresponds to data that transforms to an equivalent point on a cycle of a sinewave. Each revolution of the vector around the phase wheel, at a constant speed, generates one complete cycle of the sinewave the frequency of which is determined by the basic tuning equation

$$f = (M \times CLCK)/(2^{\varrho}). \tag{3-1}$$

where, f is the output frequency; M, the register vector jump size; Q is the bit resolution of the LUT;  $2^Q$  is the number of data-points in the LUT and SCLCK is the system clock frequency inside the DDS. In some DDS microchips, the external clock is first multiplied by an integer value through a multiplier to generate higher frequency clocks for processing the data inside the DDS structure. In such DDS architectures, the SCLCK is the frequency of clock signal after multiplier.

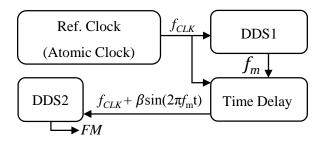

The main idea behind the electrical FM signal generator presented in this study is that a DDS will output frequency/phase modulated sinewave if the phase of its clock signal is dynamically being adjusted. The FM signal generator developed here uses two DDS processors: one for adjusting the phase of the clock signal and the other one for generating the FM signal from the modulated clock. To do this, a voltage-controlled time-delay circuit is adopted to modulate the reference clock frequency before feeding it into the high frequency DDS, DDS2, also indicated in Figure 3-2. Figure 3-3 shows a block diagram indicating the major components of this method. DDS1 is used to generate a sinusoidal voltage that controls the time-delay circuit. Importantly, the clock for both DDS1 and DDS2, are derived from the same source, in our experiments a 10 MHz rubidium oscillator (SRS model PRS10 [61]).

Figure 3-3- Block diagram of the circuit containing the signal path from reference clock to the DDS2.

As seen in Figure 3-3, the reference clock is simultaneously timing both DDS circuits. Being directly timed from the clock source, the DDS1 output signal is used to modulate the reference clock signal via the time-delay sub-circuit. The output of the time-delay circuit is then used as a clock for the DDS2 circuit. Definitions of the mathematical parameters in this figure are discussed in more detail in the following section. To achieve clock speeds suitable for RF generation, the 10 MHz clock signal is multiplied by 20 (or

any integer from 4 to this value) through a Phase Locked Loop (PLL) multiplier within the DDS2 chip. Because the multiplier output, *SCLCK*, follows the phase of the input clock through the PLL, it is assumed that the phase modulations, being substantially slower than the 10 MHz clock signal, will be similarly transmitted.

#### 3.2.2 Theory of Synchronous FM Signal Generation

As shown in Figure 3-2 (page 19), each rising edge of the clock signal triggers the LUT to send a digital value to the DAC through which an analog equivalent is generated. For a constant clocking speed, this results in a perfect sine wave. Under such an assumption, the sine wave at the DDS output is

$$V(t_r) = V_0 \sin(\omega_c t_r) = V_0 \sin(\omega_c r \Delta t_0), \qquad (3-2)$$

where,  $V_0$  is the amplitude of the output signal;  $\omega_c$ , the angular frequency of the signal that is equal to  $2\pi f_c$ ; r, an integer number increasing by each pulse of the SCLCK (i.e. a clock count); and  $\Delta t_0$  is the clock timing interval. For the modulated reference clock, the instantaneous timing interval reads as:

$$\Delta t = \Delta t_0 + \frac{\beta}{r\omega_c} \sin(\omega_m r \Delta t_0), \qquad (3-3)$$

where,  $\omega_m$  is the angular modulation frequency, and  $\beta$  is the modulation depth. Substituting  $\Delta t_0$  in (3-2) with  $\Delta t$  gives

$$V(t_r) = V_0 \sin \left[ \omega_c r \Delta t_0 + \beta \sin \left( \omega_m r \Delta t_0 \right) \right], \tag{3-4}$$

where,  $r\Delta t_0$  is the quantized time approximating to a continuous parameter,  $t_r$ , as  $\Delta t_0$  approaches zero. Equation (3-4) represents an FM signal with corresponding carrier frequency of  $f_c = \omega_c/2\pi$ , modulation frequency of  $f_m = \omega_m/2\pi$ , and modulation depth  $\beta$ . For the purpose of computing frequency content, this FM signal, V(t), can be represented in the complex exponential form:

$$V(t)/V_0 = \sin\left(\omega_c t + \beta \sin\left(\omega_m t\right)\right) = i \left[e^{i(\omega_c t + \beta \sin(\omega_m t))} - e^{-i(\omega_c t + \beta \sin(\omega_m t))}\right]/2.$$

(3-5)

Equation (3-5) can be rewritten in terms of Jacobi-Anger expansions in the form of following series [38, 39]

$$e^{-i\left(\omega_{c}t+\beta\sin\left(\omega_{m}t\right)\right)} = e^{-i\omega_{c}t}J_{0}\left(\beta\right) + \sum_{n=1}^{\infty} \left(\left(-1\right)^{p}e^{-i\left(\omega_{c}-p\omega_{m}\right)t} + e^{-i\left(\omega_{c}+p\omega_{m}\right)t}\right)J_{p}\left(\beta\right),\tag{3-6}$$

$$e^{i(\omega_{c}t+\beta\sin(\omega_{m}t))} = e^{i\omega_{c}t}J_{0}(\beta) + \sum_{p=1}^{\infty} \left(e^{i(\omega_{c}+p\omega_{m})t} + \left(-1\right)^{p} e^{i(\omega_{c}-p\omega_{m})t}\right)J_{p}(\beta), \tag{3-7}$$

If the signal phase is subject to a single modulation frequency, the modulation depth is a constant. Hence the output comprises the original carrier frequency plus an infinite series of sidebands at integer multiples of the modulation frequency. In practice, the number of significant modulation sidebands in the output spectrum is a function of the modulation depth [43, 62]. By taking the Fourier transform of (3-6) and (3-7), a discrete FM output spectrum with magnitude coefficients as a function of  $\beta$  is seen as presented in the equation below.

$$x_{FM} = (V_0/2) \times \sum_{n=0}^{\infty} J_p(\beta) \delta(f - (f_c \pm pf_m)), \tag{3-8}$$

where,  $\delta(-)$  is the Dirac delta.

# 3.3 Modulator Circuit Design

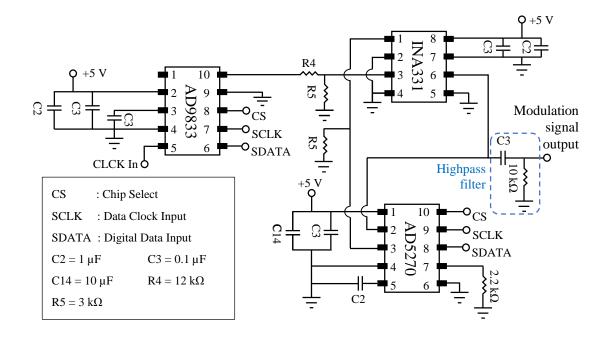

As stated, the modulation process requires a voltage-controlled time-delay circuit to generate controlled delays in the phase of a sinusoidal signal from a 10 MHz oscillator that is subsequently used to time a high frequency DDS circuit. The controlling voltage signal, which acts to modulate the time delay, is generated by a second DDS that is synchronously timed by the same, but unmodulated, 10 MHz carrier signal. Both the carrier and modulation harmonics are consequently timed by the same clock signal. The time-delay circuit is shown in Figure 3-4. This consists of a wide bandwidth JFET input operational amplifier model LF353 [63], an ultrafast precision comparator model LT1016 [64], and a retriggerable mono-stable multi-vibrator model SN74LS123 [65].

Figure 3-4- Details of the phase delay circuit in conjunction with major blocks of other DDS1 and DDS2 circuits.

The modulation signal coming from DDS1 is amplified to the desired amplitude and then applied to the voltage-controlled delay. There is a buffer between the DDS1 and the comparator of the time-delay circuit to eliminate possible loading effects due to

impedance mismatch between them. The harmonically varying delay results in a dynamic shift in the reference clock going into the comparator. The net result of this is to produce a voltage-controlled pulse width generator where the pulse width is proportional to the modulation voltage from the DDS1. Finally, the output signal of the comparator is used to trigger the multi-vibrator. Since the commercial atomic clocks typically generate 10 MHz signal, the phase delay is designed to be linear with input voltage at this frequency.

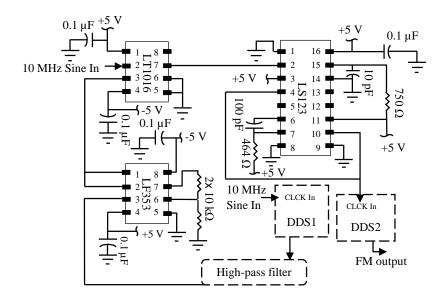

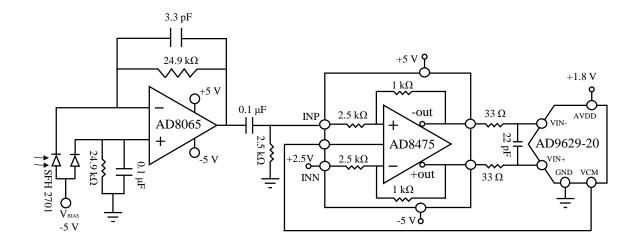

Figure 3-5- Schematic of the DDS1 circuit with a digital amplitude control.

The DDS1 circuit is shown in Figure 3-5. In the first prototype of the FM board, a potentiometer was used to control the amplitude of the modulation signal,  $V_m$ . This potentiometer was replaced with a digital rheostat, model AD5270 [66], to provide full-digital control over all the characteristics of the generated FM signal, see Figure 3-5. Due to the linear relationship between the delay generated in the time-delay circuit and  $V_m$ , this will subsequently control the modulation depth,  $\beta$ , equation (3.3). The modulation

depth changes the energy distribution among the sidebands of the FM signal. This can be observed in the frequency content and relative side-band amplitudes based on Jacobi-Anger expansion. The high-pass filter between DDS1 and the time-delay circuit, shown in Figure 3-4, is a simple first-order RC filter located at the output of the DDS1 circuit in Figure 3-5. This filter eliminates the DC offset at the output of the DDS1 circuit so as to make it compatible with the input voltage range of the time-delay circuit as it is discussed in the testing section of the sub-circuits of the board. This also provides an AC-couples modulation signal that is compatible with the reference inputs of lock-in amplifiers.

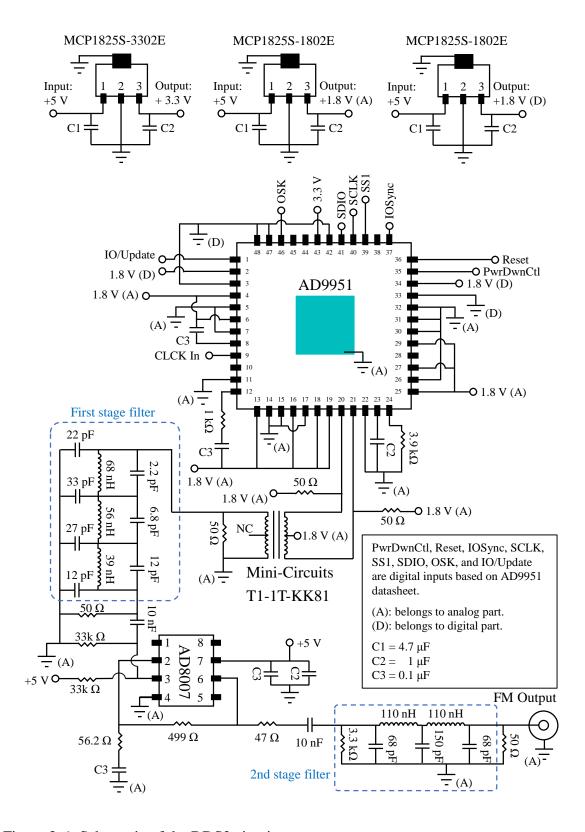

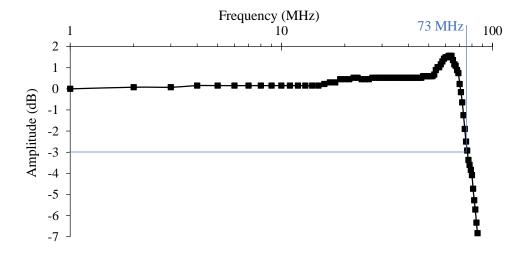

The DDS2 circuit is shown in Figure 3-6. The DDS2 chip, AD9951, requires two separate 1.8 V supplies for analog and digital parts that were provided by small surface-mount, fixed-voltage regulators, model MCP1825S, made by Microchip Technology Inc [67]. Acceptable signal qualities were achieved by a two-layer board with separate digital and analog ground plates, and separate power supplies via fixed-voltage regulators. To decrease the noise in the circuit, the impedance of the traces used in the Printed Circuit Board (PCB) is matched to the required impedance for VHF signals (50  $\Omega$ ). To further eliminate impedance mismatching that can attenuate and distort the signal and introduce noise, SubMiniature version A (SMA) connectors are used. For the best spectral purity possible, two stages of filtering are included on the output of the DDS2 circuit, shown in Figure 3-6. The first stage is a shunt-connected, 7th order, elliptic low-pass filter with a cutoff frequency of 160 MHz with component values based on a commercial DDS2 evaluation board [68]. The second stage of filtering is a  $\pi$  configuration, 5-pole, Butterworth low-pass filter with a cutoff frequency of 73 MHz [69].

Figure 3-6- Schematic of the DDS2 circuit.

# 3.4 FM signal generator testing and results

# 3.4.1 Experimental apparatus and test procedure

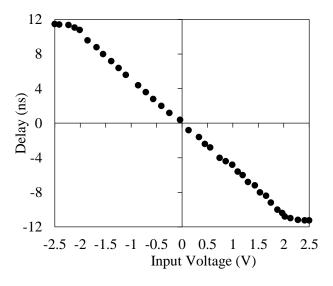

Since the modulator combines three main circuits of DDS1, time-delay, and DDS2 circuits, prior to evaluating the complete modulator, it is necessary to evaluate the performance of each of these individual sub-circuits. To determine time delay as a function of the input voltage, the DDS1 was bypassed and a DC voltage applied to pin 3 of the LF353 microchip shown in Figure 3-4. With a 10 MHz signal going into the circuit, the delay through the comparator versus different voltages was measured using an oscilloscope, see Figure 3-7. As observed in Figure 3-7, the generated delay varies linearly with the input voltage. Furthermore, it is seen that the delay circuit becomes nonlinear for input-voltages outside the range -2 V to 2 V, thereby limiting the amplitude of the modulation signal generated by DDS1. Over this range the response of the time delay circuit is -5.207 ns.V-1 with a coefficient of determination of 0.9994.

Figure 3-7 Variation of the generated delay from the LT1016 comparator as a function of the voltage applied to the LF353 amplifier.

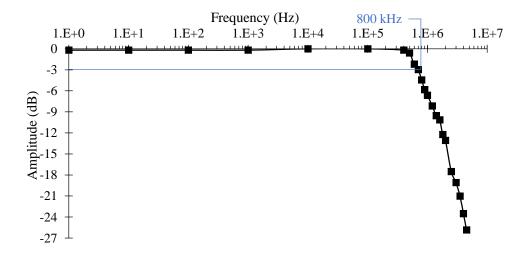

The amplitude frequency responses of the DDS1 and DDS2 circuits as they are clocked by constant 10 MHz signal are shown in Figure 3-8 and Figure 3-9, respectively. The magnitude of DDS1 output attenuates at frequencies greater than 1 MHz. It also has a DC offset of about 2V. To eliminate this DC offset, a high-pass filter with a cutoff frequency of 1 kHz is used at its output, as shown in Figure 3-5. The two stages of low pass filters shown in Figure 3-6 provide a cut-off frequency of about 73 MHz. This cut-off frequency is shown in Figure 3-9.

Figure 3-8- Frequency response of the DDS1 circuit over a 2 MHz band.

Figure 3-9- Frequency response of the DDS2 circuit from 1 to 80 MHz.

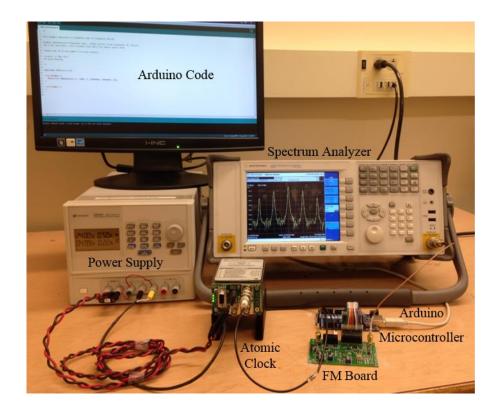

# 3.4.2 Performance tests on first prototype of FM board

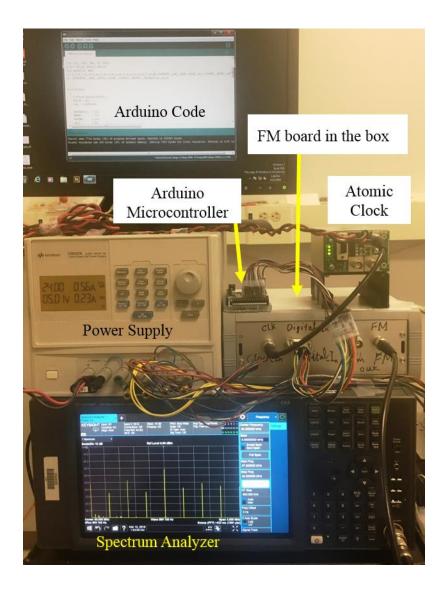

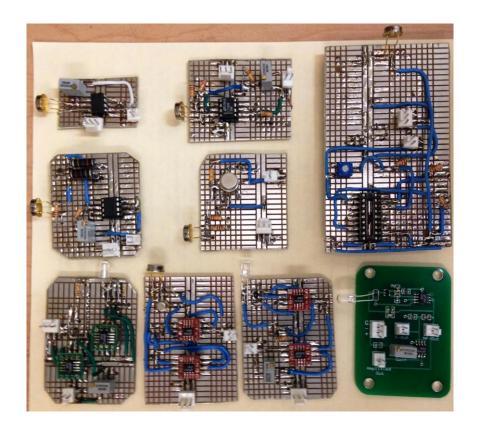

Having designed and implemented the FM circuit, see Figure 3-10, an experiment was set up using an Arduino Mega<sup>™</sup> microcontroller to program the microchips, and a rubidium oscillator (SRS model PRS10) for the clock, see Figure 3-11. This rubidium frequency standard provides a low phase noise of <-130 dBc/Hz at 10 MHz and a short-term stability of <2×10<sup>-11</sup> s. Because this provides the clock signal for both DDS chips, the frequency components of all generated FM signals are synchronized to this reference. The frequency components of the FM signals are measured using a spectrum analyzer (Agilent CSA model N1996A-506). This analyzer has a frequency range up to 6 GHz with resolutions settable from 10 Hz to 5 MHz. The Arduino code used for controlling the DDS microchips are listed in APPENDIX A.

Figure 3-10- First prototype of the FM board.

The FM board shown in Figure 3-10 has only one high-pass filter between the atomic clock and the clock input of the board without any non-inverting amplifier. It also uses a potentiometer instead of a digital rheostat. Furthermore, this board uses a power regulator at its power input section to generate ±5 V DC lines from the supplied 5 V DC power. These are the main differences between this first prototype of the FM board and the final prototype which is presented in the next section. The reason for modifying the first prototype of the board to implement the final prototype is presented hereinafter.

Figure 3-11- Experimental setup to test the first prototype FM signal generator performance.

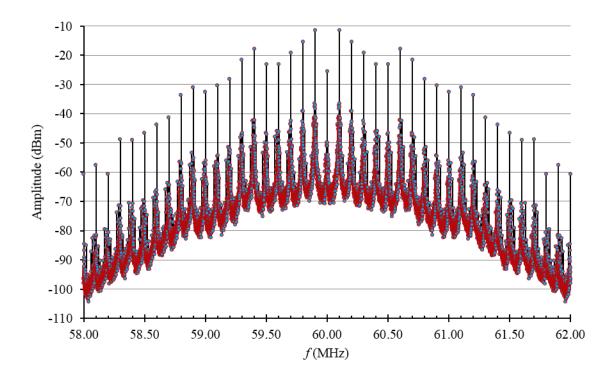

Two samples of frequency spectra of the generated FM signals by the first prototype FM board are shown in Figure 3-12 and Figure 3-13. As seen in these figures, there is an instability in the distribution of energy in the harmonics of the modulation frequency so that the noise level is about -50 dBm.

Figure 3-12- Frequency spectrum of FM signal of  $f_c = 60$  MHz and  $f_m = 100$  kHz generated by the first prototype board.

Figure 3-13- Frequency spectrum of FM signal of  $f_c = 60$  MHz and  $f_m = 250$  kHz generated by the first prototype board.

The tests performed on the board revealed that this instability is due to loading of both the comparator and the DDS1 clock input. To solve this issue, a non-inverting amplifier was used between the atomic clock output and the clock input port of the board. Also, to protect the atomic clock from signals reflecting from the modulator, a buffer was added between the DDS1 clock input and the atomic clock output. These modifications were implemented in the final prototype of the board presented in the next section.

# 3.4.3 Final prototype FM board

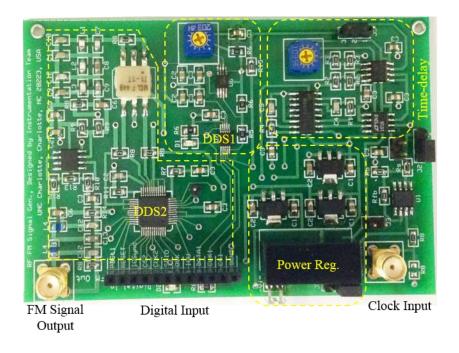

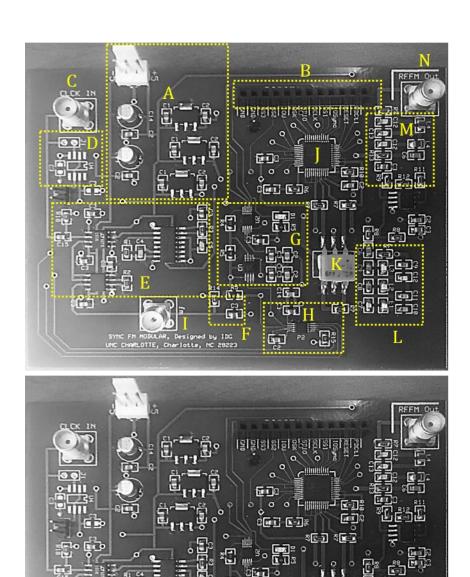

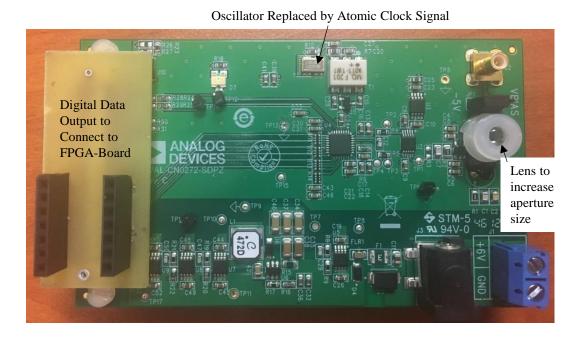

The final prototype of the FM board is shown in Figure 3-14. Since the ground plate of the clock line buffer was the same as the DDS sub-circuits analog ground, it was adding substantial noise to the signal. To solve this issue, the buffer was separated from the PCB as shown in Figure 3-15. The adjustable gain non-inverting amplifier provides control on the amplitude of the clock signal to set it to the required level for the DDS1. Experiments showed that these are the necessary circuits between the atomic clock and the FM board input to achieve the highest signal-to-noise ratio without loading the atomic clock. To test the spectral purity and precision of the frequency components of the final prototyped FM board, the experiment shown in Figure 3-11 was set up for this new board, see also Figure 3-16. A CXA signal analyzer model N9000B (9 kHz – 7.5 GHz) is used in this experiment and the resolution is set to 1 Hz for all the spectra presented in this chapter, except for those that are mentioned specifically.

Figure 3-14- Photograph of the final prototype PCB with different sub-circuits components; A) power input and regulators, B) digital input, C) clock input, D) omitted clock-line buffer layout, E) time-delay, F) high-pass filter, G) DDS1 circuit, H) digital rheostat to control modulation signal amplitude, I) modulation signal output, J) DDS2, K) transformer, L) low-pass filter with 160 MHz cutoff, M) low-pass filter with 75 MHz cutoff, N) FM output.

SYNC FM MODULAR, Designed by IDC UNC CHARLOTTE, Charlotte, NC 20223

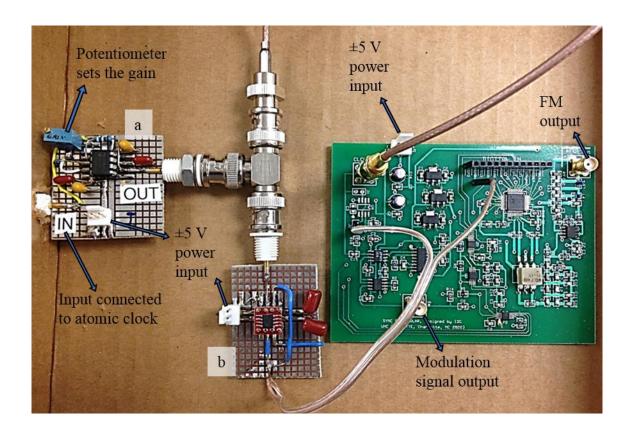

Figure 3-15- The FM board with separated buffers in the clock line; a) non-inverting adjustable gain amplifier; b) buffer between DDS1 and clock line.

There are three parameters in the final prototyped FM signal generator that can be varied, these being the modulation depth  $\beta$  (which is a linear function of  $V_m$ ), the carrier frequency  $f_c$  and the modulation frequency  $f_m$ . To study the effects of  $\beta$  on the shape of the spectra,  $V_m$  is changed by setting different values of resistance for the digital rheostat in the last version board—that is identical to the manual potentiometer in the first version board—and the spectra captured for a variety of carrier and modulation frequencies.

Figure 3-16- Experimental setup to test the final prototype FM signal generator performance.

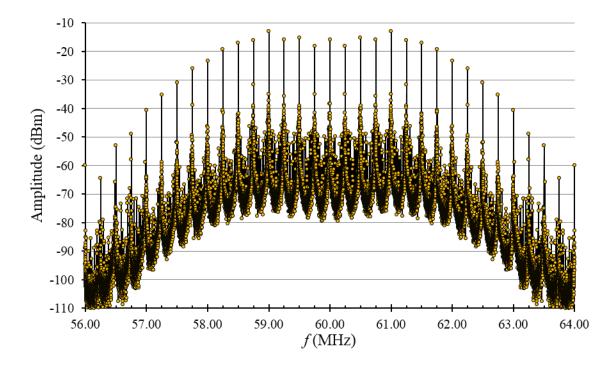

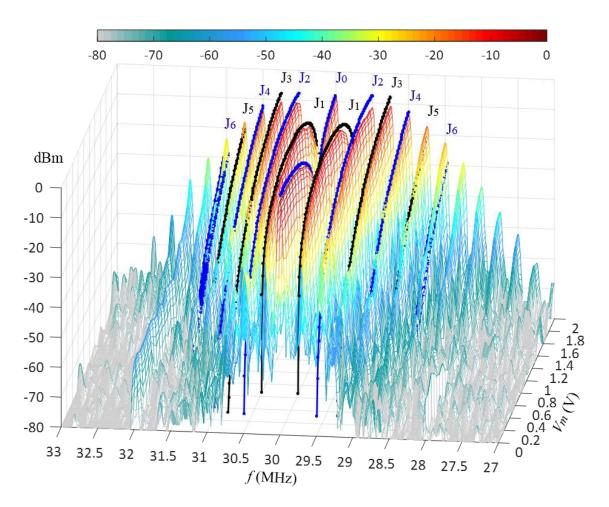

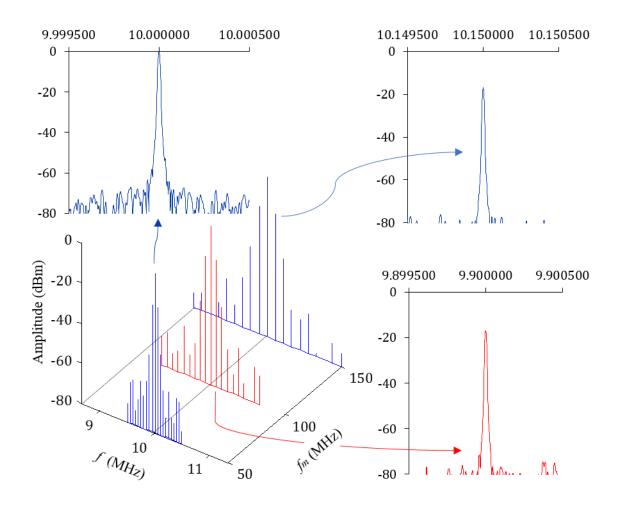

The frequency spectra of signals with  $f_c=30\,$  MHz,  $f_m=250\,$  kHz, and various  $V_m$  values are plotted in Figure 3-17 and Figure 3-18. For the data presented in these figures, the resolution of the spectrum analyzer was set to 100 Hz and frequency components of the spectra spanning 27 to 33 MHz with frequency steps of 6 kHz were captured. The reason for setting the resolution higher than 10 Hz, which is the finest possible resolution in the Agilent CSA spectrum analyzer used in this study, is to

generate more visible (broader) sidebands for visualization in these 3D figures. The lines plotted on top of the sidebands if Figure 3-17 represent the absolute value of Bessel function of first kind of integer orders -6 to 6 at the same decibel magnitude (dBm) scale used in 3D spectra. To further illustrate the Bessel function dependence of amplitude with modulation depth, the absolute values of Bessel functions of the first kind for integer orders of 0 to 8 are compared with the sidebands magnitudes in Figure 3-18.

Figure 3-17- Measured frequency spectra of signals of  $f_c = 30$  MHz and  $f_m = 250$  kHz with varying  $\beta(0-3.7)$  indicated by  $V_m(0-2)$ , compared with modulation amplitude resulted from Jacobi-Anger expansion.

Figure 3-18- Measured frequency spectra of signals with  $f_c=30\,$  MHz and  $f_m=250\,$  kHz with varying  $V_m$  values of 0 to 2 V compared with the absolute value of Bessel functions of first kind,  $J_i(\beta)$ , for  $i=0,1,\ldots,8$  in a dBm scale.

As seen in Figure 3-17 and Figure 3-18, the generated signals are consistent with the characteristic predicted by the Jacobi-Anger expansion for the relationship between

$\beta$  and  $V_m$ . The same behavior was observed for signals with other  $f_c$  and  $f_m$  values ranging from 10 MHz to 70 MHz and 10 kHz to 300 kHz, respectively.

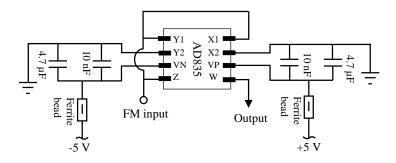

Figure 3-19- Schematic of the mixer, AD835, circuit.

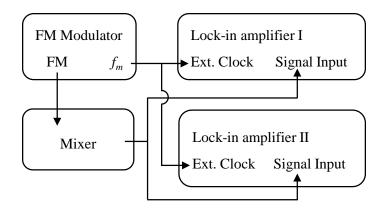

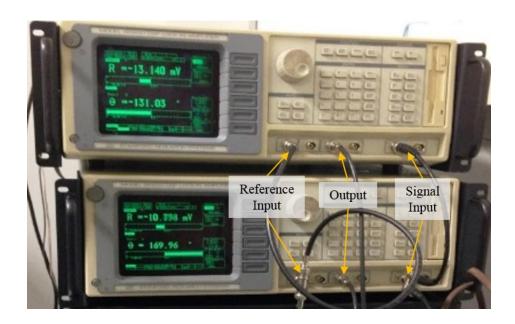

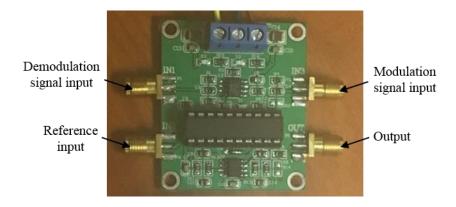

Theoretically, successive modulation frequency harmonics have alternating parity with respect to the carrier of the FM signal, i.e. successive sidebands should have  $90^{\circ}$  phase difference. To evaluate this phase difference, a mixer (AD835) [70] with two lock-in amplifiers (SRS model SR850) were used to detect the phase difference between the sidebands. Schematic diagrams of the AD835 mixer is shown in Figure 3-19 and the experimental setup to measure the phase difference between different harmonics of  $f_m$  is shown in Figure 3-20. Both lock-in amplifiers were externally referenced by locking to the  $f_m$  output of the FM board. One of the lock-in amplifiers is locked to the first harmonic at  $f_m$  and the other to the second harmonic at  $2f_m$ . The phase difference between these harmonics was measured for different  $f_m$  values. The DSP lock-in amplifiers used here can measure any of the first to the tenth harmonics of the reference signal as long as the frequency is smaller than 100 kHz. Therefore, this measurement was limited to  $f_m < 50$  kHz.

Figure 3-20- Schematic diagram of the experimental setup for measuring the phase difference between odd and even sidebands.

Table 3-1- Measured phase differences between sidebands.

| $f_m$ (kHz) | Harmonic I phase (deg.) | Harmonic II<br>phase (deg.) | Phase difference (deg.) |

|-------------|-------------------------|-----------------------------|-------------------------|

| 10          | -8.31                   | 83.39                       | 91.7                    |

| 20          | 0.48                    | 86.88                       | 87.36                   |

| 30          | 3.48                    | 91.46                       | 87.98                   |

| 30          | 3.09                    | 91.20                       | 88.11                   |

| 30          | 2.63                    | 95.94                       | 93.31                   |

| 35          | 3.2                     | 92.71                       | 89.51                   |

| 40          | 2.87                    | 89.71                       | 86.84                   |

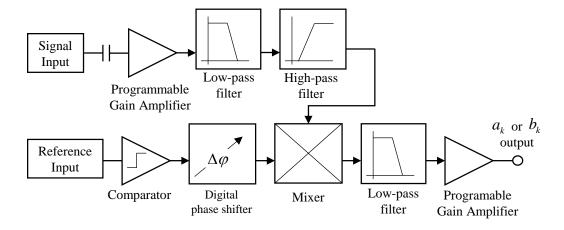

| 50          | -8.41                   | 78.25                       | 86.66                   |