## AN INTEGRATED CIRCUIT WITH SINGLE FUNCTIONAL UNIT LEVEL INTEGRATION OF ELECTRONIC AND PHOTONIC ELEMENTS: DESIGN OF THE FET - LET HYBRID 6T SRAM AND THE ELEMENTS

by

Antardipan Pal

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2022

Approved by:

Dr. Yong Zhang

Dr. Mohamad-Ali Hasan

Dr. Jeremy Holleman

Dr. Yasin Raja

©2022 Antardipan Pal ALL RIGHTS RESERVED

## ABSTRACT

## ANTARDIPAN PAL. An Integrated Circuit With Single Functional Unit Level Integration Of Electronic And Photonic Elements: Design Of The FET - LET Hybrid 6T SRAM And The Elements (Under the direction of DR. YONG ZHANG)

Continuous scaling of complementary metal-oxide-semiconductor (CMOS) transistor technology over the past few decades following Moore's law has led to significant enhancement in the speed and performance of computing architectures. In today's world with high demand in data processing, CMOS scaling is focusing more on low power, cost-effective processes, and high performance to meet the requirements of high-end computations. To meet the high computation demands, reengineered, high performance, and low power device structures were necessary, and hence field effect transistors (FET) structures have evolved from planner to multi-gate, and gate all around (GAA) structures. Also, other than the very well matured silicon electronics, advanced technologies allowing heterogeneous integration of different materials systems (e.g., Si, Ge, III–V, and II-VI groups) have been developed. Though heterogeneous integration of silicon electronics with compound semiconductors can be beneficial, such developments in hybrid integration cannot address the fundamental limitations of the pure CMOS circuits, the resistive capacitive (RC) delay associated with metallic wires, and the dielectric gate delay associated with FETs. These delays ultimately limit the data speed and energy consumption.

In this research work we have explored novel applications in electronic-photonic integrated circuits of a special type of metal-semiconductor-metal (MSM) photoconductive structure known as the light effect transistor (LET) which can emulate the current voltage characteristics of a FET but with much better performances in terms of switching speed (considering carrier transit delay), energy consumption per switch and  $I_{on}/I_{off}$  ratio, and also other optoelectronic functions like optical

logic gates, optical summation, optical amplification, and optoelectronic analog operation using LETs, which cannot be done using FETs. The LET can provide extremely fast optoelectronic switching (of the order of  $\sim$  ps), and its simplistic structure does-not add unwanted parasitic and leakages which are common in all gated FETs.

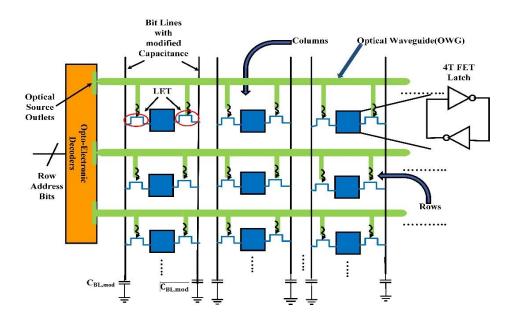

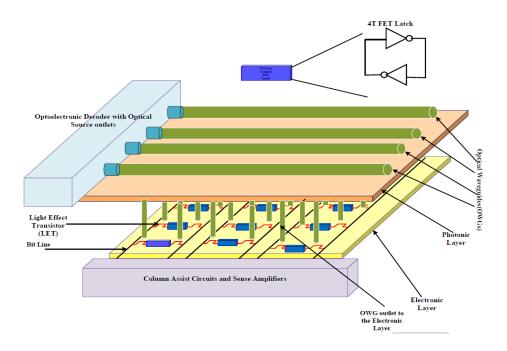

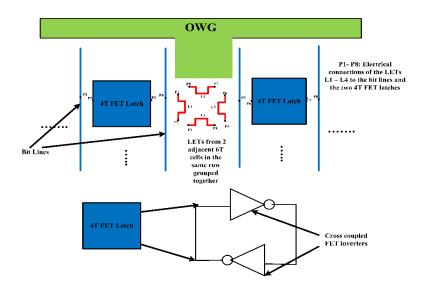

To understand the superiority of LETs over FETs, particularly the potential vast performance improvement in a hybrid integrated circuit of the two types of devices, we have explored the possibilities of LETs to replace some FETs in various pure electronic circuits. Using analytical relations and simulations, we have extensively studied the effect of replacing the access FETs in a 6T SRAM (six transistor static random-access memory) structure with LETs and have made some drastic changes in the hybrid 6T FET - LET structure by replacing the whole electrical wordline with an optical waveguide (OWG). We have also proposed a prototype novel hybrid 3D integration scheme for the 6T SRAM architecture where all the typical electronic and optoelectronic components (4T FET latch, access LETs, bit lines, peripherals, etc.) will be placed on a single electronic layer while photonic layer with regularly spaced openings that provide the optical signal for switching four LETs grouped together from two adjacent hybrid 6T cells in the electronic layer. Also, a fully functional FET - LET hybrid SRAM bit cell with superior performance has been designed and implemented using the *mixed-mode* design environment of Synopsys Sentaurus TCAD.

# DEDICATION

To my father and my uncle, in their loving memory.

#### ACKNOWLEDGEMENTS

I would like to express my heartfelt gratitude and sincerely thank to my advisor, Dr. Yong Zhang for his continuous and undiminished support throughout my research. His constant motivation, enthusiasm, and guidance helped me significantly in developing logical and reasoning capabilities that are critical for research. Also, many thanks to Dr. Zhang for supporting me financially with research assistantships. Without his support, this work would not have been possible.

Along with Dr. Zhang, I would like to sincerely thank the ECE department and the department of Physics and Optical Science, for providing me with the necessary infrastructure and necessary software required for my research work. I would also like to extend my heartiest appreciation to my colleagues Jose and Tang for their support. I would like to express my sincere gratitude and thanks to my committee members, Dr. Jeremy Holleman, Dr. Mohamad-Ali Hasan, and Dr. Yasin Raja for their continuous encouragement. Also special thanks to Dr. Holleman, and Dr. Hasan for their valuable comments and suggestions during the research aptitude test which have helped me a lot to progress this research. I am very grateful to Mr. Dennis D. Yau for providing invaluable suggestions and comments on the published paper and this work in general.

Special thanks to Dr. Yasin Raja for agreeing to preside over my research as an external committee member. I would opportunity to express my gratitude to the ECE department of UNC Charlotte, for providing me with the opportunity to pursue my Ph.D., for assisting me financially with GASP and assistantships, and for allowing me to use the lab and research facilities in the department. Finally, I would like to thank my family, especially my late father for standing by me through all the good and tough times.

# TABLE OF CONTENTS

| LIST OF FIGURES                                             | ix   |

|-------------------------------------------------------------|------|

| LIST OF TABLES                                              | xiii |

| CHAPTER 1: Introduction                                     | 1    |

| 1.1 Motivation                                              | 1    |

| 1.2 Objective                                               | 4    |

| CHAPTER 2: Optoelectronic Devices                           | 6    |

| 2.1. Overview                                               | 6    |

| 2.2. Nanowire Photodetectors                                | 7    |

| 2.3. Working Mechanism and Carrier Transport                | 9    |

| CHAPTER 3: Light Effect Transistor                          | 13   |

| 3.1. Device Overview and Comparison with FETs               | 13   |

| 3.2. LET Device Characterization                            | 15   |

| 3.2.1. Estimation of LET Parameters                         | 17   |

| 3.2.2. TCAD Modelling of the FET and LET Devices            | 20   |

| 3.3 Conclusion                                              | 31   |

| CHAPTER 4: Conventional and Hybrid 6T SRAM                  | 33   |

| 4.1. Survey of SRAMs                                        | 33   |

| 4.2. 6T SRAM                                                | 37   |

| 4.2.1 Working Mechanism                                     | 37   |

| 4.2.2 Delay and Energy Estimation of 6T SRAM Array          | 39   |

| 4.2.3. Peripheral and Assist Circuits in the SRAM Array     | 42   |

| 4.3 6T Hybrid SRAM                                          | 44   |

| 4.3.1. Delay and Energy Estimation of the Hybrid SRAM Array | 46   |

| 4.3.2. Performance Evaluation of the Hybrid SRAM Array                                                    | 48  |

|-----------------------------------------------------------------------------------------------------------|-----|

| 4.3.3. Probable Effects on the Peripherals                                                                | 57  |

| 4.3.4. Leakage and Possible Improvements                                                                  | 59  |

| 4.3.5. Proposal of a Novel Integration Scheme for the Hybrid 6T SRAM Array                                | 64  |

| 4.3.6. Compatibility with CMOS and Scalability                                                            | 67  |

| 4.4. Conclusion                                                                                           | 69  |

| CHAPTER 5: Design of a Low Loss Optical Waveguide                                                         | 70  |

| 5.1. On Chip Electronic Photonic Integration                                                              | 70  |

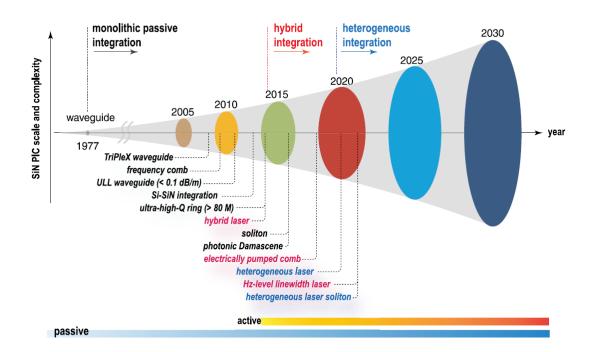

| 5.2. Silicon Nitride Waveguides for Silicon Photonic Integrated Circuits                                  | 73  |

| 5.3. Design and Simulation of Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> Low Loss Optical Waveguide | 77  |

| 5.3.1. Simulation of the $Si_3N_4/SiO_2$ OWG                                                              | 83  |

| 5.3.2. Analyzing the Waveguide Design                                                                     | 89  |

| 5.4. Conclusion                                                                                           | 94  |

| CHAPTER 6: Design of a Fully Functional Hybrid FET-LET 6T SRAM Bit Cell                                   | 96  |

| 6.1. Noise Margins in 6T SRAM Cells                                                                       | 96  |

| 6.1.1. Measuring SNMs in 6T SRAM Cells                                                                    | 97  |

| 6.1.2. Analytical Calculation of the SNM in Regular 6T Cells                                              | 100 |

| 6.2. Mixed Mode TCAD simulation of Regular and Hybrid 6T Cells                                            | 102 |

| 6.3. Analyzing the Results and SNM Variation in the Hybrid 6T Cell                                        | 106 |

| 6.4. Conclusion                                                                                           | 110 |

| <b>CHAPTER 7:</b> Conclusion and Future Possibilities                                                     | 111 |

| 7.1 Conclusion                                                                                            | 111 |

| 7.2 Future Directions                                                                                     | 112 |

| 7.3. Publications                                                                                         | 113 |

| REFERENCES                                                                                                | 115 |

# LIST OF FIGURES

| FIGURE 1.1: Signal flow path in an Electronic-Photonic Integrated Circuit                              | 1  |

|--------------------------------------------------------------------------------------------------------|----|

| FIGURE 2.1: SOI-based chip-level optical interconnect module with lasers and                           | 7  |

| photodetectors using 3-D guided-wave path for multi-core processor or memory-to-processor              |    |

| interface.                                                                                             |    |

| FIGURE 3.1: A Light Effect Transistor (LET).                                                           | 14 |

| FIGURE 3.2: Output and transfer characteristics of a prototype LET based on                            | 16 |

| a CdSe nanowire.                                                                                       |    |

| FIGURE 3.3: Typical file structure and design flow in Synopsys Sentaurus TCAD.                         | 21 |

| FIGURE 3.4: Schematic of a FinFET showing the different regions and interfaces.                        | 21 |

| FIGURE 3.5: Simulated meshing structure of the FinFET in Synopsys TCAD.                                | 22 |

| FIGURE 3.6: Simulated current density in various regions of the FinFET.                                | 23 |

| FIGURE 3.7: Simulated $I_d - V_g$ and $I_d - V_{ds}$ plots for the FinFET.                             | 25 |

| FIGURE 3.8: Simulated meshing structure of the LET in Synopsys TCAD.                                   | 26 |

| FIGURE 3.9: Simulated current density of the LET in Synopsys TCAD                                      | 26 |

| FIGURE 3.10: Simulated output characteristics $(I_d - V_{ds})$ of the LET, g in /cm <sup>3</sup> /sec. | 27 |

| FIGURE 3.11: Simulated transfer characteristics of the LET, both axes in log scale,                    | 28 |

| and only $I_d$ in log scale.                                                                           |    |

| FIGURE 3.12: Simulated output characteristics $(I_d - V_{ds})$ of the ballistic LET.                   | 29 |

| FIGURE 3.13: Simulated transfer characteristics of the ballistic LET,                                  | 29 |

| both axes in log scale, and only $I_d$ in log scale.                                                   |    |

| FIGURE 3.14: Gain vs optical generation ( $P_g$ ) for a regular LET.                                   | 30 |

| FIGURE 4.1: Memory levels in a processor showing the memory bandwidth and latency.                     | 34 |

| FIGURE 4.2: A conventional 6T SRAM cell.                                                               | 37 |

| FIGURE 4.3: 6T SRAM cell showing the read operation and write operation.                               | 38 |

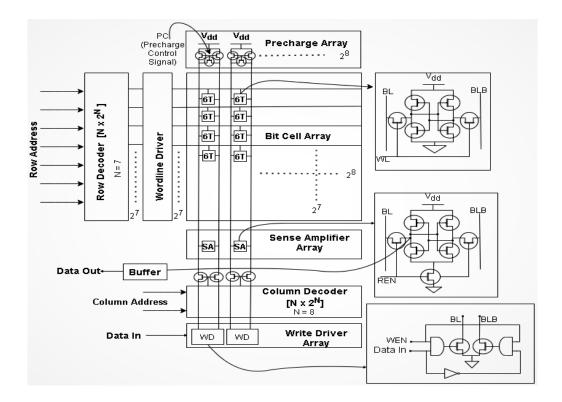

| FIGURE 4.4: A conventional 6T SRAM array.                                                              | 40 |

| FIGURE 4.5: A 6T SRAM array with all the peripherals.                                                  | 42 |

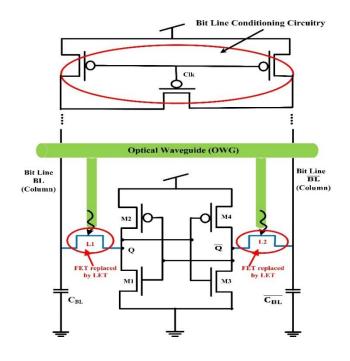

| FIGURE 4.6: Prototype hybrid 6T SRAM cell with LET access.                                             | 45 |

| FIGURE 4.7: Prototype hybrid 6T SRAM array.                                                            | 45 |

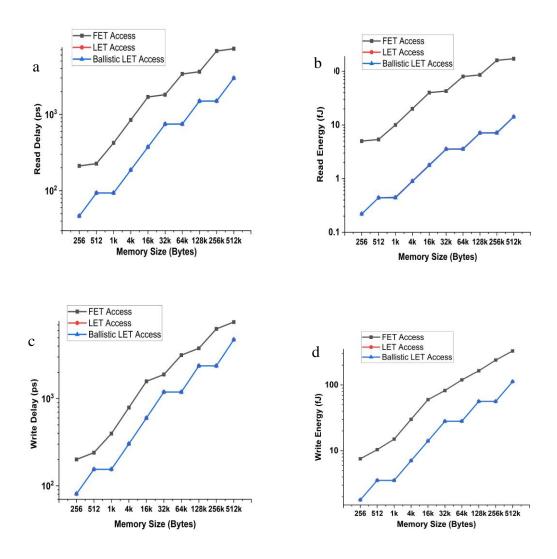

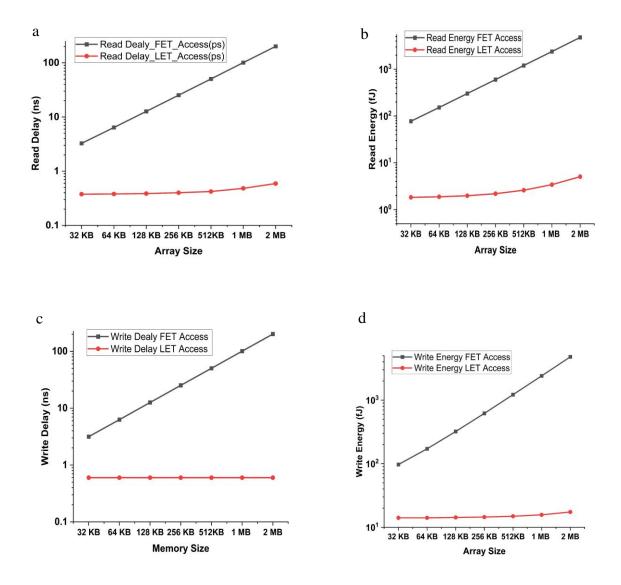

| FIGURE 4.8: Read and write delay and energy for various SRAM arrays with FET, LET,                     | 50 |

| and ballistic LET access devices.                                                                      |    |

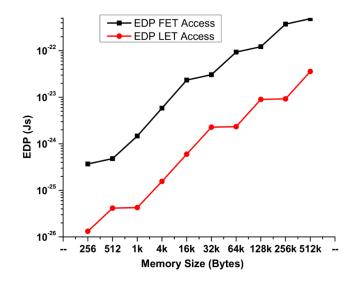

| FIGURE 4.9: EDP for various SRAM arrays with FET, and LET access devices.               | 53 |

|-----------------------------------------------------------------------------------------|----|

| FIGURE 4.10: Read and write delay and energy for various SRAM arrays with FET,          | 56 |

| LET access devices and a maximum of 512 cells/bit line.                                 |    |

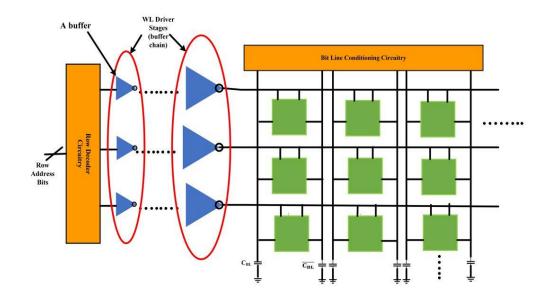

| FIGURE 4.11: Conventional 6T SRAM array with word line driver buffers.                  | 58 |

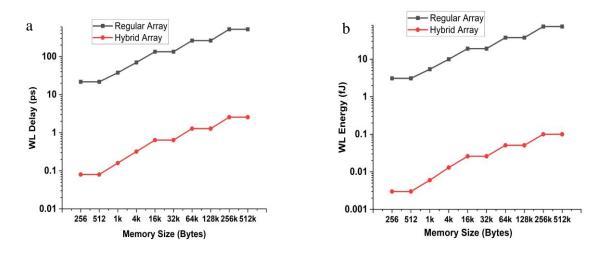

| FIGURE 4.12: Word line delay energy for the regular array and the hybrid SRAM array     | 59 |

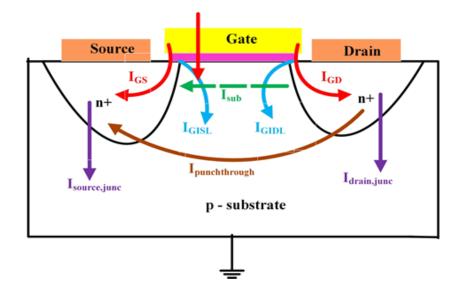

| FIGURE 4.13: Leakage mechanism in a MOSFET.                                             | 60 |

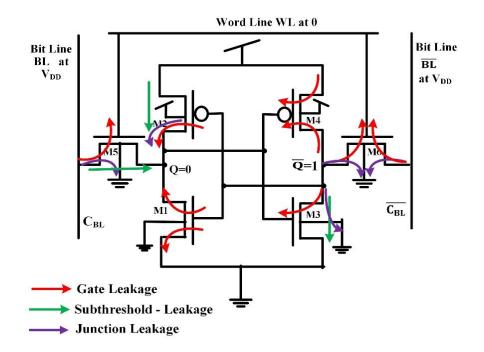

| FIGURE 4.14: Leakage currents in a conventional 6T cell just prior to a read or         | 61 |

| write operation.                                                                        |    |

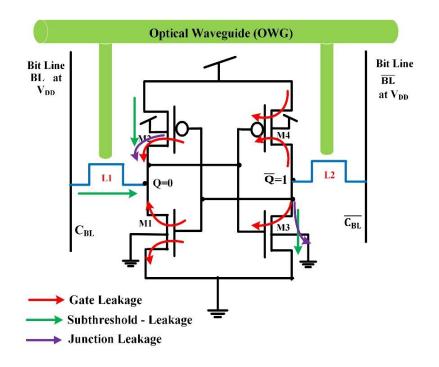

| FIGURE 4.15: Leakage currents in a hybrid 6T cell just prior to read or write operation | 63 |

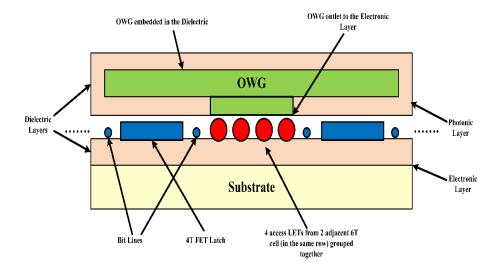

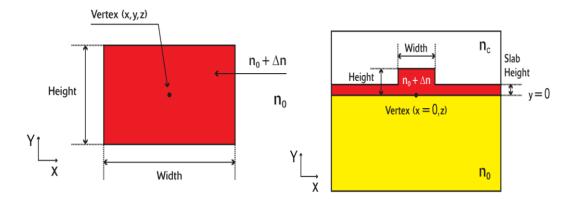

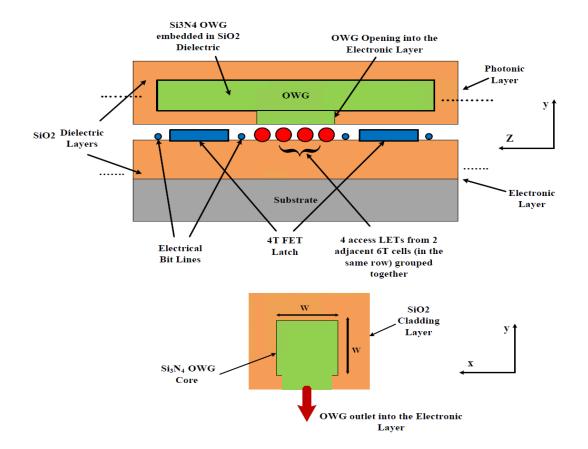

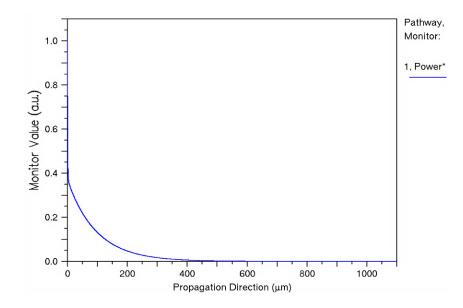

| FIGURE 4.16: A prototype 3D integration scheme for the FET-LET                          | 66 |

| hybrid 6T SRAM array.                                                                   |    |

| FIGURE 4.17: A 2D schematic of the hybrid 6T array layout with 4 LETs                   | 66 |

| grouped together and illuminated for a single OWG opening.                              |    |

| FIGURE 4.18: A cross sectional view of the novel integration scheme showing the         | 67 |

| electronic and photonic layers and the 4 LETs grouped together.                         |    |

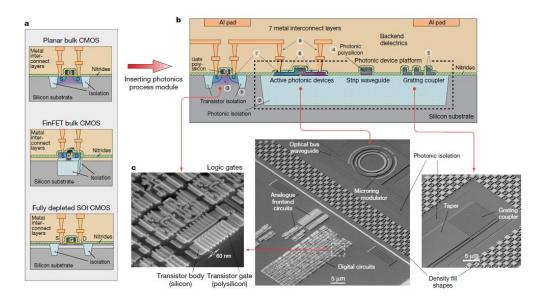

| FIGURE 5.1: Integration of a photonics process module into planar bulk CMOS             | 72 |

| with photonic devices implemented in an optimized polysilicon film.                     |    |

| FIGURE 5.2: Progress of silicon nitride-based photonic integration with key             | 74 |

| demonstrations labeled with the release year.                                           |    |

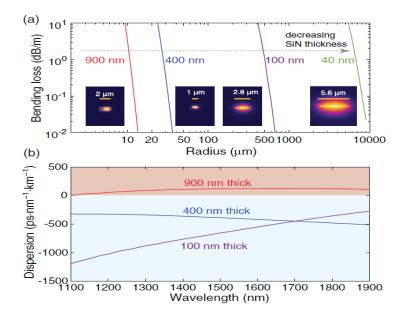

| FIGURE 5.3: $Si_3N_4$ waveguide bending loss versus bending radius and waveguide        | 75 |

| dispersion.                                                                             |    |

| FIGURE 5.4: Bend radii, propagation loss, and window of transparency for $Si_3N_4$ ,    | 76 |

| SOI, and InP waveguides.                                                                |    |

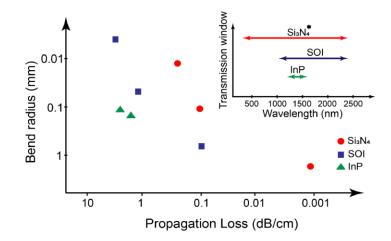

| FIGURE 5.5: Channel type and rib ridge type OWG cross section structure                 | 78 |

| in Synopsys RSoft CAD.                                                                  |    |

| FIGURE 5.6: 2D schematic of portion of the hybrid 6T array layout showing               | 81 |

| minimum distance required between two adjacent OWG openings.                            |    |

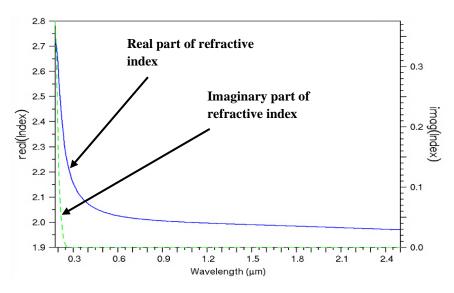

| FIGURE 5.7: Refractive index profile (real and imaginary) of $Si_3N_4$ with variation   | 81 |

| of optical wavelength.                                                                  |    |

|                                                                                         |    |

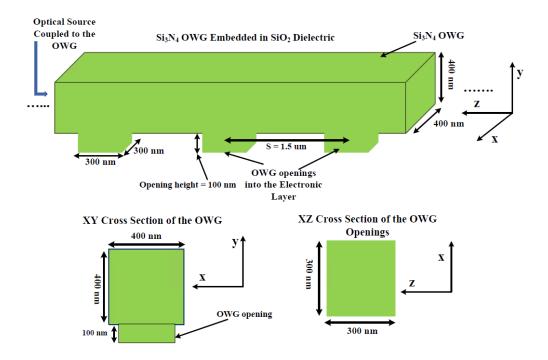

| FIGURE 5.8: 3D schematic of the OWG structure showing the cross section and                   | 82 |

|-----------------------------------------------------------------------------------------------|----|

| the openings (not drawn to scale) perpendicular to the direction of light injection.          |    |

| FIGURE 5.9: The YZ and XY cross sections of the hybrid structure showing the SiO <sub>2</sub> |    |

| encapsulating the $Si_3N_4$ OWG.                                                              | 83 |

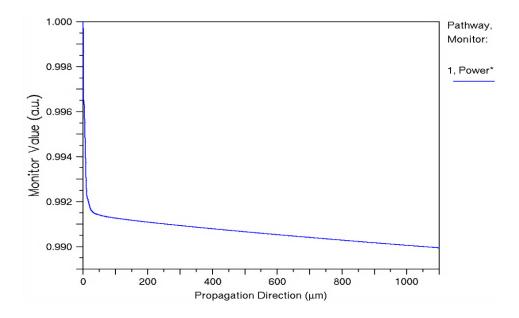

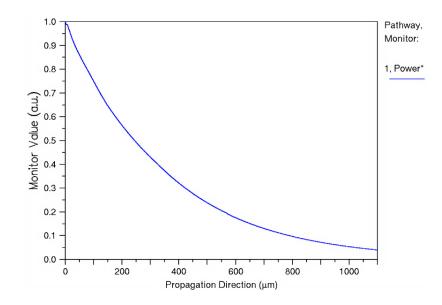

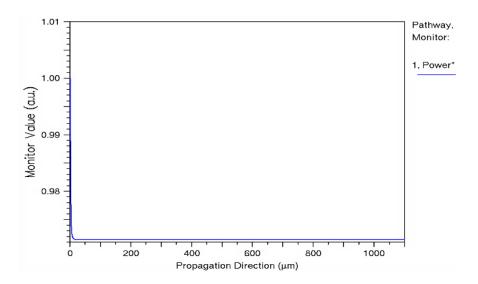

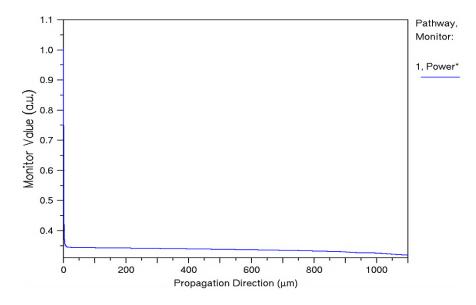

| FIGURE 5.10: Optical energy propagation through the 400 nm OWG along                          | 84 |

| Z without the OWG openings.                                                                   |    |

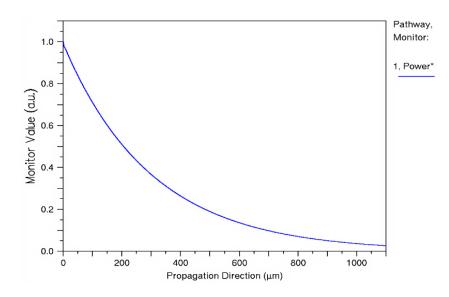

| FIGURE 5.11: Optical energy propagation through the 400 nm OWG along                          | 85 |

| Z with the OWG openings.                                                                      |    |

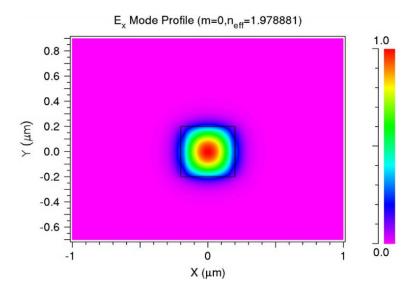

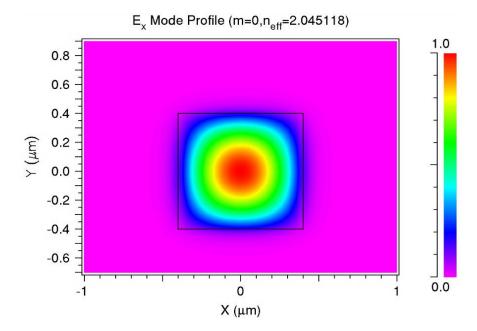

| FIGURE 5.12: Mode profile (XY cross section of the 400 nm OWG) of                             | 86 |

| the fundamental mode.                                                                         |    |

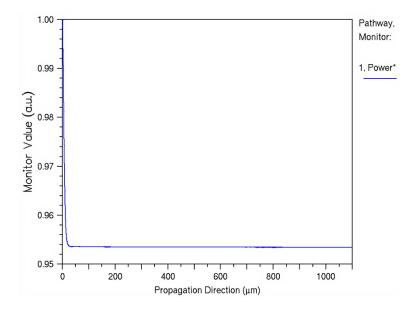

| FIGURE 5.13: Optical energy propagation through the 800 nm OWG                                | 86 |

| along Z without the OWG openings.                                                             |    |

| FIGURE 5.14: Optical energy propagation through the 800 nm OWG                                | 87 |

| along Z with the OWG openings.                                                                |    |

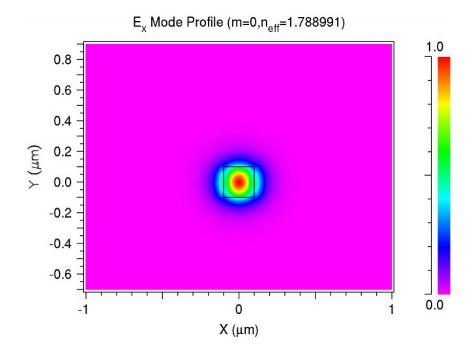

| FIGURE 5.15: Mode profile (XY cross section of the 800 nm OWG) of                             | 87 |

| the fundamental mode.                                                                         |    |

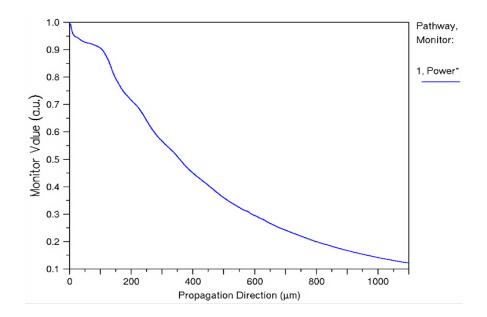

| FIGURE 5.16: Optical energy propagation through the 200 nm cross section                      | 88 |

| OWG along Z without the OWG openings.                                                         |    |

| FIGURE 5.17: Optical energy propagation through the 200 nm cross section                      | 88 |

| OWG along Z with the OWG openings.                                                            |    |

| FIGURE 5.18: Mode profile (XY cross section of the 200 nm OWG) of the                         | 89 |

| fundamental mode.                                                                             |    |

| FIGURE 5.19: 3D layout of the photonic layer showing the parallel                             | 92 |

| OWGs with minimum spacing between adjacent OWGs.                                              |    |

| FIGURE 5.20: Optical energy propagation through the 100 nm                                    | 93 |

| cross section OWG along Z without the OWG openings.                                           |    |

| FIGURE 5.21: Optical energy propagation through the 100 nm                                    | 94 |

| cross section OWG along Z with the OWG openings.                                              |    |

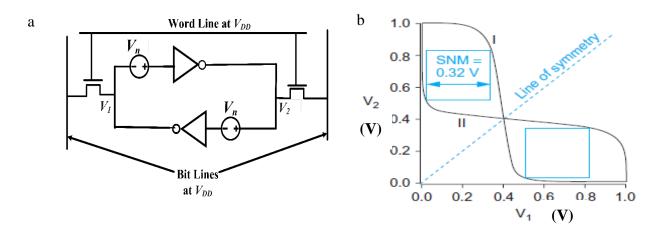

| FIGURE 6.1: 6T SRAM Cell with noise source to determine SNM,                                  | 98 |

| and butterfly diagram showing the hold SNM.                                                   |    |

|                                                                                               |    |

| FIGURE 6.2: 6T SRAM Cell with noise source to determine SNM.             | 100 |

|--------------------------------------------------------------------------|-----|

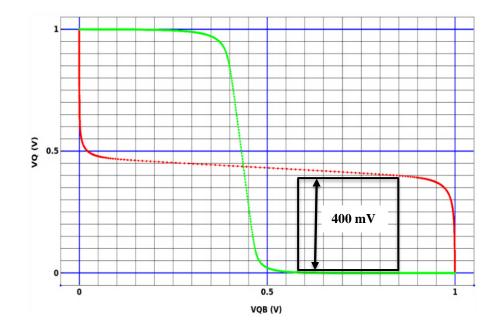

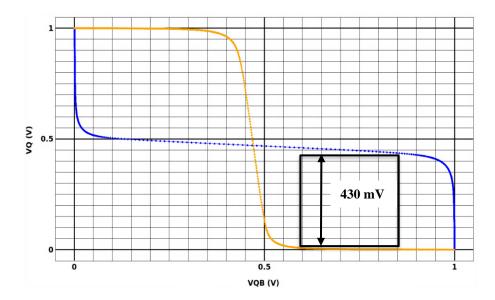

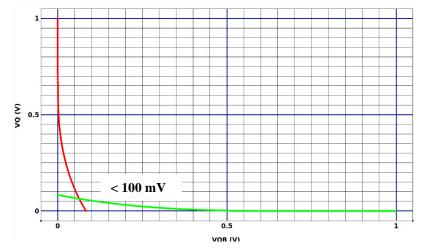

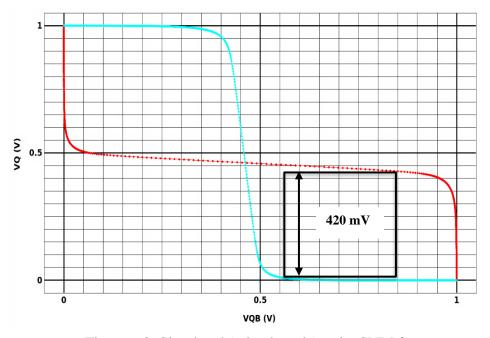

| FIGURE 6.3: Simulated (mixed mode) hold SNM for a regular 6T SRAM cell.  | 103 |

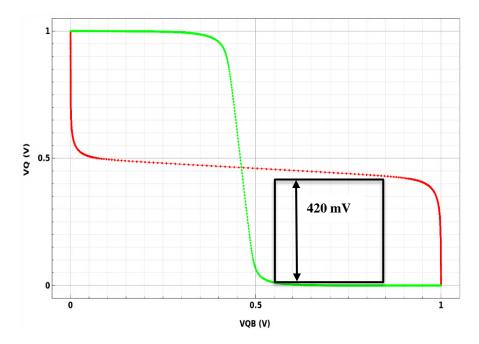

| FIGURE 6.4: Simulated (mixed mode) hold SNM for a hybrid 6T SRAM cell.   | 104 |

| FIGURE 6.5: Simulated (mixed mode) read SNM for a regular 6T SRAM cell.  | 104 |

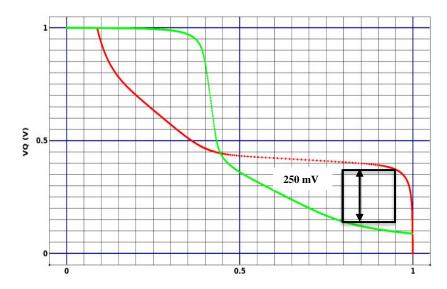

| FIGURE 6.6: Simulated (mixed mode) read SNM for a hybrid 6T SRAM cell.   | 105 |

| FIGURE 6.7: Simulated (mixed mode) write SNM for a regular 6T SRAM cell. | 105 |

| FIGURE 6.8: Simulated (mixed mode) write SNM for a hybrid 6T SRAM cell.  | 106 |

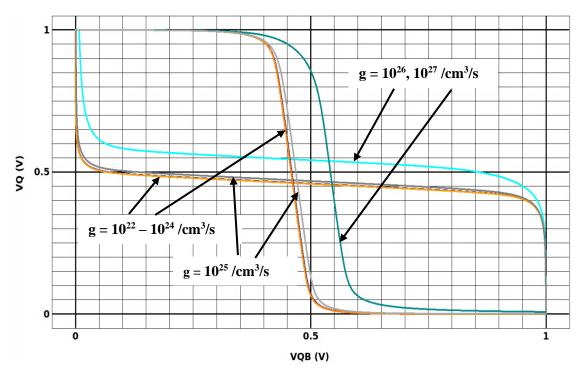

| FIGURE 6.9: Butterfly curves for a hybrid 6T SRAM cell for various       | 109 |

| optical generation rates for the access LETs.                            |     |

## LIST of TABLES

TABLE 4.1: Comparison of various performance metrices of 256 – KB and512 – KB 6T SRAM array with FET, LET and ballistic LET access devices.51

### **CHAPTER 1: Introduction**

### 1.1 Motivation

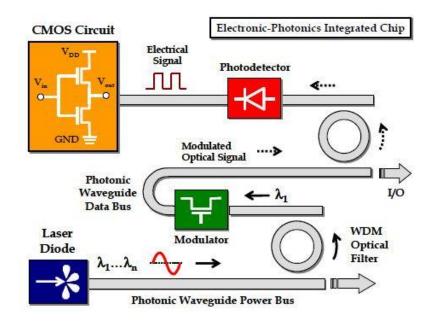

Over the last decade, there has been a huge boom in CMOS photonics, and it has opened up whole new paths toward advancements in integrated circuits (ICs) and integrated systems in the post-Moore scaling era. Over the last decade, the improvements in photonic integrated circuits are mostly due to the heterogeneous integration of novel optoelectronic devices with standard CMOS circuits. Figure 1.1 [1] shows the optoelectronic signal flow in a typical electronic – photonic integrated circuit (EPIC), where the active photonic devices (for instance photodetector) can act as an optoelectronic switch and can be placed in the photodetector section such that its electrical output can drive the CMOS circuit.

Figure 1.1: Signal flow path in an Electronic-Photonic Integrated Circuit [1]

To significantly ameliorate the energy-efficiency and data capacity of communication systems and ICs, and high preformation computing circuits, the combined use of hybrid electronic-photonic ICs have become extremely important [2-4]. The main advantage of using photons in place of electrons to process and transfer data at speeds reaching Terabits/s, over longer distances, is the much lower energy dissipation in purely photonic systems, as compared to the dissipative metal electrical wires. Among all platforms for building photonic integrated circuits (PICs), silicon on-insulator (SOI) is the most promising due to the CMOS compatible process enabled by low-cost and large-volume manufacturing. Silicon photonics integrated circuits (SiPICs) have become a potentially matured technology that can satisfy the exponentially increasing need for higher data rates with very small energy consumption, compact size, and significantly lower cost compared to discrete photonics or III-V or II-VI materials and systems [5, 6].

Some important electronic design goals are: (1) reduction of gate latency, (2) ultra-low energy consumption per bit, and (3) simplified circuit topology (for instance logic operations using optoelectronic logic circuits require a lesser number of active devices compared to all FET based CMOS circuit) and layout architecture for many complex computation structures [3]. Compared to computation, logic operation, and switching with optics, optical interconnects have been more intensively investigated due to their advantages over metal interconnects especially in intra and inter-chip communications [1]. Though over the last decade optical interconnects have been of most interest, it is also possible to have optical computations and logic operations such as implementing basic Boolean operations like the (N)AND, (N)OR, and X(N)OR logic gates and even more complex functionalities such as 1-bit half and full adders [3, 4]. Moreover, most recently,

an ultra-fast low-power deep learning network has been implemented by optical mach-mehnder interferometers (MZIs) and has consolidated the position of computation with photonics [7].

In recent times silicon photonics has been leveraging the CMOS infrastructure to address the growing demands for optical communications for internet and data center networks. The close integration of silicon photonics with CMOS promises to transform electronic–photonic technologies, enabling processor and memory chips with high-bandwidth optical input/output as discussed in [8, 9]. In the real world, photonic devices need to be integrated with a variety of nanoelectronic functions (digital, analog, memory, storage, and so on) on a single silicon die (chip). Monolithic (that is on a single chip) integration of photonic devices in close proximity to typical electronic devices like FETs is mainly crucial for reasons like allowing to achieve of high levels of performance, scalability, and complexity simultaneously for electronic–photonic systems [8, 9].

In conventional logic gates, data loss is a significant issue, and it is mainly caused since the number of inputs and outputs are not equal. It was shown by Landauer [10, 11] that the traditional Boolean logic gate for its regular operation, must dissipate energy at least kTln2 per bit loss, where k is the Boltzmann constant and T is the absolute temperature. In today's electronic systems, Ohmic loss (I<sup>2</sup>R) is inevitable and occurs due to the flow of electrons through a conducting/semiconducting medium. Hence, in today's data centric era, an increase in power consumption is becoming a bottleneck for high performance VLSI circuits and systems. Even though CMOS technology is the most widely used in a VLSI circuit because of its low power consumption, the energy dissipated during charging and discharging operations cannot be abolished without sacrificing the circuit operation, since it is proportional to the clock frequency of the circuits [12]. On the other hand, photon being the ultimate unit of information traveling with the speed of light (with a bandwidth of THz), and with data packets of zero effective mass forming an optical signal, the techniques of computing with light may provide a way out of the limitations of computational speed, bandwidth limitations, power dissipation and complexity inherent in traditional electronic computing methods [4]. Also, in principle, it would be possible to emulate the functions of the electronic gates in a computational digital circuit with optical logic gates where the optoelectronic counterparts of the FETs (say a light effect transistor (LET) which an M-S-M structure based photodetector that can emulate the characteristics of a FET as will be discussed in detail in Chapter 3) will perform the optically controlled logic switching, and the electrical metal wires can be replaced with optical waveguides [13, 14].

## 1.2 Objective

Photonic devices can provide advantages in speed and switching energy as compared to electronic counterparts, however, there are three major challenges that photonic devices face when they are directly integrated with electronic devices: size mismatch, energy data rate (EDR), and cascadability [15, 16]. Even though photoconductive devices may potentially offer advantages in switching speed [17] and switching energy [13, 14, 18, 19], it has a major drawback, and hence a photonic device such as the LETs [13, 20], cannot be directly used to drive another LET based circuit since the electrical output of the LET cannot provide the optical input signal that is used drive a similar device. So to simultaneously take advantage of the photonic devices and at the same time avoid the cascading issue in computing applications [20], a hybrid approach has been proposed wherein an integrated circuit only the switching FETs are replaced by LETs. A good example of such a circuit is a 6T static random access memory (SRAM) cell where the access FETs are replaced by LETs, and accordingly the metallic word lines by optical waveguides (OWGs) [14]. Also, this application not only improves the performance of the SRAM but also alleviates

the challenges of size mismatch and EDR (EDR  $\leq$  10 fJ/bit is desirable for on-chip communication) [15, 16]. This is possible with this approach because it is not required to illuminate each photonic individually, but they can be grouped together and (all access LETs in a row of the 6T array) simultaneously illuminated [14, 20] as in the operation of conventional SRAMs [21].

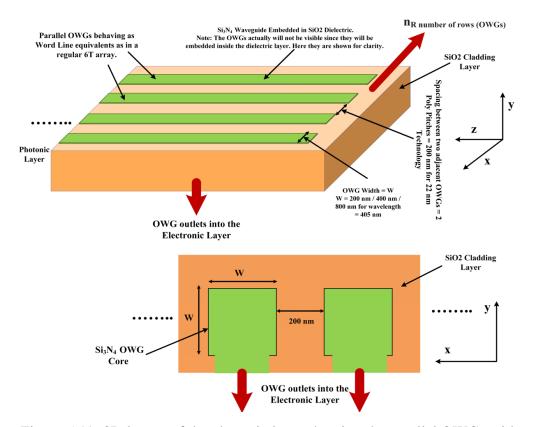

A novel OWG architecture embedded inside a dielectric layer in the photonic layer with multiple openings into the electronic layer has been designed and simulated using the Synopsys Photonic Design suite, *RSoft* which shows that the proposed OWG system can perform similar functions as the word line of a regular 6T array, by efficiently transmitting optical energy to the LET access devices in the same row. Moreover, the design and implementation of a fully functional hybrid 6T SRAM cell with better noise characteristics compared to the regular 6T cell confirm that the proposed hybrid structure is not only high performing (lesser delay and energy consumption) but also very robust (higher noise stability), which makes the hybrid 6T SRAM a felicitous candidate for cache applications in high performance computing systems.

#### **CHAPTER 2: Optoelectronic Devices**

#### 2.1 Overview

Optoelectronics is the combination of optics and electronics which includes the study, design, and manufacture of a hardware device that converts electrical energy into light and vice versa through semiconductors [22]. Optoelectronic devices rely on light-matter interactions and electronic properties of matter to convert light into electrical signals or vice versa. There has always been a drive to improve light-matter interactions in semiconductor materials to make better optoelectronic devices.

In the last decade, one-dimensional or quasi-one-dimensional nanostructures (e.g., nanowires) have been widely researched as potential building blocks for nanoelectronics circuits. Due to their excellent electronic and photonic properties (due to their high surface to volume ratio as a result of a reduction in volume) semiconductor nanostructures (especially nanowires) are being used extensively for photodetectors, optoelectronic switches, optical interconnects, and photovoltaics [23-27]. The optical properties of nanostructures are particularly sensitive to their physical dimensions, and the high surface to volume ratio not only allows for enhanced optical absorption but also enhances carrier confinement which in turn results in a high gain in photodetectors [28, 29]. Due to their excellent electronic and optical properties, and reduced sizes, semiconductor nanowires based electronic-photonic devices are very important building modules for the monolithic integration of nanoelectronic and nanophotonic devices.

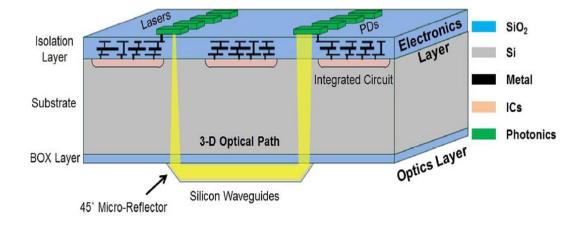

Silicon (Si) is the most widely used semiconductor in the IC technology, and silicon nanowires (SiNW) are the most extensively studied for electronic applications. Since Si is the main building block of IC technology, Si-based photodetectors are a lucrative choice for on-chip integration with other electronic devices (for instance FETs), since the whole process flow is

CMOS compatible [23, 24, 30], and the Si photodetectors and other Si-based optical components can be readily fabricated alongside the standard Si FET ICs as shown in Figure 2.1 [30].

Figure 2.1: SOI-based chip-level optical interconnect module with lasers and photodetectors using 3-D guided-wave path for multi-core processor or memory-to-processor interface [30].

### 2.2 Nanowire Photodetectors

Photoconductivity is the process of modulation of the electrical conductivity of a device/material due to incident radiation of a suitable wavelength. In the process of photoconductivity, there are several successive or simultaneous mechanisms like the absorption of the incident light depending on the absorptivity of the material, carrier photogeneration, and carrier transport (including carrier trapping, de-trapping, and recombination) through the device to give the photocurrent governed by various physical models [24, 25, 31]. The change in conductivity of a device due to the absorption of radiation of a suitable wavelength mainly depends upon the number of carriers produced per photon absorbed (carrier generation quantum yield), and the mobility of photogenerated carriers (both majority and minority). The duration of the

photoconductive effect leading to the modulation of conductivity depends on the electronic structure of the material (like the presence of traps and defects) which in turn dictates the carrier lifetime of the photogenerated carriers [24]. The high photoresponsivity and gain observed in semiconductor nanowires, and the recent advancement in capturing and understanding the physics behind the photoconduction mechanism in low dimensional systems and materials with a high density of surface states and traps are of huge interest in the potential use of NWs as photo sensing elements in highly integrated optoelectronic devices, optical interconnects, and transceivers. The optical properties of NWs are mainly dependent upon the dielectric functions of bulk materials, with some additional effects like optical birefringence, light scattering, and waveguiding effects (light funneling). However, variations in properties arising from the NW geometry and the low dimensionality leading to carrier confinement also play an important role in the total photoconductivity [24, 31]. The optical birefringence effect mainly depends on the modulation or change of the and also due to the variation of the optical matrix elements due to the quantization of carries and is mainly predominant in very thin NWs with diameter < 10 nm, and due to the confinement of the optical electric field inside the NW's dielectric material. In the case of thin NWs (typically when NW diameter < light wavelength ( $\lambda$ )) the electric field vector's perpendicular component is generally non-dominant while the parallel component dominates, while for thick NWs the electric field distribution inside the NW is non-uniform [24]. Also, enhanced scattering of light happens in NWs when the physical dimension is comparable to or much lesser than the wavelength of incident radiation [24, 31]. It is evident from rigorous numerical calculations that the Silicon NW arrays have a very high absorption of incident light when the wavelength is much greater than that of the fundamental bandgap due to the very high confinement of the electromagnetic energy into the high refractive index of the NW material and its reduced volume,

which is known as light funneling, and thus outperforming their thin film counterparts made from the same material [24, 31].

## 2.3 Working Mechanism and Carrier Transport

The carrier dynamics and transport phenomena in photodetectors can be described by the combination of Poisson's equation, carrier continuity equations, and the drift diffusion equations as shown below [25, 32, 33]:

$$\nabla^2 \Psi = -\frac{q}{\varepsilon} (p - n + N_D - N_A) \tag{2.1}$$

$$-\frac{1}{q}\nabla J_n - g + r_n + \frac{\partial n}{\partial t} = 0$$

(2.2)

$$\frac{1}{q}\nabla J_p - g + r_p + \frac{\partial p}{\partial t} = 0$$

(2.3)

$$J_n = q\mu_n nF + qD_n \nabla n \tag{2.4}$$

$$J_p = q\mu_p pF - qD_p \nabla p \tag{2.5}$$

where  $\Psi$  is the electrostatic potential; p and n are the total hole and electron concentration after illumination; g is the optical generation rate and  $r_{n/p}$  is the electron/hole recombination rate;  $\mu_{n/p}$  is the electron/hole mobility;  $D_{n/p}$  is the electron/hole diffusion constant, and F is the applied electric field. Under illumination (considering an n-type device), the change in conductivity of the device occurs either due to the change in carrier concertation or change in carrier mobility due to scattering effects is shown [24, 31]:

$$\Delta \sigma = \sigma_{light} - \sigma_{dark} = e(\mu \Delta n + n \Delta \mu) \qquad (2.6)$$

Generally, the change in carrier concentration ( $\Delta n$ ) due to illumination is much higher than the change in mobility ( $\Delta \mu$ ), and hence neglecting the change in mobility effect, and considering only the recycling gain theory [28], the photocurrent density in an n-type device can be written as:

$$J_{PC} = eF\mu\Delta n \tag{2.7}$$

The excess carrier depends on the amount of photogenerated carrier which in turn depends on the optical generation rate (number of photo carriers generated per unit volume per unit time due to optical absorption) given by [24, 34]:

$$g = \eta^* \frac{\left(\frac{P_{opt}}{\hbar\omega}\right)}{volume}$$

(2.8)

where  $P_{opt}$  is the absorbed optical power, and it depends on the surface area of the device exposed to illumination and the absorption coefficient of the material,  $\hbar\omega$  is the energy of a photon, and  $\eta^*$ is the effective carrier photogeneration quantum efficiency which takes into account the effect of reflection, scattering, and low dimensionality of the NW on optical absorption. Now under steady state and constant illumination, neglecting the effects of excess carrier confinement at the device contacts, and the non-uniform distribution of excess carriers due to the applied electric field [28], the excess carrier concentration may be given as [24, 28]:

$$\Delta n = g\tau \tag{2.9}$$

where  $\tau$  is the carrier lifetime and mainly depends on the material properties and the quality of the material used in the device. By combining Equations 2.7 through 2.9, the steady-state photocurrent density for a given wavelength can be written as:

$$J_{PC} = \eta^* \frac{\left(\frac{P_{opt}}{\hbar\omega}\right)}{volume} eF\mu\tau \qquad (2.10)$$

It is observed from Equation 2.10 that along with other parameters, the photocurrent depends on the quality of the material ( $\tau$  is generally higher for good quality materials) used in the device. If the effects of both electrons and holes are to be considered, then the total photocurrent density can be written as:

$$J_{PC} = \eta^* \frac{\left(\frac{P_{opt}}{\hbar\omega}\right)}{volume} eF(\mu_n \tau_n + \mu_p \tau_p)$$

(2.11)

For a, strictly speaking, MSM photoconductor device, the carrier dynamics under bias are dependent on the potential barrier heights at the two MS contacts, and the voltage drop at the two metal contacts [25, 28, 29]. The asymmetry in the *I*–*V* curve of these M-S-M structures mainly arises from the difference in potential barrier heights at the two M-S contacts. Under illumination, the increase in current is not only due to the excess carrier concentration (which decreases the series resistance of the NW) but also due to the reduction of the barrier heights at the two M-S contacts [25]. Hence the observation of very high current in single NW-based MSM devices has contribution both from photoconductivity as well as the reduction of the potential barriers at the contacts [25] due to local carrier generation. Also, the recombination at the junctions can be suppressed by the illumination which enhances the photocurrent. It has also been reported that the contribution of contact barrier reduction due to illumination is more pronounced on the photocurrent of the MSM structure than the photoconductive reduction of NW resistance due to the generated excess carriers [25].

Zero bias photo response, similar to that in a solar cell, has been observed in M-S-M structures. The reason may be the formation of a built-in potential barrier at the two contacts due to band bending at the two M-S interfaces which are due to the work functions difference between the metal and the semiconductor contacts [25] at the two ends of the device. In the NW-based M-

S-M device, if the device's active region is much lesser in length than the device depletion width, then there is a possibility of the existence of an axial field in the middle of the NW without any application of bias voltage, and this phenomenon can collect the carriers giving rise to zero bias photocurrent [25]. For exactly symmetrical MS junctions, the net zero bias photo current will be zero. The zero bias photocurrent increases non-linearly with incident power following a relation  $I_{ph} \alpha P_{opt}^{\gamma}$  [24, 25]. Generally, the photocurrent depends on photo-generated carriers, which in turn depends on the trap state dynamics and trap occupation probability around the Fermi level, and is often empirically related to absorbed optical power  $P_{opt}$  with an exponent  $\gamma$ . The exponent depends on the distribution of carrier traps and carrier recombination that happens inside the active region of the device [28, 29].

.

#### CHAPTER 3: Light Effect Transistor

## 3.1 Device Overview and Comparison with FETs

A FET is principally a voltage-controlled device with four terminals: source (S), drain (D), gate (G), and body (B), where the S-D conductivity is modulated by the application of a voltage at the G to create a layer of free charges which conducts current between the S-D terminals [35]. FETs are the most widely used electronic device in ICs and are used for analog, logical, and memory operations. Although FETs have evolved structurally from the early planar to the multigate 3D structures (like DG FET, FinFET, etc.) with continuous shrinkage in device dimensions, the basic operating principle remains the same. These multi-gate structures have led to greater fabrication complexity, and ultimately to challenges in gate fabrication and precise doping control [36-38]. Though various new technologies, like FinFETs tunnel-FETs (TFETs) [39, 40] have been developed in recent years to enable the continuation of Moore's law [41], further development with such technologies is not very promising. Also, more sophisticated structures like semiconductor nanowire (SNW) based FETs [42, 43], FETs comprising of 2D channel materials, [44, 45], and FETs with multiple independent gates have been exploited, however, no clear pathway for overcoming a FET's intrinsic physical limitations [46-48] dictated by its operation mechanisms, such as random dopant fluctuations, gate fabrication complexities, and inherent parasitic capacitances and resistances, and no viable revival technologies exist so far.

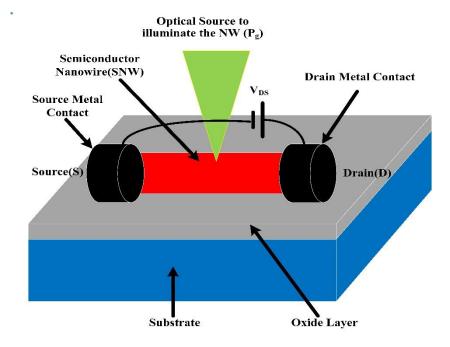

A LET as shown in Figure 3.1 [13, 14] is a two-terminal M-S-M structure with a semiconductor nanowire (SNW) placed on an insulating substrate with two M-S junctions at the ends forming the S and D contacts. Figure 3.1 brings out the structural simplicity of the LET

without a physical gate over conventional gated FETs. The working mechanism of a LET is different from that of a traditional FET in that the source-drain conductivity of a LET is

Figure 3.1: A Light Effect Transistor (LET) [14].

modulated by light or electromagnetic radiation of a suitable wavelength as in a photoconductive mechanism [49] as opposed to electrostatic control by the gate, and the current carriers are generated through optical absorption rather than thermal activation of the dopants. The advantage of an LET over an FET stems from various factors such as the removal of the physical gate, thus minimizing the complex gate fabrication process and random dopant fluctuations in FETs [36]. Hence, the LET can be scaled down to the quantum regime without the problem of short-channel effects (SCEs) that are common in nanoscale FETs [50]. Also, because the LET structure does not have a physical gate, the device speed is expected to be only limited by the carrier transit time or lifetime, whichever is smaller, rather than the capacitive delay as in the gated FETs.

While the LET can readily emulate the current-voltage (I-V) relationship of a FET (as shown in the next section) under a single beam illumination (as in a photodetector), it offers functions not readily achievable by either a FET or a photodetector [51, 52], when it operates differently than a typical photodetector under multiple independent beam illumination. It is to be noted that a traditional p-n junction-based photodetector (though superior to the M-S-M counterparts in terms of bias voltage requirements) cannot emulate the I-V of a conventional FET under illumination, while a photoconductive-based M-S-M structure like the LET under illumination can resemble a FET with gate voltage [13]. Under simultaneous multiple beam illumination (which is usually for photoconductive function), the LET can further function as optical AND and OR gates, perform optical amplification [13], and other optical analog functions that are not possible by a photodetector or single FET device.

## 3.2 LET Device Characterization

For the LET operation under illumination, the optical gating process has two control parameters:  $\lambda_g$  and  $P_g$  under single CW illumination. For the LET transfer and output characteristics studied in [13], a single beam focused CW illumination where the center of the SNW was illuminated with 633, 532, 442, or 325 nm light; and a uniform illumination of the SNW with white light from a halogen lamp was used. The LETs output characteristic was studied as a variation of the drain current with drain-source voltage ( $I_d$  vs  $V_{ds}$ ) under a constant optical power and wavelength,  $P_g(\lambda_g)$ , which is analogous to the FET's output characteristics under a constant gate bias; while the transfer characteristic was studied as the variation of drain current with the optical power shined on the SNW ( $I_d$  vs  $P_g(\lambda_g)$ ) at a constant  $V_{ds}$ , analogous to FET's transfer characteristic where the gate voltage for the FET has been replaced by the control optical power in case of LET.

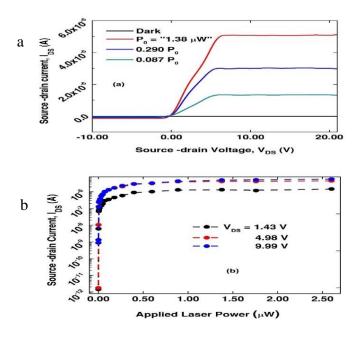

In the previous study using a CdSe NW of 5.5  $\mu$ m in length and 80 nm in diameter with Indium (In) contacts at two ends, the illumination optically modulates the electrical conductivity of the NW between "on" and "off" states resembling that of FETs, with the measured output characteristics shown in Figure 3.2a [13]. It is to be noted that the high values of  $V_{ds}$  requirement are due to the very long length of NW used in the experiment, while for LET applications if NW of lesser lengths is used  $V_{ds}$  scales down accordingly [14]. As seen in the previous study [13], the current varies with changing the wavelength of light used for the gating purpose, fundamentally due to wavelength dependent light-matter interactions, which also gives the LET more flexibility in achieving gating-dependent optoelectronic functions as compared to FETs.

Figure 3.2: (a) Output and (b) transfer characteristics of a prototype LET based on a CdSe nanowire [13].

In the measured transfer characteristics (variation of  $I_d$  with  $P_g$  for different  $V_{ds}$ ) of the LET as shown in Figure 3.2b [13], the threshold power ( $P_T$ ) corresponds to the onset of the liner  $I_d - P_g$ region for a given value of  $\lambda_g$ . A LET can employ the subthreshold region to function as optical AND gates or for optical amplification purposes. It is to be noted that in the experimental results, the power actually absorbed by the NW is ~ 10% of the applied power, since the laser spot size is considerably larger than the NW diameter, hence reducing the beam size closer to the NW diameter could drastically reduce the  $P_g$  requirement [13]. Also, the asymmetry in the measured output characteristics is probably due to the asymmetry in the In/CdSe contacts at the two ends of the NW, where one is close to ohmic and the other is close to a Schottky contact.

### 3.2.1 Estimation of LET Parameters

Since very long M-S-M devices are not very useful for VLSI circuit applications, and hence for performance estimation, a more practical NW length of 100 nm – 500 nm has been assumed. Although the demonstrated prototype LETs were based on CdSe NWs, there is no limit to the material system per the device mechanism. At room temperature, many semiconductors (e.g., Si, SiC, InAs, InP, GaAs, CdSe) have saturation electron velocities in the range of  $10^7 - 10^8$  cm/s when the electrical field is of the order of 100 kV/cm [53, 54] which implies a carrier transit time of the order of 1 - 0.1 ps and 5 - 0.5 ps for a 100 nm and 500 nm long NW respectively. Also, it is to be noted that 100 nm is the typical length scale of ballistic transport where the saturation velocity can be achieved. For longer NWs in the non-ballistic transport regime, the electron transit time depends on the electrical field. For Si at E = 10 kV/cm, electron velocity is around 7 x  $10^6$  cm/s [53, 54], and the carrier transit time ( $t_{LET}$ ) can be estimated to be 4.3 and 7.1 ps respectively for 300 nm and 500 nm long Si NW. If the NW in the LET can be scaled down to operate in the ballistic regime (typically  $\leq 100$  nm), then ultrafast switching (of the order of 1 ps or faster) can be obtained which implies ultrasmall switching energy for the LET. The photocurrent current in the LET device may be written as [13]:

$$I_d = \frac{e_{\eta N_{ph}G}}{t_{LET}} \tag{3.1}$$

where  $\eta$  is the illumination efficiency,  $N_{ph}$  is the number of photons absorbed and *G* is the photoconductive gain between the carriers generated by light and the total carriers in the current as given by the recycling gain theory [24, 28]:

$$G = \frac{F\mu\tau}{L} \tag{3.2}$$

where *F* is the applied Electric field (depends on the D-S voltage),  $\tau$  is the photocarrier lifetime which depends on the quality (traps and defects, surface states, etc.) of the material; *L* is the length of the device. In Equation 3.1, considering the photon flux =  $N_{ph}/t_{LET}$ , the optical power ( $P_g$ ) needed to have a current of  $I_d$  at a gain of *G* is then given by:

$$P_g = \frac{E_{ph}I_d}{e\eta G} \tag{3.3}$$

Assuming  $I_d = 1\mu A$  (a good assumption for digital VLSI circuits);  $G = 10^3$  (gain of the M-S-M photodetectors increases as NW length is decreased);  $\eta = 1$ , and the photon energy for 532 nm illumination,  $E_{ph} \approx 2.33$  eV, the needed optical power will be,  $P_g = 2.3$  nW. For a LET the electrical switching energy due to the transit of carriers and the S-D current can be estimated by:

$$E_{el} = I_d V_{ds} t_{LET} \tag{3.4}$$

Assuming a switching time (carrier transit time)  $t_{LET} = 1$  ps (for a ballistic device), and an oncurrent of  $I_d = 1$  µA under a D-S bias,  $V_{sd} = 1$  V, the electrical switching energy  $E_{el}$  will be 1 aJ/switch. However, in the LET, optical gating power also contributes to the switching energy and the optical switching energy is. given by:

$$E_{op} = P_g t_{LET} = \frac{E_{ph} I_d}{e \eta G} t_{LET} \qquad (3.5)$$

Plugin in the values of  $P_g = 2.3$  nW and  $t_{LTT} = 1$  ps,  $E_{op} = 2.3 \times 10^{-3}$  aJ/switch  $\ll Eel$ , which leaves sufficient room allowing for lower gain and below 100% light power delivery efficiency. Hence the total switching energy ( $E_{el} + E_{op}$ ) will be  $\approx 1$  aJ/switch which is almost more than two orders of magnitude lesser than advanced FETs having switching energy in the range of 0.1 - 1 fJ/switch.

Even considering a non-ballistic device of length 300 nm with  $t_{LET} = 4.3$  ps, with  $I_d = 5$   $\mu$ A (more suitable for circuit purposes as will be seen in the next chapter), at a  $V_{ds} = 1.5$  V, the  $E_{el}$   $\approx 32$  aJ/switch and  $E_{op} \approx 3.95$  x 10<sup>-2</sup> aJ/switch, which gives total switching energy of  $\approx 32$  aJ/switch, which is still at least three times lesser than FET's minimum switching energy.

In an even more idealistic case, assuming a ballistic device with a quantum impedance of 12.9 k $\Omega$  [55], transit time of 0.1 ps, S-D current of 1  $\mu$ A, and no voltage loss at the contacts, the electrical switching energy can be as low as 1.3 x 10<sup>-21</sup> J/switch at an extremely low  $V_{sd}$  of only 13 mV [13]. Also, the large prototype device (CdSe NW of length 5.5  $\mu$ m and diameter of 80 nm) studied experimentally under 532 nm illumination of 110 nW (only about 6% of the power was actually absorbed), yielded  $I_d = 0.35 \,\mu$ A at  $V_{ds} = 1.43$  V; while in dark condition,  $I_d \sim 1$  pA, which corresponds to about 1.5 pW off power. Estimating the total switching energy for such a large device using the typical room temperature carrier lifetime in a II-VI semiconductor of the order of 100 ps is  $E_{el} + E_{op} \approx 0.06$  fJ/switch, which would still be better than typical FETs. In FETs, the gate related RC delays predominate over the carrier transit-time delay; but in the LET, the carrier

transit time through the NW channel is expected to be the predominant factor for determining the switching speed and energy of a discrete LET [14, 20].

### 3.2.2 TCAD Modelling of the FET and LET Devices

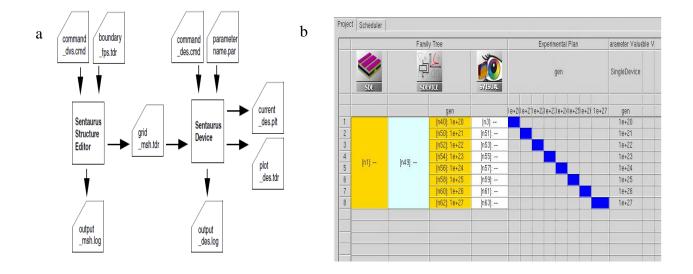

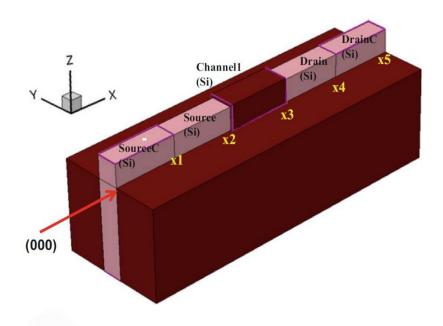

The FET and LET devices have been modeled using the Sentaurus TCAD modeling suite from SYNOPSYS [56] [57]. A typical Senataurus Workbench (SWB) workflow for device design in Synopsys Sentaurus TCAD is shown in Figure 3.3. In the Sentaurus Structure Editor (SDE) tool, the device structure is made, all the various doping profiles are added, all electrical contacts are made and finally, the meshing (for the active region with high carrier density and high electric field, generally fine meshing is needed) is done for the device. Once the SDE simulation is complete the control automatically flows to the SDEVICE module in the workbench, where the meshing information from the SDE module is incorporated; all the physical models describing the device nonidealities and depending on the device's working mechanism are added, and then various mathematical solvers are run iteratively to solve the Poisson's equation along with the carrier transport equations to obtain the outputs which are then viewed in the SVISUAL module. The meshing and other device parameters (I-V) are also viewed in SVISUAL module. A FinFET structure as shown in Figure 3.4 [58] has been simulated with the following device parameters: physical gate length  $(L_g) = 22$  nm; fin width  $(F_w) = 10$  nm; fin height  $(F_h) = 10$  nm; source length = 15 nm; drain length = 15 nm; drain contact length = source contact length = 15 nm. For the n-FinFET the channel has been doped with boron @  $10^{15}$ /cm<sup>3</sup>, while the source, drain, and their respective contacts have been doped with arsenic @ 10<sup>18</sup>/cm<sup>3</sup>. Similarly, for the p-FinFET, the channel has been doped with arsenic @ 10<sup>15</sup>/cm<sup>3</sup>, while the source, drain, and their respective contacts have been doped with boron @  $10^{18}$ /cm<sup>3</sup>.

Figure 3.3: Typical (a) file structure (b) design flow in Synopsys Sentaurus TCAD.

Figure 3.4: Schematic of a FinFET showing the different regions and interfaces [58].

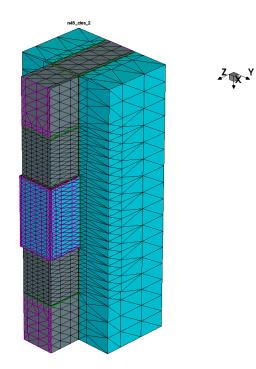

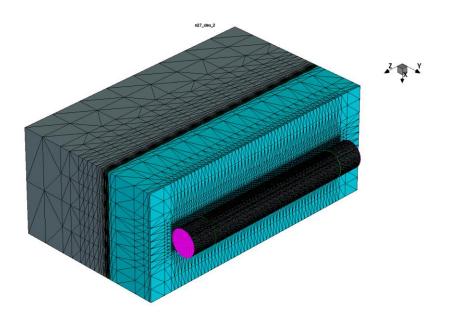

For the simulation purpose, the meshing of the device structure generated from the *SDE* module is shown in Figure 3.5 which shows fine meshing in the channel and interface regions. To model the device's non-idealities, doping dependent, high field saturation, and normal electric field dependent mobility degradation models along with carrier recombination models are included for carrier transport in the FinFET in the *SDEVICE* module [56, 57]. Also, some advanced models like the density gradient quantum correction model (if the device dimension is < 10 nm) and carrier tunneling model [56, 57] for tunneling of carriers from the drain and source into the channel have been included in the *SDEVICE* module. For the carrier transport phenomena, the standard drift diffusion model has been used [57].

Figure 3.5: Simulated meshing structure of the FinFET in Synopsys TCAD.

For both the FinFET device and the LET device shown next, at the metal contacts Dirichlet boundary condition has been assumed [57, 59]. At metal–semiconductor interfaces, by default, there is an Ohmic boundary condition (in our case no specific metal was specified, but just set the two MS contacts to be ohmic. However, it is possible to choose the metals for Ohmic/Schottky contacts, and even set workfunctions for the contact metals or the potential barrier height at the MS contacts) which has been used in the simulation [57]. In this simulation, the potential barrier at the MS contact is computed automatically by the software, and carrier tunneling models such as the *Nonlocal Tunneling* [57, 59] at material interfaces, MS contacts, and junctions are incorporated in the simulation with carrier tunneling mass for Silicon and oxide from their respective parameter files [57]. The simulated current density in various regions of the device is shown in Figure 3.6, with gate voltage ( $V_g$ ) varying from 0 to 1.5 V and at a  $V_{ds}$  of 1.4 V., and all the standard material parameters for Silicon were considered in the simulation. It is observed that there is also a very

Figure 3.6: Simulated current density in various regions of the FinFET.

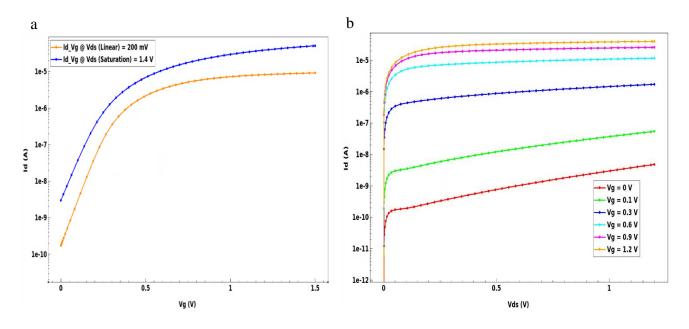

high current density on the body of the device. Though in a FET structure, the current is only expected to flow in the channel between the drain and source terminals, the body also has an appreciable current since it has an electrical connection and also due to the vertical electric field from the gate terminal. This unexpected current will not be present in the case of a LET structure since the body neither has any electrical connection nor is there any gate that creates the vertical electric field. The transfer and output characteristics for the FinFET device at different  $V_{ds}$  and  $V_g$  values respectively are shown in Figure 3.7, and from the TCAD analysis section the threshold voltage ( $V_{th}$ ) of the device is around 0.35 V and the off current (at  $V_g = 0$  V and  $V_{ds} \sim 0$  V, which is equivalent to the dark current in the LET) is of the order of  $10^{-10}$  A.

In the case of the LET, the structure is very simple with no precise doping requirements and no gate electrode requirement. A NW of 300 nm in length and 50 nm in diameter is considered. Two metal contacts were taken from the two ends of the NW to form the source and drain. For the optical switching part, various constant optical generation rates were assumed which can emulate the optical gating in the NW for various optical powers shined on the NW, since optical generation rate (g)  $\propto P_s$ . Contrary to the case of FinFET, only the high field mobility degradation model has been incorporated in the LET since principally the NW is undoped (however if the NW is to be doped then doping dependent mobility modification and recombination models should be considered), and also there will not be any mobility degradation due to normal (perpendicular to the NW channel) electric field, but only due to longitudinal electric filed [56, 57] since there is

Figure 3.7: Simulated (a)  $I_d - V_g$  and (b)  $I_d - V_{ds}$  plots for the FinFET for various  $V_{ds}$  and  $V_g$  values, respectively.

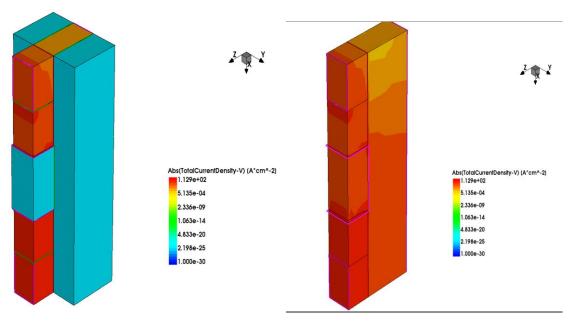

no gate control on the NW channel electrostatic. SRH and Auger recombination models with standard parameters for Silicon were included in the NW region as well as the Si/SiO<sub>2</sub> interface with standard parameters for Silicon and SiO<sub>2</sub> [57]. Also, the carrier tunneling model for tunneling of carriers from the two contacts into the NW channel under illumination and applied electric field has been included. For carrier transport, the standard drift-diffusion model has been used. The meshing of the LET structure in the *SDE* tool and the structure showing the current density in different regions of the device are shown in Figures 3.8 and 3.9, respectively. From Figure 3.9, it can be seen that in contrast to the simulated FinFET structure, the LET does not have any current flowing through the device substrate since the NW is placed on a thick insulator and the substrate has no electrical connection, and hence body related leakage will not be there in the case of LETs.

Figure 3.8: Simulated meshing structure of the LET in Synopsys TCAD.

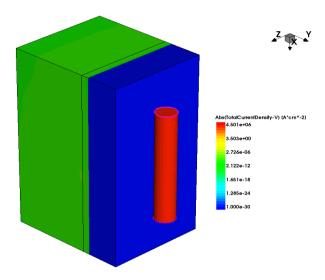

The output characteristics  $(I_d - V_{ds})$  plot of the LET device under illumination for various optical generation rates  $g = 10^{21} - 10^{29} / \text{cm}^3/\text{sec}$  (which signifies the various optical gating powers  $P_g$ ), and the  $I_d$  -  $V_{ds}$  under dark conditions (g = 0) are shown in Figure 3.10:

#### Simulated Currrent Density

Figure 3.9: Simulated current density of the LET in Synopsys TCAD.

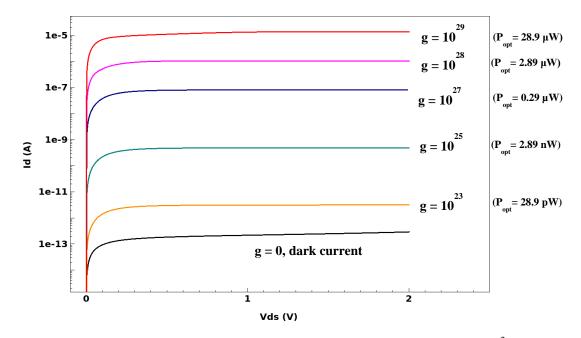

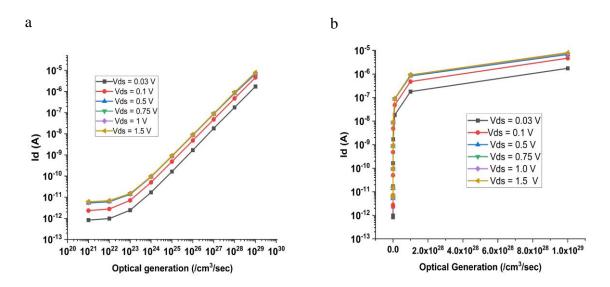

It is well established from Figure 3.10 that the output characteristics of the LET under different illumination powers (in the simulation it is represented by different generation rates) are very similar to that of conventional FET's output characteristic with different gate voltages. Also, the transfer characteristics,  $I_d$  (drain current) –  $P_g$  ( $P_g$  equivalent to optical generation rates since  $P_g \propto$  photon flux at a particular wavelength) plot for the LET under different  $V_{ds}$  values

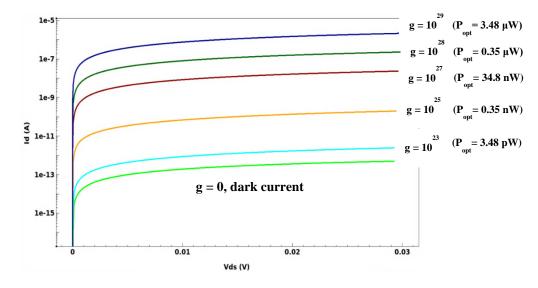

Figure 3.10: Simulated output characteristics  $(I_d - V_{ds})$  of the LET, g in /cm<sup>3</sup>/sec.

is shown in Figure 3.11, where in Figure 3.11a the optical generations are also in log scale to accommodate for the wide range of values, and in Figure 3.11b the optical generations are in linear scale which resembles the FET's transfer characteristics with a subthreshold slope. In the low power region, the  $I_d$  -  $P_g$  (optical generation) is sublinear but quickly becomes linear as seen in Figures 3.11 and 3.13.

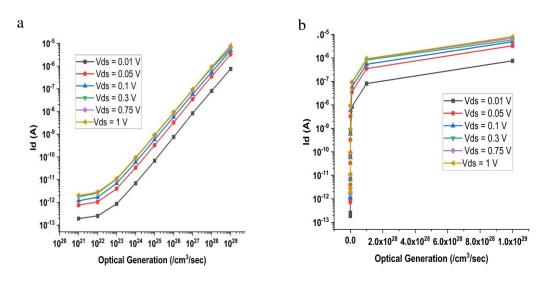

Moreover, a ballistic LET with a much small dimension (length = 100 nm and diameter = 30 nm) has also been designed and simulated using Synopsys TCAD. To incorporate the ballistic transport, the ballistic mobility model has been used in the simulation which considers the carrier dynamics in the ballistic regime [57].

Figure 3.11: Simulated transfer characteristics ( $I_d$  – Optical Generation) of the LET (a) both axes in log scale, (b) only  $I_d$  in log scale.

Also, the dark current (for both regular and ballistic LET) is extremely low (of the order of  $10^{-13}$  A) mainly due to the lack of background doping in the NW (undoped NW). Moreover, asymmetrical MS contacts by using contact metals with different work functions such that one contact is close to ohmic (by default in Sentaurus *SDEVICE* module) and the other is close to a Schottky contact [60] (metal with workfunction > that of Silicon) can further reduce the dark current. The output and transfer characteristics of the ballistic device are shown in Figures 3.12 and 3.13, respectively. As evident from the figure, the ballistic device needs an extremely low

drain-source bias of around 30 mV (as also mentioned in [13]) to have a similar range of oncurrents (10<sup>-6</sup> A) as the regular device, in the comparable range of the generation rates,  $10^{21} - 10^{29}$ / cm<sup>-3</sup>s<sup>-1</sup>, and hence it will be very suitable for ultra-low power applications.

Figure 3.12: Simulated output characteristics  $(I_d - V_{ds})$

of the ballistic LET, g in  $/cm^3/sec$ .

Figure 3.13: Simulated transfer characteristics ( $I_d$  – Optical Generation) of the ballistic LET (a) both axes in log scale, (b) only  $I_d$  in log scale.

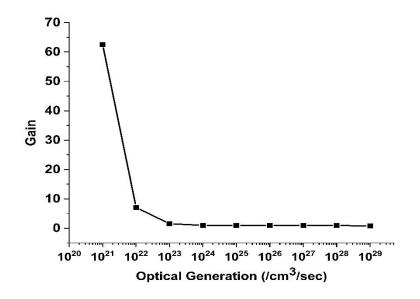

Also, photoconductive gain of the device defined as the ratio of the total carriers in the current to the carriers generated by optical excitation [24, 29] is calculated for the regular LET using the simulated  $I_d$  and optical generation values from Figure 3.11 and the gain is plotted for the regular LET with respect to the optical generation rates as shown in Figure 3.14.

Figure 3.14: Gain vs optical generation  $(P_g)$  for the regular LET.

It is seen from the Figure 3.14 that there is some gain for the LET device at lower optical generations rates  $(10^{20} - 10^{22} / \text{cm}^3/\text{sec})$  which rapidly falls to values ~ < 1 as generation rates increase. The observed gain at lower optical generation rates (the reason for gain needs further investigation) may be due to the more pronounced effect of the externally injected carriers from the M-S Ohmic contacts on the total current giving rise to a gain, and the contribution of injected carriers from the M-S Ohmic contacts fall rapidly (due to carrier saturation maybe due to the effect of traps) at higher optical generation rates as the huge number of excess carriers generated from the external optical illumination dominate the total current and hence gain also falls rapidly and saturates to a value ~ 1.

Now, considering  $I_d = 1 \ \mu$ A, at  $V_{ds} = 1.5 \ V$  at an optical generation  $g = 10^{28}/\text{cm}^3/\text{sec}$  (from Figures 3.10 and Figure 3.11) and using the (photoconductive gain) G = 0.98 (for  $g = 10^{28}/\text{cm}^3/\text{sec}$  form Figure 3.14), and using the Equations 3.3 and 3.5 (and other parameters exactly same as used in Equations 3.3 and 3.5),  $P_g = 2.38 \ \mu$ W and  $E_{op} = 10.2$  aJ respectively, and also the calculated  $P_g$  is very similar to what is shown in Figure 3.10. Now using Equation 3.4 and considering the exact same parameters as used above,  $E_{el} = 6.45$  aJ, which is comparable to the  $E_{op}$  calculated above, and  $E_{op} << E_{el}$  as discussed in Section 3.2.1 does not hold since the simulated LET gains are ~ 1 (G values are not high) for the generating rates considered in the calculation. Also, it is to be noted that having no gain is not necessarily bad, because high gain typically means low speed (bandwidth, since gain-bandwidth product is constant for a device), although no gain means higher optical gating power ( $P_g$ ) to produce the same photo current as seen in the above calculations.

## 3.3 Conclusion

In this chapter, the details of the LET device, its optoelectrical characteristics, performance matrices, and also its possible application in digital circuits are discussed. The I-V curve shows that a LET under single beam illumination can emulate the I-V (both the output and transfer characteristics) of a standard FET, the only difference is that the gate voltage in the case of the FET is replaced by the optical power in the case of the LET. Moreover, it has been found from TCAD simulation that since the LET does not have any electrical connection to the body (which just provides mechanical support), there is no unwanted leakage path to the body and hence the body current in the LET is almost ten orders of magnitude lesser than the body current in the simulated FinFETs. Since the nanowire in the LET is undoped the dark current is extremely low, of the order of 10<sup>-13</sup> A for the Silicon NW used in the simulation, an on-

current of the order of  $10^{-6}$  A yields an on-off ratio of  $10^{7}$ . Moreover, the ballistic device (length = 100 nm, diameter = 30 nm) also has similar values of the on-off ratio with only a slightly lower dark current of about 4 x  $10^{-13}$  A (the regular LET has a dark current of about 7 x  $10^{-13}$  A), and it needs only around 30 mV – 50 mV of drain-source bias to achieve such high on-off ratios, which makes the ballistic devices extremely energy efficient and a very useful candidate for ultra-low voltage electronic circuits.

#### CHAPTER 4: Conventional and Hybrid 6T SRAM

This Chapter reused the contents from the articles below:

Reprinted with permission from A. Pal, Y. Zhang, and D. D. Yau, "Monolithic and singlefunctional-unit level integration of electronic and photonic elements: FET-LET hybrid 6T SRAM," Photon. Res., vol. 9, no. 7, pp. 1369-1378, 2021/07/01 2021, doi: 10.1364/PRJ.420887. Reprinted with permission from A. Pal, Y. Zhang, and D. D. Yau, "Light Effect Transistors for High-Speed and Low-Energy Electronic and Photonic Integrated Circuits," in 2021 IEEE Research and Applications of Photonics in Defense Conference (RAPID), 2-4 Aug. 2021 2021, pp. 1-2, doi: 10.1109/RAPID51799.2021.9521451.

# 4.1 Survey of SRAMs

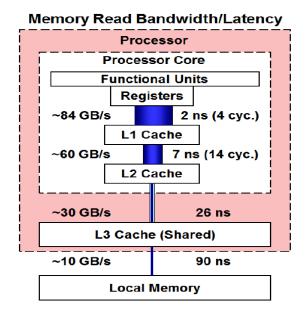

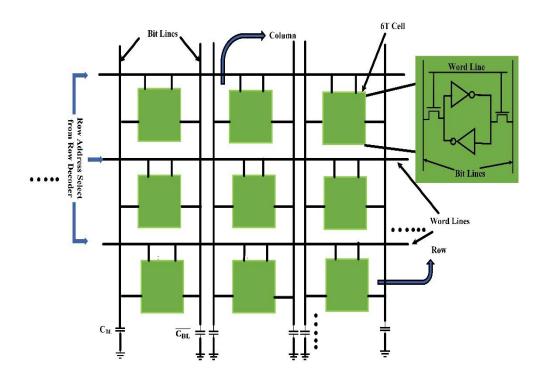

High speed, low power, low leakage, and low noise Static Random-Access Memory (SRAM) are in high demand for high-performance cache memories in computing systems. Memories are the most power-hungry blocks and consume most of the area on a chip due to their high capacity [61, 62]. Therefore, the performance and energy efficiency of SRAM is extremely important in both high-performance and ultralow-power portable, battery-operated electronic systems. SRAMs being the fastest of all memories are generally used as high-speed cache memories which have a direct connection with the CPU as shown in the processor - memory architecture of Figure 4.1 [63], and such high-speed memory-processor interfacing is not possible to attain with other memory architectures. Since on-chip caches typically consume 25% – 45% of the total energy of a chip [64, 65], and hence it is imperative to design high-speed, energy-efficient, low leakage embedded memories that are desirable for a modern electronic system.

Many techniques have been exploited at both device and circuit levels to improve the performance of the SRAM on an incremental level, particularly in speed and energy consumption

Figure: 4.1 Memory levels in a processor showing the memory bandwidth and latency. Width of blue lines indicates relative access speed [63].

[66-68]. It is possible to design a low leakage SRAM cell with supply voltage scaled down in which the voltage swing per switching activity per cell can be reduced (in both read or write operation), which will reduce the overall dynamic power consumption of the circuit. However, lowering supply voltage is fundamentally limited by various design issues like degradation in cell stability, noise margin, reduced on-current-to-off-current ratio, and strong sensitivity to process, voltage, and temperature variations [62, 69, 70]. Also, various other detrimental effects like degradation of the noise margin, an exponential increase of the leakage current, SCEs resulting from aggressive scaling of CMOS memory cells into the nanometer regime, especially in less than 32 nm technology [69, 70]. Moreover, to worsen things, excessive scaling of device dimensions and using ultrathin gate oxide in advanced technology nodes have resulted in an alarming amount of gate oxide tunneling current [62, 70] which adversely affects the circuit leakage. Also, the parameter fluctuation effects like line-edge roughness, random dopant fluctuation, and gate-oxide-

thickness fluctuation reduce the stability of SRAM cells and hence adversely affect the data storage capacity and the read and write operation (degraded noise margins and hence the stability), [62, 70]. Though the sub-threshold design for low-power applications has been carried out, the successful operation of such memory circuits is very challenging since the performance of SRAMs and the noise margins degrade at very low voltages [62, 70].

Double gate (DG) MOSFET, tunnel FETs (TFET), and FinFETs with better control of channel electrostatics have emerged as lucrative choices in the last decade to improve the performance of SRAM cells in terms of leakage current reduction, speed enhancement and mitigate various SCEs which are predominant in highly scaled bulk MOSFETs [50, 67, 71]. With the increase of SCEs with reduced technology nodes in highly scaled planar FETs, the most feasible device with reduced SCEs that is compatible with the standard CMOS technology is the tri-gate device structure, the FinFET. Various device and circuit techniques have been implemented to enhance the performance of FinFET based SRAM cells/arrays [67, 72, 73]. Different circuit techniques, such as using additional devices to improve SRAM cell stability and the usage of the back gate feature of independent gate FinFETs in the access paths of the SRAM cell to reduce environmental variation and leakage, have been used to boost the overall performance of the SRAM cell [67, 74, 75]. Techniques including the usage of reduced gate voltage (word line voltage) for the access transistors, using negative ground under the idle condition, employing dual threshold voltage devices, and transistor stacking have been reported to minimize the leakage currents and increase speed [76]. The ways to improve the read and write access time as well as reduce leakage many techniques have been proposed; like forward body biasing technique and self-controllable-voltage-level switch techniques are used to better the performance of the SRAM cell in terms of speed improvement in the active mode, whereas a reversed body biasing technique is used to reduce the leakage in the standby mode [77].

Moreover, it has been well established that 6T SRAMs made from nanowire (NW) based structures (e.g., gate-all-around, band-to-band tunneling FETs) have much better noise margin, lesser variability, and much better leakage suppression due to lesser SCEs as compared to FinFET based structures [78-80]. It has also been reported that scaling down to more advanced technology nodes (far below 22 nm), NW based device structures offer much better SCEs, drain induced barrier lowering (DIBL), subthreshold slopes, higher switching speeds, and less variability in device performance with scaling [81], which enhances the robustness of the circuits made from them.

Above-mentioned efforts primarily focus on improving the FET performance on the single device level to bring about the improvement for the 6T SRAM cell. However, the primary factors limiting the read and write speeds and the corresponding energy consumptions are the characteristics of the access transistors (rather than the transistors of the inverters) and the capacitances of the word lines and bit lines. The hybrid FET-LET 6T SRAM [14, 18] discussed in this chapter can offer a major improvement in performance with better energy efficiency by replacing the two access FETs with two LETs and also replacing the electrical word line wires with dielectric optical waveguides (OWGs). This hybrid structure offers a very close monolithic integration of the electronic and photonic components at the chip level offering a hybrid EPIC structure. Additionally, this application avoids the well-known energy-data rate (EDR) challenge (EDR  $\leq$  10 fJ/bit for on-chip communication) [15, 16], because it does not require using light to address photonic devices individually, but in a group simultaneously through an optical waveguide, for example, simultaneously illuminating all the access devices in a row of the hybrid array [14].

Although photoconductive devices are superior in compared to electronic devices in switching speed [13, 14] and switching energy [13, 20], they have a major drawback of directly cascading with another similar device. Likewise, LETs (with their electrical output) cannot be used to directly drive another LET-based logic gate (which needs optical input) efficiently without going through relatively inefficient electrical to optical energy conversion.

## 4.2 6T SRAM

# 4.2.1 Working Mechanism

In this section, the roles of access transistors in determining the overall speed and total energy consumption of a conventional 6T SRAM cell/array with 6 FETs are analyzed to highlight the needs and directions for improvement. The three main operations of a 6T SRAM cell are writing data into the cell, reading data from the cell, and holding or storing data.

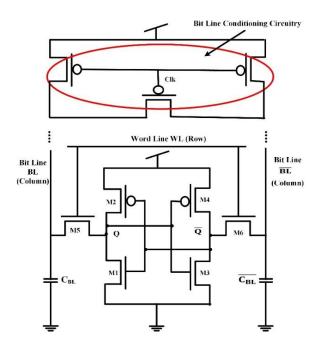

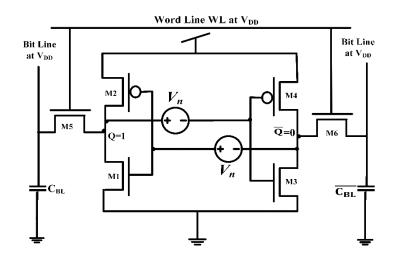

Figure 4.2: A conventional 6T SRAM cell [14].

As shown schematically in Figure 4.2, a conventional 6T SRAM has two cross-coupled latches formed of FETs M1-M4, along with two access devices M5 and M6 that allows to access the cross-coupled latch for the read and write operations. The two access transistors along with the word line (WL) and bit lines ( $BL/\overline{BL}$ ) play an extremely crucial role in determining the overall speed, power dissipation, and stability of the cell [21, 82, 83]. Encircled in red in Figure 4.2 are the three p-FET devices which serve as the bit line conditioning elements, and their role is to pre-charge and make the bit line voltages equal to each other before each read and write operation, and they also play a crucial role in the read and write processes of the SRAM array [84].

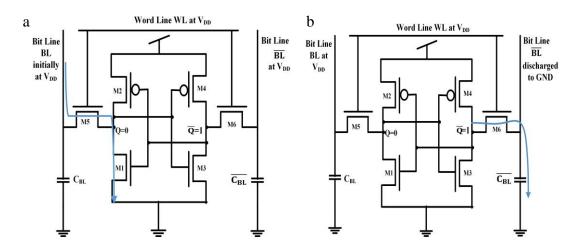

The dynamic energy consumptions of the 6T SRAM that occur during either the write or read process. are analyzed assuming that the SRAM cell is initially at logic 0 (i.e., Q = 0,  $\overline{Q} = 1$ ), as shown in Figures 4.3a and 4.3b. Before the 6T cell read operation the bit line capacitances  $C_{BL}$  and  $\overline{C}_{BL}$  are pre-charged to  $V_{DD}$  via the pre-charge circuitry; then after the word line turns on the access devices M5 and M6, the bit line BL is partially discharged through the path M5 and M1 as shown in Figure 4.3a, while the bit line  $\overline{BL}$  remains at  $V_{DD}$ , which allows the sense circuitry to read

Figure: 4.3 (a) 6T SRAM cell showing the read operation (b) write operation.

the state based on the voltage difference between bit lines BL and  $\overline{BL}$ . Similarly for the write operation as shown in Figure 4.3b, one of the already pre-charged bit lines,  $\overline{BL}$  is fully discharged via the write circuitry (not shown in the figure), then the node  $\overline{Q}$  which was initially at logic 1 is discharged through the access device M6 such that M1 and M4 turn off while M2 and M3 turn on, and a cell flipping occurs such that Q = 1,  $\overline{Q} = 0$  and hence a write-1 operation takes place. As can be seen from Figure 4.3, the bit line and the word line capacitances mainly depend on the drain/source capacitance and gate capacitance respectively of the access transistors, along with bit line and word line wire capacitances. Hence, as evident the access devices play a crucial role in determining the overall SRAM cell performance.