# HIGH FREQUENCY GAN POWER CONVERTERS DIGITAL TWIN

by

Mehrdad Biglarbegian

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2018

Approved by:

Dr. Babak Parkhideh

Dr. Badrul Chowdhury

Dr. Robert Cox

Dr. Maciej Noras

©2018 Mehrdad Biglarbegian ALL RIGHTS RESERVED

#### ABSTRACT

# MEHRDAD BIGLARBEGIAN. High Frequency GaN Power Converters Digital Twin. (Under the direction of DR. BABAK PARKHIDEH)

There is a need for a foundation of a research study aimed at investigations on near real-time reliability awareness of Gallium Nitride devices in high-frequency power converters for which we need advanced hardware and algorithms. This dissertation is moving beyond traditional reliability analysis and looking to more applicable and accurate analytical tools by introducing deep learning techniques and advanced sensing solutions. The computational structures will be applied at the edge of the power converter through online sensing and data processing units as well as on a remote server. They will provide an iterative ability to predict the time until the device may fail or reach a pre-defined degradation threshold.

With the availability of the most granular information deduced from advanced devices, a new data-driven scheme is proposed for system monitoring and possible lifetime extension Gallium Nitride power converters. The approach relies on the real-time  $R_{ds(on)}$  data extraction from the power converter, and calibration of an adaptive model using multi-physics co-simulations under power cycling. More specifically, the focus is on deploying machine learning algorithms to exploit for the parameter estimation in power electronics engineering reliability. The proposed techniques in this work are quite new and have not yet been developed and analyzed for high-frequency power converters specifically with Gallium Nitride power semiconductor devices.

#### ACKNOWLEDGEMENTS

I would like to thank my adviser Dr. Babak Parkhideh for his continuous support on my work, which helped me to complete this dissertation. His positive attitude toward research is unique and made me believe that I can aim for the highest goals. Thanks also go to my dissertation committees Drs. Badrul Chowdhury, Robert Cox, and Maciej Noras. I was fortunate to learn a lot from all of them in both teaching and research.

I would like to thank EPIC and ECE at UNC-Charlotte, and NSF for providing me with scholarships, and Dr. Mohammad Biglarbegian at University of Guelph, which further facilitated conducting my Ph.D. research.

Many thanks to my fellow students and friends at UNC-Charlotte who have supported my work. In my daily life, I have been blessed with so many wonderful friends that I am afraid I can not mention them one by one here. I would like to sincerely thank my colleagues Hamidreza Jafarian, Iman Mazhari, Namwon Kim, Shahriar Nibir, Neel Shah, Mohammadreza Baharani, Saman Mostafavi, Daniel Evans, John Troxler, Michael Ajazi, Sven Hauer, Andreas Lauer, Daniel Fregosi, Deepak Somayajula, and many others in the PV Integration Lab for unforgettable memories.

I wish there was a chance to present this work to my father who left me alone in the middle of my Ph.D. His spirit will always be with me, and he was always encouraged me to continue my studies. I want to express my greatest thankfulness to my mother and my brothers Drs. Mohammad and Behzad for their endless support in my whole life. All these years, I got a lot of encouraging words from my best family members all around the world that I will remember these fruitful moments and the emotional supports.

Finally, I would like to thank my great teachers and professors in my whole life for their dedication and excellence in teaching and education.

# DEDICATION

To my beautiful wife Fatemeh!

It wouldn't have been possible this without your supreme patience! Your boundless love was always inspiring me to continue all days and nights!

# TABLE OF CONTENTS

| LIST OF FIGURES                                                          | х   |

|--------------------------------------------------------------------------|-----|

| LIST OF TABLES                                                           | xix |

| LIST OF ABBREVIATIONS                                                    | XX  |

| CHAPTER 1: INTRODUCTION                                                  | 1   |

| 1.1. Motivation                                                          | 1   |

| 1.2. Literature review                                                   | 2   |

| 1.3. Proposed solution                                                   | 4   |

| 1.4. Thesis contributions                                                | 6   |

| CHAPTER 2: FAILURE MECHANISM OF GaN TRANSISTORS IN<br>POWER APPLICATIONS | 8   |

| 2.1. Characteristics and structure of GaN transistors                    | 8   |

| 2.2. Failure mechanism in power semiconductors                           | 10  |

| 2.2.1. Challenges for reliability evaluation in GaN power<br>devices     | 10  |

| 2.2.2. A review of failure mechanism in previous studies                 | 11  |

| CHAPTER 3: ONLINE PROGNOSTIC IN SWITCHING POWER<br>CONVERTERS            | 13  |

| 3.1. Introduction                                                        | 13  |

| 3.2. Online reliability analysis GaN devices                             | 14  |

| 3.3. GaN Power Converter-Digital Twin                                    | 17  |

| 3.3.1. Thermomechanical susceptibility                                   | 17  |

| 3.3.2. Reliability framework of power converter                          | 17  |

| 3.3.3. Energy-based fatigue failure modeling                             | 18  |

|       | ER 4: I<br>ESSMEN | DEEP LEARNING FOR ONLINE RELIABILITY<br>T                             | 26 |

|-------|-------------------|-----------------------------------------------------------------------|----|

| 4.1.  | Introduc          | tion                                                                  | 26 |

|       | 4.1.1.            | Challenges of using machine learning algorithm<br>(Bayesian model)    | 27 |

| 4.2.  | Recurren          | nt neural networks                                                    | 30 |

| 4.3.  | -                 | arning Reliability Awareness of Converters at the Edge<br>ep RACE)    | 32 |

|       | 4.3.1.            | Long short-term memory                                                | 32 |

|       | 4.3.2.            | Device model training                                                 | 34 |

| CHAPT | ER 5: SY          | STEM INTEGRATION                                                      | 38 |

| 5.1.  | Introduc          | tion                                                                  | 38 |

|       | 5.1.1.            | Real-time edge analysis                                               | 38 |

|       | 5.1.2.            | Data training and batch aggregation on the cloud                      | 38 |

| 5.2.  | Architec          | ture for real-time system monitoring                                  | 39 |

|       | 5.2.1.            | Proposed physics of failure-statistics model using cloud computations | 39 |

|       | 5.2.2.            | Hardware system setup                                                 | 40 |

|       | 5.2.3.            | Prototype robustness verification                                     | 41 |

| CHAPT | ER 6: EX          | PERIMENTAL RESULTS                                                    | 46 |

| 6.1.  | Introduc          | tion                                                                  | 46 |

|       | 6.1.1.            | Experimental training of power transistors                            | 46 |

|       | 6.1.2.            | Hardware setup design and verification                                | 48 |

|       | 6.1.3.            | Power consumption and processing time analysis                        | 52 |

vii

| CHAPTER 7: SMART CURRENT MONITORING IN GaN POWER<br>DEVICES-SENSEGaN             | 58 |

|----------------------------------------------------------------------------------|----|

| 7.1. Introduction                                                                | 58 |

| 7.2. Current mirroring in GaN-SenseGaN                                           | 59 |

| 7.3. SenseGaN characterization                                                   | 61 |

| 7.4. Converter design-simulation analysis                                        | 63 |

| 7.5. Converter design-simulation analysis                                        | 63 |

| 7.6. Converter design-hardware prototype and experimental results                | 65 |

| 7.7. SenseGaN in the BCM control of a DC-DC boost converter                      | 67 |

| 7.8. Proposed boundary conduction mode control In a boost<br>converter           | 69 |

| 7.8.1. Active switch current measurement with SenseGaN                           | 69 |

| 7.8.2. The proposed algorithm for BCM control                                    | 69 |

| 7.9. Experimental verification                                                   | 74 |

| 7.10. Isolated current mirroring in GaN-Iso-SenseGaN                             | 76 |

| 7.11. Iso-SenseGaN characterization                                              | 79 |

| 7.12. Iso-SenseGaN in the BCM control of a DC-DC boost converter                 | 80 |

| 7.13. Iso-SenseGaN in the BCM control of a DC-AC converter                       | 82 |

| CHAPTER 8: CONCLUSIONS                                                           | 87 |

| CHAPTER A: PCB EMBEDDED INDUCTORS FOR HIGH-<br>FREQUENCY POWER CONVERTERS        | 89 |

| CHAPTER B: CURRENT MEASUREMENT TECHNIQUES FOR<br>HIGH-FREQUENCY POWER CONVERTERS | 98 |

viii

# CHAPTER C: ON SELF-HEALING OF SYSTEM LEVEL INVERT-ERS CONSIDERING CURRENT SENSOR INACCURACY AND AGING DEGRADATION

# REFERENCES

119

# LIST OF FIGURES

| FIGURE 1.1: <b>Conceptual matrix</b> : The four major parameters for advanced power electronics converter designs.                                                                                                                                                                | 2  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 1.2: Conventional reliability modeling: Accelerated life<br>tests of hundreds of hours are developed for extracting the math-<br>ematical modeling of device failure.                                                                                                      | 4  |

| FIGURE 1.3: General proposed reliability solution: The proposed framework of Internet of Things reliability analysis using edge/cloud computations for an advanced power electronics converter.                                                                                   | 6  |

| FIGURE 1.4: Thesis framework: The main contributions of this work are provided in eight chapters.                                                                                                                                                                                 | 7  |

| FIGURE 2.1: Lateral GaN structure: The cross section of an enhance-<br>ment GaN.                                                                                                                                                                                                  | 9  |

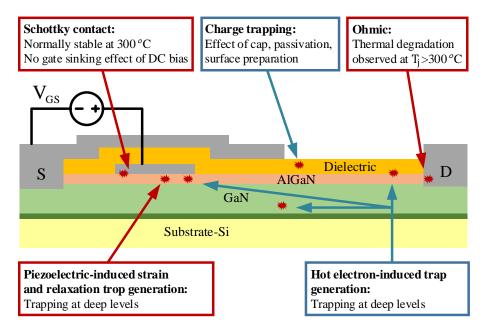

| FIGURE 2.2: Lateral GaN structure: The most susceptible regions in GaN device.                                                                                                                                                                                                    | 12 |

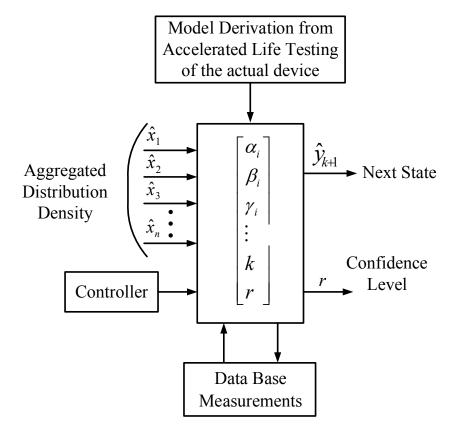

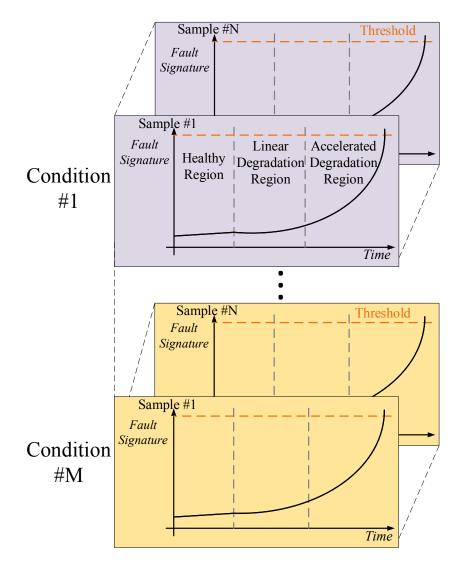

| FIGURE 3.1: Conventional reliability solution: #N samples of devices with #M conditions have been analyzed experimentally under accelerated life tests to find the reliability model. Adaptability with the new technologies and the experimental costs are their main drawbacks. | 15 |

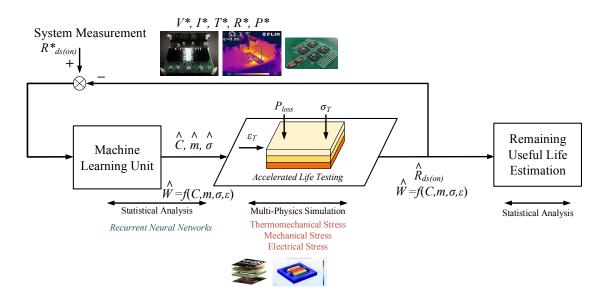

| FIGURE 3.2: <b>Proposed solution</b> : Adaptive prognostics concept using multi-physics co-simulations and machine learning algorithm with advanced monitoring.                                                                                                                   | 16 |

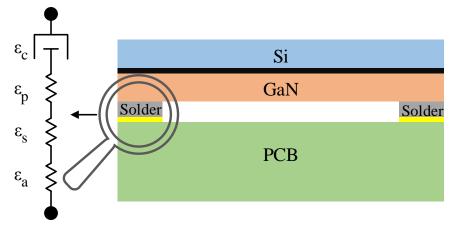

| FIGURE 3.3: Mounted GaN on the PCB: Simplified model of a lateral GaN mounted on the PCB. GaN and Silicon (substrates) are isolated with thin layer of AlGaN, and packaging is not considered in the model.                                                                       | 19 |

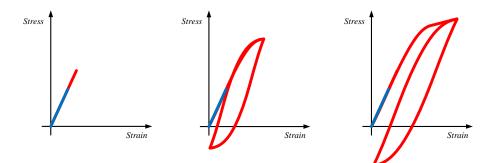

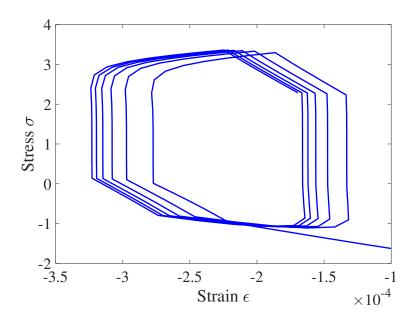

| FIGURE 3.4: The hysteresis loss: Once the nominal mean stress is less than border mean stress (left) vs. the mean stress is higher than the border mean stress (right).                                                                                                           | 21 |

х

| FIGURE 3.5: Proposed framework for GaN power converter-<br>Digital Twin: The online device monitoring, and simulation-based<br>ALT for reliability analysis. A machine learning system is developed<br>for system calibrations and parameter estimations.                                                               | 21 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

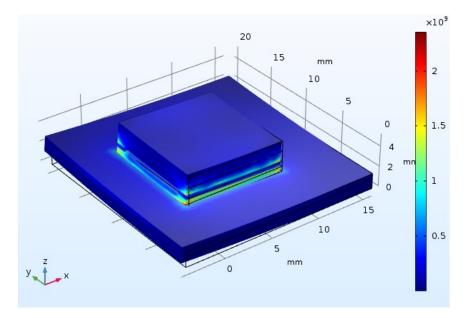

| FIGURE 3.6: Simulation of the accelerated life test: The fatigue failure mode of the lateral GaN device is simulated through the finite element analysis.                                                                                                                                                               | 22 |

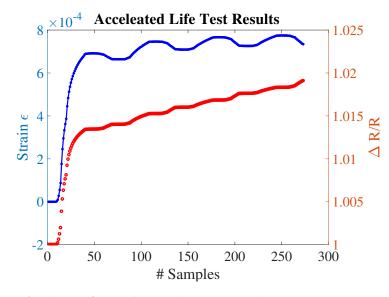

| FIGURE 3.7: Simulation of strain-resistance: The resistance varia-<br>tions and the strain changes are simulation based on the proposed<br>geometry.                                                                                                                                                                    | 23 |

| FIGURE 3.8: Simulation of strain-resistance: The simulated energy<br>loss generated from the stress and strain variation of the joints in the<br>accelerated life analysis.                                                                                                                                             | 24 |

| FIGURE 3.9: Simulation result of the accelerated life test: The variations $R_{ds(on)}$ under temperature cycling due to solder fatigue of GaN on Silicon.                                                                                                                                                              | 24 |

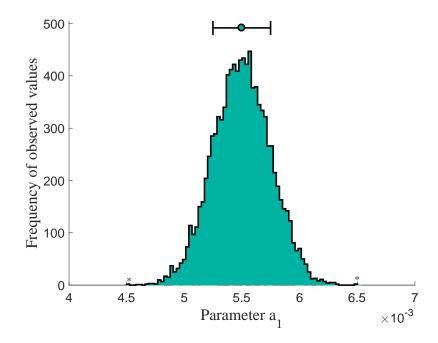

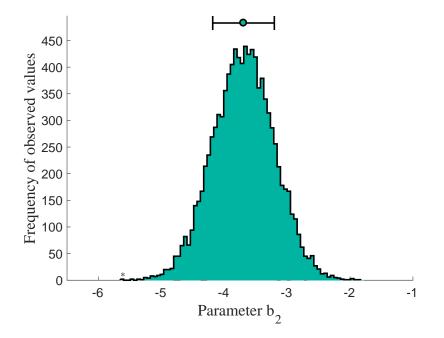

| FIGURE 4.1: <b>Parameter estimation</b> : The probability density function<br>of the posterior as the unknown parameters, and verification MCMC<br>algorithm.                                                                                                                                                           | 29 |

| FIGURE 4.2: <b>Parameter estimation</b> : The probability density function<br>of the posterior as the unknown parameters, and verification MCMC<br>algorithm.                                                                                                                                                           | 29 |

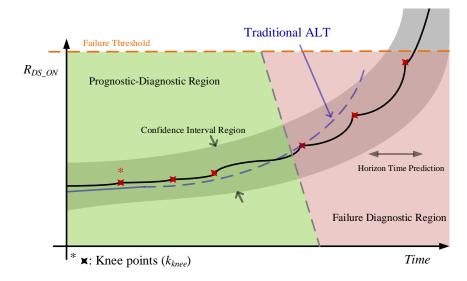

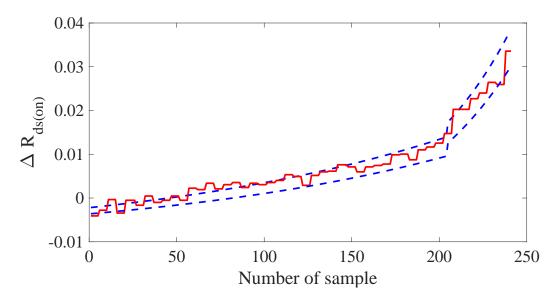

| FIGURE 4.3: <b>Bayesian calibration</b> : The output results of the algorithm for pattern recognition within the confidence interval. Red: drain-source resistance changes, blue: the estimated resistance variation within the specific confidence level after the data filtering and highlighted near the knee point. | 30 |

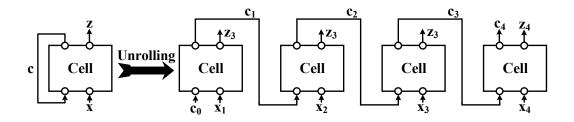

| FIGURE 4.4: <b>Recurrent Neural Networks</b> : The schematic of standard<br>RNN cell and its unrolling version for four input time sequence                                                                                                                                                                             | 31 |

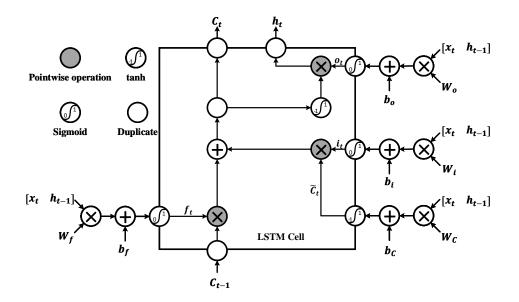

| FIGURE 4.5: A single LSTM cell: Inside of an LSTM cell consisting of three gates and the state of the cell is preserved by variable $c_t$ .                                                                                                                                                                             | 33 |

| FIGURE 4.6: Batch tensor configuration: Three dimensional batch tensor with a characterized vector $R_{mt}^k$ .                                                                                                                                                                                                         | 34 |

xi

|                                                                                                                                                                                                                                                                                                                           | xii |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

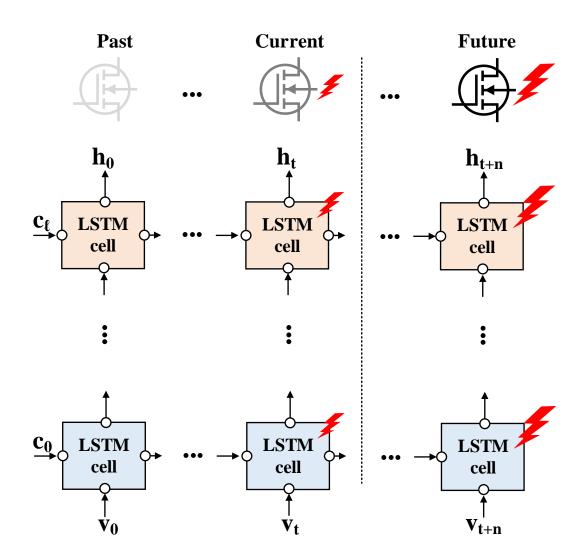

| FIGURE 4.7: The stacked LSTM: An unrolled LSTM cell predicts the next $n$ samples of $\Delta R_{ds(on)}$ based on last sensed data.                                                                                                                                                                                       | 35  |

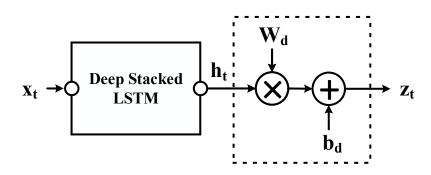

| FIGURE 4.8: The proposed deep LSTM network model: A lin-<br>ear layer is added to the deep stacked LSTM to map $h_t$ to on-line<br>measured $\Delta R$ at time t.                                                                                                                                                         | 36  |

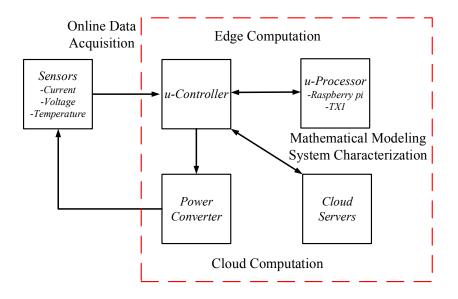

| FIGURE 5.1: The edge node diagram: It consists of a $\mu$ -controller and AI SoC to generate gate signals and predict the trajectory resistance of power transistor.                                                                                                                                                      | 39  |

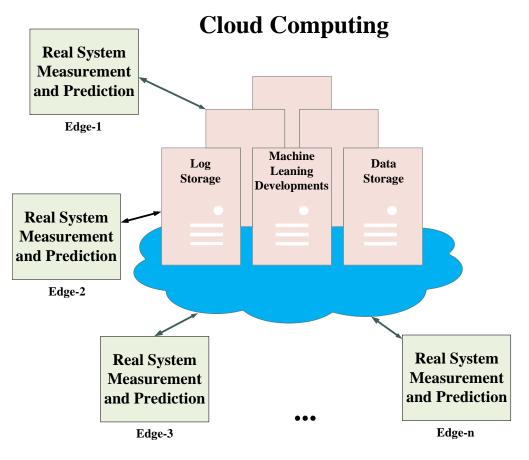

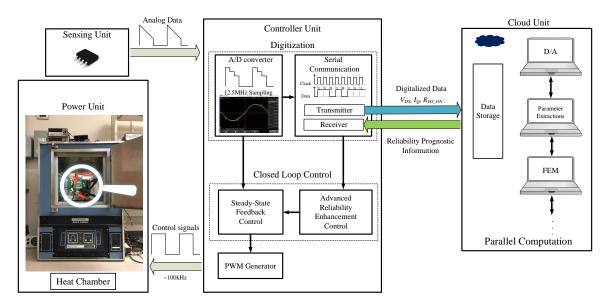

| FIGURE 5.2: New IoT approach for reliability assessment: DAS for<br>characterization of power converters, and multi-process computation<br>on cloud networks. The proposed infrastructure architecture provides<br>feasibility of data-processing techniques for adaptive prognostics in<br>power electronics converters. | 41  |

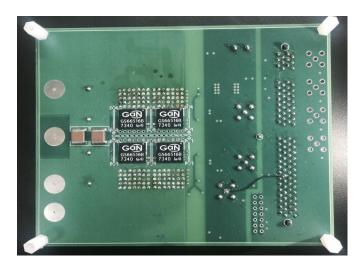

| FIGURE 5.3: <b>Hardware prototype</b> : The buck converter designed in four layers.                                                                                                                                                                                                                                       | 42  |

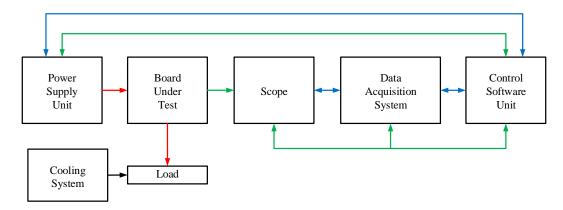

| FIGURE 5.4: <b>Data acquisition system</b> : Supervisory system control was designed for data collection and converter protection. red: power path, blue: control signals, and green: sensing signals.                                                                                                                    | 43  |

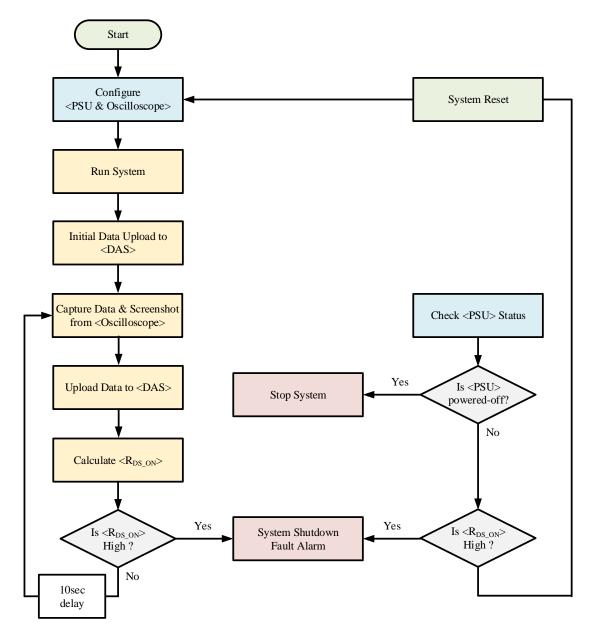

| FIGURE 5.5: <b>Data acquisition system</b> : The thread is provided for device characterization and resistance measurement.                                                                                                                                                                                               | 44  |

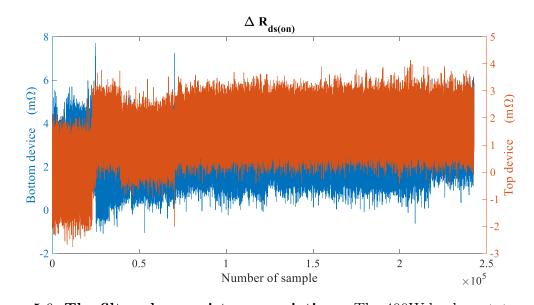

| FIGURE 5.6: The filtered on-resistance variations: The 400W buck<br>prototype was tested over 30G cycles with continuous operation at<br>100kHz switching frequency, and drain-source resistance variations<br>was captured automatically.                                                                                | 45  |

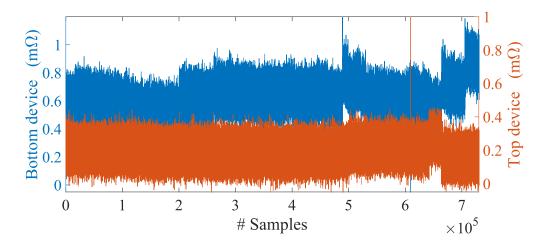

| FIGURE 5.7: The filtered on-resistance variations: The buck converter was tested over 100 billion electrical cycles $400W$ and $100kHz$ . The drain-source on-resistance variations was captured automatically, and stored on the cloud networks.                                                                         | 45  |

| FIGURE 6.1: The proposed reliability solution: The advanced solution leverages the benefits of Internet of Things for reliability analysis using edge/cloud.                                                                                                                                                              | 46  |

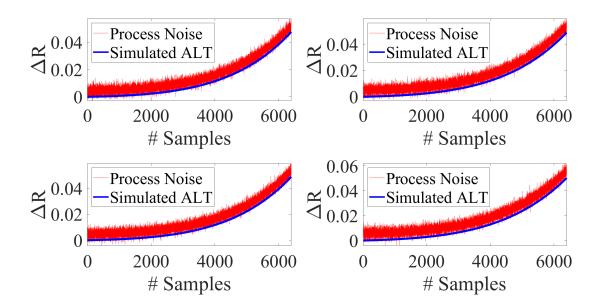

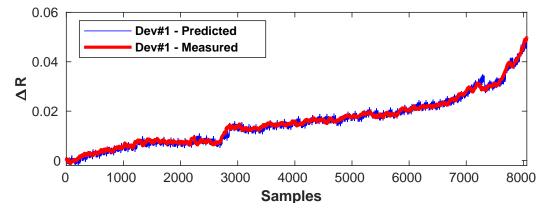

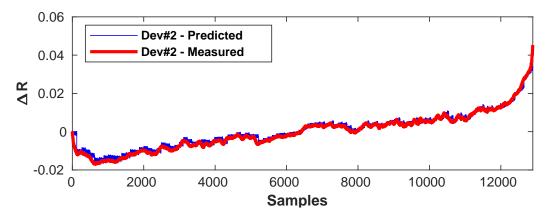

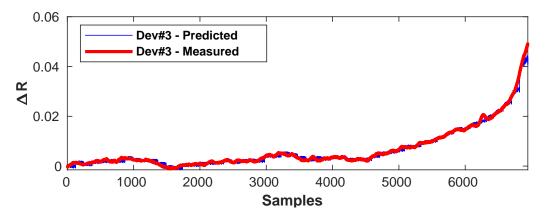

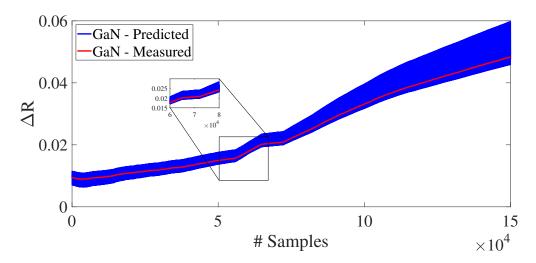

| FIGURE 6.2: <b>Experimental results:</b> The prediction of $\Delta R_{ds(on)}$ variations of device-1 through Deep RACE method.                                                                                                                                                                                           | 48  |

| FIGURE 6.3: <b>Experimental results:</b> The prediction of $\Delta R_{ds(on)}$ variations of device-2 through Deep RACE method.                                                                                                                                  | 49 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 6.4: <b>Experimental results:</b> The prediction of $\Delta R_{ds(on)}$ variations of device-3 through Deep RACE method.                                                                                                                                  | 49 |

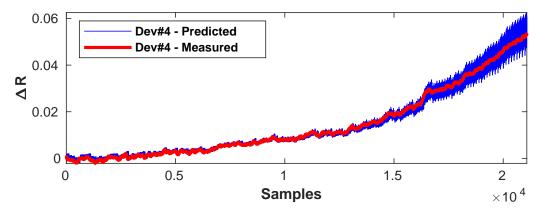

| FIGURE 6.5: <b>Experimental results:</b> The prediction of $\Delta R_{ds(on)}$ variations of device-4 through Deep RACE method.                                                                                                                                  | 49 |

| FIGURE 6.6: <b>Experimental results:</b> The prediction of $\Delta R_{ds(on)}$ variations of device-5 through Deep RACE method.                                                                                                                                  | 50 |

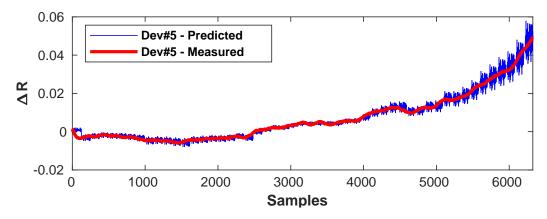

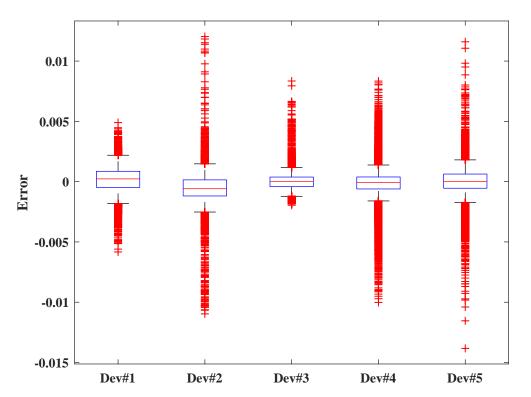

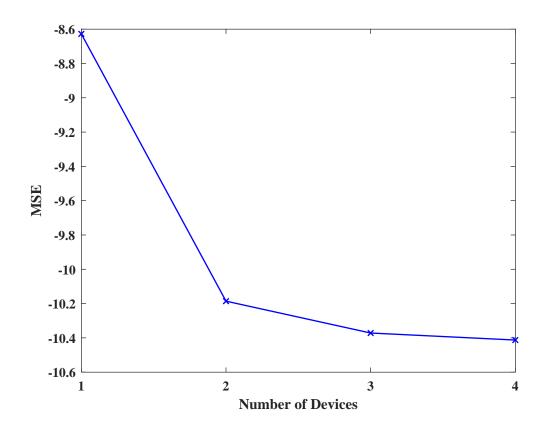

| FIGURE 6.7: Error distribution: The box plot of errors for five power modules.                                                                                                                                                                                   | 51 |

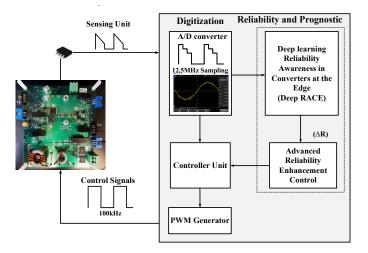

| FIGURE 6.8: The egde node diagram: It consists of a $\mu$ -controller and AI SoC to generate gate signals and predict the trajectory resistance of power transistor.                                                                                             | 52 |

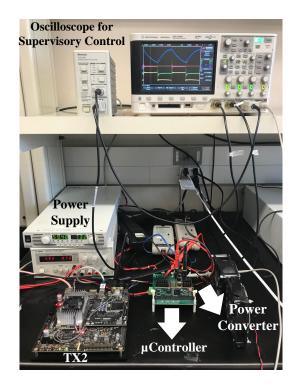

| FIGURE 6.9: <b>Experimental verification</b> : The hardware setup was implemented including the high-frequency power converter controller by $\mu$ -controller, the SoC-TX2 for edge computation. The supervisory control is designed for the safety protection. | 54 |

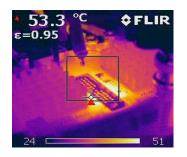

| FIGURE 6.10: <b>Experimental verification</b> : Temperature rise control of the converter through thermal image.                                                                                                                                                 | 54 |

| FIGURE 6.11: <b>Prognostic results</b> : The $R_{ds(on)}$ variations for GaN with Si-substrate using the FEA simulations, and only one set of data for training.                                                                                                 | 55 |

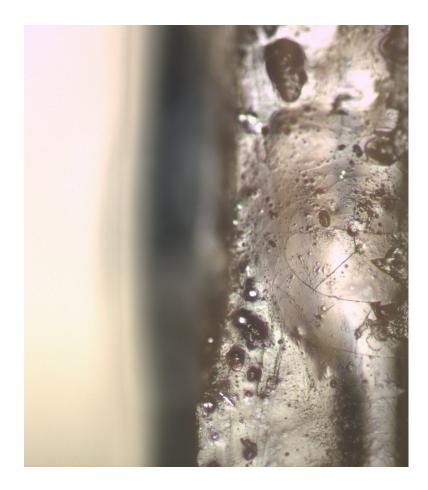

| FIGURE 6.12: <b>Experimental results</b> : The solder degradation is observed on the source of GaN power devices in the defected device of the buck converter.                                                                                                   | 56 |

| FIGURE 6.13: <b>Experimental results</b> : The solder degradation is not observed on the source and drain of GaN power devices in the healthy device of the buck converter.                                                                                      | 57 |

xiii

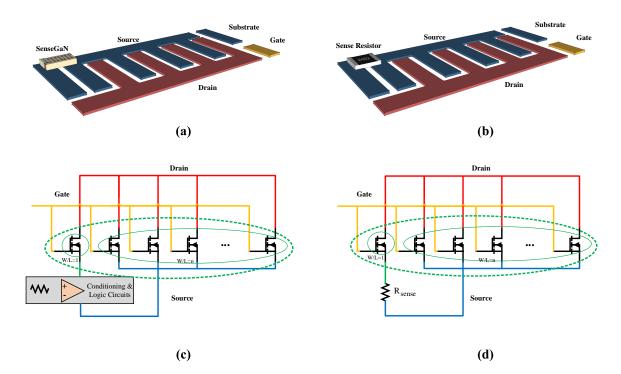

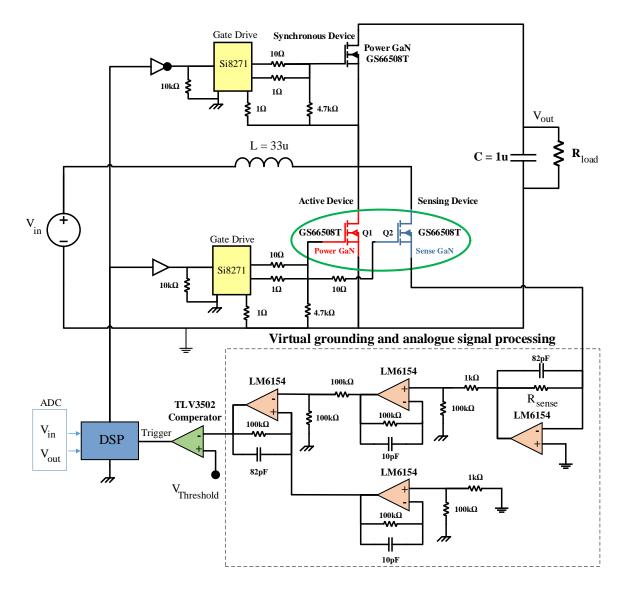

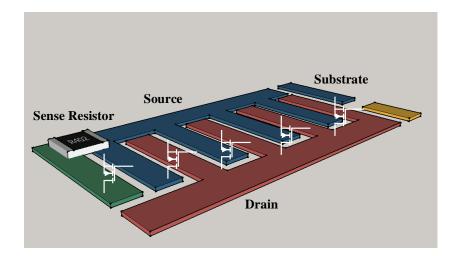

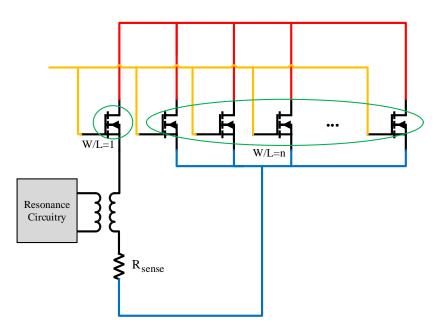

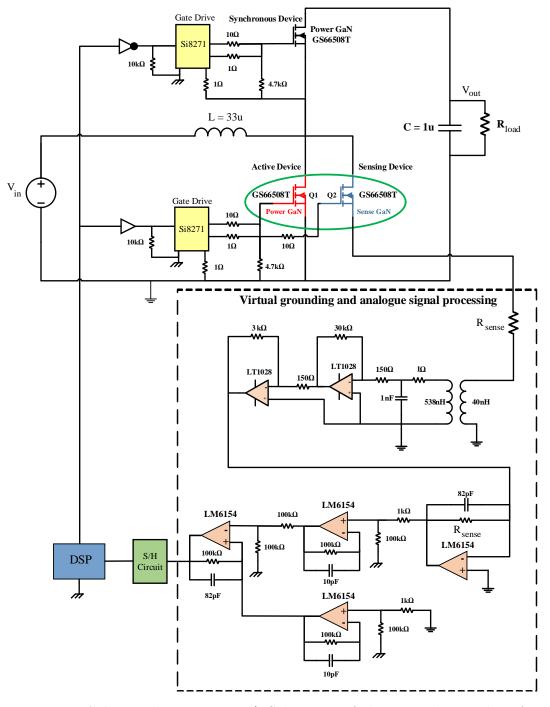

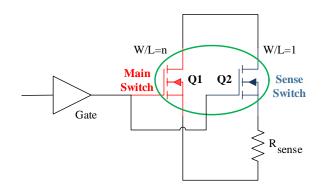

- FIGURE 7.1: SenseGaN configuration: Proposing a scheme of SenseGaN for lateral dies based on available commercial products. (a): shows the geometry of SenseGaN die with virtual grounding to compensate thermal coupling and impedance matching. (b): represents the geometry of SenseGaN dies with Sense resistor without virtual ground compensation. (c): shows the equivalent electrical circuit model of SenseGaN with virtual grounding. This section will include all the logic circuits in a die interconnected into the power transistor. (d): shows the equivalent electrical circuit model of Sense resistor for a single switch.

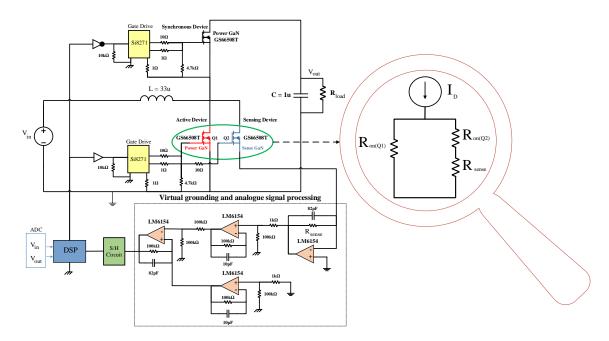

- FIGURE 7.2: Schematic capture: Schematic of implemented virtual

grounding for SenseGaN technique in a GaN boost converter. The

virtual grounding circuit guarantee the tight connection of GaN

power (Q1) and Sensing GaN (Q2) and consequently more accurate

monitoring of the main current. The zoomed-in of the circuit shows

the main current stream for temperature variation characterization.

- FIGURE 7.3: **Spice simulation results**: SenseGaN in two different scenarios. blue: inductor current, orange: measurement with SenseGaN circuit a) sensing resistor is  $1\Omega$ , b) sensing resistor is  $1k\Omega$ . As it shown choosing higher resistance would impact the sensing significantly. For these devices, it is recommended to use sensing resistor  $<20\Omega$  to compromise between higher efficiency and system robustness performance.

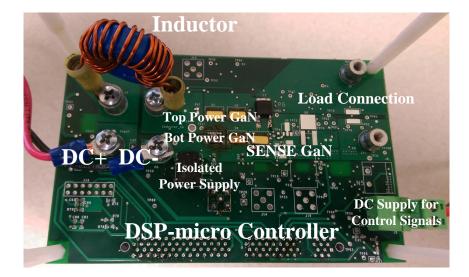

- FIGURE 7.4: Hardware setup: The prototype was designed in fourlayers: Top layer: Power stage, Inner layer-1: Power ground, Innerlayer-2: Shield layer, Bottom layer: Control signals and conditioningcircuits.

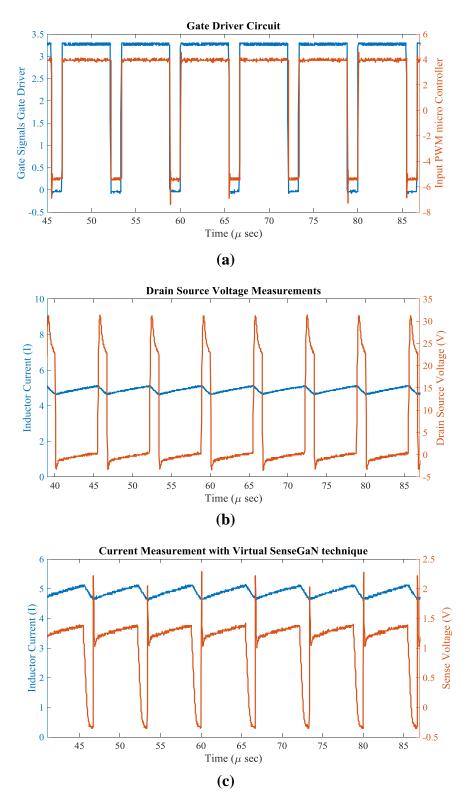

- FIGURE 7.5: Experimental results: a) blue: input gate signal from micro controller, and orange: output gate signals of the isolated gate driver. b) blue: inductor current measured with amplifier current gun, orange: drain-source voltage of the converter c) blue: inductor current measured with amplifier current gun, orange: current measurement with SenseGaN 150kHz, 5A boost power converter.

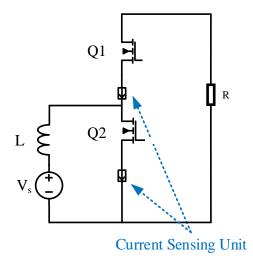

- FIGURE 7.6: Schematic capture: The boost operation system with 68 SenseGaN and control units.

xiv

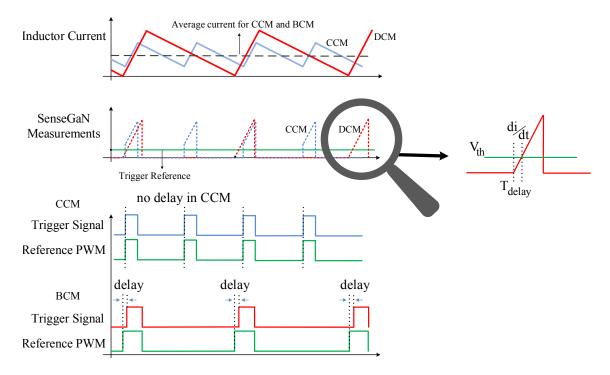

60

66

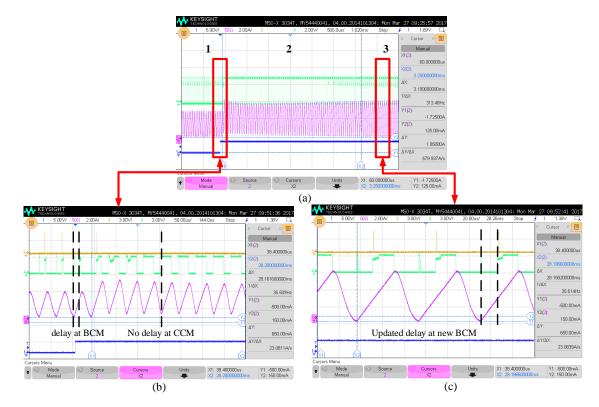

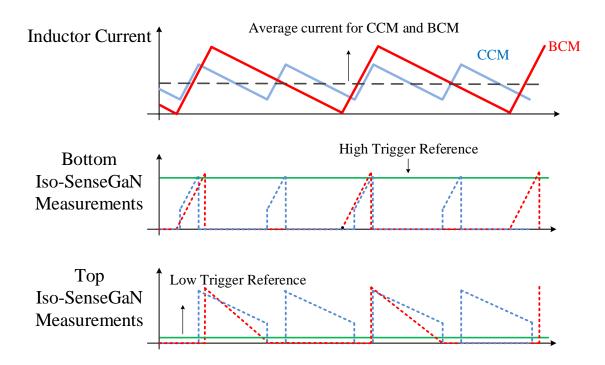

| FIGURE 7.7: The system operation mode and curser identifi-<br>cations: a) The inductor current at CCM (blue) and BCM (red)<br>with the same average current. b) The current monitoring with the<br>SenseGaN for the active device in CCM and BCM. (here, the zoomed-<br>in version of threshold trigger reference signal for delay generation is<br>exposed) c) The microcontroller compares the trigger reference signal<br>generated by the comparator and PWM signals to generate the delay<br>signal in CCM and BCM.                                                                                               | 70 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

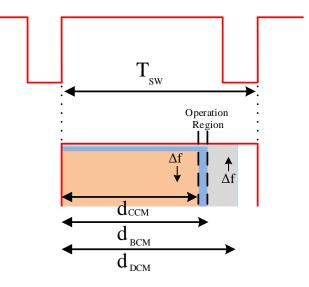

| FIGURE 7.8: The system operation modes: The operational regions<br>for distinguishing CCM, BCM, and DCM in a single cycle. Orange:<br>CCM, Blue: Optimum region for BCM, Gray: DCM.                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71 |

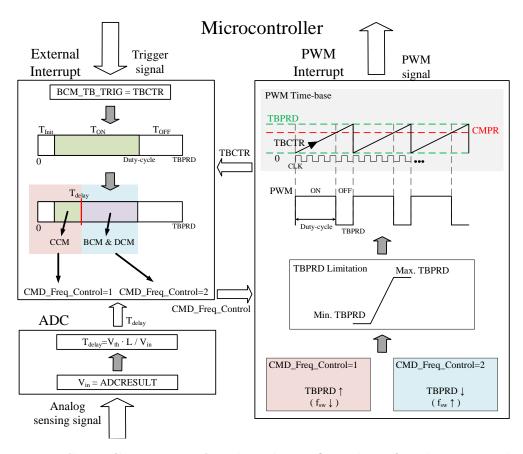

| FIGURE 7.9: SenseGaN control: The scheme flow chart for the proposed BCM control algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72 |

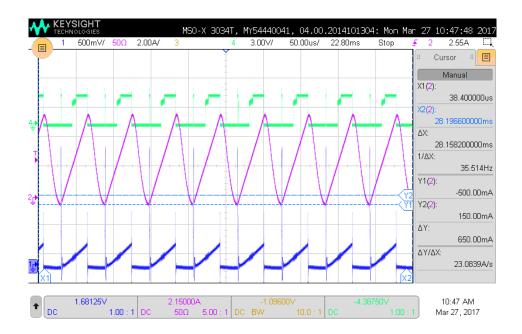

| FIGURE 7.10: <b>Experimental results</b> : SenseGaN operation at 2.5A with 350mV/A sensitivity. Purple: inductor current measurement (amplifier current gun), Blue: SenseGaN measurement, Green: generated trigger signal from the analogue comparator (TLV3502).                                                                                                                                                                                                                                                                                                                                                      | 73 |

| FIGURE 7.11: Experimental results: Implementation of BCM in a<br>boost converter with SenseGaN. Purple: inductor current measured<br>with an amplifier current gun, Green: generated trigger signal with<br>the fast comparator Blue: trigger signal for load change. a) Con-<br>verter operation at different CCM and BCM regions. b) Initial BCM<br>condition (duty cycle: 40%), and transient to CCM (60%) c) New<br>BCM steady-state condition for higher current after implementing<br>the iterative control scheme. Delay detection between trigger signal<br>and PWMs are highlighted in BCM and CCM operation. | 75 |

| FIGURE 7.12: Iso-SenseGaN configuration: Proposing a scheme of Iso-SenseGaN for lateral dies based on available commercial products.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76 |

| FIGURE 7.13: <b>Iso-SenseGaN</b> : The equivalent circuit model of the Iso-SenseGaN for the available lateral GaN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77 |

| FIGURE 7.14: Schematic capture: a) Schematic of the virtual ground-<br>ing for Iso-SenseGaN technique with galvanic isolation in a GaN<br>boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 78 |

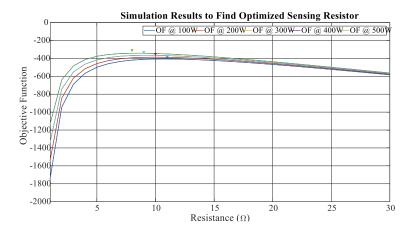

| FIGURE 7.15: <b>Optimization in SenseGaN</b> : The compromise of higher performance (low resistance) vs. lower loss (high resistance) are analyzed in the OF.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80 |

$\mathbf{X}\mathbf{V}$

|                                                                                                                                                                                                                                                                                                             | AVI |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

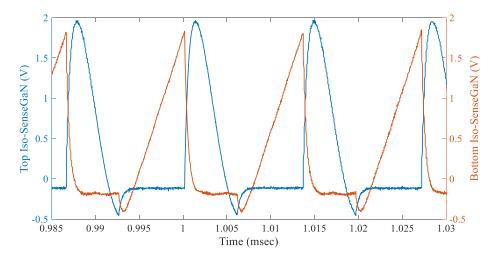

| FIGURE 7.16: <b>BCM control of a DC-DC boost converter</b> : the system operation mode at the CCM (blue) and the BCM (red) with the same average current.                                                                                                                                                   | 80  |

| FIGURE 7.17: <b>BCM control of a DC-DC boost converter</b> : the current monitoring reflected in the Iso-SenseGaN. Two reference trigger signals are considered to turn-on the top and bottom devices consecutive.                                                                                          | 81  |

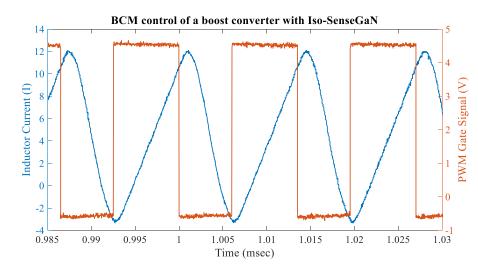

| FIGURE 7.18: <b>BCM control of a DC-DC boost converter</b> : orange: PWM gate signals, blue: inductor current.                                                                                                                                                                                              | 82  |

| FIGURE 7.19: <b>BCM control of a DC-DC boost converter</b> : orange: bottom Iso-SenseGaN, blue: top Iso-SenseGaN outputs.                                                                                                                                                                                   | 82  |

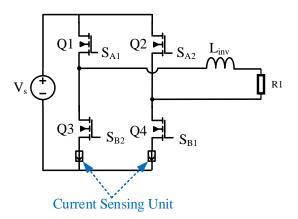

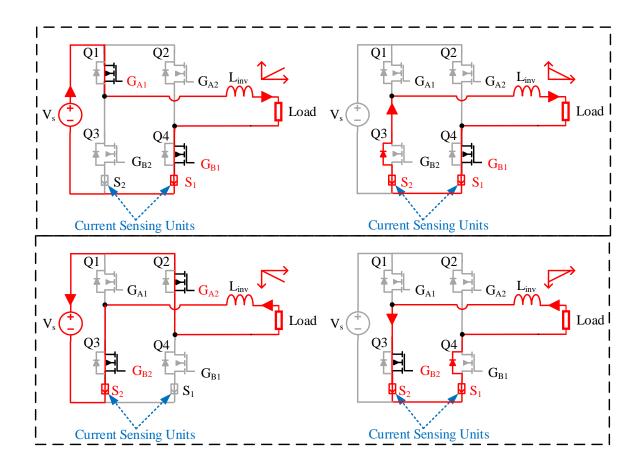

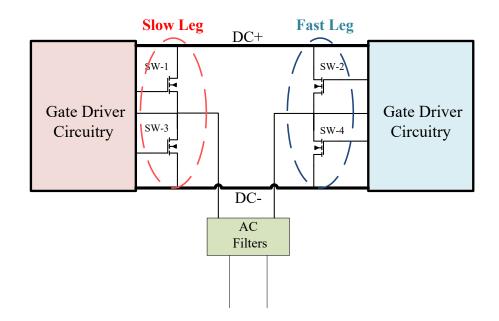

| FIGURE 7.20: (Iso)SenseGaN for the BCM control of a DC-AC converter: The proposed architecture for the sensor placement in an inverter.                                                                                                                                                                     | 83  |

| FIGURE 7.21: <b>Inverter operation</b> : The system operation for the BCM operation in the inverter, proposed by SenseGaN current mirroring techniques. The current path highlighted with red one shows the four modes of operation.                                                                        | 83  |

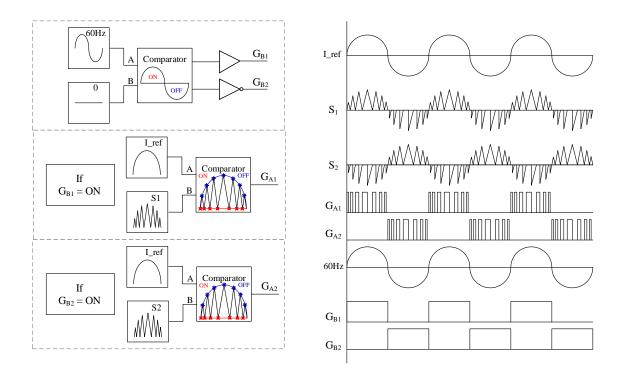

| FIGURE 7.22: <b>Proposed BCM technique</b> : The analogue circuit logics<br>for PWM generation through SenseGaN and the fundamental fre-<br>quency of the grid.                                                                                                                                             | 84  |

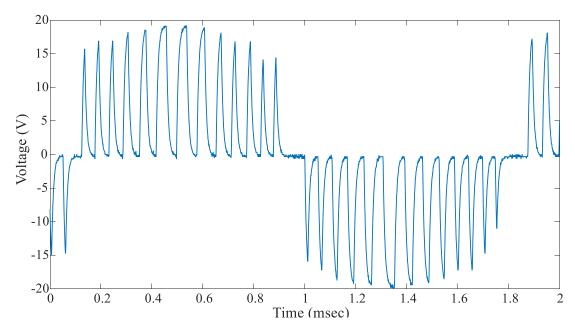

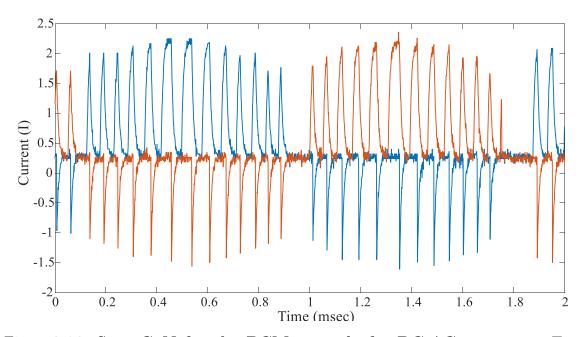

| FIGURE 7.23: SenseGaN for the BCM control of a DC-AC con-<br>verter: Two reference trigger signals are considered to turn-on the<br>bottom devices consecutively. The closed loop operation of the DC-<br>AC converter operation is verified in CHIL (blue: grid voltage)                                   | 85  |

| FIGURE 7.24: SenseGaN for the BCM control of a DC-AC con-<br>verter: Two reference trigger signals are considered to turn-on the<br>bottom devices consecutively. The closed loop operation of the DC-<br>AC converter operation is verified in CHIL (top: bottom SenseGaN-1,<br>orange: bottom SenseGaN-2) | 85  |

| FIGURE A.1: Schematic configuration: The hybrid sinusoidal unipo-<br>lar DC-AC converter topology considering one leg as fast switching,<br>the second leg switching with grid frequency.                                                                                                                   | 91  |

xvi

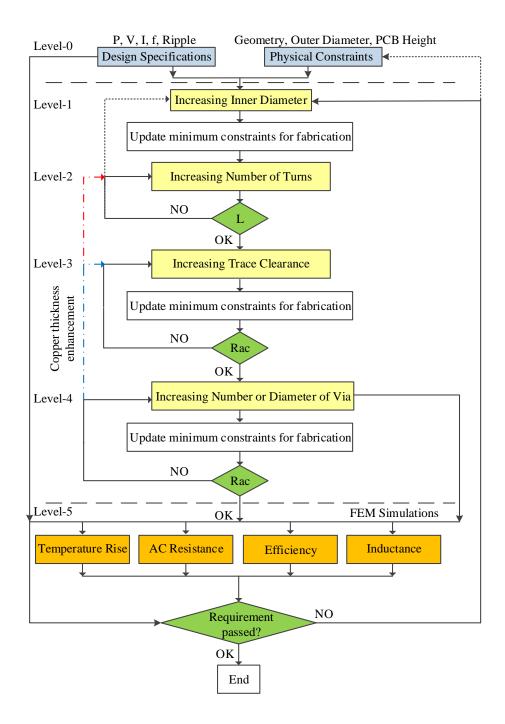

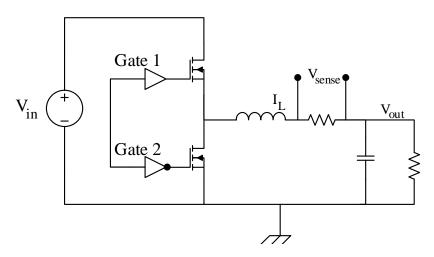

- FIGURE A.2: **Optimization approach**: The algorithm descriptions to achieve the lowest resistance at the highest possible power density for the PCB embedded inductor within the 1-10MHz.

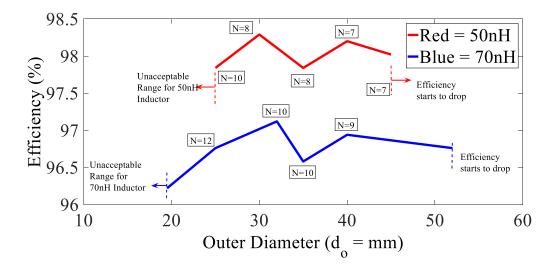

- FIGURE A.3: Numerical results: The algorithm procedure for providing possible solutions for power density, and filtering requirements meeting from level-0 to level-2 based on proposed method. The selected candidate will be highlighted when the multiplying of the concavity and the derivative of function reach to optimum values. The possible solutions can be used for running the algorithm from level-3 to level-5.

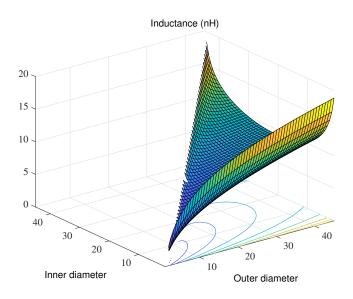

- FIGURE A.4: Simulation results: The efficiency variations of the constant inductance with the minimum possible resistance, at the specific allocated area, are depicted through the algorithm. This shows that a high efficient inductor can be achieved in various geometry configurations with different outer diameter and number of turns; however, the smaller size is more desired to reach higher power density. The inner diameter of the inductor is set to 15mm to keep the temperature rise lower than 40C for 18A. This provides a comprehensive legend for PCB embedded inductor designers in the defined frequency and power range.

- FIGURE B.1: Shunt method: Schematic of external sense resistor for 100 capturing the inductor and output current. The voltage drop across the resistor theoretically can represent the actual current waveform; however, this method in practice has a lot of issues for high-frequency and high current applications.

- FIGURE B.2: SenseFET: General scheme of SenseFET. This technique should be implemented in an integrated package for higher performances.

- FIGURE B.3: Filter method: General schematic of filter-based current 102 sensing. The active calibration for the passive element is required, and the common-mode voltage issue still exists in this approach.

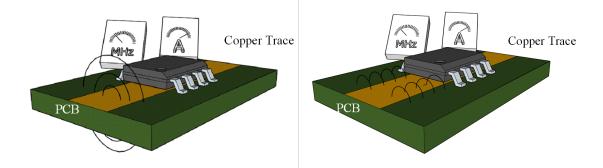

- FIGURE B.4: Magneto-Resistors sensor: General operation of the 105 contact-less AMR sensor: magnetic field generations at low frequency (left) and high-frequency (right) are shown.

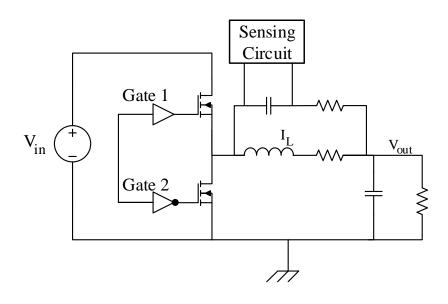

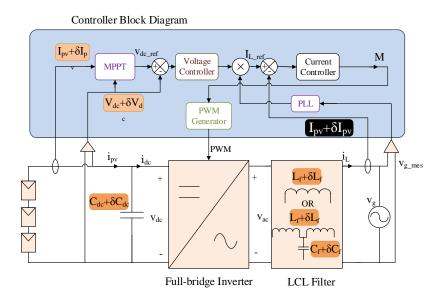

- FIGURE C.1: **PV inverter schematic**: The proposed scheme for a 110 single phase inverter with the control architecture

xvii

94

97

97

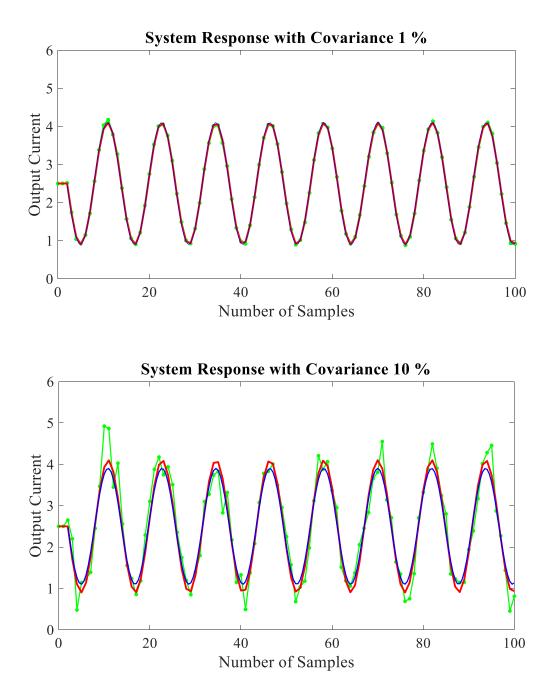

| FIGURE C.2: Simulation results: The current sensor response under<br>two different covariance measurement errors (1% and 10%). blue:<br>ideal waveform, green: actual system reference response, red: modi-<br>fied system response correction with Kalman filter estimation.                                                                                                                                               | 111 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

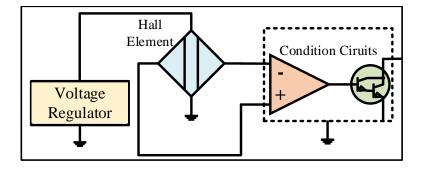

| FIGURE C.3: <b>Current sensor model</b> : The scheme of Hall-Effect current sensor for age modeling.                                                                                                                                                                                                                                                                                                                        | 113 |

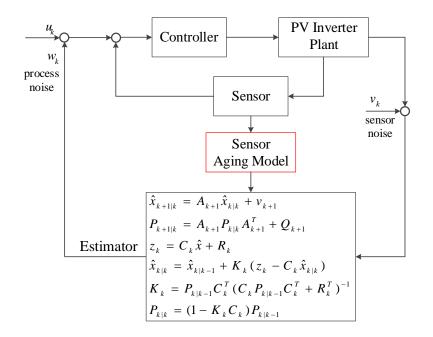

| FIGURE C.4: <b>Self-healing scheme</b> : The proposed scheme for modified model of the PV inverter system considering the sensor characteristics and Kalman filter estimator.                                                                                                                                                                                                                                               | 114 |

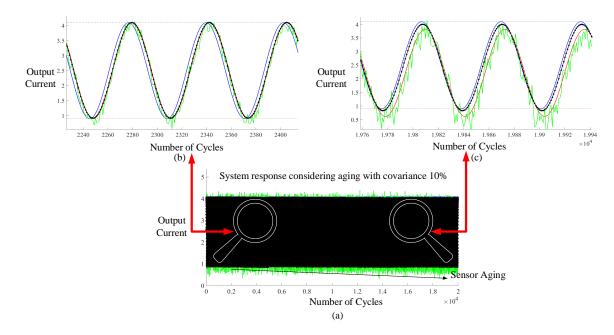

| FIGURE C.5: Simulation results: The estimation results considered<br>by a Kalman filter to the modified model of current sensor aging.<br>The system response is modeled with 10% covariance error of the<br>current sensor and shown based during the aging process. blue: ideal<br>waveform, green: actual sensor measurement, red: system response<br>correction with Kalman filter without aging considerations, black: | 117 |

system response correction with Kalman filter considering the aging

process.

xviii

# LIST OF TABLES

| TABLE 2.1: Summary of main failure mechanisms in GaN power                                                                         | 11  |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| TABLE 3.1: Stress-strain parameters for the simulation analysis                                                                    | 20  |

| TABLE 3.2: Selected device characteristics comparisons for converter<br>design                                                     | 25  |

| TABLE 5.1: Components in Converter Circuit Design                                                                                  | 42  |

| TABLE 6.1: The parameters for LSTM network training                                                                                | 47  |

| TABLE 6.2: Prediction error for the power MOSFET transistors                                                                       | 50  |

| TABLE 6.3: The comparison of absolute average error of Deep RACE with the others                                                   | 51  |

| TABLE 6.4: nVidia TX2 embedded module specification                                                                                | 53  |

| TABLE 6.5: TX2 embedded board power consumption                                                                                    | 53  |

| TABLE 7.1: Components in converter circuit design                                                                                  | 86  |

| TABLE A.1: Summary of important research on PCB inductors for power<br>applications                                                | 92  |

| TABLE C.1: Selected parameter for model development                                                                                | 116 |

| TABLE C.2: Robustness comparison for single phase PV inverter under<br>different current sensing inaccuracies without compensation | 118 |

| TABLE C.3: Robustness comparison for single phase PV inverter under<br>different current sensing inaccuracies with compensation    | 118 |

## LIST OF ABBREVIATIONS

- 2DEG Two-Dimensional Election Gas

- ADC Analogue to Digital Converter

- ALT Accelerated Life Test

- BCM Boundary Conduction Mode

- BPTT Back Propagation Through Time

- CCM Continuous Conduction Mode

- CHIL Controller Hardware-In-the-Loop

- CMPR Counter Compare Register

- CTE Coefficient of Thermal Expansion

- DAS Data Acquisition System

- DCM Discontinuous Conduction Mode

- DUT Device Under Test

- EMI Electromagnetic Interfaces

- FEA Finite Element Analysis

- FET Field Effective Transistors

- GaAs Gallium Arsenide

- GaN Gallium Nitride

- HEMT High Electron Mobility Transistors

- IGBT Insulated Gate Bipolar Transistor

### IoT Internet of Things

- LSTM Long Short-Term Memory

- MCMC Monte Carlo Markov Chain

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MPPT Maximum Power Point Tracking

- MR Magnetoresistance

- MSE Mean Square Error

- PF Power Factor

- PoF Physics of Failure

- PV Photovoltaic

**RLHS** Random Latin Hypercube Sampling

**RNN** Recurrent Neural Network

Si Silicon

SiC Silicon Carbide

SIRI Smart Inverter Robustness Index

SMPS Switch Mode Power Supply

TBCTR Time-based Counter Register

TBPRD Time Based Period Register

THD Total Harmonic Distortion

WBG Wide Bandgap

XINT External Interrupt

ZCD Zero Current Detection

# CHAPTER 1: INTRODUCTION

#### 1.1 Motivation

Over the years, many solutions have been proposed to convert the primary source of energy to the electricity. Despite all the novel techniques to improve the quality and the conversion efficiency, more than 40% of the primary energy got lost [1]. Power electronics systems can provide effective solutions due their reliable, efficient, smaller footprint and weight in the wide range of applications as high voltage direct current, motor drives, distributed energy sources, solid-state transformers, transportation systems, data centers, and etc. Due to significant progress of consumer electronics in recent years, it is expected by 2030, the power electronics will be used in 80% of applications somewhere from generation to end-users [2].

Having advanced Wide Band-gap (WBG) technologies such as Silicon Carbide (SiC), Gallium Arsenide (GaAs), Aluminum Nitride (AlN), Boron Nitride (BN), and Gallium Nitride (GaN) are crucial to meet the progressive trends in future. For the power applications (< 650V), GaN semiconductor is a promising solution for many due to their superior performance regarding conduction loss, switching loss, thermal resistance. Although GaN devices theoretically are more reliable compared to the existing Si-based technologies, however, lack of available data sets do not exist to guarantee their reliable service over the time. Lack of this information will significantly impact maintenance scheduling for large companies and utilities.

This dissertation focuses on the challenges on the reliability of GaN power devices, and explicitly proposes a new cost-effective framework online reliability assessment of high-frequency GaN power converters.

#### 1.2 Literature review

In today's world, for practical implementation and proper functionality of switching power supplies, several main performance factors are considered: efficiency, size, cost, and the reliability. The advancement material, digital processors, and power semiconductors provide new opportunity to reach beyond the former limits quickly. Depending on the usage, some of these factors could be highlighted more than the others; however, due to the dependability of many applications to switching power converters, these days we need to improve all these factors (Fig. 1.1) at the same time. The dependability in power electronics converters makes the reliability very critical from component level manufacturing to system level engineering.

Figure 1.1: **Conceptual matrix**: The four major parameters for advanced power electronics converter designs.

Many studies have been dedicated to analyzing the reliability of power electronics systems under electrical loading, environmental conditions, and mechanical stresses over the years. In one of the most comprehensive survey-based studies over 200 products of 80 companies, solder and semiconductors are responsible for 34% of the failure, capacitors 30%, Printed Circuit Board (PCB) for 26%, and the rest goes to connectors and different facts [3, 4]. Therefore, many reliability analysis dedicated to power semiconductors and capacitors. Many researchers spend significant time to study capacitor failures. The outcome is that a capacitor is among the weakest link, which degrades quite fast over thermal and electrical stresses. In digitally controlledpower converters, the failure diagnostic in capacitors are relatively straightforward. The ripple current/voltage variations, changes of equivalent series resistance, and capacitance are the most common techniques for diagnostics of failure in capacitors [5, 6].

In power semiconductor modules duo to significant higher stress on power semiconductor modules and continuous progress of devices, vast studies carried out and still the research is continuing. For instance, in Si-based power modules such as Metal Oxide Semiconductor Field Effect Transistor (MOSFET) and Insulated Gate Bipolar Transistor (IGBT), the failure mechanisms are categorized into two groups as extrinsic and intrinsic failures. The extrinsic failures include the transistor packaging issues that are mainly summarized as a bond-wire lift, die solder detachment, and contact migration [7, 8]. The intrinsic refers to failure damages coming from the semiconductor itself. Most common failures of intrinsic types are the dielectric breakdown, time-dependent dielectric breakdown, electromigration [9, 10, 11, 12].

In recent years, thanks to the development and growth of WBG devices, efficient, lighter, and reliable power converter will be promised to the industry. The WBG materials have much higher energy band-gap compared to Si, which enables a new path for operating at higher temperature and power.

Although technically the WBG-based power converter should be more reliable due to their higher activation of energy, practically due to continuous improvement of cost-effective device packaging, the reliable operation of these compound semiconductors is unknown. There are some research papers and industrial reports dealing with the reliability analysis of Si devices and recently SiC devices, whereas there are few reports on GaN power devices. Recent studies focus on single device performance in DC operation for power and thermal cycling like most reliability study. The Weibull distribution has historically been the best tool for describing the reliability engineers in probability prediction of failures over time. While this technique is very accurate at describing failure distributions for large populations of components, it works very poorly at predicting the time until failure of an individual component Fig. 1.2. Moreover, the proposed techniques are very expensive (time, and cost), and their adaptability for the new technologies should be examined fundamentally. Therefore, there is a need to rethink about the reliability platform establishing for failure pattern recognition.

Figure 1.2: Conventional reliability modeling: Accelerated life tests of hundreds of hours are developed for extracting the mathematical modeling of device failure.

### 1.3 Proposed solution

In this dissertation, the goal is to characterize and recognize the component-wise pattern variations through the actual measurement of the GaN power devices in a power converter. Therefore, a new concept of reliability analysis is proposed, and the main contributions are presented as follows:

a) Data collection for fault diagnostic and risk analysis through the state of the high-frequency current solutions. This part mainly focuses on gathering data related to the failure mechanism of the devices to run advanced learning methods.

b) From the available data, the advanced learning methods should be processed to be able to extract the proper information to be able to analyze the power converter reliable, safe and healthy operation shown in Fig. 1.3. In this framework, the machine learning technique will be used to be able to find the correlations between unknown physical and mathematical equations.

c) Proposing mathematical modeling from the existing technologies of GaN devices used in power converter, and calibrating them for advanced learning.

The behavior of the device during normal operation and the degradation region will be analyzed. The features associated with the failure will be extracted using Recurrent Neural Network (RNN) method, and the faulty device will be recognized. Once the healthy pattern versus defective device got identified as the base of training the data, the new data sets will be predicted with the actual measurement of the device. In general, the process could be analyzed either through edge computation in the microprocessor as cloud computations where the cloud servers are located for the captured data. In this thesis the cloud server computation was used for easier implementation; however, the possibility of edge computation was also examined.

As it mentioned above, most of the commonly applied techniques relied on the Accelerated Life Test (ALT) of the actual device as Device Under Test (DUT) to apply harsh testing and be able to find the suitable regions of the devices through the Physics of Failure (PoF). In our proposed method, the Finite Element Analysis (FEA) will be used, and the ALT will be implemented in the simulation platform. As we expect the simulation modeling might not be accurate in the beginning state due to lack of the previous model of a device or converter, the active calibration

Figure 1.3: General proposed reliability solution: The proposed framework of Internet of Things reliability analysis using edge/cloud computations for an advanced power electronics converter.

method will be used to reduce the computation error over the time through the actual measurements. This eventually leads to finding cheaper, and adaptable solution as more data will be collected, and the simulation could be calibrated over the time.

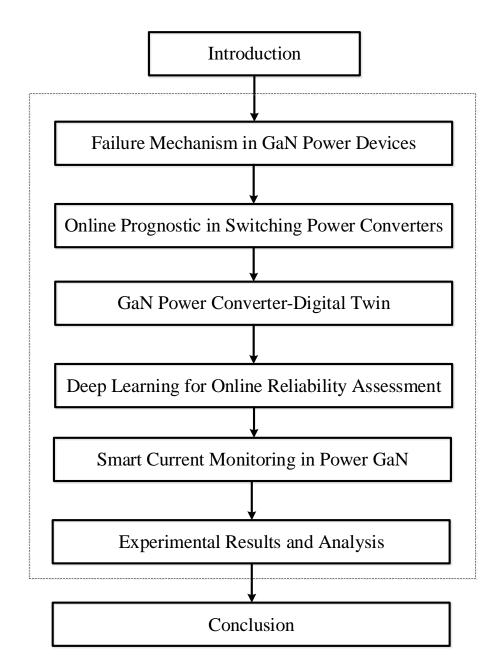

### 1.4 Thesis contributions

The thesis chapters are described as follows: Chapter 2 describes the failure mechanism affecting enhancement mode GaN power devices. Chapter 3 focuses on the fault diagnostic and the proposed solution for the active prognostics including the test benches. This chapter presents the architecture of the system as power electronics point of view. In Chapter 4, the concept of Deep Learning Reliability Awareness of Converters at the Edge (Deep RACE) is developed. Chapter 5 focuses on the system integration through edge computation following with the experimental results in Chapter 6. Chapter 7 discusses a new current measurement technique for active  $R_{ds(on)}$  measurements followed with the experimental results along with the conclusion and future work in Chapter 8. The thesis organization is also shown in Fig. 1.4.

Figure 1.4: **Thesis framework**: The main contributions of this work are provided in eight chapters.

# CHAPTER 2: FAILURE MECHANISM OF GaN TRANSISTORS IN POWER APPLICATIONS

#### 2.1 Characteristics and structure of GaN transistors

The invention of the High-electron-mobility transistor (HEMT) and using a channel instead of a doped region, which results in the generation of GaN transistors goes to back to 1970s. However, they have not been widely used due to technology maturation, and significantly lower cost of Si-based transistors. After 2000, using depletion mode GaN devices in RF application got more popular, where fabrication of different crystals such as SiC and AlGaN have been implemented [13, 14]. Nowadays, the general road map of using GaN will be categorized as: GaN on Si (for high power low cost applications) [15, 16], GaN on SiC (high performance, high cost for RF applications) [17], GaN on Diamond (for higher thermal conductivity applications) [18], GaN on GaN (Integrated IC, vertical GaN for future applications) [19]. It is expected by 2024 the GaN power market has annual growth more than 28% [20].

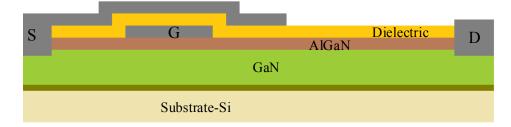

The common structure of GaN power devices is built in lateral architecture, which results in lower parasitic capacitance. Moreover, this architecture makes the main conduction path shorter, which results in lower  $R_{ds(on)}$ . In today's technology, the Si wafer is considered for the substrate to reduce the cost of manufacturing. GaN crystals are grown on the buffer layer (typically AlN) on the top of the substrate, followed by AlGaN to form an ohmic contact. The piezoelectric effect as a main source of GaN conductivity, the high concentration of electrons will be accumulated between AlGaN and GaN layer, and typically referred to as Two-Dimensional Electron Gas (2DEG). In enhancement mode GaN devices, a dielectric layer is considered underneath of the gate metal to make the normally-off transistors shown in Fig. 2.1.

Figure 2.1: Lateral GaN structure: The cross section of an enhancement GaN.

The lateral GaN structure has some benefits like relatively easy fabrication, lower conduction loss, and inexpensive solution. However, relatively low breakdown voltage, and the current collapse issue (due to high current flow near the surface) are the main drawbacks of this architecture [21]. After processing the waver, in order to make electrical connection to the outside, unlike many conventional methods for bond wire attachment, direct soldering of contacts to the wavers are used in state-of-the-art solutions of lead manufacturers [13, 16].

In general, higher energy band gap results in higher voltage breakdown, and lower ohmic resistance, which GaN shows promising performance on this side. Theoretically, GaN transistors should have a longer lifetime than Si devices because of their significantly higher activation energy (>2.0 e.V compared to 0.7 e.V for Si). However, engineers based on their requirements might come up with an individual converter design. These design might also have significant differences concerning topology, power rating, efficiency, performance, and implementation.

Today's manufacturers focused on two types of GaN power modules as enhancement and Cascode GaN devices. The enhancement mode GaN was known as normally OFF devices, and Cascode built as the combination of depletion mode GaN in series with Si-MOSFET. The Cascode architecture was proposed by different manufacturers (Transphorm, Sharp and TI), where in addition to depletion mode GaN a normally OFF Si-MOSFET is offered to make it feasible in many common designs. The gate circuit design of the MOSFET can control the ON/OFF state of the GaN since the MOSFET with higher absolute voltage compared to GaN threshold voltage. This topology has two side effects: As the gate circuit of the MOSFETs operates at a higher voltage level compared to the GaN, and consequently has a higher loss in the circuit. Moreover, the series MOSFETs will add additional resistance on the conduction path and reverse recovery charge of the body diode. On the other side, enhancement mode GaN give an opportunity to make the device normally OFF when the applied gate voltage compared to the source is zero. However, the effect of reverse conduction due to its inherent physics of the GaN semiconductors, they can fully turn on in the third quadrant. Lack of Si-body diode in the GaN devices might result in a higher loss during transients in Switch Mode Power Supplies (SMPS), which needs careful adjustment of dead-times. Moreover, a lower threshold of the voltage in the enhancement mode GaN offers lower loss in the gate driver circuits, but it makes the design very challenging because of overshoot and cross-talk considerations in the layout. All in all, simple packaging and no reverse recovery charge issue coming from the body diode, potentially much lower on-resistance gives a lot of interest for the manufacturer and designers to invest in this technology.

Due to relatively new evolved technology in the last years, and different manufacturing processes for GaN modules, a need for comprehensive reliability analysis would be crucial. This will be very helpful for designers who need transitions to this technology. Even for Si-based devices where their reliability have been examined, and standards test setup have been verified for several decades, there is no specific methodology to show the performance and characterization of power devices under converter operation, which might be varied from one to another design.

# 2.2 Failure mechanism in power semiconductors

### 2.2.1 Challenges for reliability evaluation in GaN power devices

Theoretically, GaN power transistors should have a longer lifetime than Si-devices because of their higher activation energy. However, due to some manufacturing limitation, this might not have been shown in any product yet. For instance, to reduce the cost of the GaN devices, many of lead manufacturers fabricate GaN on the Sisubstrate, where GaN and Si inherently have crystal mismatching. High-temperature methods have characterized most common ALT analysis for Si-based semiconductors and the failure mechanisms. For instance, Arrhenius exponential law as one of the most common techniques for the reliability assessment in Si-based semiconductors, the variation of activation energy results in the higher error for extrapolation to the real test conditions. Therefore, there are some severe constraints to comment on the accuracy of the conventional methodologies for failure mechanism extraction and remaining useful life estimation [22, 23].

Table 2.1: Summary of main failure mechanisms in GaN power

| Failure Potential                                     | $R_{ds(on)}$ | $V_{th}$         | $I_g$            |

|-------------------------------------------------------|--------------|------------------|------------------|

| Scottkey contact                                      | Increase     | Increase         | -                |

| Contact degradation                                   | -            | -                | Increase         |

| Ohmic thermal degradation                             | Increase     | Abnormal changes | -                |

| Charge trapping*                                      | Increase     | Decrease         | -                |

| Hot carrier trap generation <sup><math>*</math></sup> | Increase     | Decrease         | Increase         |

| Piezoelectric*                                        | Increase     | Decrease         | Abnormal changes |

### 2.2.2 A review of failure mechanism in previous studies

Power cycling tests on the discrete 650V GaN devices have been performed thoroughly in [24, 25] under several ALT. These studies showed the variations of  $I_{dss}$ ,  $R_{ds(on)}$ ,  $V_{th}$ , and  $T_j$  are more dominant after the ALT, and also verified that the solder layer is crucial in the device early degradation. Using  $R_{ds(on)}$  as a precursor for earlier failure of GaN devices was considered under ALT, and Extended Kalman Filter estimator was developed for device failure propagation and threshold identification in [26]. However, all of these methods have been analyzed under DC input supplies, where the results might vary under real switching converter operation, and need further evaluations.

Figure 2.2: Lateral GaN structure: The most susceptible regions in GaN device.

Furthermore, the focus is on finding the root of failure in GaN devices, by using similar semiconductors as Si-power semiconductors and GaAs in RF applications. The failure mechanism in Si-modules is categorized into two main groups as intrinsic and extrinsic. Intrinsic refers to failure damages coming from the semiconductors failures; however, the latter one includes the transistor packaging issues. Most common failures of intrinsic types are the dielectric breakdown, time-dependent dielectric breakdown, electromigration. For extrinsic, bond-wire lift failure, die solder degradation are reported in the previous literature [7, 8, 27, 28, 29, 30]. These studies verified the bond-wire lift has the severe effect on the device failure over time. However, because of the significant progress of developing new packages, such as LGA or GaN-PX, the conventional bond-wire issues cannot be easily found as the common failure in the modern GaN devices [31, 32]. Some studies by focusing on the similarity of the crystal structure of GaAs, and considering the similar substrate characteristics of Sibased semiconductors derived the potential failure in GaN modules [33, 34, 35, 36]. The most common potential failure of lateral GaN power devices is shown in Fig. 2.2 and precursor identifications are summarized in Table 2.1.

## CHAPTER 3: ONLINE PROGNOSTIC IN SWITCHING POWER CONVERTERS

### 3.1 Introduction

Controllable power semiconductor devices play the most dominant role in the switching power converters. Operating at high current and voltage create extreme stress on the power devices, which meanwhile make them the most susceptible components in the converters. Therefore, reliable operation of the power converters will be more highlighted in emerging technologies and future applications.

To address the reliability issues of a complex system in the design, fabrication, and maintenance process, different diagnostic and prognostics techniques are proposed. The evaluation of these processes is beneficiary to enable health management systems for useful life estimation and reducing the risk of failures [37, 38, 39]. However, the applied techniques (i.e., such as Kalman filter and Bayesian calibration) used classical first-order models; therefore their accuracies are limited and cannot be adaptive to long-term changes. Moreover, in advanced power electronics, it is hard to understand the degradation physics due to the system's sophistication, which makes then model them accurately in mathematical formats [40, 41, 42].

Recent advances in machine learning open a new horizon toward smart and autonomous systems. Applying machine learning at the earliest stage of design procedure has the most significant effect on the reliability pattern modeling. With the new wave of the Internet of Things (IoT), there is a big chance to be connected to any devices [43, 44]. In particular, the much higher impact could be in the power electronics as many factors are unknown, or it is tough to model in classical fashion. A real-time, low latency decision making and scalable systems require to move the computation of prediction from the cloud to the network nodes. This section presents a transformative approach for power semiconductor devices reliability to streamline the integration of devices into the smart power electronics systems. Therefore, an integrated framework is proposed based on cloud-edge platform, where training happens in the cloud and inference at the edge next to the power devices. In this regard, the recent advances of Recurrent Neural Networks (RNN) in deep learning is used to capture the behavior over time in complex systems. While training can be done off-line, interference will be operated at the edge (on-line) providing real-time feedback of the reliability modeling as well as active control and decision making for device proliferate.

### 3.2 Online reliability analysis GaN devices

The GaN power semiconductor is a promising solution to improve the efficiency and the performance of future power converters [45, 46]. Despite the superior characteristics of GaN devices, they are often turned down due to limited information on reliability in many applications. Diagnostics/prognostics approaches enable a possibility of solving reliability issues in complex systems from design to operation for remaining useful life estimation, and mitigation of failure risks. The studies on reliability assessment and system monitoring have focused on component level reliability, damage accumulation, data analytic and condition-based predictions [12, 40]. Component failure approaches rely on the statistical model derived from obtained data in a laboratory environment and/or historical component usage [11]. These methods are not considered prognostics since they do not take into account the unit-to-unit difference and their specific usage history. The damage accumulation methods offer more accurate tendency, but they need empirical verification and experimental observations. Data analytic and condition-based monitoring focus on big-data extraction, and estimation with the past usage history data provided by ALT. Several methods are proposed for mean-life estimates like six sigma, fault tree analysis, state space, and filtering estimations [41, 47].

Figure 3.1: Conventional reliability solution: #N samples of devices with #M conditions have been analyzed experimentally under accelerated life tests to find the reliability model. Adaptability with the new technologies and the experimental costs are their main drawbacks.

Furthermore, a newly developed PoF analysis is presented to identify the failure root mechanism and drive the reliability models quantitatively. Theoretically speaking, it is possible to make life predictions based on these methods; however, the performance is likely going to be poor when compared to the actual failure time observed. This occurs because no knowledge of the actual component is used, and all the applied techniques considered the constant failure rates in components and system levels [11, 48]. Most of the developed approaches relied on stress on the devices under power/thermal cycling with the experimental observations shown in Fig. 3.1. In the active monitoring technique, based on the available data from the system, a predictive online model for the converter operation can be derived. Having the limited knowledge of the existing state or the system status, the adaptive model can predict the system characteristics within the next time horizons shown in Fig. 3.2. The combination of failure diagnostics (model derivation) and self-verification techniques (deep learning analysis) can be evolved as a new generation of physics-based diagnostic/prognostic scheme to develop an adaptive model for a system level reliability.

Figure 3.2: **Proposed solution**: Adaptive prognostics concept using multi-physics co-simulations and machine learning algorithm with advanced monitoring.

This work presents a hybrid condition-based prediction where the ALT will be run in multi-physics simulations. Based on the simulated reliability model, a new RNN machine learning scheme is proposed for the system prognostics. Here, the component selection for the reliability analysis and modeling of solder fatigue in the power converter is described. This section also proposes the methodology for health conditioning system, which focuses on machine learning method for parameter estimations of the system calibration.

#### 3.3 GaN Power Converter-Digital Twin

#### 3.3.1 Thermomechanical susceptibility

In the existing lateral enhancement mode GaN products, GaN is grown on the Sisubstrate. Due to inherent mismatching of stacked materials, the different Coefficient of Thermal Expansion (CTE) of the mounted GaN onto the PCB causes generation of cracks. The GaN power device is subject to the high power, which makes the thermomechanical stress in the solder joints among the most susceptible sections. Therefore, the crack could propagate along the solder joints and eventually it will result in permanent failure in the devices. The solder joint fatigue existed in Si-based devices, but the fatigue in the compound semiconductors will be worse. Although there is no direct correlation between crack propagation and physical parameter extraction, the previous study showed this mechanism could have an impact on the gradual increase of the electrical resistance [49, 50, 51].

# 3.3.2 Reliability framework of power converter

To comment on the reliability assessment of power converters, it is essential to have a robust converter. Therefore, the summarized all the possible candidate of GaN devices are provided that could be used for this study. The loss index of  $R_{ds(on)} \times Q_g$ is defined to compare the efficiency power conversion in different devices, the thermal resistance and the reverse recovery charge also considered as shown in Table 3.2.

The various CTE of stacked layers inject stress concentrations, and they cause deformation of materials. The deformation mainly is observed as a crack on the solder joints, and eventually results in permanent failure of the compound semiconductors. The characterization of the crack propagation is very hard because of the complexity of the device and assembling of stacked layers. Moreover, challenging on the measurements of the operation of high-frequency converter makes the system modeling very difficult. Therefore, a new framework is proposed to be able to characterize the unknown parameters that physically are not possible to measure them on the operating power converter. The main contribution is to correlate the mathematical formulations of the direct measurement of  $R_{ds(on)}$  the corresponding mechanical parameters responsible for the fatigue. The proposed framework consists of three main sections as simulation-based ALT, online system monitoring, and the machine learning unit.

In the simulation-ALT, the energy-based fatigue of the power semiconductor under stress-strain hysteresis is modeled. The Gerber files of the converter layout will be imported, and the semiconductor device is shaped accordingly. Knowing the device conduction loss, the ALT is carried out under temperature cycling with the FEA. The simulation output provides a degradation model of the actual system. The model calibration is needed due to lack of detailed information of mounted device onto the PCB in the real order. The calibration will be done with the online measurements and update the unknown parameters through machine learning units. The online monitoring system focuses on system measurement of the main physical parameters (e.g., voltage, current, and the temperature). The resistance of the semiconductor, total loss, and the converter power range can be calculated based on the captured data. The machine learning unit based on the proposed model calibrates the simulation model according to the actual measurements shown in Fig. 3.5.

#### 3.3.3 Energy-based fatigue failure modeling

Thermal fatigue failure due to the CTE of materials is the main failure mechanism of the solder joint connections, especially in the compound semiconductors. The increase in the electrical resistance during fatigue has been studied and verified in [49, 50]. The energy-based fatigue is used by focusing on the energy accumulated in the susceptible regions shown in Fig. 3.3. The dissipated energy occurs within the strain-stress diagram, and the variations of resistance-strain are depicted in (3.1):

$$\Delta R_{ds(on)} = R_{ds(on)}(1+2v+a)\epsilon \tag{3.1}$$

Figure 3.3: Mounted GaN on the PCB: Simplified model of a lateral GaN mounted on the PCB. GaN and Silicon (substrates) are isolated with thin layer of AlGaN, and packaging is not considered in the model.

where v is Poisson ratio, a is the resistivity of the material, and  $\epsilon$  is the material strain [51]. These parameters depend on the material and the operational temperature can be considered as constant values. The total mechanical strain of the solder deformation can be given as (3.2):

$$\epsilon_t = \epsilon_e + \epsilon_c + \epsilon_p \tag{3.2}$$

where the  $\epsilon_e$ ,  $\epsilon_c$ ,  $\epsilon_p$  are elastic, creep and plastic strains respectively, and can be calculated in (3.3):

$$\frac{d\epsilon_s}{dt} = C_{ss}[sinh(\alpha\sigma)]^n exp(\frac{-E_a}{kT})$$

(3.3)

$$\epsilon_e = \sigma/E \tag{3.4}$$

$$\frac{d\epsilon_c}{dt} = \frac{d\epsilon_s}{dt} (1 + \epsilon_t B) exp(-B \frac{d\epsilon_c}{dt} t)$$

(3.5)

The summary of the parameters and the associated values are in Table 3.1.

| Parameter    | Description                 | Value                | Unit           |

|--------------|-----------------------------|----------------------|----------------|

| $C_{ss}$     | Constant                    | $8 \times e^4$       | 1/s            |

| lpha         | Stress level                | $4.6 \times e^{-4}$  | 1/psi          |

| k            | Boltzmann coefficient       | $1.38\times10^{-23}$ | $m^2 Kg/s^2 K$ |

| n            | Stress component            | 4                    | -              |

| $E_a$        | Activation of energy        | 0.7                  | e.V            |

| $\epsilon_t$ | Transient creep strain      | 0.025                | -              |

| B            | Transient creep coefficient | 260                  | -              |

| $C_p$        | Constant                    | $1.2 \times e^{-23}$ | -              |

| $\dot{m}$    | Constant                    | 5.5                  | -              |

| T            | Ambient Temperature         | 300                  | K              |

Table 3.1: Stress-strain parameters for the simulation analysis

During solder fatigue, the plastic strain plays a major role, where the rests of the strain changes remain almost constant [41, 52]. Knowing the material properties and the junction temperature of the device, the parameters associated with the elastic and creep strains will be constant:

$$\Delta W_{hys} = \oint_{Hystloop} \sigma d\epsilon \tag{3.6}$$

wherein (3.6)  $\sigma$  is the stress,  $\epsilon$  is strain, and  $W_{hys}$  is the cyclic dissipated energy loss shown in Fig. 3.4. Knowing the changes of strain ( $\epsilon$ ) could result in changes of on-resistance  $R_{ds(on)}$ , while the ALT runs for each iteration, a series test resistor will be added to the model to calculate the resistance variations. It can be presumed that the energy loss calculated in  $\Delta W_{hys}$  will potentially affect the tiny variations on the physical measurement of the on-resistance. Since finding all the unknown parameters associated with the loss model could be very difficult and time-consuming, the simplified model of this is used. Since the strain changes have a linear impact in the initial stages, the simplified model is developed as:

$$\epsilon_t = A \times (\sigma_{load} / \sigma_{ref})^B \tag{3.7}$$

where A and B are the unknown parametric constants coming from the machine learning algorithm,  $\epsilon_t$  is the total strain and  $\sigma_{load}$  is the load stress depending on the GaN loss generation and material properties defined in the simulation platform, and  $\sigma_{ref}$  is the reference stress expected from the manufacturer test plans shown in Fig. 3.6. Here, the fundamental material properties are used that has been used in the lateral GaN devices.